# Vishay Semiconductors

# Silicon PIN Photodiode

## **DESCRIPTION**

T1610P is a high speed and high sensitive PIN photodiode chip with 7.7 mm² sensitive area. It is sensitive to visible light much like the human eye and has peak sensitivity at 560 nm. Anode is the bond pad on top, cathode is the backside contact.

#### **FEATURES**

• Package type: chip

• Radiant sensitive area (in mm<sup>2</sup>): 7.7

· High photo sensitivity

- High radiant sensitivity

- · Suitable for visible light

- · Fast response times

- Angle of half sensitivity:  $\varphi = \pm 60^{\circ}$

- Compliant to RoHS directive 2002/95/EC and in accordance to WEEE 2002/96/EC

- · Ambient light sensor

- · Backlight dimmer

### **GENERAL INFORMATION**

The datasheet is based on Vishay optoelectronics sample testing under certain predetermined and assumed conditions, and is provided for illustration purpose only. Customers are encouraged to perform testing in actual proposed packaged and used conditions. Vishay optoelectronics die products are tested using Vishay optoelectronics based quality assurance procedures and are manufactured using Vishay optoelectronics established processes. Estimates such as those described and set forth in this datasheet for semiconductor die will vary depending on a number of packaging, handling, use, and other factors. Therefore sold die may not perform on an equivalent basis to standard package products.

| PRODUCT SUMMARY |                      |         |                       |  |

|-----------------|----------------------|---------|-----------------------|--|

| COMPONENT       | I <sub>ra</sub> (μΑ) | φ (deg) | λ <sub>0.5</sub> (nm) |  |

| T1610P          | 2.9                  | ± 60    | 390 to 800            |  |

#### Note

Test conditions see table "Basic Characteristics"

| ORDERING INFORMATION |                                      |              |              |  |

|----------------------|--------------------------------------|--------------|--------------|--|

| ORDERING CODE        | PACKAGING                            | REMARKS      | PACKAGE FORM |  |

| T1610P-SF-F          | Wafer sawn on foil without any frame | MOQ: 800 pcs | Chip         |  |

| T1610P-SD-F          | Wafer sawn on foil with discoframe   | MOQ: 800 pcs | Chip         |  |

#### Note

MOQ: minimum order quantity

| ABSOLUTE MAXIMUM RATINGS          |                |                   |               |      |  |

|-----------------------------------|----------------|-------------------|---------------|------|--|

| PARAMETER                         | TEST CONDITION | SYMBOL            | VALUE         | UNIT |  |

| Reverse voltage                   |                | $V_{R}$           | 16            | V    |  |

| Junction temperature              |                | Tj                | 100           | °C   |  |

| Operating temperature range       |                | T <sub>amb</sub>  | - 40 to + 100 | °C   |  |

| Storage temperature range         |                | T <sub>stg1</sub> | - 40 to + 100 | °C   |  |

| Storage temperature range on foil |                | T <sub>stg2</sub> | - 40 to + 50  | °C   |  |

#### Note

T<sub>amb</sub> = 25 °C, unless otherwise specified

# Vishay Semiconductors

# Silicon PIN Photodiode

| BASIC CHARACTERISTICS          |                                                                     |                      |      |            |      |      |

|--------------------------------|---------------------------------------------------------------------|----------------------|------|------------|------|------|

| PARAMETER                      | TEST CONDITION                                                      | SYMBOL               | MIN. | TYP.       | MAX. | UNIT |

| Breakdown voltage              | I <sub>R</sub> = 100 μA, E = 0                                      | V <sub>(BR)</sub>    | 16   |            |      | V    |

| Reverse dark current           | V <sub>R</sub> = 10 V, E = 0                                        | I <sub>ro</sub> 2    |      |            | 5    | nA   |

| Diode capacitance              | V <sub>R</sub> = 3 V, f = 1 MHz, E = 0                              | 0 C <sub>D</sub> 730 |      |            | pF   |      |

| Reverse light current          | $E_V = 100 \text{ lx, CIE illuminant A,}$<br>$V_R = 5 \text{ V}$    | ı, I <sub>ra</sub>   |      | 2.9        |      | μΑ   |

| Angle of half sensitivity      |                                                                     | φ                    |      | ± 60       |      | deg  |

| Wavelength of peak sensitivity |                                                                     | $\lambda_{p}$        |      | 560        |      | nm   |

| Range of spectral bandwidth    |                                                                     | λ <sub>0.5</sub>     |      | 390 to 800 |      | nm   |

| Rise time                      | $V_R = 5 \text{ V}, R_L = 50 \Omega,$<br>$\lambda = 515 \text{ nm}$ | t <sub>r</sub>       |      | 100        |      | ns   |

| Fall time                      | $V_R = 5 \text{ V}, R_L = 50 \Omega,$<br>$\lambda = 515 \text{ nm}$ | t <sub>f</sub>       |      | 100        |      | ns   |

### Notes

### **BASIC CHARACTERISTICS**

T<sub>amb</sub> = 25 °C, unless otherwise specified

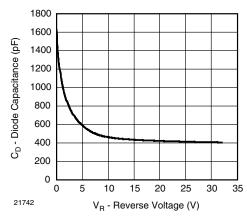

Fig. 1 - Diode Capacitance vs. Reverse Voltage

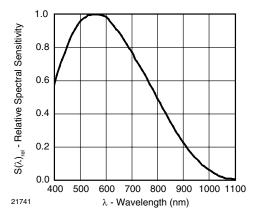

Fig. 2 - Relative Spectral Sensitivity vs. Wavelength

| MECHANICAL DIMENSIONS             |                |      |              |      |                 |

|-----------------------------------|----------------|------|--------------|------|-----------------|

| PARAMETER                         | SYMBOL         | MIN. | TYP.         | MAX. | UNIT            |

| Length of chip edge (x-direction) | L <sub>x</sub> |      | 2.97         |      | mm              |

| Length of chip edge (y-direction) | L <sub>y</sub> |      | 2.97         |      | mm              |

| Sensitive area                    | As             |      | 7.7          |      | mm <sup>2</sup> |

| Die height                        | Н              |      | 0.28         |      | mm              |

| Bond pad anode                    | x * y          |      | 0.125 x 0.11 |      | mm <sup>2</sup> |

$T_{amb}$  = 25 °C, unless otherwise specified

The measurements are based on samples of die which are mounted on a TO-header without resin coating

# Silicon PIN Photodiode

# Vishay Semiconductors

| ADDITIONAL INFORMATION (1)      |               |  |  |

|---------------------------------|---------------|--|--|

| Frontside metallization, anode  | AlSi          |  |  |

| Backside metallization, cathode | NiV-Ag        |  |  |

| Dicing                          | Sawing        |  |  |

| Die bonding technology          | Epoxy bonding |  |  |

#### Note

The visual inspection shall be made in accordance with the "specification of visual inspection as referenced". The visual inspection of chip backside is performed with stereo microscope with incident light and 40x to 80x magnification.

The quality inspection (final visual inspection) is performed by production. An additional visual inspection step as special release procedure by QM is not installed.

#### HANDLING AND STORAGE CONDITIONS

- The hermetically sealed shipment lots shall be opened in temperature and moisture controlled cleanroom environment only. It is mandatory to follow the rules for disposition of material that can be hazardous for humans and environment.

- Product must be handled only at ESD safe workstations. Standard ESD precautions and safe work environments are as defined in MIL-HDBK-263.

- · Singulated die are not to be handled with tweezers. A vacuum wand with non metallic ESD protected tip should be used.

#### **PACKING**

Chips are fixed on adhesive foil. Upon request the foils can be mounted on plastic frame or disco frame. For shipment, the wafers are arranged to stacks and hermetically sealed in plastic bags to ensure protection against environmental influence (humidity and contamination).

Use for recycling reliable operators only. We can help getting in touch with your nearest sales office. By agreement we will take back packing material, if it is sorted. You will have to bear the costs of transport. We will invoice you for any costs incurred for packing material that is returned unsorted or which we are not obliged to accept.

<sup>(1)</sup> All chips are checked in accordance with the Vishay Semiconductor, specification of visual inspection FVOV6870.

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com