8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

### **Product List**

SM59D03G2L25, 25MHz 8KB+ internal Flash MCU SM59D03G2C25, 25MHz 8KB+ internal Flash MCU

## **Description**

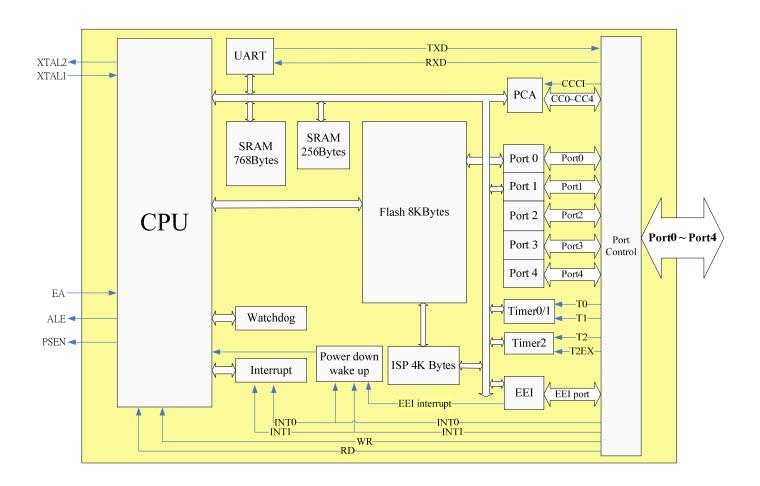

The SM59D03G2 series product is an 8-bit single chip macro-controller with 8K bytes Flash & 1K byte RAM embedded.

It is a derivative of the 8052 micro-controller family with a fully compatible instruction sets.

The 8K bytes embedded Flash can be programmed via a commercial writer or ISP (In-System Programming) or ICP (In-Circuit Programming) function. The unused Flash on 4K bytes ISP service Program area can be the memory space for the EEPROM application through the ISP.

After programming, the code can be protected to prevent illegal read and write.

Its plentiful peripherals can make many applications easier and more efficient, such as dual DPTR, UART, WDT, Timers, PCA and EEI which are functionally compatible with most other chips.

SM59D03G2 also provides power saving modes (IDLE and STOP), low EMI characteristics, etc. All of the requirements are considered to achieve the ideal MCU.

# **Ordering Information**

yymmv SM59D03G2ihhkL

yy: year, mm: month

v: version identifier{ A, B,...}

i: process identifier {L=2.7V~3.6V,C=4.5V~ 5.5V}

hh: working clock in MHz {25}

k: package type postfix {as below table}

L:PB Free identifier

{No text is Non-PB Free, "P" is PB Free}

| Postfix | Package  | Pin / Pad Configuration |  |  |

|---------|----------|-------------------------|--|--|

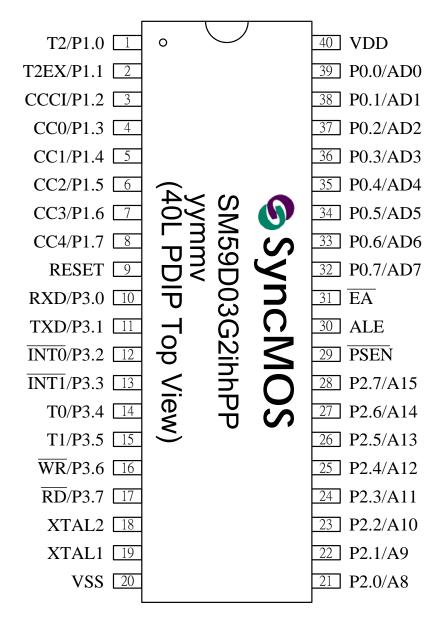

| Р       | 40L PDIP | Page 2                  |  |  |

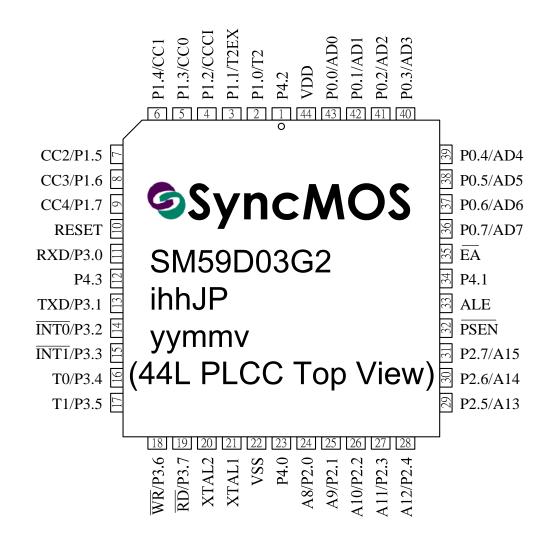

| J       | 44L PLCC | Page 3                  |  |  |

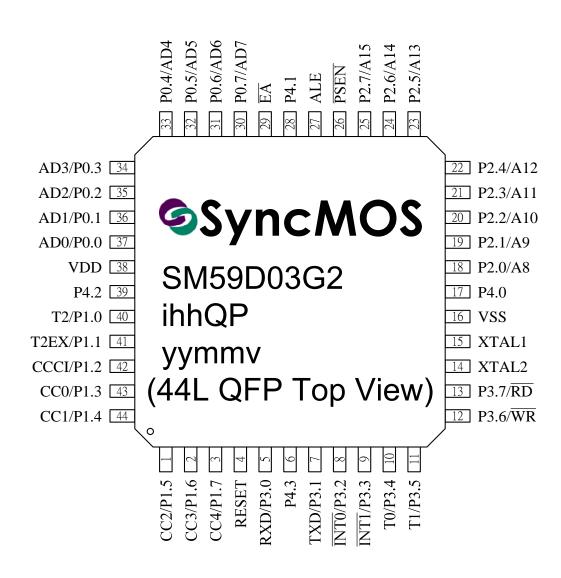

| Q       | 44L QFP  | Page 4                  |  |  |

### **Features**

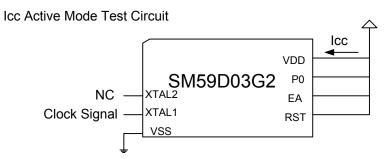

- Operating Voltage: 2.7V ~ 3.6V or 4.5V ~ 5.5V

- General 8052 family compatible

- 12 or 6 clocks per machine cycle

- Frequency runs up to 25MHz

- 8K bytes on chip program Flash

- 4K bytes In-System Programming(ISP) and EEPROM capability

- 768 Bytes on-chip expanded RAM with disable function

- 256 Bytes for standard 8052 RAM.

- External RAM address up to 64KB

- Dual 16-bit Data Pointers (DPTR0 & DPTR1)

- One channel serial peripheral interface (UART)

- Three 16 bit Timers/Counters(Timer 0, 1, 2)

- Four 8-bit I/O ports for PDIP package

- Four 8-bit I/O ports + one 4-bit I/O ports for PLCC or QFP package

- Programmable Watchdog Timer (WDT)

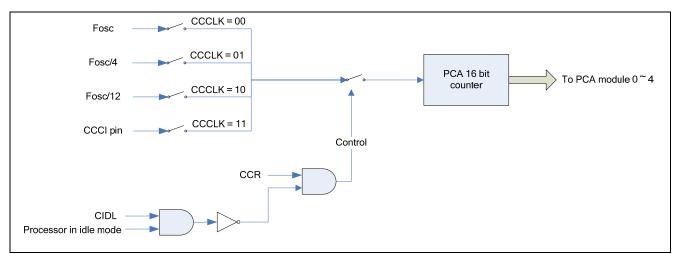

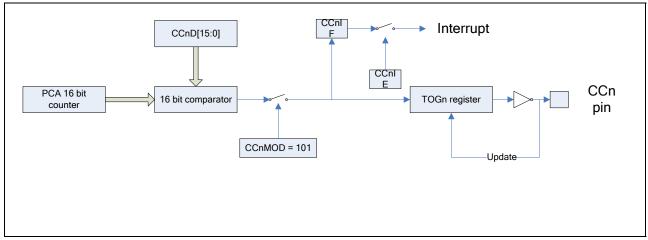

- Programmable Counter Array (PCA) for Pulse

Width Modulation (PWM), capture and compare

- External interrupt 0, 1 with two priority level

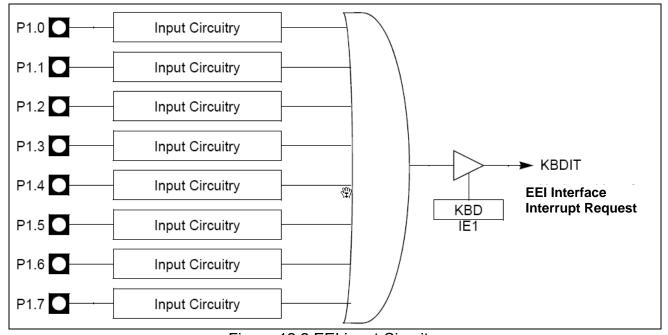

- Expanded External Interrupt (EEI) interface for eight more external interrupts.

- ISP service program space configurable in N\*512 byte (N=0 to 8) size for IAP application

- Direct and simple ICP programming without service program

- ALE output select for low EMI

- Clock output as the source for next MCU

- Power Management Unit ( IDLE and STOP mod)

- Code protection function

- Flash Memory Endurance : 100K erase and write cycles each byte at TA=25°C

- Flash Memory Data Retention :10 years

Contact SyncMOS: www.syncmos.com.tw 6F, No.10-2 Li- Hsin 1st Road, SBIP,

Hsinchu, Taiwan 30078

TEL: 886-3-567-1820 FAX: 886-3-567-1891

# **Pin Configuration**

# **Block Diagram**

### 8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

**Pin Description**

| <u>PIN</u>          | Pin Description    |                     |                            |     |                                                                                                          |  |  |  |  |  |

|---------------------|--------------------|---------------------|----------------------------|-----|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 40L<br>PDIP<br>Pin# | 44L<br>QFP<br>Pin# | 44L<br>PLCC<br>Pin# | Symbol                     | I/O | Names                                                                                                    |  |  |  |  |  |

| 1                   | 40                 | 2                   | P10/T2/EEI0/ICP_CLK        | i/o | Bit 0 of port 1 & Timer 2 external input clock & EEI interrupt 0 & ICP clock input                       |  |  |  |  |  |

| 2                   | 41                 | 3                   | P11/T2EX/EEI1/ICP_TRIG     | i/o | Bit 1 of port 1 & Timer 2 capture trigger & EEI interrupt 1 & ICP Trigger (active low)                   |  |  |  |  |  |

| 3                   | 42                 | 4                   | P12/CCCI/EEI2<br>/ICP_DATA | i/o | Bit 2 of port 1 & PCA External clock input & EEI interrupt 2 & ICP data/command IO                       |  |  |  |  |  |

| 4                   | 43                 | 5                   | P13/CC0/EEI3               | i/o | Bit 3 of port 1 & PCA Channel 0 & EEI interrupt 3                                                        |  |  |  |  |  |

| 5                   | 44                 | 6                   | P14/CC1/EEI4               | i/o | Bit 4 of port 1 & PCA Channel 1 & EEI interrupt 4                                                        |  |  |  |  |  |

| 6                   | 1                  | 7                   | P15/CC2/EEI5               | i/o | Bit 5 of port 1 & PCA Channel 2 & EEI interrupt 5                                                        |  |  |  |  |  |

| 7                   | 2                  | 8                   | P16/CC3/EEI6               | i/o | Bit 6 of port 1 & PCA Channel 3 & EEI interrupt 6                                                        |  |  |  |  |  |

| 8                   | 3                  | 9                   | P17/CC4/EEI7               | i/o | Bit 7 of port 1 & PCA Channel 4 & EEI interrupt 7                                                        |  |  |  |  |  |

| 9                   | 4                  | 10                  | RESET                      | i   | Hardware reset input (active high)                                                                       |  |  |  |  |  |

| 10                  | 5                  | 11                  | P30/RXD                    | i/o | Bit 0 of port 3 & Serial interface channel receive/transmit data                                         |  |  |  |  |  |

| 11                  | 7                  | 13                  | P31/TXD                    | i/o | Bit 1 of port 3 & Serial interface channel transmit data or receive clock in mode 0                      |  |  |  |  |  |

| 12                  | 8                  | 14                  | P32/INT0                   | i/o | Bit 2 of port 3 & External interrupt 0 (low or falling-edge trigger)                                     |  |  |  |  |  |

| 13                  | 9                  | 15                  | P33/INT1                   | i/o | Bit 3 of port 3 & External interrupt 1 (low or falling-edge trigger)                                     |  |  |  |  |  |

| 14                  | 10                 | 16                  | P34/T0                     | i/o | Bit 4 of port 3 & Timer 0 external input                                                                 |  |  |  |  |  |

| 15                  | 11                 | 17                  | P35/T1                     | i/o | Bit 5 of port 3 & Timer 1 external input                                                                 |  |  |  |  |  |

| 16                  | 12                 | 18                  | P36/WR                     | i/o | Bit 6 of port 3 & external memory write signal                                                           |  |  |  |  |  |

| 17                  | 13                 | 19                  | P37/RD                     | i/o | Bit 7 of port 3 & external memory read signal                                                            |  |  |  |  |  |

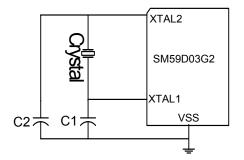

| 18                  | 14                 | 20                  | XTAL2                      | 0   | Crystal output or oscillator input                                                                       |  |  |  |  |  |

| 19                  | 15                 | 21                  | XTAL1                      | i   | Crystal input                                                                                            |  |  |  |  |  |

| 20                  | 16                 | 22                  | VSS                        |     | Ground                                                                                                   |  |  |  |  |  |

| 21                  | 18                 | 24                  | P20/A8                     | i/o | Bit 0 of port 2 & Bit 8 of external memory address                                                       |  |  |  |  |  |

| 22                  | 19                 | 25                  | P21/A9                     | i/o | Bit 1 of port 2 & Bit 9 of external memory address                                                       |  |  |  |  |  |

| 23                  | 20                 | 26                  | P22/A10                    | i/o | Bit 2 of port 2 & Bit 10 of external memory address                                                      |  |  |  |  |  |

| 24                  | 21                 | 27                  | P23/A11                    | i/o | Bit 3 of port 2 & Bit 11 of external memory address                                                      |  |  |  |  |  |

| 25                  | 22                 | 28                  | P24/A12                    | i/o | Bit 4 of port 2 & Bit 12 of external memory address                                                      |  |  |  |  |  |

| 26                  | 23                 | 29                  | P25/A13                    | i/o | Bit 5 of port 2 & Bit 13 of external memory address                                                      |  |  |  |  |  |

| 27                  | 24                 | 30                  | P26/A14                    | i/o | Bit 6 of port 2 & Bit 14 of external memory address                                                      |  |  |  |  |  |

| 28                  | 25                 | 31                  | P27/A15                    | i/o | Bit 7 of port 2 & Bit 15 of external memory address                                                      |  |  |  |  |  |

| 29                  | 26                 | 32                  | PSEN/ Clk_out              | 0   | Program storage enable (active low) & crystal/oscillator clock output as the clock source for the others |  |  |  |  |  |

| 30                  | 27                 | 33                  | ALE                        | 0   | Address latch enable                                                                                     |  |  |  |  |  |

| 31                  | 29                 | 35                  | EA                         | 1   | External access with internal pull-up (active low)                                                       |  |  |  |  |  |

| 32                  | 30                 | 36                  | P07/AD7                    | i/o | Bit 7 of port 0 & Bit 7 of external memory address/data                                                  |  |  |  |  |  |

| 33                  | 31                 | 37                  | P06/AD6                    | i/o | Bit 6 of port 0 & Bit 6 of external memory address/data                                                  |  |  |  |  |  |

| 34                  | 32                 | 38                  | P05/AD5                    | i/o | Bit 5 of port 0 & Bit 5 of external memory address/data                                                  |  |  |  |  |  |

| 35                  | 33                 | 39                  | P04/AD4                    | i/o | Bit 4 of port 0 & Bit 4 of external memory address/data                                                  |  |  |  |  |  |

| 36                  | 34                 | 40                  | P03/AD3                    | i/o | Bit 3 of port 0 & Bit 3 of external memory address/data                                                  |  |  |  |  |  |

| 37                  | 35                 | 41                  | P02/AD2                    | i/o | Bit 2 of port 0 & Bit 2 of external memory address/data                                                  |  |  |  |  |  |

| 38                  | 36                 | 42                  | P01/AD1                    | i/o | Bit 1 of port 0 & Bit 1 of external memory address/data                                                  |  |  |  |  |  |

| 39                  | 37                 | 43                  | P00/AD0                    | i/o | Bit 0 of port 0 & Bit 0 of external memory address/data                                                  |  |  |  |  |  |

| 40                  | 38                 | 44                  | VDD                        |     | Power supply                                                                                             |  |  |  |  |  |

|                     | 17                 | 23                  | P40                        | i/o | Bit 0 of port 4                                                                                          |  |  |  |  |  |

|                     | 28                 | 34                  | P41                        | i/o | Bit 1 of port 4                                                                                          |  |  |  |  |  |

|                     | 39                 | 1                   | P42                        | i/o | Bit 2 of port 4                                                                                          |  |  |  |  |  |

|                     | 6                  | 12                  | P43                        | i/o | Bit 3 of port 4                                                                                          |  |  |  |  |  |

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M030 6 Ver.C SM59D03G2 07/2009

# **Special Function Register (SFR)**

Address 80h to FFh is the location of SM59D03G2 special function register (SFR). These locations must be accessed by direct addressing mode only.

The following table gives the SFRs, part of them are identically located and defined as the general 8052 series:

Table: SM59D03G2 SFR location

|    | 0/8   | 1/9   | 2/A    | 3/B    | 4/C    | 5/D    | 6/E    | 7/F    |           |

|----|-------|-------|--------|--------|--------|--------|--------|--------|-----------|

| F8 |       |       |        |        |        | KBLS   | KBE    | KBF    | FF        |

| F0 | В     |       |        |        | ISPFAH | ISPFAL | ISPFD  | ISPC   | F7        |

| E8 |       |       |        |        |        |        |        |        | EF        |

| E0 | ACC   |       |        |        |        |        |        |        | E7        |

| D8 | P4    |       |        |        |        |        |        |        | DF        |

| D0 | PSW   |       |        |        |        |        |        |        | D7        |

| C8 | T2CON | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |        |        | CF        |

| C0 |       |       |        |        |        |        |        |        | <b>C7</b> |

| B8 | IP    | IP1   |        |        |        |        |        | SCONF  | BF        |

| В0 | P3    |       |        |        |        | RCON   |        |        | B7        |

| A8 | ΙE    | IE1   |        |        |        |        |        |        | AF        |

| Α0 | P2    | PCAC1 | PCAC2  | CC0CON | CC1CON | CC2CON | CC3CON | CC4CON | A7        |

| 98 | SCON  | SBUF  | PCACH  | PCACL  | CC0DH  | CC0DL  | CC1DH  | CC1DL  | 9F        |

| 90 | P1    | CC2DH | CC2DL  | CC3DH  | CC3DL  | CC4DH  | CC4DL  |        | 97        |

| 88 | TCON  | TMOD  | TL0    | TL1    | TH0    | TH1    | WDTC   | WDTK   | 8F        |

| 80 | P0    | SP    | DPL    | DPH    | DPL1   | DPH1   | DPS    | PCON   | 87        |

Here is the simple description and initial value of the above SFR. A detailed explanation is given in later sections.

Table: SFR description and initial value

| Register | Location | Initial value | Description              |  |  |

|----------|----------|---------------|--------------------------|--|--|

| P0       | 80h      | FFh           | Port 0                   |  |  |

| SP       | 81h      | 07h           | Stack Pointer            |  |  |

| DPL      | 82h      | 00h           | Data Pointer Low byte    |  |  |

| DPH      | 83h      | 00h           | Data Pointer High byte   |  |  |

| DPL1     | 84h      | 00h           | Data Pointer 1 Low byte  |  |  |

| DPH1     | 85h      | 00h           | Data Pointer 1 High byte |  |  |

| DPS      | 86h      | 00h           | Data Pointer select      |  |  |

| PCON     | 87h      | 00h           | Power control register   |  |  |

| TCON     | 88h      | 00h           | Timer control register   |  |  |

| TMOD     | 89h      | 00h           | Timer Mode               |  |  |

| TL0      | 8Ah      | 00h           | Timer 0 low byte         |  |  |

| TL1      | 8Bh      | 00h           | Timer 1 low byte         |  |  |

| TH0      | 8Ch      | 00h           | Timer 0 high byte        |  |  |

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M030 7 Ver.C SM59D03G2 07/2009

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

| Register | Location | Initial value | Description                                 |

|----------|----------|---------------|---------------------------------------------|

| TH1      | 8Dh      | 00h           | Timer 1 high byte                           |

| WDTC     | 8Eh      | 00h           | Watchdog timer control register             |

| WDTK     | 8Fh      | 00h           | Watchdog timer refresh key                  |

| P1       | 90h      | FFh           | Port 1                                      |

| CC2DH    | 91h      | 00h           | Compare/Capture channel 2 data high byte    |

| CC2DL    | 92h      | 00h           | Compare/Capture channel 2 data low byte     |

| CC3DH    | 93h      | 00h           | Compare/Capture channel 3 data high byte    |

| CC3DL    | 94h      | 00h           | Compare/Capture channel 3 data low byte     |

| CC4DH    | 95h      | 00h           | Compare/Capture channel 4 data high byte    |

| CC4DL    | 96h      | 00h           | Compare/Capture channel 4 data low byte     |

| SCON     | 98h      | 00h           | Serial port channel (UART) control register |

| SBUF     | 99h      | XXh           | Serial port channel (UART) data buffer      |

| PCACH    | 9Ah      | 00h           | PCA counter high byte                       |

| PCACL    | 9Bh      | 00h           | PCA counter low byte                        |

| CC0DH    | 9Ch      | 00h           | Compare/Capture channel 0 data high byte    |

| CC0DL    | 9Dh      | 00h           | Compare/Capture channel 0 data low byte     |

| CC1DH    | 9Eh      | 00h           | Compare/Capture channel 1 data high byte    |

| CC1DL    | 9Fh      | 00h           | Compare/Capture channel 1 data low byte     |

| P2       | A0h      | FFh           | Port 2                                      |

| PCAC1    | A1h      | 00h           | PCA control register 1                      |

| PCAC2    | A2h      | 00h           | PCA control register 2                      |

| CC0CON   | A3h      | 00h           | Compare/Capture channel 0 control register  |

| CC1CON   | A4h      | 00h           | Compare/Capture channel 1 control register  |

| CC2CON   | A5h      | 00h           | Compare/Capture channel 2 control register  |

| CC3CON   | A6h      | 00h           | Compare/Capture channel 3 control register  |

| CC4CON   | A7h      | 00h           | Compare/Capture channel 4 control register  |

| IE       | A8h      | 00h           | Interrupt Enable                            |

| IE1      | A9h      | 00h           | Interrupt Enable 1 register                 |

| P3       | B0h      | FFh           | Port 3                                      |

| IP       | B8h      | 00h           | Interrupt Priority                          |

| IP1      | B9h      | 00h           | Interrupt Priority 1 register               |

| SCONF    | BFh      | 00h           | System control flag                         |

| T2CON    | C8h      | C0h           | Timer 2 control register                    |

| T2MOD    | C9h      | 00h           | Timer 2 mode                                |

| RCAP2L   | CAh      | 00h           | Reload/Capture data low byte                |

| RCAP2H   | CBh      | 00h           | Reload/Capture data high byte               |

| TL2      | CCh      | FFh           | Timer 2 low byte                            |

| TH2      | CDh      | FFh           | Timer 2 high byte                           |

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M030 8 Ver.C SM59D03G2 07/2009

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

| Register | Location | Initial value | Description                  |

|----------|----------|---------------|------------------------------|

| PSW      | D0h      | 00h           | Program Status Word register |

| P4       | D8h      | xFh           | Port 4                       |

| ACC      | E0h      | 00h           | Accumulator                  |

| В        | F0h      | 00h           | B register                   |

| ISPFAH   | F4h      | 00h           | ISP address high byte        |

| ISPFAL   | F5h      | 00h           | ISP address low byte         |

| ISPFD    | F6h      | 00h           | ISP data register            |

| ISPC     | F7h      | 00h           | ISP control register         |

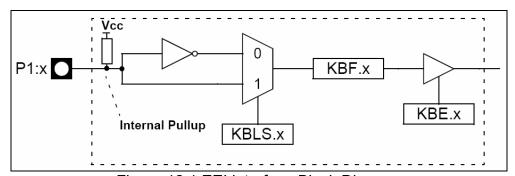

| KBLS     | FDh      | 00h           | EEI Level Selector Register  |

| KBE      | FEh      | 00h           | EEI input Enable Register    |

| KBF      | FFh      | 00h           | EEI Flag register            |

## **Function Description**

#### 1 General Features

SM59D03G2 is an 8-bit micro-controller. All of its functions and the detailed meanings of SFR will be given in the following sections.

#### 1.1 Embedded Flash

The program can be loaded into the embedded 8K bytes Flash memory via its writer or ISP (In-System Programming) or ICP (In-Circuit Programming) function.

The high-quality Flash is suitable for re-programming and data recording as EEPROM.

### 1.2 IO Pads

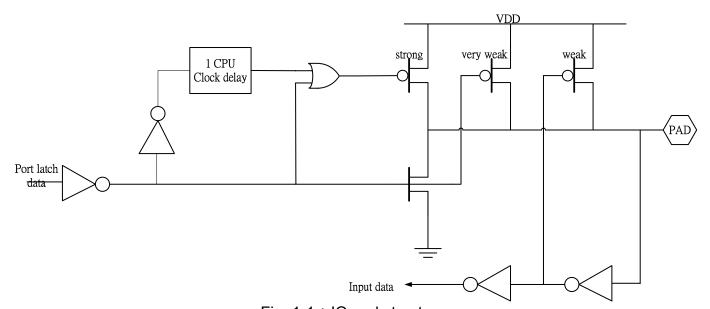

The IO pads are compatible to the 8052 series. P0 is open-drain in the input or output high condition, so the external pull-up resistor is required. P1  $\sim$  P4 are designed with internal pull-up resistors. The IO pad structure is given below:

Fig. 1-1: IO pad structure

All the pads for P0  $\sim$  P4 are with slew rate to reduce EMI. The other way to reduce EMI is to disable the ALE output if unused. This is selected by its SFR. In 3.3V applications, the IO pads are 5V tolerant except for XATL1 and XTAL2.

### 1.3 12T/6T Selection

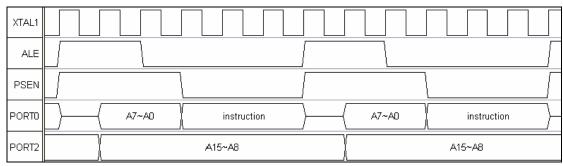

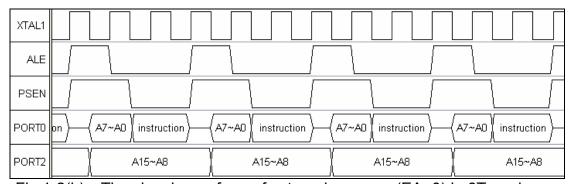

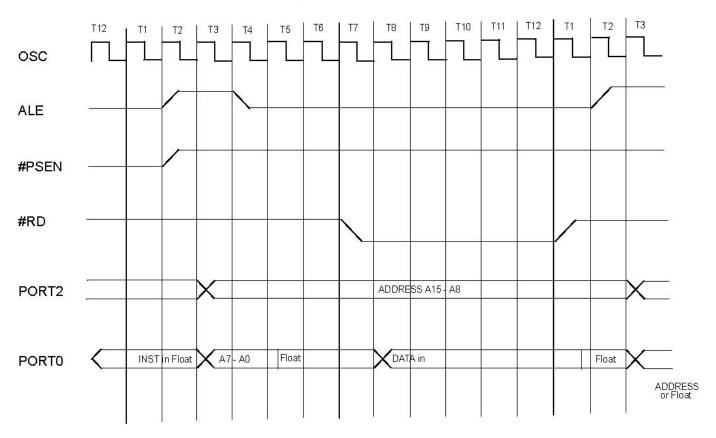

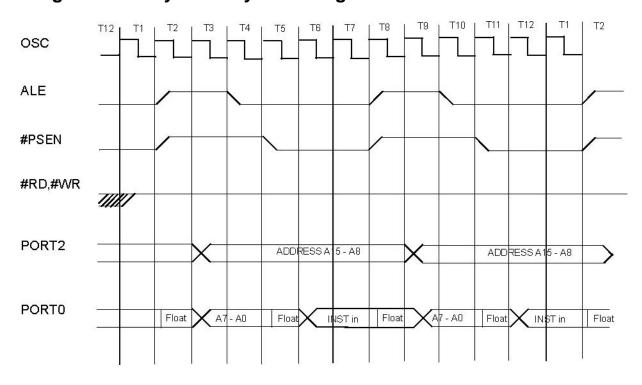

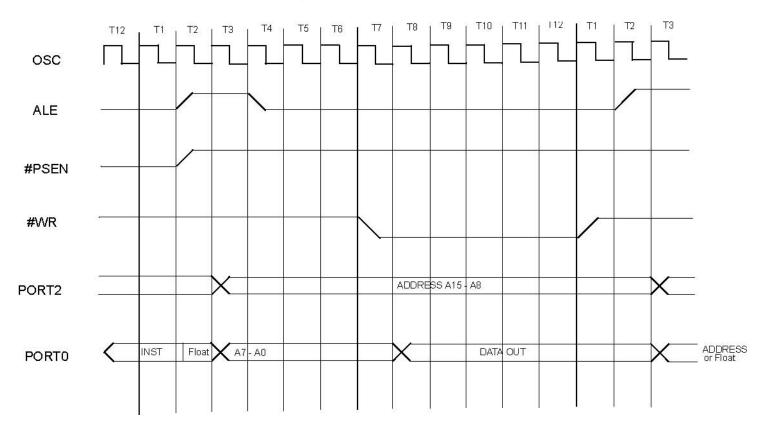

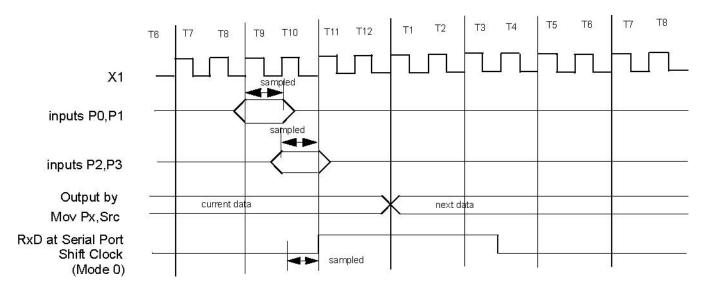

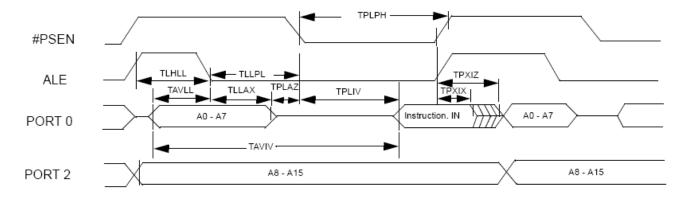

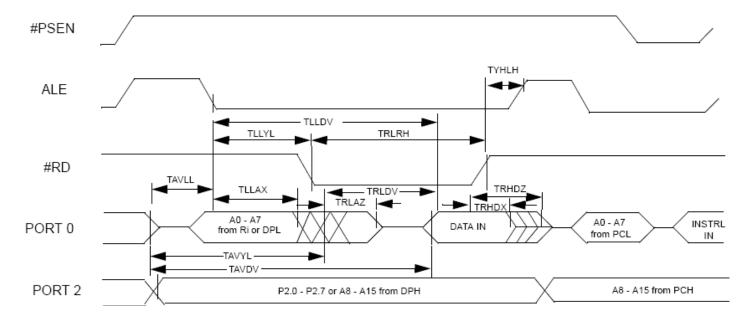

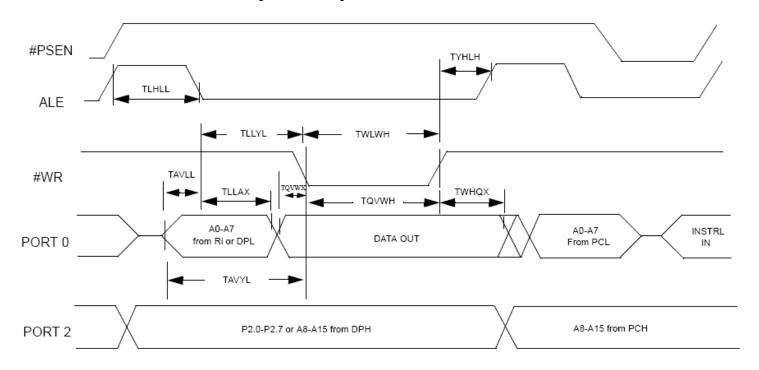

The conventional 52-series MCUs are 12T, i.e., 12 oscillator clocks per one machine cycle. If the machine cycle is changed to 6 clocks, then this 6T mode will double the running speed of 12T's with the same oscillator source. 12T or 6T is configured in the information block. The figures given below are an example to show the difference of 12T mode and 6T mode.

Fig 1-2(a): The signal waveform of external program (EA=0) in 12T mode

Fig 1-2(b): The signal waveform of external program (EA=0) in 6T mode

Since the execution speed in 6T is two times of that in 12T, in order for the easy explanation in the later sections, here we define the terminology "system clock" or "system frequency" as:

System clock frequency(Fosc) = crystal( $F_{CRY}$ ) or oscillator frequency in 6T, and System clock frequency(Fosc) = crystal( $F_{CRY}$ ) or oscillator frequency divided by 2 in 12T

Take a 16MHz oscillator as an example, the system clock frequency is 16MHz in 6T. But in 12T mode, the system clock frequency is 8MHz.

### 2 Instruction set

The SM59D03G2 uses the powerful 80C51 instruction set. It consists of 49 single-byte, 42 two-byte and 15 three-byte instructions. Among them, 63 instructions are executed in 1 machine-cycle, 46 instructions in 2 machine-cycles and 2 instructions in 4 machine-cycles. A summary of the instruction set is given in Table 2-1. All of the instructions are fully compatible with standard 8052-series'.

Table 2.1 Instruction set

| Mnemonic    | ;             | OPERATION                  | BYTE | CYCLE |

|-------------|---------------|----------------------------|------|-------|

| Arithmetic  | Instructions  |                            | J.   |       |

| ADD         | A, Rn         | A = A + Rn                 | 1    | 1     |

| ADD         | A, direct     | A = A + direct             | 2    | 1     |

| ADD         | A, @Ri        | A = A + <@Ri>              | 1    | 1     |

| ADD         | A, #data      | A = A + #data              | 2    | 1     |

| ADDC        | A, Rn         | A = A + Rn + C             | 1    | 1     |

| ADDC        | A, direct     | A = A + direct + C         | 2    | 1     |

| ADDC        | A, @Ri        | A = A + @Ri + C            | 1    | 1     |

| ADDC        | A, #data      | A = A + #data + C          | 2    | 1     |

| SUBB        | A, Rn         | A = A - Rn - C             | 1    | 1     |

| SUBB        | A, direct     | A = A - direct - C         | 2    | 1     |

| SUBB        | A, @Ri        | A = A - <@Ri> - C          | 1    | 1     |

| SUBB        | A. #data      | A = A - #data - C          | 2    | 1     |

| INC         | A             | A = A + 1                  | 1    | 1     |

| INC         | Rn            | Rn = Rn + 1                | 1    | 1     |

| INC         | direct        | direct = direct + 1        | 2    | 1     |

| INC         | @Ri           | <@Ri> = <@Ri> + 1          | 1    | 1     |

| DEC         | A             | A=A - 1                    | 1    | 1     |

| DEC         |               |                            |      |       |

|             | Rn            | Rn = Rn - 1                | 1    | 1     |

| DEC         | direct        | direct = direct - 1        | 2    | 1     |

| DEC         | @Ri           | <@Ri> = <@Ri> - 1          | 1    | 1     |

| INC         | DPTR          | DPTR = DPTR - 1            | 1    | 2     |

| MUL         | AB            | $B:A = A \times B$         | 1    | 4     |

| DIV         | AB            | A = INT (A/B)              | 1    | 4     |

|             |               | B = MOD(A/B)               |      |       |

| DA          | Α             | Decimal adjust ACC         | 1    | 1     |

| Logical Ins | structions    | •                          |      |       |

| ANL         | A, Rn         | A .AND. Rn                 | 1    | 1     |

| ANL         | A, direct     | A .AND. direct             | 2    | 1     |

| ANL         | A, @Ri        | A .AND. <@Ri>              | 1    | 1     |

| ANL         | A, #data      | A .AND. #data              | 2    | 1     |

| ANL         | direct, A     | direct .AND. A             | 2    | 1     |

| ANL         | direct, #data | direct .AND. #data         | 3    | 2     |

| ORL         | A, Rn         | A .OR. Rn                  | 1    | 1     |

| ORL         | A, direct     | A .OR. direct              | 2    | 1     |

| ORL         | A, @Ri        | A .OR. <@Ri>               | 1    | 1     |

| ORL         | A, #data      | A .OR. #data               | 2    | 1     |

| ORL         | direct, A     | direct .OR. A              | 2    | 1     |

| ORL         | direct, #data | direct .OR. #data          | 3    | 2     |

| XRL         | A, Rn         | A .XOR. Rn                 | 1    | 1     |

| XRL         | A, direct     | A .XOR. direct             | 2    | 1     |

| XRL         | A, @Ri        | A .XOR. <@Ri>              | 1    | 1     |

| XRL         | A, #data      | A .XOR. #data              | 2    | 1     |

| XRL         | direct, A     | direct .XOR. A             | 2    | 1     |

| XRL         | direct, #data | direct .XOR. #data         | 3    | 2     |

| CLR         | Α             | A = 0                      | 1    | 1     |

| CPL         | Α             | A = /A                     | 1    | 1     |

| RL          | Α             | Rotate ACC Left 1 bit      | 1    | 1     |

| RLC         | Α             | Rotate Left through Carry  | 1    | 1     |

| RR          | Α             | Rotate ACC Right 1 bit     | 1    | 1     |

| RRC         | Α             | Rotate Right through Carry | 1    | 1     |

|             |               |                            |      |       |

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M030 12 Ver.C SM59D03G2 07/2009

## 8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

| Data Trans | fers Instructions |                                             |   |   |

|------------|-------------------|---------------------------------------------|---|---|

| MOV        | A, Rn             | A = Rn                                      | 1 | 1 |

| MOV        |                   |                                             | 2 | 1 |

|            | A, direct         | A = direct                                  |   |   |

| MOV        | A, @Ri            | A = <@Ri>                                   | 1 | 1 |

| MOV        | A, #data          | A = #data                                   | 2 | 1 |

| MOV        | Rn, A             | Rn = A                                      | 1 | 1 |

| MOV        | Rn, direct        | Rn = direct                                 | 2 | 2 |

| MOV        | Rn, #data         | Rn = #data                                  | 2 | 1 |

| MOV        | direct, A         | direct = A                                  | 2 | 1 |

| MOV        | direct, Rn        | direct = Rn                                 | 2 | 2 |

| MOV        | direct, direct    | direct = direct                             | 3 | 2 |

| MOV        | direct, @Ri       | direct = <@Ri>                              | 2 | 2 |

| MOV        | direct, #data     | direct = #data                              | 2 | 1 |

| MOV        | @Ri, A            | <@Ri> = A                                   | 1 | 1 |

| MOV        | @Ri, direct       | <@Ri> = direct                              | 2 | 2 |

| MOV        | @Ri, #data        | <@Ri> = #data                               | 2 | 1 |

| MOV        | DPTR, #data16     | DPTR = #data16                              | 3 | 2 |

| MOVC       | A, @A+DPTR        | A = code memory[A+DPTR]                     | 1 | 2 |

| MOVC       | A, @A+PC          | A = code memory[A+PC]                       | 1 | 2 |

| MOVX       | A, @Ri            | A = external memory[Ri] (8-bits address)    | 1 | 2 |

| MOVX       |                   |                                             | 1 | 2 |

|            | A, @DPTR          | A = external memory[DPTR] (16-bits address) |   |   |

| MOVX       | @Ri, A            | external memory[Ri] = A (8-bits address)    | 1 | 2 |

| MOVX       | @DPTR, A          | external memory[DPTR] = A (16-bits address) | 1 | 2 |

| PUSH       | direct            | INC SP: MOV "@'SP', < direct >              | 2 | 2 |

| POP        | direct            | MOV < direct >, "@SP": DEC SP               | 2 | 2 |

| XCH        | A,Rn              | ACC and < Rn > exchange data                | 1 | 1 |

| XCH        | A, direct         | ACC and < direct > exchange data            | 2 | 1 |

| XCH        | A, @Ri            | ACC and < Ri > exchange data                | 1 | 1 |

| XCHD       | A, @Ri            | ACC and @Ri exchange low nibbles            | 1 | 1 |

| Boolean In | structions        |                                             |   |   |

| CLR        | С                 | C = 0                                       | 1 | 1 |

| CLR        | bit               | bit = 0                                     | 2 | 1 |

| SETB       | С                 | C = 1                                       | 1 | 1 |

| SETB       | bit               | bit = 1                                     | 2 | 1 |

| CPL        | C                 | C = /C                                      | 1 | 1 |

| CPL        | bit               | bit = /bit                                  | 2 | 1 |

| ANL        | C, bit            | C = C .AND. bit                             | 2 | 2 |

| ANL        | C, /bit           | C = C .AND. /bit                            | 2 | 2 |

| ORL        | C, bit            | C = C .OR. bit                              | 2 | 2 |

| ORL        | C, /bit           | C = C .OR. bit                              | 2 | 2 |

|            | ,                 |                                             |   |   |

| MOV        | C, bit            | C = bit                                     | 2 | 1 |

| MOV        | bit, C            | bit = C                                     | 2 | 2 |

| JC         | rel               | Jump if C= 1                                | 2 | 2 |

| JNC        | rel               | Jump if C= 0                                | 2 | 2 |

| JB         | bit, rel          | Jump if bit = 1                             | 3 | 2 |

| JNB        | bit, rel          | Jump if bit = 0                             | 3 | 2 |

| JBC        | bit, rel          | Jump if C = 1                               | 3 | 2 |

| Jump Instr |                   |                                             |   |   |

| ACALL      | addr11            | Call Subroutine only at 2k bytes Address    | 2 | 2 |

| LCALL      | addr16            | Call Subroutine in max 64K bytes Address    | 3 | 2 |

| RET        |                   | Return from subroutine                      | 1 | 2 |

| RETI       |                   | Return from interrupt                       | 1 | 2 |

| AJMP       | addr11            | Jump only at 2k bytes Address               | 2 | 2 |

| LJMP       | addr16            | Jump to max 64K bytes Address               | 3 | 2 |

| SJMP       | rel               | Jump on at 256 bytes                        | 2 | 2 |

| JMP        | @A+DPTR           | Jump to A+ DPTR                             | 1 | 2 |

| JZ         | rel               | Jump if A = 0                               | 2 | 2 |

| JNZ        | rel               | Jump if $A \neq 0$                          | 2 | 2 |

| CJNE       |                   |                                             |   |   |

|            | A, direct,rel     | Jump if A ≠ < direct >                      | 3 | 2 |

| CJNZ       | A, #data,rel      | Jump if A ≠ < #data >                       | 3 | 2 |

| CJNZ       | Rn, #data,rel     | Jump if Rn ≠ < #data >                      | 3 | 2 |

| CJNZ       | @Ri, #data,rel    | Jump if @Ri ≠ < #data >                     | 3 | 2 |

| DJNZ       | Rn, rel           | Decrement and jump if Rn not zero           | 2 | 2 |

| DJNZ       | direct, rel       | Decrement and jump if direct not zero       | 3 | 2 |

| NOP        |                   | No Operation                                | 1 | 1 |

|            |                   |                                             |   |   |

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

## 3 Memory Structure

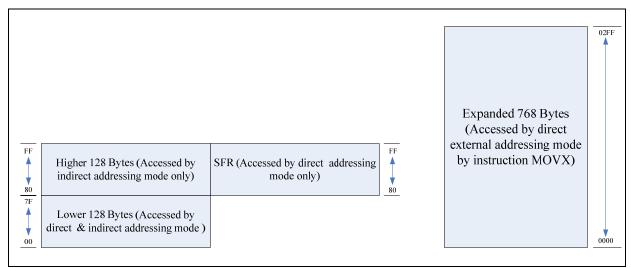

The SM59D03G2 manipulates operands in three memory spaces. They are (1) 256 bytes standard RAM, (2) 768 bytes auxiliary RAM, and (3) 8K bytes embedded Flash as program memory.

## 3.1 Program Memory

As described in Section 1, the SM59D03G2 has 8K bytes on-chip Flash memory which is used as general program memory, the address range for the 8K bytes is 0000h to 1FFFh.

The feature of FLASH memory is shown as following:

• **READ:** byte-wise

• **WRITE:** byte-wise within 30us (previously erased by a chip erase).

• ERASE:

Full Erase (8+4K bytes) within 200 ms.

Erased bytes contain FFH

● **Endurance :** 100K erase and write cycles each byte at TA=25°C

• **Retention**: 10 years

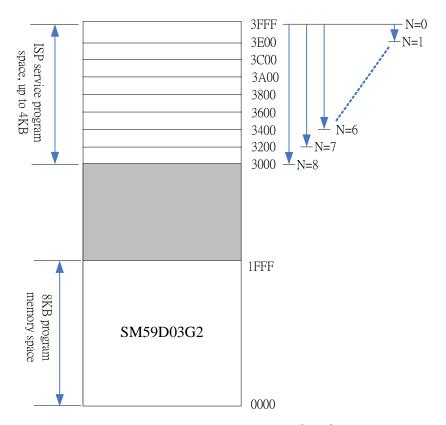

If we do ISP or IAP, there are up to 4K bytes of specific ISP service program. The address range is 3000h to 3FFFh. The ISP service program size can be partitioned as N blocks of 512 bytes (N=0 to 8). When N=0, there will be no ISP service program space available, the total 8K bytes memory are used as program memory. When N=1, the Flash from 3E00h to 3FFFh is reserved for ISP service program. When N=2, the Flash from 3C00h to 3FFFh is reserved for ISP service program... Value N is set in the information block. Fig 3.1 shows the ISP Flash reservation with different values of N.

The unused Flash on 4K bytes ISP service Program area can be the memory space for the EEPROM application through the ISP

Fig 3-1: Flash segmentation for ISP

The SM59D03G2 provides code protect function on the writer. The user can select protect or unprotect by writer. If protection is selected, users can't read the program from the writer. When the user runs in the external program mode (EA = 0) and protect bit is set and the MOVC instruction will be disable by hardware. The only way to change the protection bit back is to erase the entire Flash.

## 3.2 Data Memory

The SM59D03G2 has 256 + 768 bytes on-chip RAM, the 256 bytes are the same as general 8052 internal memory structure while the expanded 768 bytes on-chip RAM can be accessed by external memory addressing method( by instruction MOVX).

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

Fig. 3-2: RAM architecture

## 3.2.1 Data Memory - Lower 128 byte (\$00h to \$7Fh)

Data Memory 00h to FFh is the same as defined in 8052. The address 00h to 7Fh can be accessed by both direct and indirect addressing modes. Address 00h to 1Fh is register area. Address 20h to 2Fh is memory bit area, and address 30h to 7Fh is for general memory area.

## 3.2.2 Data Memory - Higher 128 byte (\$80h to \$FFh)

The address 80h to FFh can only be accessed by indirect addressing mode. It is data area.

## 3.2.3 Data Memory - Expanded 768 bytes (\$0000h to \$02FFh)

Address 0000h to 02FFh is the on-chip expanded RAM area, totally 768 bytes. This area can be accessed by external direct addressing mode with instruction MOVX.

If the address of instruction MOVX @DPTR is larger than 02FFh, then the SM59D03G2 will generate the external memory control signal automatically. The bit 1 (OME) of SFR BFh (SCONF) can enable or disable this expanded 768 byte RAM. The default setting of OME bit is 0 (disable).

## 4 CPU Engine

The SM59D03G2 CPU engine allows fetching instructions from the program memory, and accessing data with RAM or SFR. Here the SFR in the CPU engine is explained.

| Mnemonic | Description         | Direct | Bit 7 | Bit 6    | Bit 5   | Bit 4            | Bit 3   | Bit 2 | Bit 1 | Bit 0 | RESET |

|----------|---------------------|--------|-------|----------|---------|------------------|---------|-------|-------|-------|-------|

|          |                     |        |       | 80       | 51 Core |                  |         |       |       |       |       |

| ACC      | Accumulator         | E0h    | ACC.7 | ACC.6    | ACC.5   | ACC.4            | ACC.3   | ACC.2 | ACC.1 | ACC.0 | 00h   |

| В        | B register          | F0h    | B.7   | B.6      | B.5     | B.4              | B.3     | B.2   | B.1   | B.0   | 00h   |

| PSW      | Program status word | D0h    | CY    | AC       | F0      | RS[              | RS[1:0] |       | F1    | Р     | 00h   |

| SP       | Stack Pointer       | 81h    |       | SP[7:0]  |         |                  |         |       |       |       |       |

| DPL      | Data pointer low 0  | 82h    |       | DPL[7:0] |         |                  |         |       |       |       |       |

| DPH      | Data pointer high 0 | 83h    |       |          |         | DPH              | I[7:0]  |       |       |       | 00h   |

| DPL1     | Data pointer low 1  | 84h    |       |          |         | DPL <sup>2</sup> | 1[7:0]  |       |       |       | 00h   |

| DPH1     | Data pointer high 1 | 85h    |       |          |         | DPH              | 1[7:0]  |       |       |       | 00h   |

| DPS      | Data pointer select | 86h    | -     | -        | -       | -                | -       | -     | -     | DPS.0 |       |

| SCONF    | System control flag | BFh    | -     | -        | -       | -                | -       | ISPE  | OME   | ALEI  | 00h   |

### 4.1 Accumulator

ACC is the Accumulator register. Most instructions use the accumulator to hold the operand.

| Mnemonic: ACC |       |       |       |       |       |       |       | Address | s: E0h |

|---------------|-------|-------|-------|-------|-------|-------|-------|---------|--------|

|               | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0       | Reset  |

|               | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0   | 00h    |

ACC[7:0]: The A (or ACC) register is the standard 8052 accumulator.

# 4.2 B Register

The B register is used during multiply and divide instructions. It can also be used as a scratch pad register to hold temporary data.

| Mnemo | onic: B |     |     |     |     |     | Addres | s: F0h |

|-------|---------|-----|-----|-----|-----|-----|--------|--------|

| 7     | 6       | 5   | 4   | 3   | 2   | 1   | 0      | Reset  |

| B.7   | B.6     | B.5 | B.4 | B.3 | B.2 | B.1 | B.0    | 00h    |

B[7:0]: The B register is the standard 8052 register that serves as a second accumulator.

## 4.3 Program Status Word

| Mnemo | onic: PS | W  |         |     |    |    | Address | s: D0h |  |

|-------|----------|----|---------|-----|----|----|---------|--------|--|

| 7     | 6        | 5  | 4       | 4 3 |    | 1  | 0 Reset |        |  |

| CY    | AC       | F0 | RS[1:0] |     | OV | F1 | Р       | 00h    |  |

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

CY: Carry flag.

AC: Auxiliary Carry flag for BCD operations.

F0: General purpose Flag 0 available for user.

RS[1:0]: Register bank select, used to select working register bank.

| RS[1:0] | Bank     | Location  |

|---------|----------|-----------|

|         | Selected |           |

| 00      | Bank 0   | 00h – 07h |

| 01      | Bank 1   | 08h – 0Fh |

| 10      | Bank 2   | 10h – 17h |

| 11      | Bank 3   | 18h – 1Fh |

OV: Overflow flag.

F1: General purpose Flag 1 available for user.

P: Parity flag, affected by hardware to indicate odd/even number of "one" bits in the Accumulator, i.e. even parity.

### 4.4 Stack Pointer

The stack pointer is a 1-byte register initialized to 07h after reset. This register is incremented before PUSH and CALL instructions, causing the stack to begin at location 08h.

| Mnem | onic: SP |   |    |       |   |   | Addre | ss: 81h |

|------|----------|---|----|-------|---|---|-------|---------|

| 7    | 6        | 5 | 4  | 3     | 2 | 1 | 0     | Reset   |

|      |          |   | SP | [7:0] |   |   |       | 07h     |

SP[7:0]: The Stack Pointer stores the Scratchpad RAM address where the stack begins. In other words, it always points to the top of the stack.

#### 4.5 Data Pointer

The data pointer (DPTR) is 2-bytes wide. The lower part is DPL, and the highest is DPH. It can be loaded as 2 byte register (MOV DPTR, #data16) or as two registers (ea. MOV DPL, #data8). It is generally used to access external code or data space (ea. MOVC A, @A+DPTR or MOV A, @DPTR respectively).

| Mnemo | onic: DP | L |     |        |   | Addres 2 1 0 |   |       |  |

|-------|----------|---|-----|--------|---|--------------|---|-------|--|

| 7     | 6        | 5 | 4   | 3      | 2 | 1            | 0 | Reset |  |

|       |          |   | DPI | L[7:0] |   |              |   | 00h   |  |

DPL[7:0]: Data pointer Low 0

| Mnemo | onic: DP | Η |     |        |   |   | Addre     | ss: 83h |  |  |  |

|-------|----------|---|-----|--------|---|---|-----------|---------|--|--|--|

| 7     | 6        | 5 | 4   | 3      | 2 | 1 | 1 0 Reset |         |  |  |  |

|       |          |   | DPI | H[7:0] |   |   |           | 00h     |  |  |  |

DPH[7:0]: Data pointer High 0

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

### 4.6 Data Pointer 1

The dual data pointer accelerates the moving of block data. The standard DPTR is a 16-bit register that is used to address external memory or peripherals. In the SM59D03G2, the standard data pointer is called DPTR, the second data pointer is called DPTR1. The data pointer select bit chooses the active pointer. The data pointer select bit is located in the LSB of DPS register (DPS.0).

The user switches between pointers by toggling the LSB of DPS register. All DPTR-related instructions use the currently selected DPTR for any activity.

| Mnemo | onic: DP | L1 |     |         |   |   | Addres | ss: 84h |

|-------|----------|----|-----|---------|---|---|--------|---------|

| 7     | 6        | 5  | 4   | 3       | 2 | 1 | Reset  |         |

|       |          |    | DPL | .1[7:0] |   |   |        | 00h     |

DPL1[7:0]: Data pointer Low 1

| Mnemo | onic: DP | H1 |     |         |   |   | Addre | ss: 85h |

|-------|----------|----|-----|---------|---|---|-------|---------|

| 7     | 6        | 5  | 4   | 3       | 2 | 1 | 0     | Reset   |

|       |          |    | DPH | 11[7:0] |   |   |       | 00h     |

DPH1[7:0]: Data pointer High 1

| Mnemo | onic: DP | S |   |   |   |   | Addres | s: 86h |

|-------|----------|---|---|---|---|---|--------|--------|

| 7     | 6        | 5 | 4 | 3 | 2 | 1 | 0      | Reset  |

| -     | -        | - | - | - | - | - | DPS.0  | 00h    |

DPS.0: Data Pointer select register.

DPS.0 = 1 is selected DPTR1.

## 4.7 System control flag

| Mnemonic: SCONF Address: B |   |   |   |   |      |     |      | s: BFh |

|----------------------------|---|---|---|---|------|-----|------|--------|

| 7                          | 6 | 5 | 4 | 3 | 2    | 1   | 0    | Reset  |

| -                          | - | - | - | - | ISPE | OME | ALEI | 00h    |

ISPE: ISP function enable bit.

ISPE = 1 is enable ISP function.

ISPE = 0 is disable ISP function.

OME: 768 bytes on-chip RAM enable bit.

OME = 1 is enable 768 bytes on-chip RAM.

OME = 0 is disable 768 bytes on-chip RAM.

ALEI: ALE output disable.

ALEI = 1 is disable ALE output.

ALEI = 0 is Enable ALE output.

#### 5 Port 0 – Port 4

Port 0 ~ Port 4 are the general purpose IO of this controller. Port 4[3:0] is available with 44-pin PLCC or QFP package only, not for 40-pin package. Most of the ports are multiplexed with the other outputs, e.g., Port 3[0] is also used as RXD in the UART application. Port0 is open-drain in the input and output high condition, so external pull-up resistors are required. As for the other ports, the pull-up resistors are built internally.

For general purpose applications, every pin can be assigned to either high or low independently because their SFRs are bit addressable as given below:

| Mnemo | onic: P0 |      |      |      |      |      | Addres | s: 80h |  |

|-------|----------|------|------|------|------|------|--------|--------|--|

| 7     | 6        | 5    | 4    | 3    | 2    | 1    | 0      | Reset  |  |

| P0.7  | P0.6     | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0   | FFh    |  |

P0.7~ 0: Port0[7] ~ Port0[0]

| Mnemo | onic: P1 |      |      |      |      |      | Addres | s: 90h |  |

|-------|----------|------|------|------|------|------|--------|--------|--|

| 7     | 6        | 5    | 4    | 3    | 2    | 1    | 0      | Reset  |  |

| P1.7  | P1.6     | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0   | FFh    |  |

P1.7~ 0: Port1[7] ~ Port1[0]

| Mnemo | onic: P2 |      |      |      |      |      | Addres | s: A0h |

|-------|----------|------|------|------|------|------|--------|--------|

| 7     | 6        | 5    | 4    | 3    | 2    | 1    | 0      | Reset  |

| P2.7  | P2.6     | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2.0   | FFh    |

P2.7~ 0: Port2[7] ~ Port2[0]

| Mnemonic: P3 Address: B0 |      |      |      |      |      |      |      |       |

|--------------------------|------|------|------|------|------|------|------|-------|

| 7                        | 6    | 5    | 4    | 3    | 2    | 1    | 0    | Reset |

| P3.7                     | P3.6 | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3.0 | FFh   |

P3.7~ 0: Port3[7] ~ Port3[0]

| Mnemo | Address | s: D8h |   |      |      |      |      |       |

|-------|---------|--------|---|------|------|------|------|-------|

| 7     | 6       | 5      | 4 | 3    | 2    | 1    | 0    | Reset |

| Х     | Х       | Х      | Х | P4.3 | P4.2 | P4.1 | P4.0 | xFh   |

P4.3~ 0: Port4[3] ~ Port4[0]

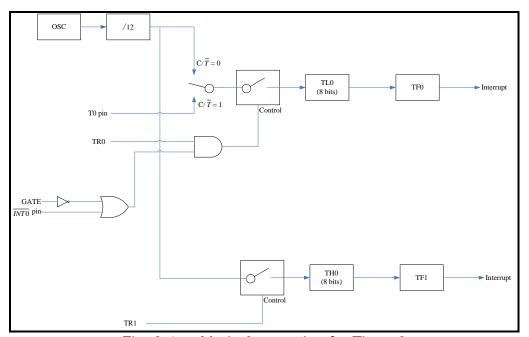

#### 6 Timer 0 and Timer 1

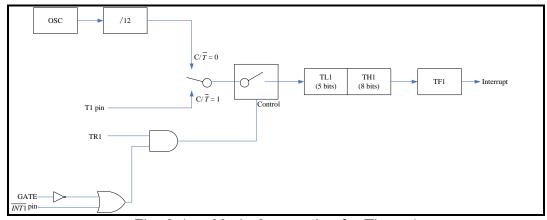

These timer and counter functions are presented in the same module. The "timer" or "counter" function is selected by the control bits  $C/\overline{T}$  in SFR TMOD. Timer 0 and Timer 1 have four operation modes, which are selected by bit-pairs (M1, M0) in SFR TMOD. Mode 0, 1, and 2 are the same for both timer and counters. Mode 3 is different. The four operating modes are described below:

#### 6.1 Mode 0

In this mode, the timer register is configured as a 13-bit register. Take Timer 1 as the example, as the counter rolls over from all 1s to all 0s, it sets the Timer 1 interrupt flag TF1. The counter input is enabled by the timer when TR1 = 1 and either GATE = 0 or  $\overline{INT1}$  = 1, here setting GATE = 1 allows the timer to be controlled by external input  $\overline{INT1}$ , to facilitate pulse width measurements. TR1 is a control bit in the SFR TCON and GATE is in TMOD.

The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL1. The upper 3 bits of TL1 are indeterminate and should be ignored. Setting the run flag (TR1) does not clear the registers.

Mode 0 operation is the same for Timer 0 and Timer 1. So substituting TR0, TF0 and  $\mathit{INT0}$  for the corresponding Timer 1 signals in the last paragraph, we can know the operation of Mode 0 for Timer 0. But there are two different GATE bits, one is for Timer 1(TMOD.7) and the other one is for Timer 0 (TMOD.3).

Fig. 6-1: Mode 0 operation for Timer 1

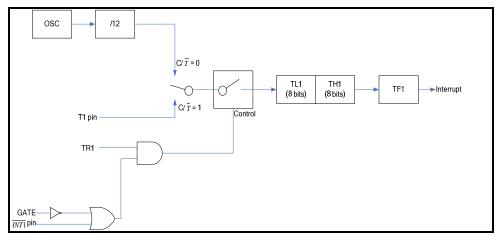

### 6.2 Mode 1

Mode 1 is the same as Mode 0, except that the timer register runs with all 16 bits.

Fig. 6-2: Mode 1 operation for Timer 1

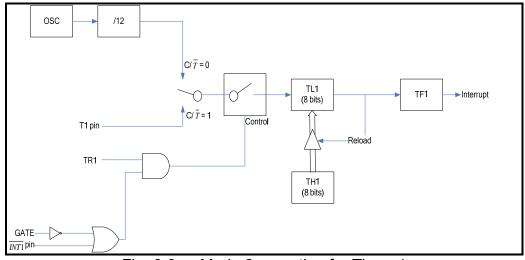

### 6.3 Mode 2

For Timer 1, Mode 2 configures the timer register as an 8-bit counter (TL1) with automatic reload. Overflow from TL1 not only sets TF1, but also reloads TL1 with the contents of TH1, which is preset by software. The reload operation leaves TH1 unchanged. Timer 0 Mode 2 operation is also the same.

Fig. 6-3: Mode 2 operation for Timer 1

### 6.4 Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 takes TL0 and TH0 as two separate counters. TL0 uses the Timer 0 control bits:  $C/\overline{T}$ , GATE, TR0,  $\overline{INT0}$ , and TF0. TH0 is locked into a timer function to count machine cycles and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer or counter. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

Fig. 6-4: Mode 3 operation for Timer 0

## 6.5 SFR description

| Mnemonic | Description              | Direct | Bit 7 | Bit 6            | Bit 5      | Bit 4 | Bit 3 | Bit 2            | Bit 1 | Bit 0 | RESET |

|----------|--------------------------|--------|-------|------------------|------------|-------|-------|------------------|-------|-------|-------|

|          |                          |        |       | Time             | er 0 and 1 |       |       |                  |       |       |       |

| TL0      | Timer 0 , low byte       | 8Ah    |       | TL0[7:0]         |            |       |       |                  |       | 00h   |       |

| TH0      | Timer 0 , high byte      | 8Ch    |       | TH0[7:0]         |            |       |       |                  |       | 00h   |       |

| TL1      | Timer 1 , low byte       | 8Bh    |       | TL1[7:0]         |            |       |       |                  |       |       | 00h   |

| TH1      | Timer 1 , high byte      | 8Dh    |       | TH1[7:0]         |            |       |       |                  |       |       | 00h   |

| TMOD     | Timer Mode<br>Control    | 89h    | GATE  | $C/\overline{T}$ | M1         | MO    | GATE  | $C/\overline{T}$ | M1    | MO    | 00h   |

| TCON     | Timer/Counter<br>Control | 88h    | TF1   | TR1              | TF0        | TR0   | IE1   | IT1              | IE0   | IT0   | 00h   |

## 6.5.1 Timer/Counter Mode Control register (TMOD)

| Mnemonic: TMOD Address: |                  |      |    |      |                  |    |    |       |  |

|-------------------------|------------------|------|----|------|------------------|----|----|-------|--|

| 7                       | 6                | 5    | 4  | 3    | 2                | 1  | 0  | Reset |  |

| GATE                    | $C/\overline{T}$ | M1   | MO | GATE | $C/\overline{T}$ | M1 | M0 | 00h   |  |

|                         | Tim              | er 1 |    |      |                  |    |    |       |  |

GATE: If set, enables external gate control (pin  $\overline{\text{INT0}}$  or  $\overline{\text{INT1}}$  for Counter 0 or 1, respectively). When  $\overline{\text{INT0}}$  or  $\overline{\text{INT1}}$  is high, and TRx bit is set (see TCON register), a counter is incremented every falling edge on T0 or T1 input pin  $\overline{\text{C/T}}$ : Selects Timer or Counter operation. When set to 1, a Counter operation is performed, when cleared to 0, the corresponding register will function as a Timer.

M[1:0]: Selects mode for Timer/Counter 0 or Timer/Counter 1.

| M1 | MO | Mode  | Function                                                                                                                                                                              |

|----|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Mode0 | 13-bit Counter/Timer, with 5 lower bits in TL0 or                                                                                                                                     |

|    |    |       | TL1 register and 8 bits in TH0 or TH1 register                                                                                                                                        |

|    |    |       | (for Timer 0 and Timer 1, respectively). The 3                                                                                                                                        |

|    |    |       | high order bits of TL0 and TL1 are hold at zero.                                                                                                                                      |

| 0  | 1  | Mode1 | 16-bit Counter/Timer.                                                                                                                                                                 |

| 1  | 0  | Mode2 | 8 -bit auto-reload Counter/Timer. The reload value is kept in TH0 or TH1, while TL0 or TL1 is incremented every machine cycle. When TLx overflows, a value from THx is copied to TLx. |

| 1  | 1  | Mode3 | If Timer 1 M1 and M0 bits are set to 1, Timer 1 stops. If Timer 0 M1 and M0 bits are set to 1, Timer 0 acts as two independent 8 bit Timers / Counters.                               |

## 6.5.2 Timer/Counter Control register (TCON)

| Mnemo | Addres | s: 88h |     |     |     |     |     |       |

|-------|--------|--------|-----|-----|-----|-----|-----|-------|

| 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   | Reset |

| TF1   | TR1    | TF0    | TR0 | IE1 | IT1 | IE0 | IT0 | 00h   |

- TF1: Timer 1 overflow flag set by hardware when Timer 1 overflows. This flag can be cleared by software and is automatically cleared when interrupt is processed.

- TR1: Timer 1 Run control bit. If cleared, Timer 1 stops.

- TF0: Timer 0 overflow flag set by hardware when Timer 0 overflows. This flag can be cleared by software and is automatically cleared when interrupt is processed.

- TR0: Timer 0 Run control bit. If cleared, Timer 0 stops.

- IE1: Interrupt 1 edge flag. Set by hardware, when falling edge on external pin INT1 is observed. Cleared when interrupt is processed.

- IT1: Interrupt 1 type control bit. Selects falling edge or low level on input pin to cause interrupt.

- IE0: Interrupt 0 edge flag. Set by hardware, when falling edge on external pin INT0 is observed. Cleared when interrupt is processed.

- ITO: Interrupt 0 type control bit. Selects falling edge or low level on input pin to cause interrupt.

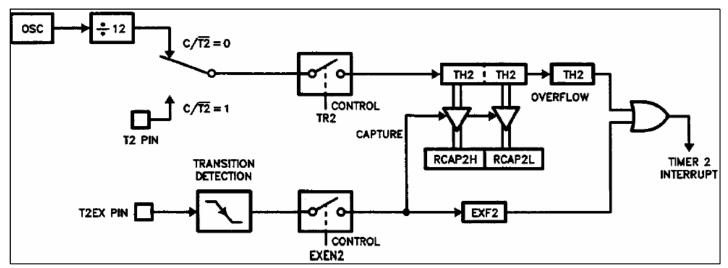

### 7 Timer 2

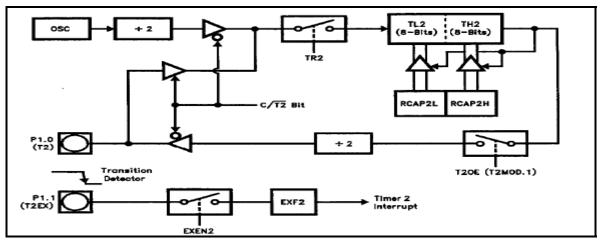

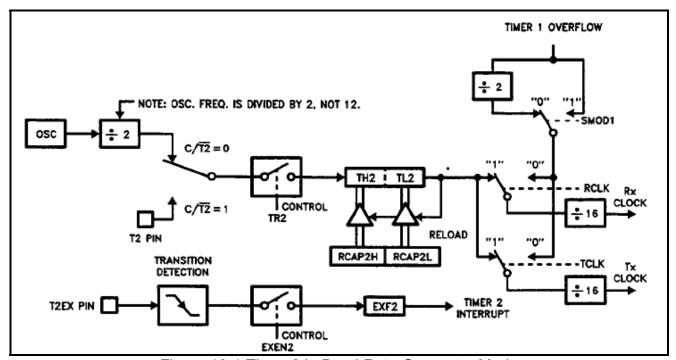

Timer 2 is a 16-bit timer/counter which can operate either as a timer or an event counter. This is selectable by bit  $C/\overline{T2}$  in the SFR T2CON. It has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON as shown below.

Timer 2 consists of two 8-bit registers, TH2 and TL2. In the timer function, the TL2 register is incremented every machine cycle, thus one can think of it as counting machine cycles. Since a machine cycle consists of a 12-clock period in 12T, the count rate is 1/12 of the oscillator clock frequency. In 6T, it is 1/6.

In the counter function, the register is incremented in response to every 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (24 clock periods in 12T) to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency in 12T mode or 1/12 in 6T mode. To ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

Table 7-1: Timer 2 Operating Modes

| RCLK+TCLK | CP/RL2 | TR2 | MODE                |

|-----------|--------|-----|---------------------|

| 0         | 0      | 1   | 16-bit Auto-reload  |

| 0         | 0 1    |     | 16-bit Capture      |

| 1         | 1 X    |     | Baud rate Generator |

| X         | X      | 0   | Off                 |

## 7.1 Capture mode

In the capture mode, there are two options selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON. This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt.

Figure 7-1: Timer 2 in capture mode

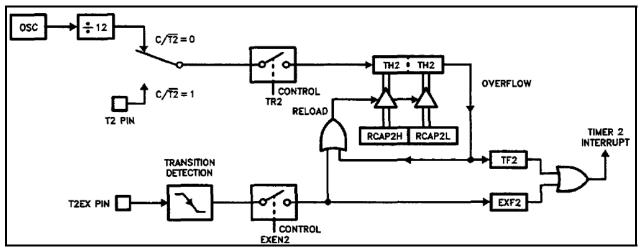

## 7.2 Auto-reload (Up or Down Counter)

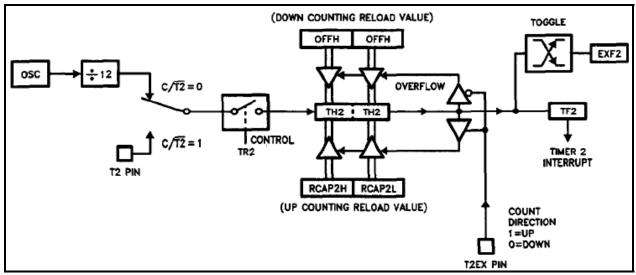

Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by a bit named DCEN (Down Counter Enable) located in the SFR T2MOD. Upon reset, the DCEN bit is set to 0 so that Timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 7-2 shows Timer 2 automatically counting up when DCEN = 0. In this mode there are two options selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to FFFFh and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with the 16-bit value in RCAP2H and RCAP2L. The values in RCAP2H and RCAP2L are preset by software. If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transition also sets the EXF2 bit. Both the TF2 and EXF2 bits can generate an interrupt if enabled.

Setting the DCEN bit enables Timer 2 to count up or down as shown in Figure 7-3. In this mode the T2EX pin controls the direction of count. A logic 1 at T2EX makes Timer 2 count up. The timer will overflow at FFFFh and set the TF2 bit. This overflow also causes the 16-bit value in RCAP2H and RCAP2L to be reloaded into the timer registers, TH2 and TL2, respectively.

A logic 0 at T2EX makes Timer 2 count down. Now the timer underflows when TH2 and TL2 are equal to the values stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes FFFFH to be reloaded into the timer registers.

The EXF2 bit toggles whenever Timer 2 overflows or underflows. This bit can be used as a 17th bit of resolution if desired. In this operating mode, EXF2 does not flag an interrupt.

Figure 7-2: Timer 2 in auto reload mode (DCEN=0)

Figure 7-3: Timer 2 in auto reload mode (DCEN=1)

## 7.3 Programmable clock out

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides begin a regular I/O pin, has two alternate functions. It can be programmed (1) to input the external clock for Timer/Counter 2 or (2) to output a 50% duty cycle clock. An example is that the clock output ranges from 61Hz to 4MHz at a 16MHz oscillator frequency if in 12T mode.

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (T2CON.1) must be cleared and bit T2OE(T2MOD.1) must be set. Bit TR2 (T2CON.2) starts and stops the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

Clock-Out Frequency =

$$\frac{\text{Oscillator Frequency}}{4 \times (65536 - RCAP2H, RCAP2L)}$$

In the clock-out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when Timer 2 is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and clock-out frequencies can not be determined independently from one another since they both use RCAP2H and RCAP2L.

Figure 7-4: Timer 2 in clock-out mode

## 7.4 SFR description

| Mnemonic | Description                       | Direct | Bit 7 | Bit 6       | Bit 5      | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0                           | RES<br>ET |

|----------|-----------------------------------|--------|-------|-------------|------------|-------|--------|-------|-------|---------------------------------|-----------|

|          |                                   |        |       | Time        | er 0 and 1 |       |        |       |       |                                 | •         |

| TL2      | Timer 2 , low byte                | CCh    |       |             |            | TL    | 2[7:0] |       |       |                                 | 00h       |

| TH2      | Timer 2 , high byte               | CDh    |       | TH2[7:0]    |            |       |        |       |       |                                 | 00h       |

| RCAP2L   | Reload and capture data low byte  | CAh    |       | RCAP2L[7:0] |            |       |        |       |       |                                 | 00h       |

| RCAP2H   | Reload and capture data high byte | CBh    |       | RCAP2H[7:0] |            |       |        |       |       |                                 | 00h       |

| T2MOD    | Timer 2 mode                      | C9h    | -     | -           | -          | -     | -      | -     | T2OE  | DCEN                            | x0h       |

| T2CON    | Timer 2 control register          | C8h    | TF2   | EXF2        | RCLK       | TCLK  | EXEN2  | TR2   | C/T2  | $\frac{\text{CP/}}{\text{RL2}}$ | 00h       |

| Mnemonic: T2CON Address: C8 |     |      |      |      |       |     |      |        |       |  |  |

|-----------------------------|-----|------|------|------|-------|-----|------|--------|-------|--|--|

|                             | 7   | 6    | 5    | 4    | 3     | 2   | 1    | 0      | Reset |  |  |

|                             | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 | 00h   |  |  |

- TF2: Timer 2 overflow flag is set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either RCLK = 1 or TCLK = 1.

- EXF2: Timer 2 external flag is set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down counter mode (DCEN = 1).

- RCLK: Receive clock enable. When set, causes the serial port to use Timer 2 overflow pluses for its receive clock in serial port Modes 1 and 3. RCLK = 0 causes Timer 1 overflows to be used for the receive clock.

- TCLK: Transmit clock enable. When set, causes the serial port to use Timer 2 overflow pulses for it's transmit clock in serial port Modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.

- EXEN2: Timer 2 external enable. When set, allows a capture or reload to occur as a result of a negative transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2 = 0 causes Timer 2 to ignore events at T2EX.

- TR2: Start/Stop control for Timer 2. TR2 = 1 starts the timer.

- $C/\overline{T2}$ : Timer or counter select for Timer 2.  $C/\overline{T2} = 0$  for timer function.  $C/\overline{T2} = 1$  for external event counter (falling edge triggered).

- CP/RL2: Capture/Reload select. CP/RL2 = 1 causes captures to occur on negative transitions at T2EX if EXEN2 = 1. CP/RL2 = 0 causes automatic reloads to occur when Timer 2 overflows or negative transitions occur at T2EX when EXEN2 = 1. When either RCLK or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow.

| Mnemonic: T2MOD Address |   |   |   |   |   |      |      |       |  |  |

|-------------------------|---|---|---|---|---|------|------|-------|--|--|

| 7                       | 6 | 5 | 4 | 3 | 2 | 1    | 0    | Reset |  |  |

| -                       | - | - | - | - | - | T2OE | DCEN | x0h   |  |  |

T2OE: Timer 2 Output Enable bit.

DCEN: When set, this bit allows Timer 2 to be configured as an up/down counter.

## 8 Watchdog timer

The watchdog timer is an 8-bit counter that is incremented once every WDTCLK clock cycle. After an external reset, the watchdog timer is disabled and all registers are set to zero.

When SM59D03G2 is reset, it will read internal setting for the bit WDTEN.When the WDTEN is selected ,the watchdog function will enable. The WDTM[2:0] is control WDTCLK. User can select WDTEN on the writer.

Table 8-1 Watchdog Timer Overflow Period:

| WDTM[2:0]       | 000    | 001    | 010    | 011     | 100     | 101     | 110      | 111      |

|-----------------|--------|--------|--------|---------|---------|---------|----------|----------|

| OverFlow Period | 1.58ms | 3.15ms | 6.30ms | 12.60ms | 25.12ms | 50.41ms | 100.82ms | 201.65ms |

The watchdog timer will reset the system after 256 WDTCLK is reached. Once the watchdog is started it cannot be stopped. To enable the WDT is done by setting 1 to the bit 7 (WDTE) of WDTC. After WDTE set to 1, the 16-bit counter starts to count. It will generate a reset signal when overflows. The WDTE bit will be cleared to 0 automatically when SM59D04G2 been reset, either hardware reset or WDT reset

To reset the WDT is done by setting 1 to the CLEAR bit of WDTC before the counter overflow. This will clear the content of the 16-bit counter and let the counter re-start to count from the beginning.

The SFR WDTK[7:0] must be set first. The first value set to it is 1Eh, then the next value is E1h.

| Mnemonic       | Description                     | Direct | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | RESET |

|----------------|---------------------------------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|

| Watchdog Timer |                                 |        |       |           |       |       |       |       |       |       |       |

| WDTC           | Watchdog timer control register | 8Eh    | WDTE  | -         | CLEAR | -     | -     | WDTM2 | WDTM1 | WDTM0 | 00H   |

| WDTK           | Watchdog timer refresh key      | 8Fh    |       | WDTK[7:0] |       |       |       |       |       |       | 00H   |

| Mnemo | Addres | s: 8Eh |   |   |       |       |       |       |

|-------|--------|--------|---|---|-------|-------|-------|-------|

| 7     | 6      | 5      | 4 | 3 | 2     | 1     | 0     | Reset |

| WDTE  | -      | CLEAR  | - | - | WDTM2 | WDTM1 | WDTM0 | 00H   |

WDTM[2:0]: Watchdog timer over flow period setting.

WDTE: Watchdog timer Enable.

WDTE=0: Disable WDT function either the WDTEN was setting on

the Writer •

WDTE=1: Enable WDT function when the WDTEN was setting on

the Writer •

This bit will be cleared to 0 automatically when MCU been reset,

either hardware reset or WDT reset •

CLEAR Setting this bit the Watchdog timer counter clear and re-start to count

from the Beginning •

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

| Mnemo | onic: WE  | )TK |   |   |   |   | Addres | ss: 8Fh |

|-------|-----------|-----|---|---|---|---|--------|---------|

| 7     | 6         | 5   | 4 | 3 | 2 | 1 | 0      | Reset   |

|       | WDTK[7:0] |     |   |   |   |   | 00h    |         |

WDTK: Watchdog timer refresh key.

A programmer must set it to 1Eh first, then E1h next. After these, the above SFR WDTC can be set.

## 9 ISP (In-System Programming)

The SM59D03G2 can perform ISP or In-Application Programming (IAP) function by putting the ISP service code into the assigned ISP code area as shown in Table 9-1. One page of Flash memory is 512bytes.

| SM59D03G2                |

|--------------------------|

| Table 9-1: ISP code area |

| SM59D03G2       |                                     |  |  |  |  |

|-----------------|-------------------------------------|--|--|--|--|

| Lock-bit number | ISP code area                       |  |  |  |  |

| 1               | 512 bytes (from \$3E00h to \$3FFF)  |  |  |  |  |

| 2               | 1K bytes (from \$3C00h to \$3FFF)   |  |  |  |  |

| 3               | 1.5K bytes (from \$3A00h to \$3FFF) |  |  |  |  |

| 4               | 2K bytes (from \$3800h to \$3FFF)   |  |  |  |  |

| 5               | 2.5K bytes (from \$3600h to \$3FFF) |  |  |  |  |

| 6               | 3K bytes (from \$3400h to \$3FFF)   |  |  |  |  |

| 7               | 3.5K bytes (from \$3200h to \$3FFF) |  |  |  |  |

| 8               | 4K bytes (from \$3000h to \$3FFF)   |  |  |  |  |

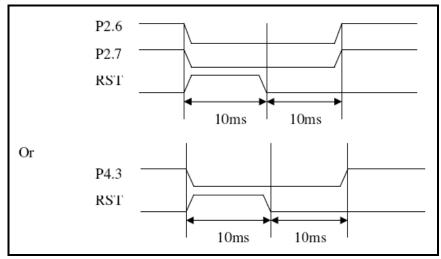

There are three ways to enter the ISP code area. They are

- (1) Blank first data: If the first Flash data is blank (data in address 0000h is FFh), the controller will read it after power on and after identifying it as blank, the program counter will go to the ISP code area.

- (2) Execute the "LJMP" instruction in the program as IAP function.

- (3) By hardware setting: After power on reset, if the hardware finds both Port2[6] and Port2[7] are tied low, or Port4[3] is low, then the program counter will go to the ISP code area. This is shown in Fig. 9-1.

Fig 9-1: ISP entering by hardware setting

## 9.1 SFR description

| Mnemonic | Description                 | Direct | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | RESET |

|----------|-----------------------------|--------|-------|-------------|-------|-------|-------|-------|-------|-------|-------|

|          | ISP                         |        |       |             |       |       |       |       |       |       |       |

| ISPC     | ISP control register        | F7h    | START | -           | -     | -     | -     | -     | ISPF1 | ISPF0 | 00h   |

| ISPFAH   | ISP Flash address high byte | F4h    |       | ISPFA[15:8] |       |       |       |       | 00h   |       |       |

| ISPFAL   | ISP Flash address low byte  | F5h    |       | ISPFA[7:0]  |       |       |       | 00h   |       |       |       |

| ISPFD    | ISP Flash data              | F6h    |       | ISPFD[7:0]  |       |       |       | 00h   |       |       |       |

| Mnem | onic: ISF | PFAH |       |         |   |   | Addre | ss: F4h |

|------|-----------|------|-------|---------|---|---|-------|---------|

| 7    | 6         | 5    | 4     | 3       | 2 | 1 | 0     | Reset   |

|      |           |      | ISPF/ | A[15:8] |   |   |       | 00h     |

|      |           |      |       |         |   |   |       |         |

| Mnem | onic: ISF | PFAL |       |         |   |   | Addre | ss: F5h |

| 7    | 6         | 5    | 4     | 3       | 2 | 1 | 0     | Reset   |

|      |           |      | -     |         |   |   |       | 1 10001 |

ISPFA[15:0]: The ISPFAH and ISPFAL provide the 16-bit Flash memory address for the ISP function. The Flash memory address should not include the ISP service program space address. If the Flash memory address indicated by ISPFAH and ISPFAL registers overlaps with the ISP service program space, the Flash write and page erase function will have no effect.

| Mnemo | onic: ISF  | PFD |   |   |   |   | Addres | ss: F6h |

|-------|------------|-----|---|---|---|---|--------|---------|

| 7     | 6          | 5   | 4 | 3 | 2 | 1 | 0      | Reset   |

|       | ISPFD[7:0] |     |   |   |   |   |        | 00h     |

ISPFD[7:0]: The ISPFD provide the 8-bits data for ISP function.

| Mnemo | onic: ISF | C |   |   |   |      | Addres             | ss: F7h |  |

|-------|-----------|---|---|---|---|------|--------------------|---------|--|

| 7     | 6         | 5 | 4 | 3 | 2 | 1    | 0                  | Reset   |  |

| START | -         | - | - | - | - | ISPF | <del>-</del> [1:0] | 00h     |  |

ISPF[1:0]: ISP function select.

| ISPF[1:0] | ISP function           |

|-----------|------------------------|

| 00        | Byte program           |

| 01        | Chip Protect           |

| 10        | Page erase( 512 Bytes) |

| 11        | Chip erase             |

START: ISP START bit.

START = 1 : Start ISP function which indicated by ISPF[1:0].

START = 0: no operation.

The START bit is read-only by default, software must write three specific values 55h, AAh and 55h sequentially to the ISPFD register to enable the START bit write attribute. That is:

8-Bits Micro-controller 8KB+ ISP Flash & 1KB RAM embedded

Ex: Open ISP function: MOV ISPFD,#055h MOV ISPFD,#0AAh MOV ISPFD,#055h

Any attempt to set START bit will not be allowed without procedure above. After the START bit set to 1, the SM59D03G2 hardware circuit will latch the address and data bus and hold the program counter until the START bit resets to 0 when the ISP function finished. The user does not need to check the START bit status by software method.

To perform byte program or page erase ISP function, the user needs to first specify the Flash address. When performing the page erase function, the SM59D03G2 will erase the entire page indicated by the Flash address in the ISPFAH register located within the page.

To perform chip erase ISP function, the SM59D03G2 will erase all the Flash program memory and data Flash memory except the ISP program space. Also, the SM59D03G2 will unprotect the Flash memory automatically if it has been protected by setting the information block bit LOCK=0. If LOCK is 0, all the Flash memory will be read all zeros.

The following example is to show how the ISP service program does byte program – to program data of #22h to the address of the \$1005h

MOV ISPFD, #055h MOV ISPFD, #0AAh

MOV ISPFD, #055h ; Open ISP function MOV SCONF, #04h ; enable ISP function

MOV ISPFAH, #10h ; Set Flash address high byte MOV ISPFAL, #05h ; Set Flash address low byte

MOV ISPFD, #22h ; Set Flash data to be programmed

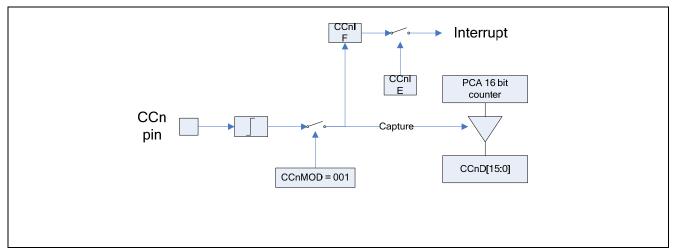

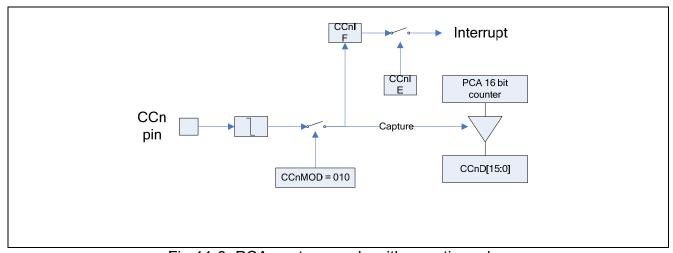

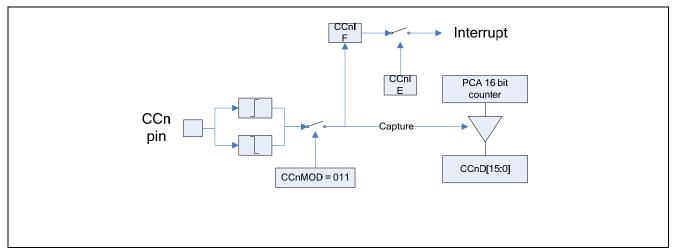

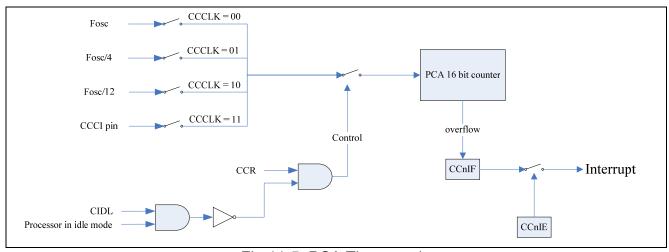

MOV ISPFC, #80h ; Start to program data of 22h to the Flash address of the \$1005h