表现。在1000年1000年,最终的是1000年,1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1000年的1

Digital Clocks

# MM5456, MM5457 Digital Alarm Clocks

## **General Description**

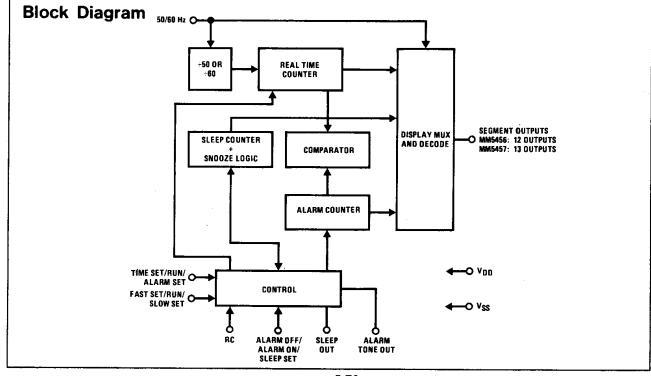

The MM5456, MM5457 digital alarm clock radio chips are monolithic MOS integrated circuits utilizing N-channel, low threshold, enhancement mode and ion-implanted depletion mode devices.

Each circuit contains all the logic necessary for a digital clock with sleep and alarm control and is intended for clock-radio applications.

Real time and alarm time are displayed in hours-minutes and sleep time is displayed in minutes when setting the sleep counter.

An alarm output is provided that "beeps" a 50% duty cycle, 700 Hz signal gated at 2 Hz rate when the alarm set time and the real time matches. A sleep output that provides a DC level is used to control the radio. It is activated with the alarm output or programmed via the sleep counter to turn OFF from 0 to 59 minutes after the sleep counter is set.

A snooze feature is provided for a 9-minute recurrence of the alarm after it has sounded.

Setting is done via the standard fast and slow set buttons when in the time set, alarm set or sleep set modes. These control inputs are TRI-STATE® inputs to reduce pin count.

The 50/60 Hz clock selects what segment data is on the outputs, i.e., a duplex LED display interface.

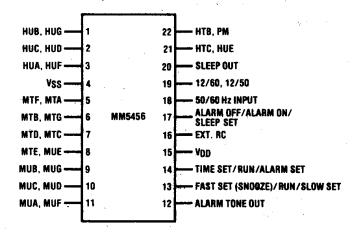

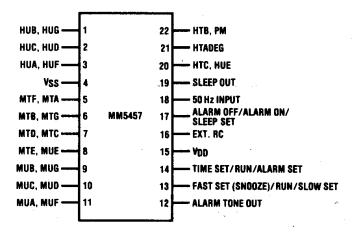

The MM5456, MM5457 are bonded in a 22-pin package. The MM5457 has a 24-hour/50 Hz option and the MM5456 has the 12-hour/50 Hz or 12-hour/60 Hz options.

### **Features**

- Duplex LED display drive

- Fast/slow set capability

- 24-hour alarm

- "Snooze" function (9 minutes)

- On-chip alarm oscillator

- Alarm tone output gated at a 2 Hz rate

- Power fail indication—entire display flashes at a 1 Hz rate

- Automatic power-on reset

- PM display indicator

- Presettable 59 minute sleep timer

## **Applications**

- Alarm clocks

- Desk clocks

- Clock radios

- Automobile clocks

- Stopwatches

- Industrial clocks

- Portable clocks

- Timers

Voltage at Any Pin Operating Temperature Storage Temperature V<sub>SS</sub> to V<sub>SS</sub> +12V -25°C to +70°C -65°C to +150°C

Lead Temperature (Soldering, 10 seconds)

300°C

## Electrical Characteristics Power supply voltage should not exceed a maximum of 12V under any circumstances.

TA within operating range, VDD = 7V to 11V

| PARAMETER                    | CONDITIONS                             | MIN                 | TYP                                           | MAX                  | UNITS      |

|------------------------------|----------------------------------------|---------------------|-----------------------------------------------|----------------------|------------|

| Power Supply Voltage         | Output Driving Display                 | 9                   |                                               | 11                   | V          |

|                              | Functional — Count Operating           | 7                   |                                               | 11                   | · V        |

| Power Supply Current         | No Output Loads                        |                     |                                               |                      |            |

|                              | V <sub>DD</sub> = 7V                   |                     |                                               | 4                    | mA         |

| •                            | V <sub>DD</sub> = 11V                  | *                   |                                               | 5                    | mA         |

| 50/60 Hz Input Frequency     |                                        | DC                  | 50/60                                         | 10k                  | Hz         |

| Logical "O", Low Level       | Į                                      | VSS                 | VSS                                           | VSS+0.5              | . <b>V</b> |

| Logical "1", High Level      |                                        | 0.7 V <sub>DD</sub> | ۷DD                                           | VDD                  | V          |

| Input Leakage                | VIN = VDD or VSS                       |                     |                                               | 10                   | μΑ         |

| All Other Input Voltages     |                                        |                     |                                               |                      |            |

| Logical "0", Low Level       |                                        | VSS                 | ٧ss                                           | V <sub>SS</sub> +0.5 | · V        |

| Logical "1", High Level      |                                        | V <sub>DD</sub> −1  | VDD                                           | VDD                  | V          |

| Power Failure Detect Voltage | (VDD Voltage)                          | 1 1                 |                                               | 5                    | · <b>V</b> |

| Alarm Output, Sleep Output   | V <sub>DD</sub> = 11V                  |                     |                                               |                      |            |

| Sourcing, Logical "1" High   | V <sub>OH</sub> = V <sub>DD</sub> - 1V | 1                   | ٠,                                            |                      | μΑ         |

| Sinking, Logical "0" Low     | VOL = VSS + 6V                         | 5                   |                                               |                      | mA         |

| Alarm Output Frequency       | $R = 68k, C = 0.1\mu F$                |                     | 700                                           |                      | Hz         |

| Segment Outputs (Except      | V <sub>DD</sub> = 10V                  |                     |                                               |                      |            |

| HTADEG)                      |                                        |                     |                                               |                      |            |

| Output Sink, Logical "0" Low | VOL = VSS + 2V                         | 20                  |                                               |                      | mA         |

| Leakage, Logical "1" High    | VOH = VDD                              |                     |                                               | 10                   | • µА       |

| Segment Output (HTADEG)      | V <sub>DD</sub> = 10V                  |                     | .*                                            |                      |            |

| Output Sink, Logical "0" Low | VOL = VSS + 2V                         | 40                  |                                               |                      | mA         |

| Leakage, Logical "1" High    | VOH = VDD                              |                     | , , <u>, , , , , , , , , , , , , , , , , </u> | 10                   | μΑ         |

# **Functional Description**

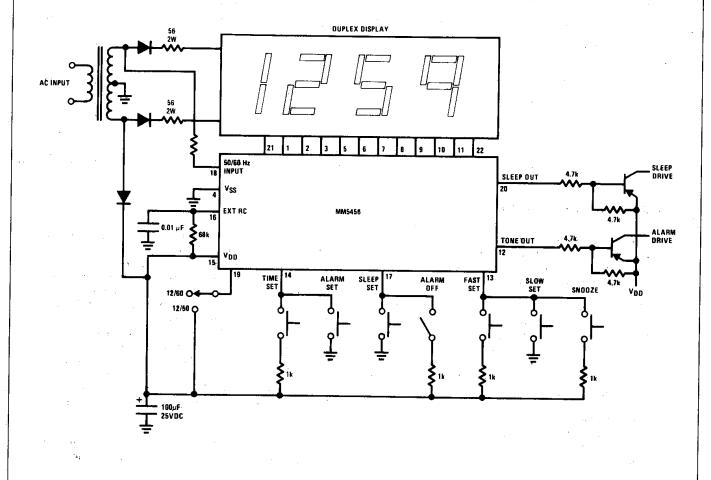

50 or 60 Hz Input: A shaping circuit is provided internally to square the 50 or 60 Hz input. This circuit allows use of a half sinewave input. A resistor in series must be used to limit current into the MOS device.

24-Hour/50 Hz, 12-Hour/60 Hz, 12-Hour/50 Hz (MM5456): When this input is connected to V<sub>DD</sub>, the display will be 12 hours with 50 Hz input. If left floating, the display will be 12 hours with 60 Hz input. (The MM5457 is internally bonded to select the 24-hour/50 Hz mode. The MM5456 selects the 12-hour/50 Hz or the 12-hour/60 Hz modes.)

Sleep Set/Alarm Enable/Alarm OFF: Whenever this input is connected to V<sub>SS</sub>, the sleep counters will display and be set to 59 minutes, if previously at 00 minutes. Fast set or slow set may be used to preset

time other than 59 minutes. When the alarm sounds, the snooze can be activated by momentarily connecting fast set pin to VDD. This will turn off the alarm for 9–10 minutes, after which the alarm will again be sounded. The snooze alarm feature may be repeatedly used for up to 59 minutes or until alarm OFF is activated by momentarily connecting this pin to VDD. When alarm OFF is activated, the alarm latch will reset and silence the alarm. The alarm will automatically sound again in 24 hours (or at a new alarm setting). If it is desired to silence the alarm for a day or more, the alarm OFF input should remain at VDD. The alarm can be enabled again by allowing the input to float.

External RC: The resistor and capacitor on this pin set the frequency of the alarm tone. The frequency is

# Functional Description (Continued)

nominally set to 1400 Hz in order to produce a 700 Hz (50% duty cycle) tone at the alarm output.

Time Set/Run/Alarm Set: This input must be activated in order to set the time counter and alarm counter. When connected to VDD, the time counter will be displayed and may be set with the fast-slow input. Upon release of fast and slow set, the time counter will be in a hold mode. If time set/alarm set is left floating, the time counter will be displayed, and the fast-slow input will be disabled (normal run mode). When this input is connected to VSS, the alarm counter will be displayed and may be set with the fast-slow input.

Fast Set/Run/Slow Set: Whenever this input is connected to VDD and time set or alarm set is activated, the appropriate counter will advance at a 60 Hz rate. If connected to VSS, the minutes counter will advance at 2 Hz with carry into the hours counter. If left floating, the clock will keep normal time. When connected to VDD and sleep set is activated, the sleep counter will count downward at a 10 Hz rate. If connected to VSS, the sleep counter will count downward at the slower rate; 2 Hz.

Alarm Output: This output remains at V<sub>DD</sub> when inactive. When the alarm latch becomes set, the alarm

700 Hz tone will be gated by a 20% duty cycle 2 Hz signal (i.e., the alarm tone will be ON for 100 ms and OFF for 400 ms). This output contains an internal pull-up to  $V_{DD}$  in order to turn OFF the external PNP transistor driver when the alarm is inactive.

Sleep Output: This output remains at VDD when inactive. When the alarm latch becomes set or the sleep counter is at other than 00 minutes, the sleep output will be ON. Snooze or alarm OFF function will disable this output simultaneously with alarm output if activated by alarm latch. Snooze function will disable this output at any time if activated by sleep counter being set. This output contains an internal pull-up to VDD in order to turn OFF the external PNP transistor switch when the output is inactive.

**Segment Outputs:** All segment outputs are open-drain devices with all sources common to VSS.

Power ON and Power Failure: After power ON or power fail, the display will flash at 1 Hz rate and time, alarm, and seconds counters will be reset to 0:00:00 (12:00:00). The alarm output will be held OFF also. The power fail can be reset by enabling time set allow.

# Typical Application

# Connection Diagrams (Dual-In-Line Packages, Top Views)

#### 12-Hour/50 or 60 Hz Clock

Order Number MM5456N See Package 22

#### 24-Hour/50 Hz Clock

Order Number MM5457N See Package 22