# V850/SA1

# **32-Bit Single-chip Microcontroller**

Hardware

μPD703014A μPD703014AY μPD703014B μPD703014BY μPD703015A μPD703015AY μPD703015B μPD703015BY μPD703015BY μPD703017A μPD703017A μPD70F3015B μPD70F3015BY μPD70F3017A μPD70F3017AY

Document No. U12768EJ4V1UD00 (4th edition) Date Published August 2005 N CP(K)

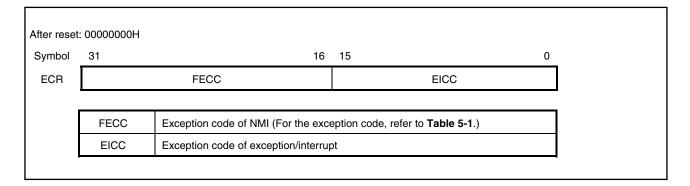

© NEC Electronics Corporation 1997, 2000, 2002 Printed in Japan [MEMO]

#### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

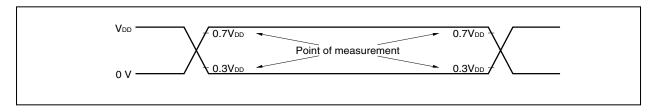

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### 6 INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/or other countries.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of August, 2005. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT] http://www.necel.com/en/support/support.html

| NEC Electronics America, Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782 | NEC Electronics (Europe) GmbH<br>Duesseldorf, Germany<br>Tel: 0211-65030 | <b>NEC Electronics Hong Kong Ltd.</b><br>Hong Kong<br>Tel: 2886-9318 |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                      | <ul> <li>Sucursal en España</li> </ul>                                   | NEC Electronics Hong Kong Ltd.                                       |

|                                                                                                      | Madrid, Spain                                                            | Seoul Branch                                                         |

|                                                                                                      | Tel: 091-504 27 87                                                       | Seoul, Korea<br>Tel: 02-558-3737                                     |

|                                                                                                      | <ul> <li>Succursale Française</li> </ul>                                 |                                                                      |

|                                                                                                      | Vélizy-Villacoublay, France<br>Tel: 01-30-675800                         | NEC Electronics Shanghai Ltd.<br>Shanghai, P.R. China                |

|                                                                                                      | • Filiale Italiana                                                       | Tel: 021-5888-5400                                                   |

|                                                                                                      | Milano, Italy<br>Tel: 02-66 75 41                                        | <b>NEC Electronics Taiwan Ltd.</b><br>Taipei, Taiwan                 |

|                                                                                                      | Branch The Netherlands                                                   | Tel: 02-2719-2377                                                    |

|                                                                                                      | Eindhoven, The Netherlands<br>Tel: 040-2654010                           | NEC Electronics Singapore Pte. Ltd.                                  |

Novena Square, Singapore Tel: 6253-8311

• United Kingdom Branch Milton Keynes, UK Tel: 01908-691-133

• Tyskland Filial Taeby, Sweden Tel: 08-63 87 200

J05.6

# Major Revisions in This Edition (1/2)

| Page       | Description                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout | Addition of <i>µ</i> PD703014B, 703014BY, 703015B, 703015BY, 70F3015B, and 70F3015BY<br>Deletion of <i>µ</i> PD703014AGC, 703014AYGC, 703015AGC, and 703015AYGC |

| p. 27      | Addition of Table 1-1 List of V850/SA1 Products                                                                                                                 |

| p. 28      | Addition of description to minimum instruction execution time in 1.2 Features                                                                                   |

| p. 30      | Deletion and addition of products in 1.4 Ordering Information                                                                                                   |

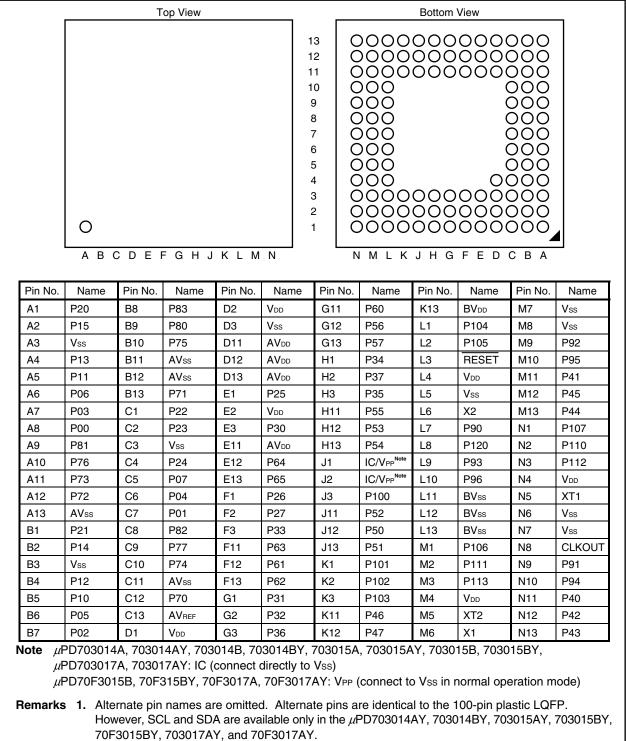

| p. 31      | Deletion and addition of products in 1.5 Pin Configuration                                                                                                      |

| p. 35      | Deletion of description in 1.6.2 (2) Bus control unit (BCU)                                                                                                     |

| p. 38      | Addition of Table 2-1 Pin I/O Buffer Power Supplies                                                                                                             |

| p. 43      | Modification of description in Table 2-2 Operating States of Pins in Each Operating Mode                                                                        |

| p. 49      | Modification of description in 2.3 (7) P60 to P65 (Port 6)                                                                                                      |

| p. 53      | Addition of 2.3 (13) CLKOUT (Clock out)                                                                                                                         |

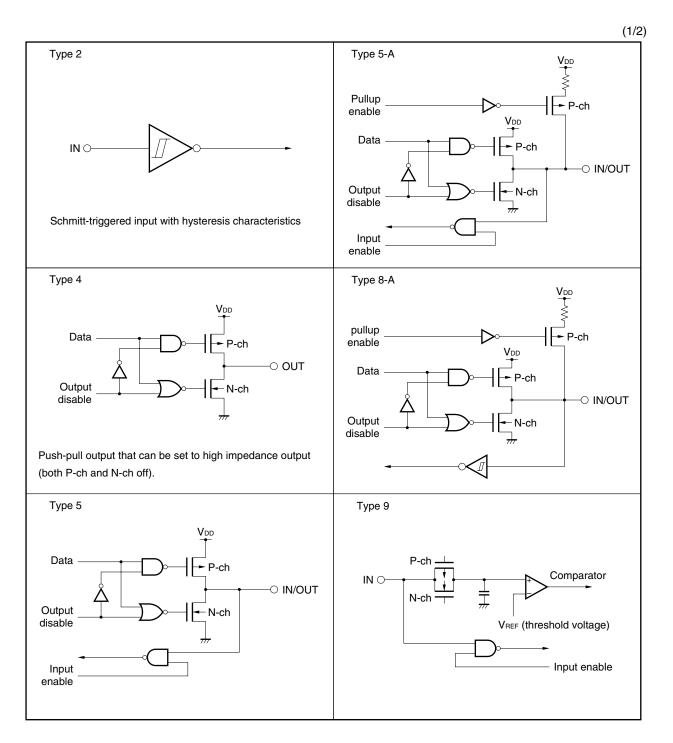

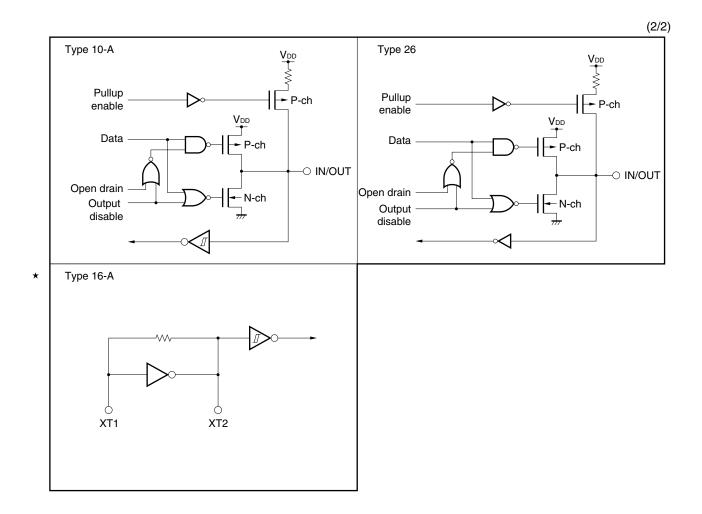

| p. 55      | Addition and modification of description in 2.4 Pin I/O Circuits and Recommended Connection of Unused Pins                                                      |

| p. 58      | Modification of 2.5 Pin I/O Circuits                                                                                                                            |

| p. 59      | Addition of description to minimum instruction execution time in 3.1 Features                                                                                   |

| p. 63      | Change of description in 3.2.2 (2) Program status word (PSW)                                                                                                    |

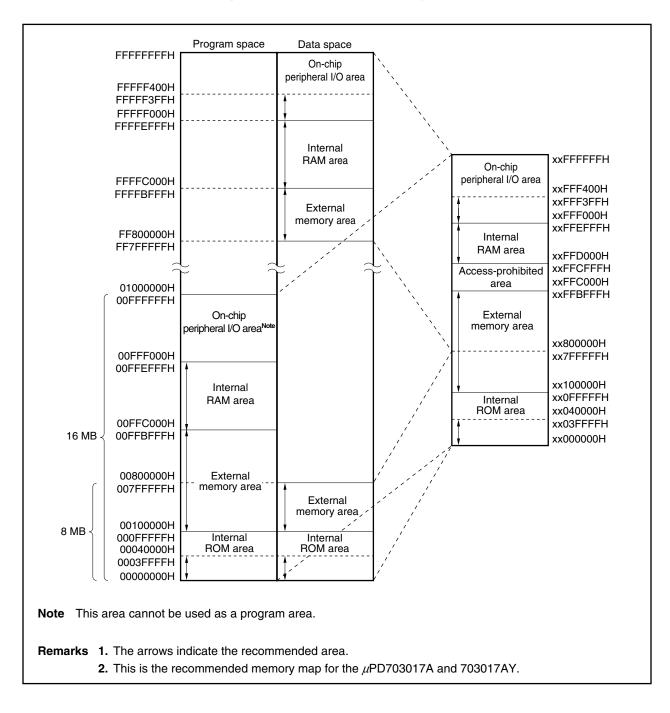

| p. 80      | Modification of Figure 3-16 Recommended Memory Map                                                                                                              |

| p. 81      | Addition of description in 3.4.8 Peripheral I/O registers                                                                                                       |

| p. 86      | Addition and modification of description in 3.4.9 Specific registers                                                                                            |

| p. 113     | Addition of description in 5.2.4 Noise elimination of external interrupt request input pin                                                                      |

| p. 114     | Addition of description in 5.2.5 Edge detection function of external interrupt request input pin                                                                |

| p. 122     | Addition to Cautions in 5.3.4 Interrupt control register (xxICn)                                                                                                |

| p. 125     | Addition of Caution in 5.3.5 In-service priority register (ISPR)                                                                                                |

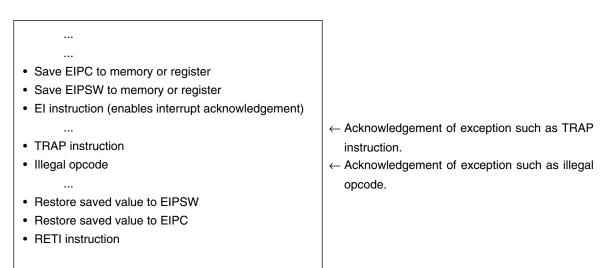

| p. 136     | Addition of 5.8.1 Interrupt request valid timing after El instruction                                                                                           |

| p. 137     | Addition of 5.9 Bit Manipulation Instruction of Interrupt Control Register During DMA Transfer                                                                  |

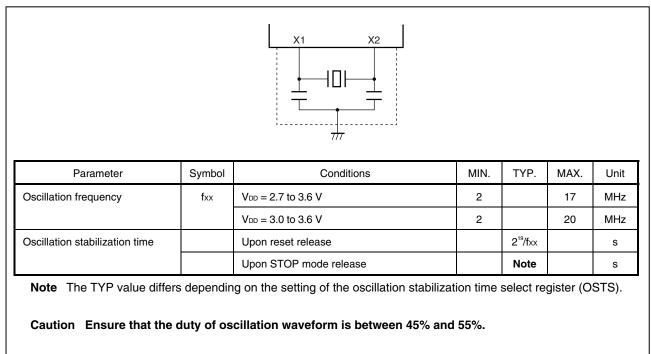

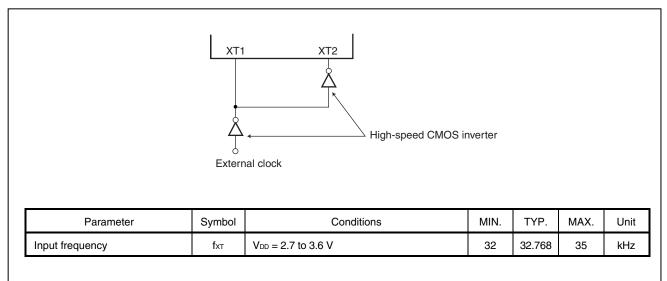

| p. 138     | Modification of description in 6.1 (1) Main clock oscillator                                                                                                    |

| p. 138     | Modification of description in 6.1 (2) Subclock oscillator                                                                                                      |

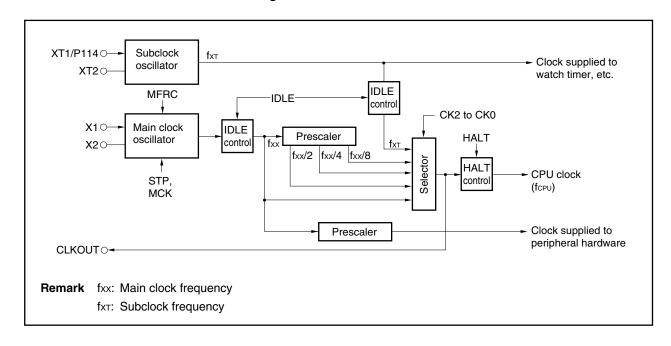

| p. 139     | Modification of Figure 6-1 Clock Generator                                                                                                                      |

| p. 140     | Addition to Notes in 6.3.1 (1) Processor clock control register (PCC)                                                                                           |

| p. 141     | Modification of description in 6.3.1 (1) (b) Example of subclock operation $\rightarrow$ main clock operation setup                                             |

| p. 142     | Addition to Notes and Cautions in 6.3.1 (2) Power save control register (PSC)                                                                                   |

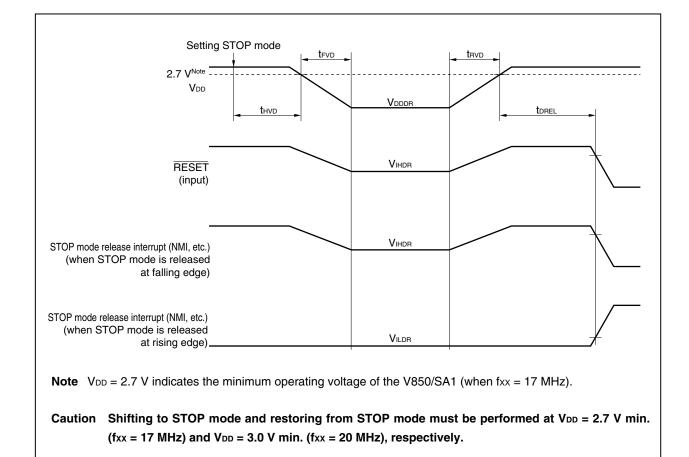

| p. 148     | Modification of description in 6.4.4 (1) Settings and operating states                                                                                          |

| p. 151     | Addition of 6.6 Notes on Power Save Function                                                                                                                    |

| p. 156     | Modification of Caution in 7.1.3 (2) Capture/compare registers 00, 10 (CR00, CR10)                                                                              |

| p. 157     | Modification of Caution in 7.1.3 (3) Capture/compare registers 01, 11 (CR01, CR11)                                                                              |

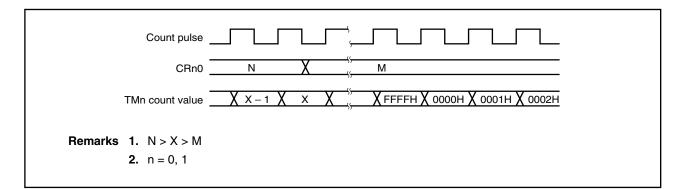

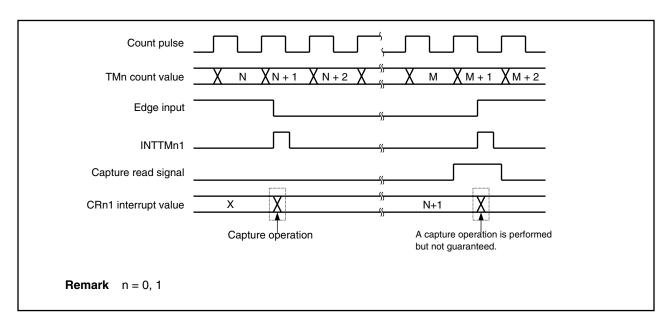

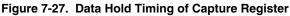

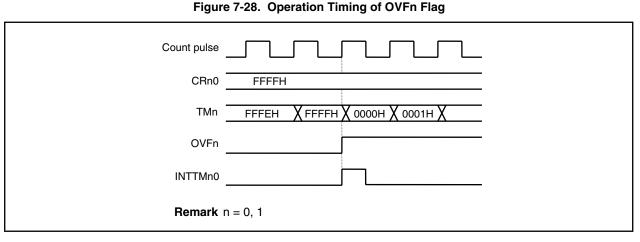

| p. 185     | Change of Figure 7-27 Data Hold Timing of Capture Register                                                                                                      |

| p. 185     | Addition of 7.2.7 (6) (c) One-shot output function                                                                                                              |

| p. 189     | Addition of 7.3.1 Outline                                                                                                                                       |

The mark  $\star$  shows major revised points.

# Major Revisions in This Edition (2/2)

| Page           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p. 196         | Change of Caution in 7.3.4 (2) 8-bit timer mode control registers 2 to 5 (TMC2 to TMC5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

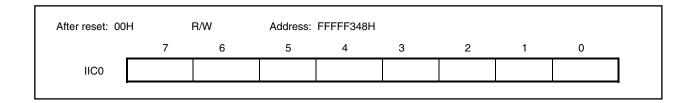

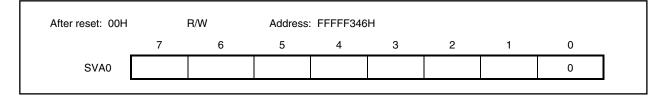

| p. 242         | Modification of description in 10.3.2 (3) IIC clock select register 0 (IICCL0), IIC function expansion register 0 (IICX0)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| pp. 295 to 299 | Addition of Figures 10-25 to 10-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

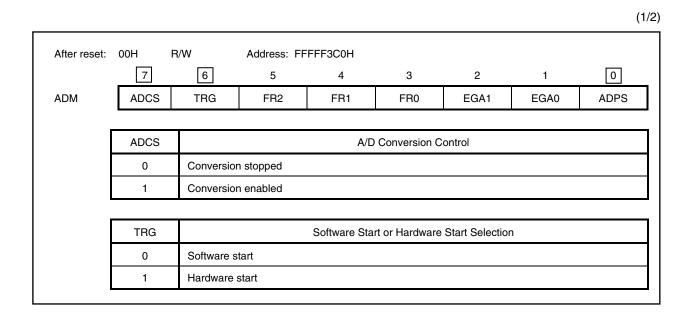

| p. 313         | Modification in 11.3 (1) A/D converter mode register (ADM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| p. 314         | Addition of Table 11-2 A/D Conversion Time Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

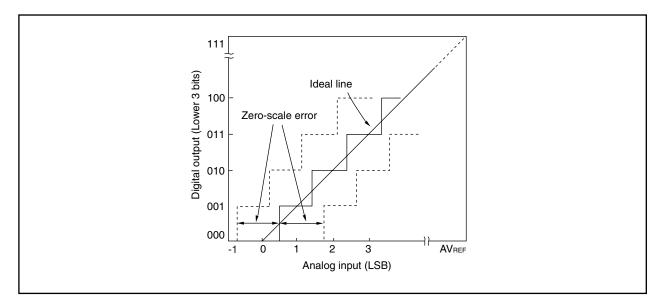

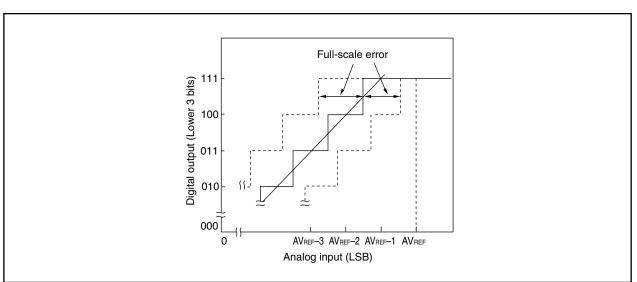

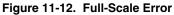

| p. 326         | Addition of 11.6 How to Read A/D Converter Characteristics Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| p. 330         | Change of description in 12.1 Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| p. 330         | Deletion of 12.2 Transfer Completion Interrupt Request and addition of 12.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| p. 331         | Addition of 12.3 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

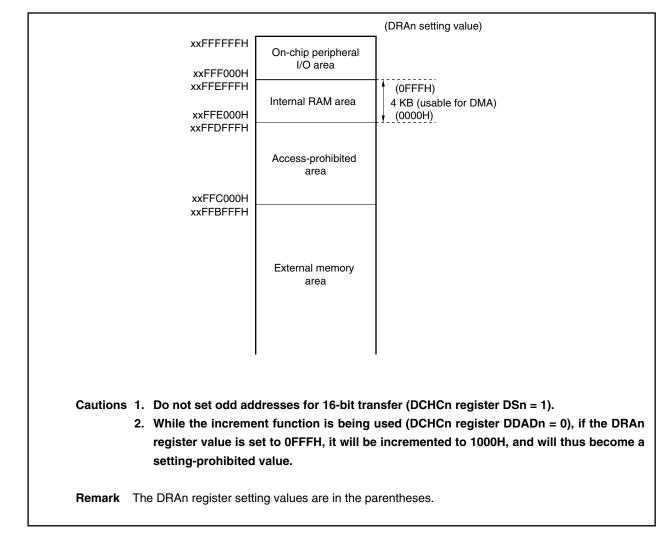

| p. 333         | Addition of Figure 12-2 Correspondence Between DRAn Setting Value and Internal RAM (4 KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

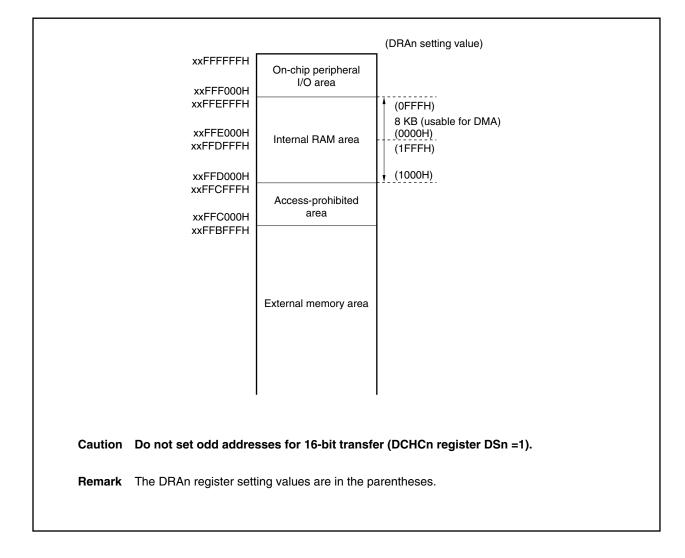

| p. 334         | Addition of Figure 12-3 Correspondence Between DRAn Setting Value and Internal RAM (8 KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| p. 338         | Addition of 12.5 Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p. 339         | Addition of 12.6 Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| p. 340         | Addition of 13.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

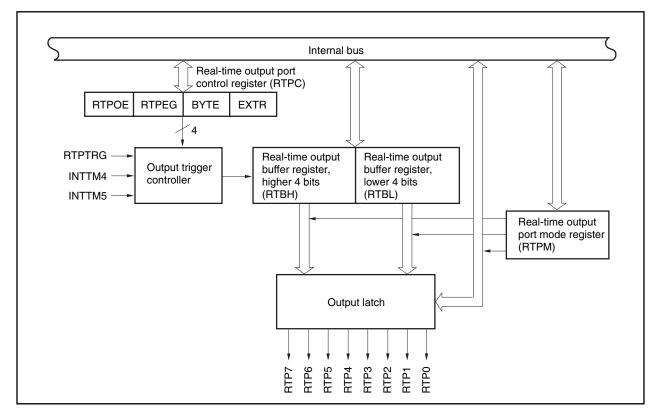

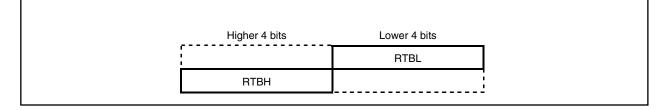

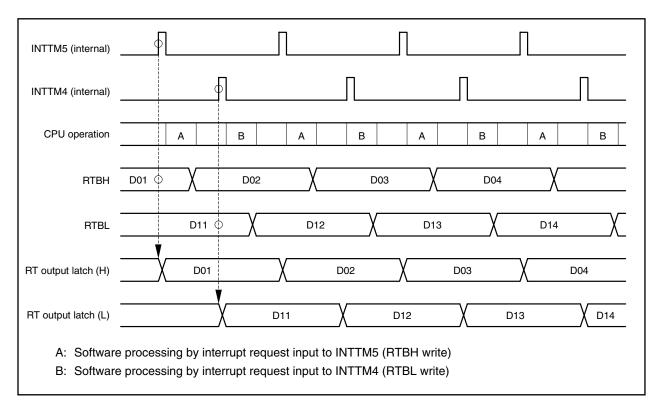

| p. 342         | Addition of 13.3 (2) Output latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| p. 345         | Modification of description in 13.5 Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| p. 347         | Addition of description in 13.7 Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| p. 348         | Addition of Table 14-1 Pin I/O Buffer Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

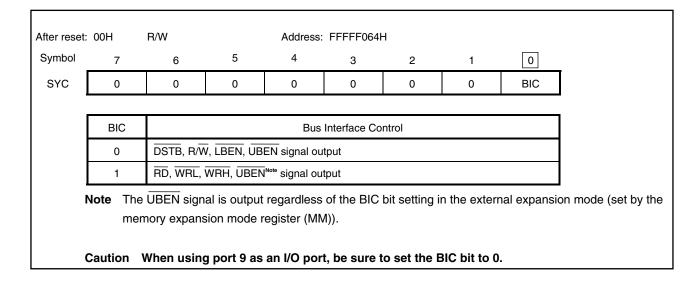

| p. 380         | Addition of Caution in 14.2.8 (1) Function of P9 pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| p. 396         | Addition of 14.4 Operation of Port Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p. 398         | Addition of Caution in CHAPTER 16 FLASH MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

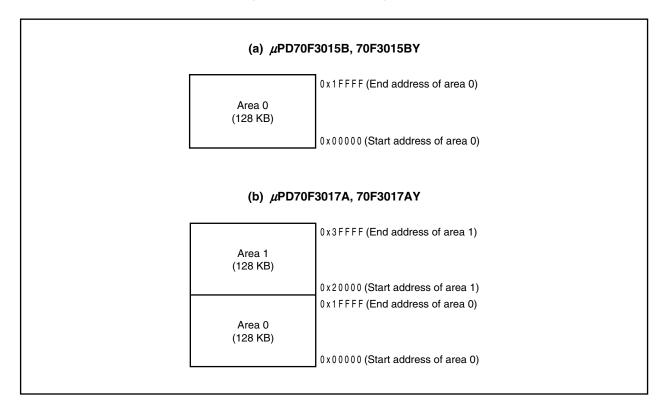

| p. 398         | Change of description in 16.1.1 Erasing unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

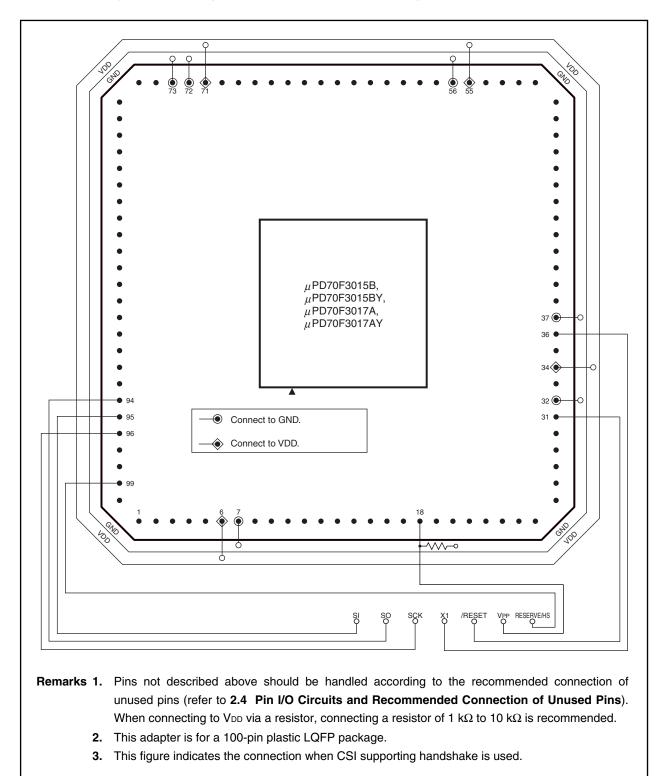

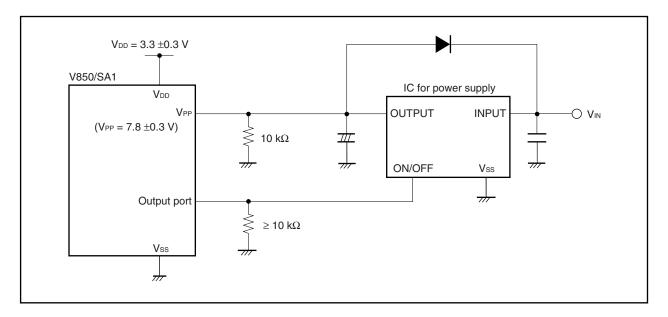

| p. 400         | Addition of Figure 16-1 Wiring Example of V850/SA1 Flash Writing Adapter (FA-100GC-8EU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| p. 401         | Addition of Table 16-1 Wiring Table of V850/SA1 Flash Writing Adapter (FA-100GC-8EU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

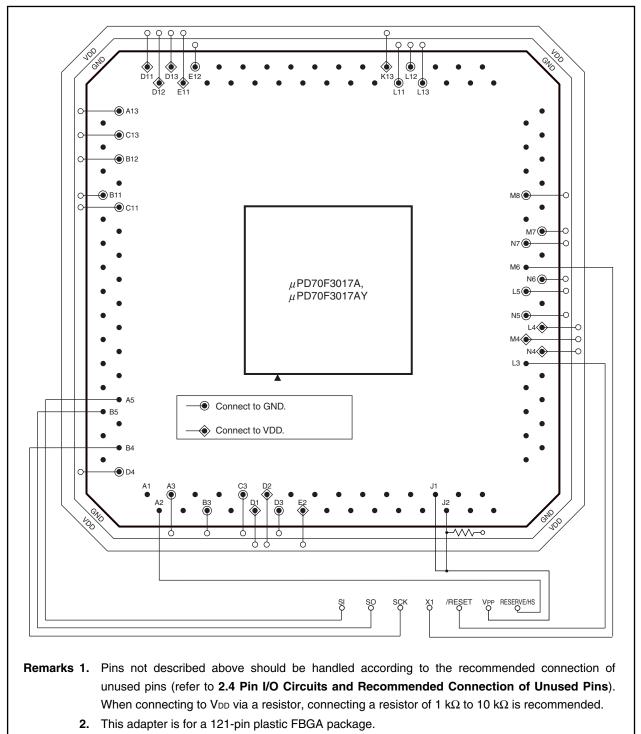

| p. 402         | Addition of Figure 16-2 Wiring Example of V850/SA1 Flash Writing Adapter (FA-121F1-EA6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| p. 403         | Addition of Table 16-2 Wiring Table of V850/SA1 Flash Writing Adapter (FA-121F1-EA6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| p. 413         | Addition of 16.7 Flash Memory Programming by Self-Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| p. 434         | Addition of CHAPTER 17 ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| p. 460         | Addition of CHAPTER 18 PACKAGE DRAWINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| p. 462         | Addition of CHAPTER 19 RECOMMENDED SOLDERING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| p. 466         | Addition of APPENDIX A NOTES ON TARGET SYSTEM DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| p. 468         | Addition of description in APPENDIX B REGISTER INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| p. 486         | Addition of APPENDIX E REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Major revisions in modification version (U12768EJ4V1UD00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Throughout     | Addition of lead-free products<br>μPD703014AF1-xxx-EA6-A, 703014AYF1-xxx-EA6-A, 703014BBF1-xxx-EA6-A, 703014BGC-xxx-8EU-A,<br>μPD703014BYF1-xxx-EA6-A, 703014BYGC-xxx-8EU-A, 703015AF1-xxx-EA6-A, 703015AYF1-xxx-EA6-A,<br>μPD703015BF1-xxx-EA6-A, 703015BGC-xxx-8EU-A, 703015BYF1-xxx-EA6-A, 703015BYGC-xxx-8EU-A,<br>μPD703017AF1-xxx-EA6-A, 703017AGC-xxx-8EU-A, 703017AYF1-xxx-EA6-A, 703017AYGC-xxx-8EU-A,<br>μPD7053015BF1-EA6-A, 70F3015BGC-8EU-A, 70F3015BYF1-EA6-A, 70F3015BYGC-8EU-A,<br>μPD70F3017AF1-EA6-A, 70F3017AGC-8EU-A, 70F3017AYF1-EA6-A, 70F3017AYGC-8EU-A |

| p.462          | Addition of lead-free products to CHAPTER 19 RECOMMENDED SOLDERING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

The mark  $\star$  shows major revised points.

#### INTRODUCTION

- **Readers** This manual is intended for users who wish to understand the functions of the V850/SA1 ( $\mu$ PD703014A, 703014AY, 703014B, 703014BY 703015A, 703015AY, 703015B, 703015BY, 703017AY, 7053017AY, 70F3015BY, 70F3017A, 70F3017AY) and design application systems using the V850/SA1.

- **Purpose** This manual is intended to give users an understanding of the hardware functions described in the Organization below.

- **Organization** The V850/SA1 User's Manual is divided into two parts: hardware (this manual) and architecture (V850 Series User's Manual Architecture).

| Hardware                         |          | Architecture                              |   |

|----------------------------------|----------|-------------------------------------------|---|

| Pin function                     |          | Data type                                 |   |

| <ul> <li>CPU function</li> </ul> |          | <ul> <li>Register set</li> </ul>          |   |

| • On ohin paripharal             | function | <ul> <li>Instruction formation</li> </ul> | r |

- On-chip peripheral function

- Flash memory programming

- Electrical specifications

- · Instruction format and instruction set

- Interrupt and exception

- Pipeline operation

- How to Use This Manual It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To find out the details of a register whose name is known:

- $\rightarrow$  Refer to **APPENDIX B REGISTER INDEX**.

- To find out the details of a function, etc., whose name is known:  $\rightarrow$  Refer to **APPENDIX D INDEX**.

To understand the details of a instruction function:

$\rightarrow$  Refer to V850 Series User's Manual Architecture available separately.

How to read register formats:

→ Names of bits whose numbers are enclosed in a square are defined in the device file under reserved words.

To understand the overall functions of the V850/SA1:

$\rightarrow$  Read this manual in the order of the **CONTENTS**.

To know the electrical specifications of the V850/SA1:

$\rightarrow$  Refer to CHAPTER 17 ELECTRICAL SPECIFICATIONS.

#### Conventions Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on the bottom

Note: Footnote for items marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numerical representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefixes indicating power of 2 (address space, memory capacity):

K (kilo) ... 2<sup>10</sup>=1024 M (mega) ... 2<sup>20</sup>=1024<sup>2</sup> G (giga) ... 2<sup>30</sup>=1024<sup>3</sup>

#### **Related Documents** The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### Documents related to V850/SA1

| Document Name                                           | Document No. |

|---------------------------------------------------------|--------------|

| V850 Series Architecture User's Manual                  | U10243E      |

| V850/SA1 Application Note                               | U13851E      |

| V850/SA1 Hardware User's Manual                         | This manual  |

| V850 Series Flash Memory Self Programming User's Manual | U15673E      |

#### Documents related to development tools (user's manuals)

| Document Name                                   | Document No.                                        |         |

|-------------------------------------------------|-----------------------------------------------------|---------|

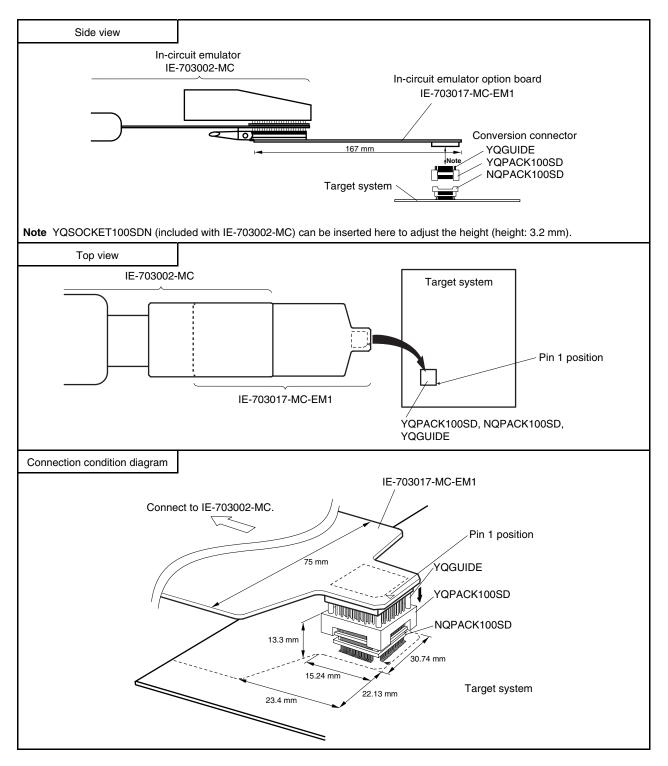

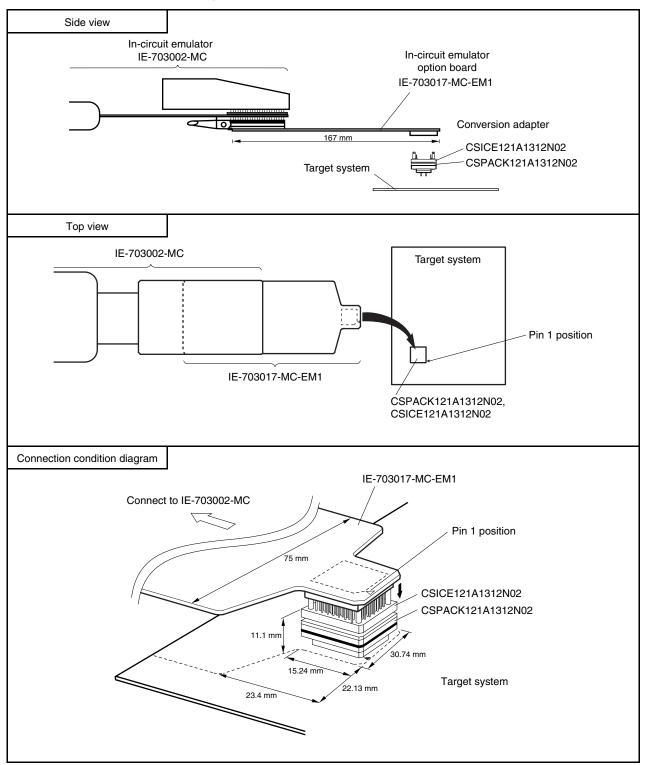

| IE-703002-MC (In-Circuit Emulator)              |                                                     | U11595E |

| IE-703017-MC-EM1 (In-Circuit Emulator Option Bo | pard)                                               | U12898E |

| CA850 Ver. 2.40 or Later C Compiler Package     | Operation                                           | U15024E |

|                                                 | C Language                                          | U15025E |

|                                                 | Project Manager                                     | U15026E |

|                                                 | Assembly Language                                   | U15027E |

| ID850 Ver. 2.40 Integrated Debugger             | Operation (Windows™<br>Based)                       | U15181E |

| SM850 Ver. 2.40 System Simulator                | Operation (Windows Based)                           | U15182E |

| SM850 Ver. 2.00 or Later System Simulator       | External Part User Open<br>Interface Specifications | U14873E |

| RX850 Ver. 3.13 or Later Real-time OS           | Basic                                               | U13430E |

|                                                 | Installation                                        | U13410E |

|                                                 | Technical                                           | U13431E |

| RX850 Pro Ver. 3.13 or Later Real-time OS       | Basic                                               | U13773E |

|                                                 | Installation                                        | U13774E |

|                                                 | Technical                                           | U13772E |

| RD850 Ver. 3.01 Task Debugger                   | U13737E                                             |         |

| RD850 Pro Ver. 3.01 Task Debugger               | U13916E                                             |         |

| AZ850 Ver. 3.0 System Performance Analyzer      | U14410E                                             |         |

| PG-FP3 Flash Memory Programmer                  | U13502E                                             |         |

| PG-FP4 Flash Memory Programmer                  |                                                     | U15260E |

#### CONTENTS

| CHAPTE | R1IN         | ITRODUCTION                                          | 27 |

|--------|--------------|------------------------------------------------------|----|

| 1.1    | Gene         | ral                                                  | 27 |

| 1.2    | Featu        | ires                                                 | 28 |

| 1.3    | Appli        | cations                                              |    |

| 1.4    | Order        | ring Information                                     |    |

| 1.5    | Pin C        | onfiguration                                         | 31 |

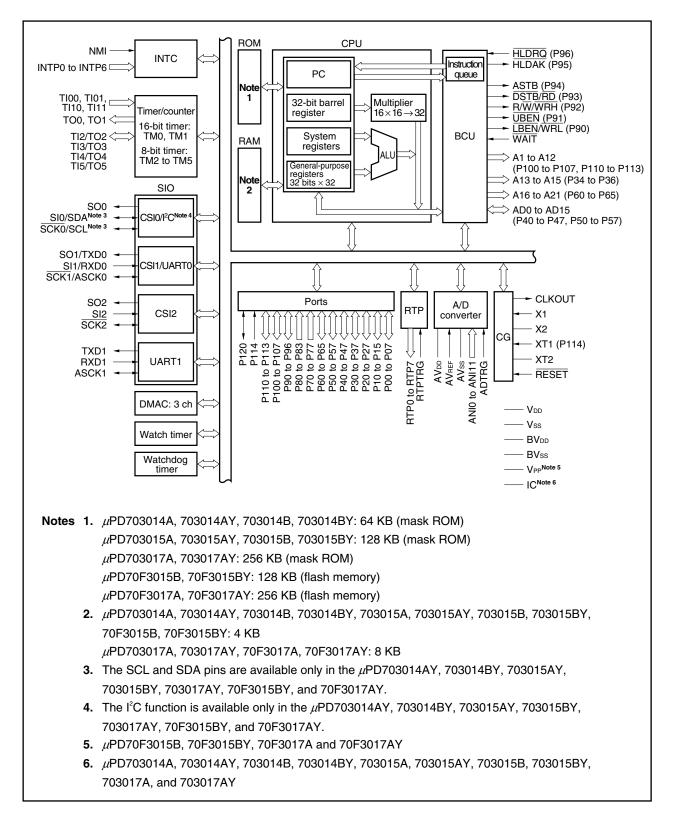

| 1.6    | Funct        | tion Blocks                                          | 34 |

|        | 1.6.1        | Internal block diagram                               |    |

|        | 1.6.2        | Internal units                                       |    |

| CHAPTE | R 2 P        | IN FUNCTIONS                                         | 38 |

| 2.1    | List o       | f Pin Functions                                      |    |

| 2.2    | Pin S        | tates                                                | 43 |

| 2.3    | Desci        | ription of Pin Functions                             | 44 |

| 2.4    |              | O Circuits and Recommended Connection of Unused Pins |    |

| 2.5    | Pin I/       | O Circuits                                           | 57 |

|        |              |                                                      |    |

| CHAPTE | R 3 C        | PU FUNCTIONS                                         | 59 |

| 3.1    | Featu        | ires                                                 |    |

| 3.2    |              | Register Set                                         |    |

| •      | 3.2.1        | Program register set                                 |    |

|        | 3.2.2        | System register set                                  |    |

| 3.3    |              | ation Modes                                          |    |

| 3.4    |              | ess Space                                            |    |

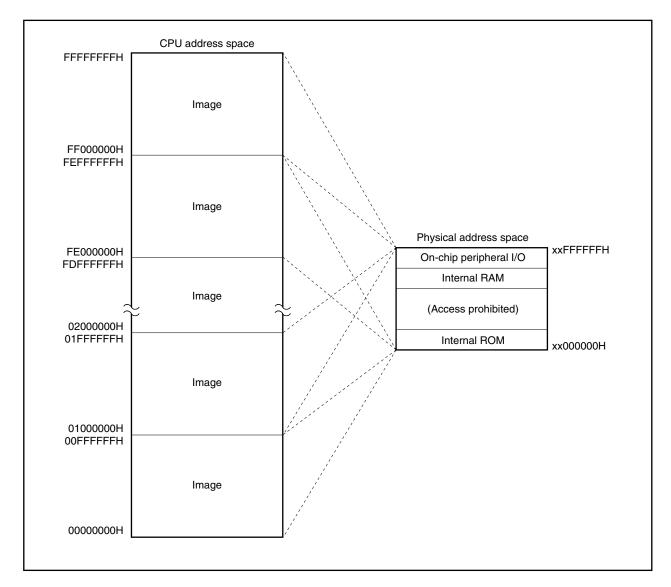

|        | 3.4.1        | CPU address space                                    |    |

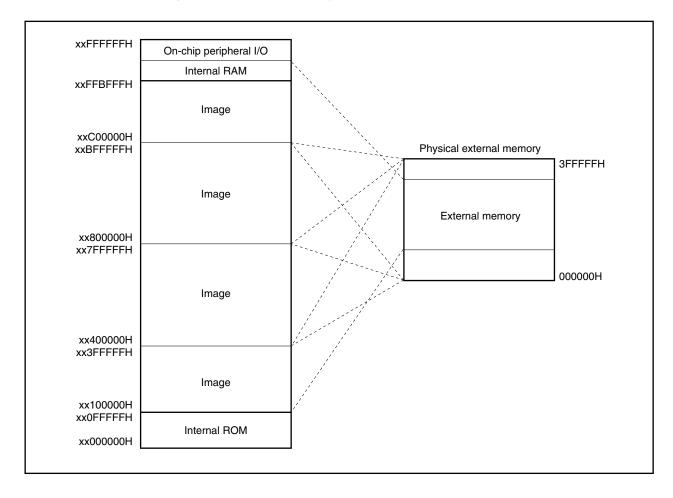

|        | 3.4.2        | Image                                                | 67 |

|        | 3.4.3        | Wraparound of CPU address space                      |    |

|        | 3.4.4        | Memory map                                           |    |

|        | 3.4.5        | Area                                                 | 70 |

|        | 3.4.6        | External expansion mode                              | 77 |

|        | 3.4.7        | Recommended use of address space                     |    |

|        | 3.4.8        | Peripheral I/O registers                             |    |

|        | 3.4.9        | Specific registers                                   |    |

| СНАРТЕ | <b>Р</b> / В | US CONTROL FUNCTION                                  | 80 |

| 4.1    |              | res                                                  |    |

| 4.2    |              | Control Pins and Control Register                    |    |

|        | 4.2.1        | Bus control pins                                     |    |

|        | 4.2.2        | Control register                                     |    |

| 4.3 I  |              | Cess                                                 |    |

| -      | 4.3.1        | Number of access clocks                              |    |

|        | 4.3.2        | Bus width                                            |    |

| 4.4     | Memory Block Function                                                 |     |  |

|---------|-----------------------------------------------------------------------|-----|--|

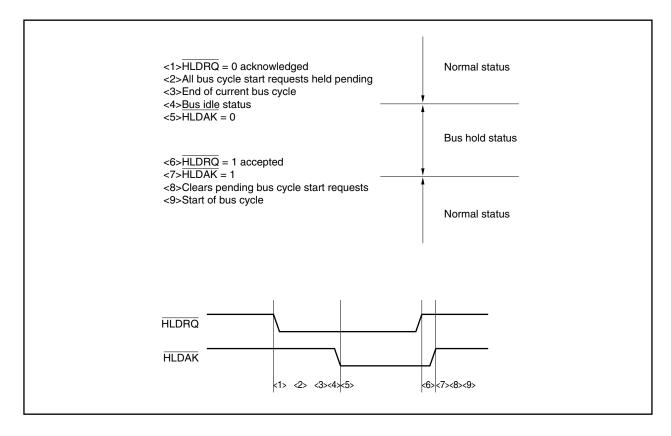

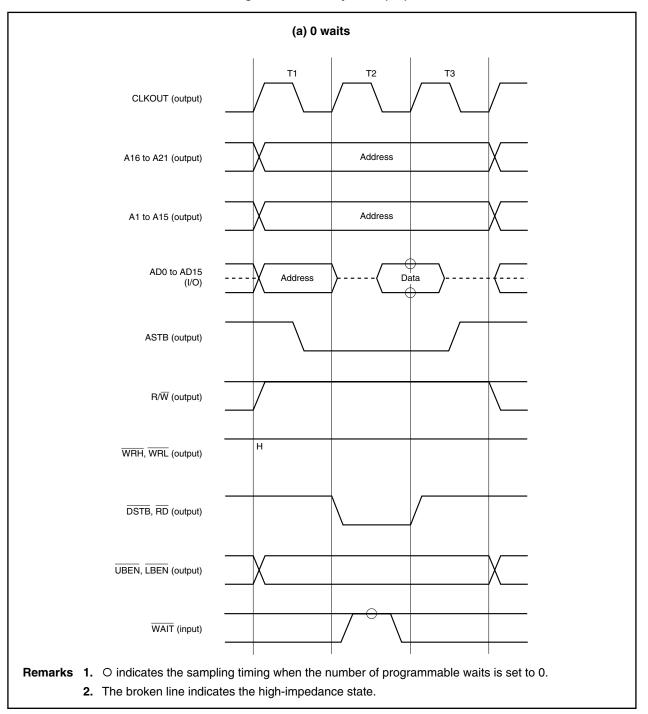

| 4.5     | Wait Function                                                         | 93  |  |

|         | 4.5.1 Programmable wait function                                      | 93  |  |

|         | 4.5.2 External wait function                                          | 94  |  |

|         | 4.5.3 Relationship between programmable wait and external wait        | 94  |  |

| 4.6     | Idle State Insertion Function                                         |     |  |

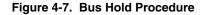

| 4.7     | Bus Hold Function                                                     | 96  |  |

|         | 4.7.1 Outline of function                                             | 96  |  |

|         | 4.7.2 Bus hold procedure                                              | 97  |  |

|         | 4.7.3 Operation in power save mode                                    | 97  |  |

| 4.8     | Bus Timing                                                            |     |  |

| 4.9     | Bus Priority                                                          | 105 |  |

| 4.10    | Memory Boundary Operation Conditions                                  | 105 |  |

|         | 4.10.1 Program space                                                  |     |  |

|         | 4.10.2 Data space                                                     | 105 |  |

|         |                                                                       |     |  |

| CHAPTER | R 5 INTERRUPT/EXCEPTION PROCESSING FUNCTION                           | 106 |  |

| 5.1     | Outline                                                               | 106 |  |

|         | 5.1.1 Features                                                        |     |  |

| 5.2     | Non-Maskable Interrupts                                               |     |  |

|         | 5.2.1 Operation                                                       |     |  |

|         | 5.2.2 Restore                                                         | 112 |  |

|         | 5.2.3 NP flag                                                         | 113 |  |

|         | 5.2.4 Noise elimination of external interrupt request input pin       | 113 |  |

|         | 5.2.5 Edge detection function of external interrupt request input pin | 114 |  |

| 5.3     | Maskable Interrupts                                                   | 115 |  |

|         | 5.3.1 Operation                                                       | 115 |  |

|         | 5.3.2 Restore                                                         | 117 |  |

|         | 5.3.3 Priorities of maskable interrupts                               | 118 |  |

|         | 5.3.4 Interrupt control register (xxICn)                              |     |  |

|         | 5.3.5 In-service priority register (ISPR)                             |     |  |

|         | 5.3.6 ID flag                                                         |     |  |

|         | 5.3.7 Watchdog timer mode register (WDTM)                             |     |  |

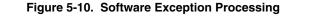

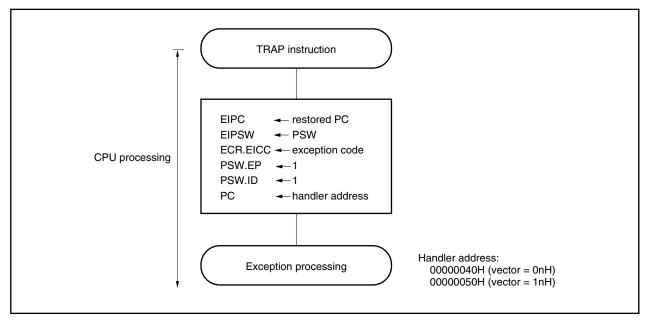

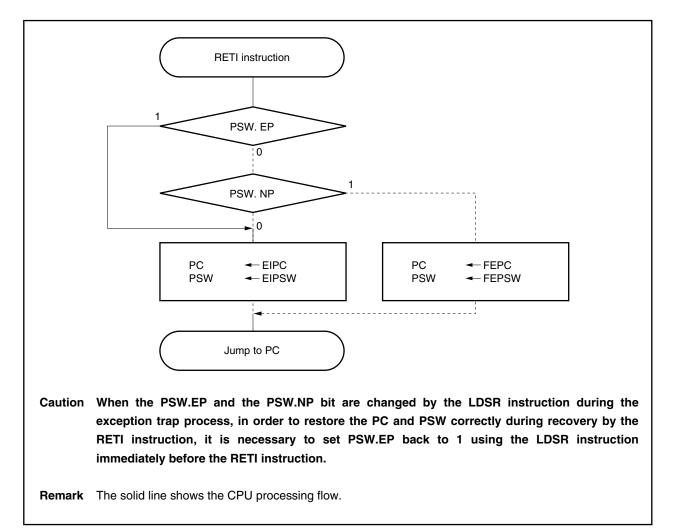

| 5.4     | Software Exceptions                                                   | 127 |  |

|         | 5.4.1 Operation                                                       |     |  |

|         | 5.4.2 Restore                                                         |     |  |

|         | 5.4.3 EP flag                                                         |     |  |

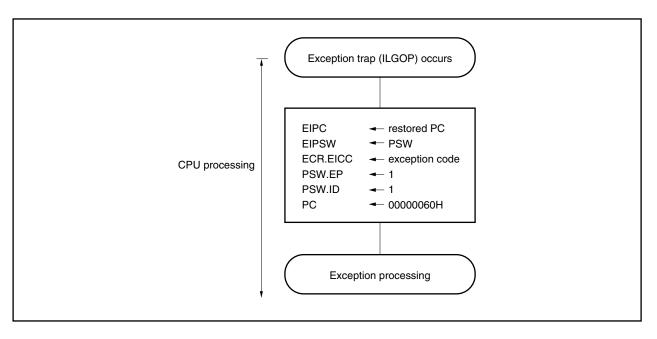

| 5.5     | Exception Trap                                                        | 129 |  |

|         | 5.5.1 Illegal opcode definition                                       |     |  |

|         | 5.5.2 Operation                                                       | 130 |  |

|         | 5.5.3 Restore                                                         | 131 |  |

| 5.6     | Priority Control                                                      | 132 |  |

|         | 5.6.1 Priorities of interrupts and exceptions                         | 132 |  |

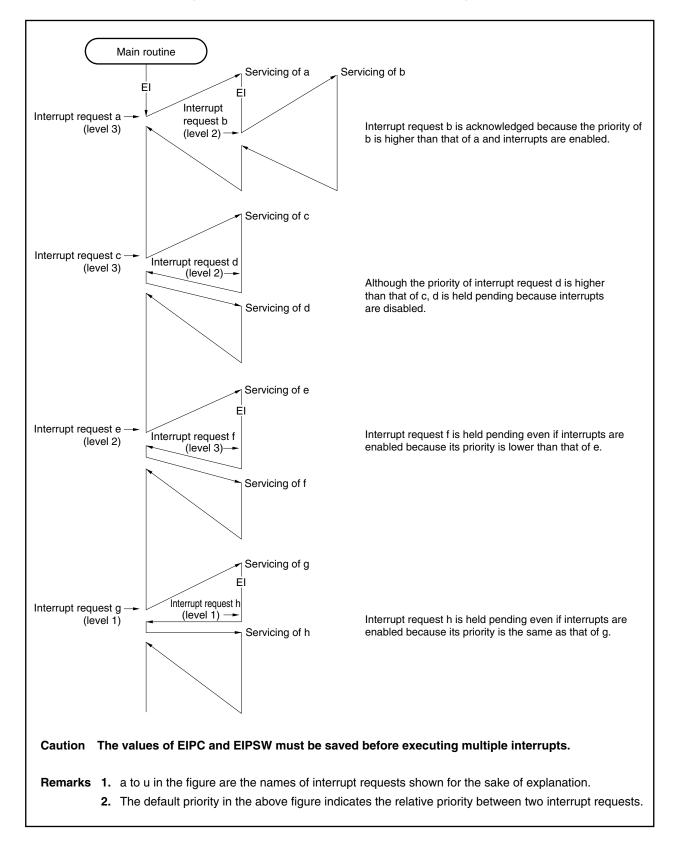

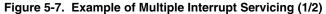

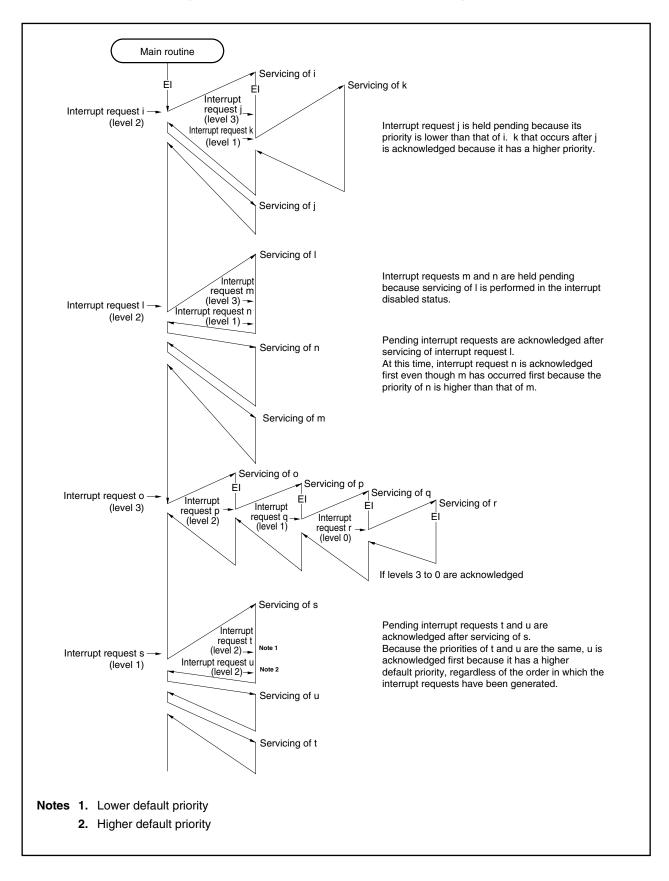

|         | 5.6.2 Multiple interrupts                                             |     |  |

| 5.7     | Interrupt Latency Time                                                |     |  |

| 5.8     | Periods in Which Interrupts Are Not Acknowledged                      | 135 |  |

|         | 5.8.1 Interrupt request valid timing after EI instruction             | 136 |  |

\*

| CHAPTE       | R 6 CLOCK GENERATION FUNCTION                            | 13 |

|--------------|----------------------------------------------------------|----|

| 6.1          | General                                                  | 13 |

| 6.2          | Configuration                                            | 13 |

| 6.3          | Clock Output Function                                    | 13 |

|              | 6.3.1 Control registers                                  | 14 |

| 6.4          | Power Save Functions                                     | 14 |

|              | 6.4.1 General                                            | 14 |

|              | 6.4.2 HALT mode                                          | 14 |

|              | 6.4.3 IDLE mode                                          | 14 |

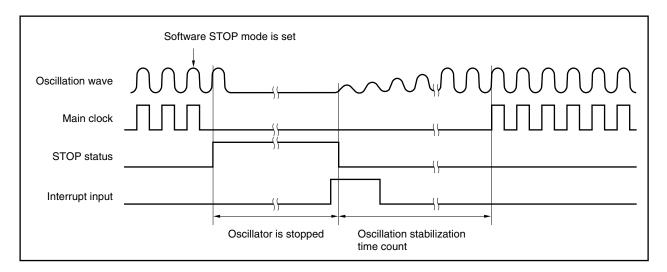

|              | 6.4.4 Software STOP mode                                 |    |

| 6.5          | Oscillation Stabilization Time                           |    |

| 6.6          | Cautions on Power Save Function                          | 13 |

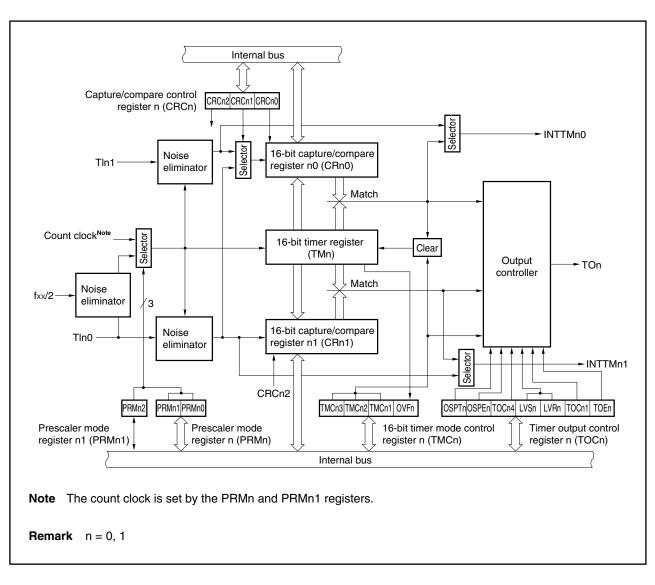

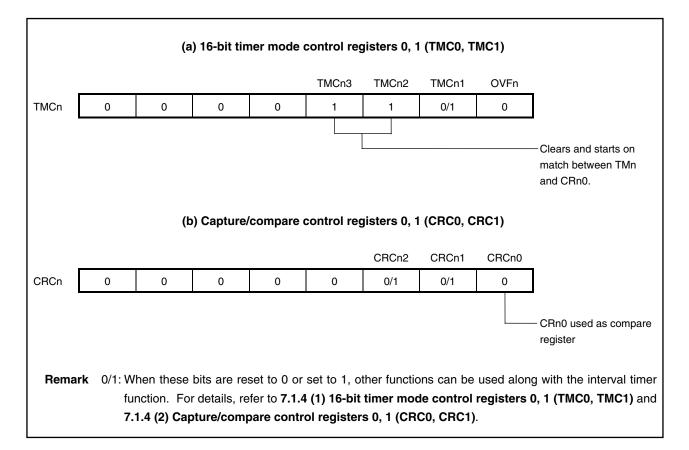

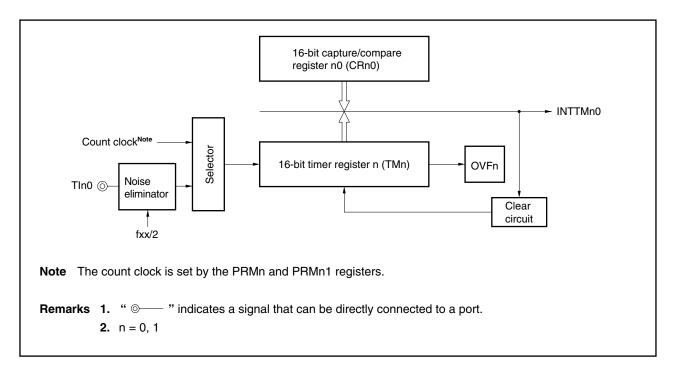

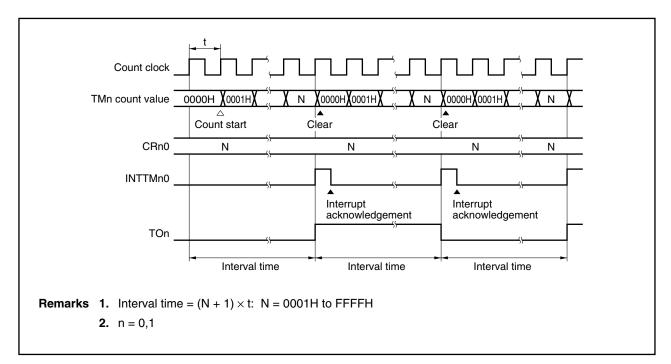

| HAPTE<br>7.1 | R 7 TIMER/COUNTER FUNCTION                               | -  |

| 7.1          | 7.1.1 Outline                                            |    |

|              | 7.1.2 Functions                                          | -  |

|              | 7.1.3 Configuration                                      | _  |

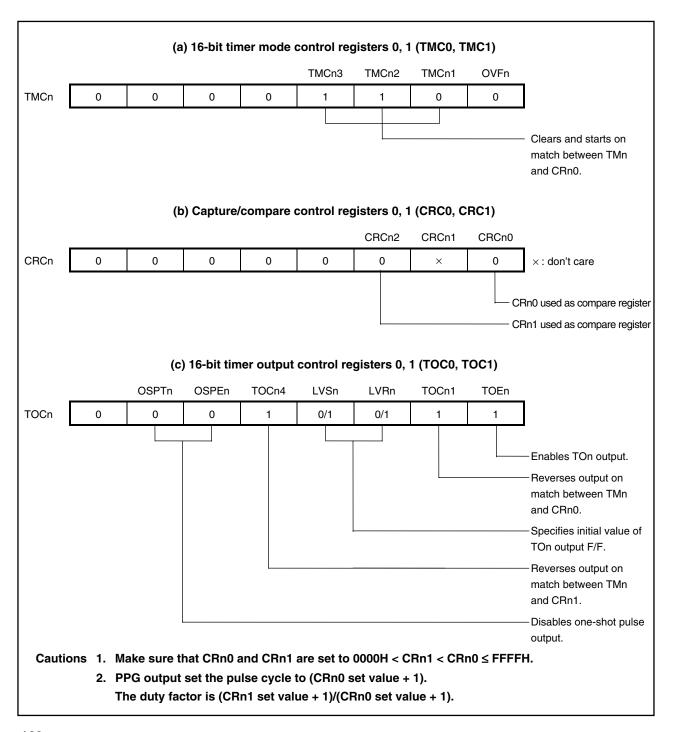

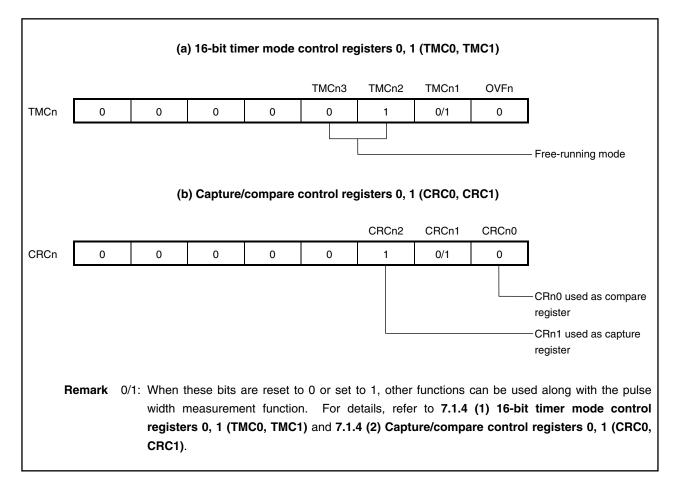

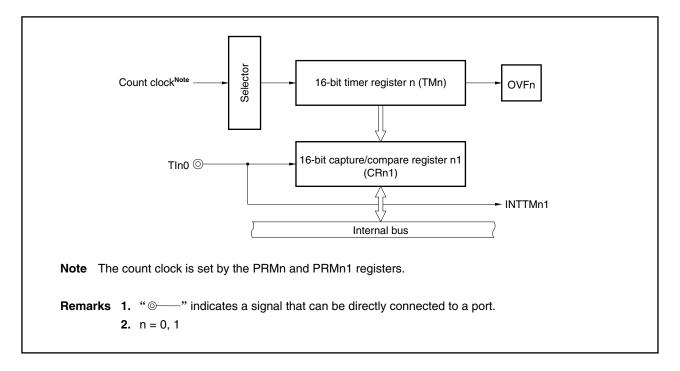

|              | 7.1.4 Timer 0, 1 control registers                       |    |

| 7.2          | 16-Bit Timer Operation                                   |    |

|              | 7.2.1 Operation as interval timer (16 bits)              |    |

|              | 7.2.2 PPG output operation                               |    |

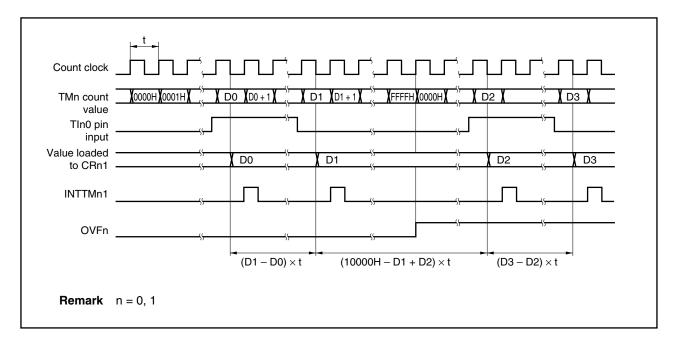

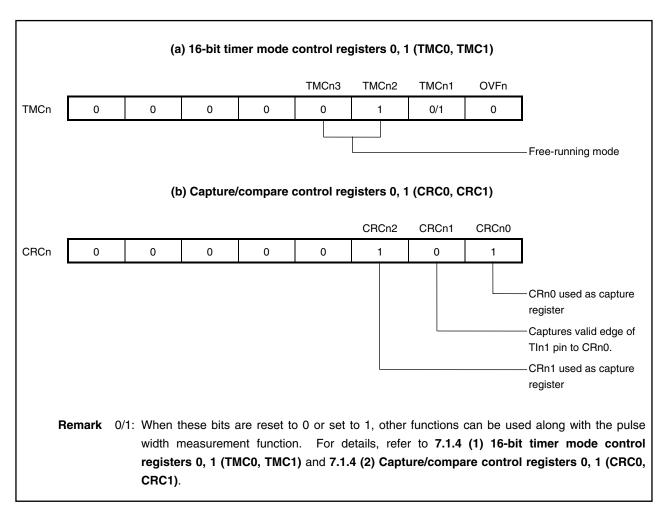

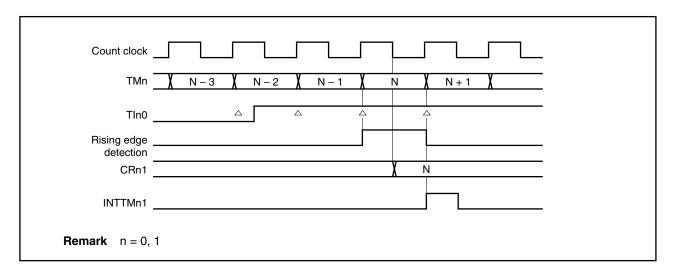

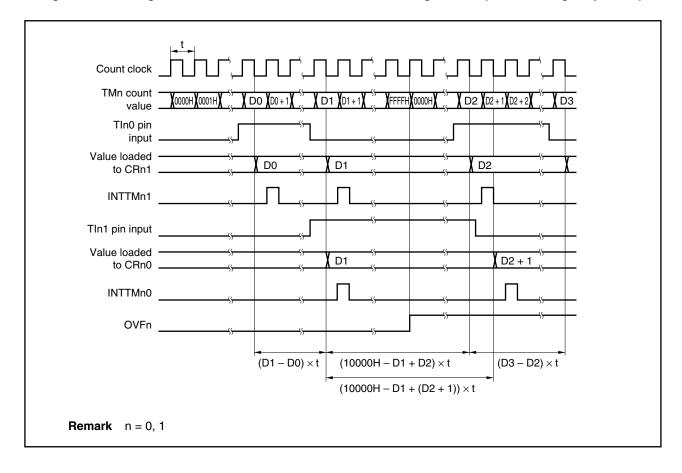

|              | 7.2.3 Pulse width measurement                            |    |

|              | 7.2.4 Operation as external event counter                |    |

|              | 7.2.5 Operation to output square wave                    |    |

|              | 7.2.6 Operation to output one-shot pulse                 |    |

|              | 7.2.7 Cautions                                           |    |

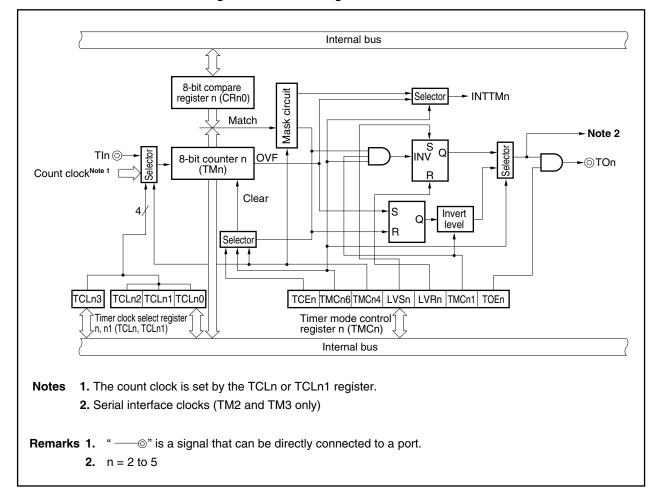

| 7.3          | 8-Bit Timers (TM2 to TM5)                                | 18 |

|              | 7.3.1 Outline                                            |    |

|              | 7.3.2 Functions                                          |    |

|              | 7.3.3 Configuration                                      |    |

|              | 7.3.4 Timer n control register                           |    |

| 7.4          | 8-Bit Timer Operation                                    |    |

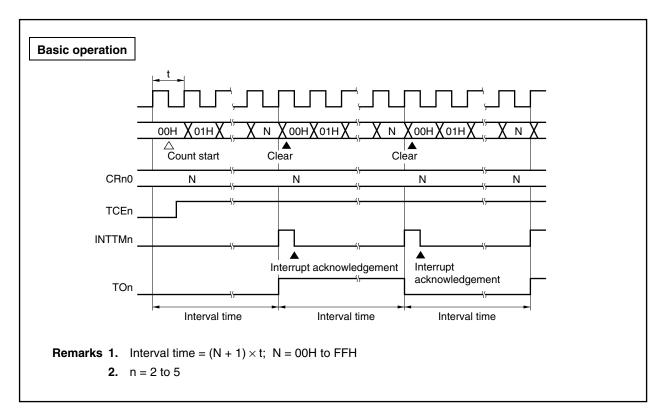

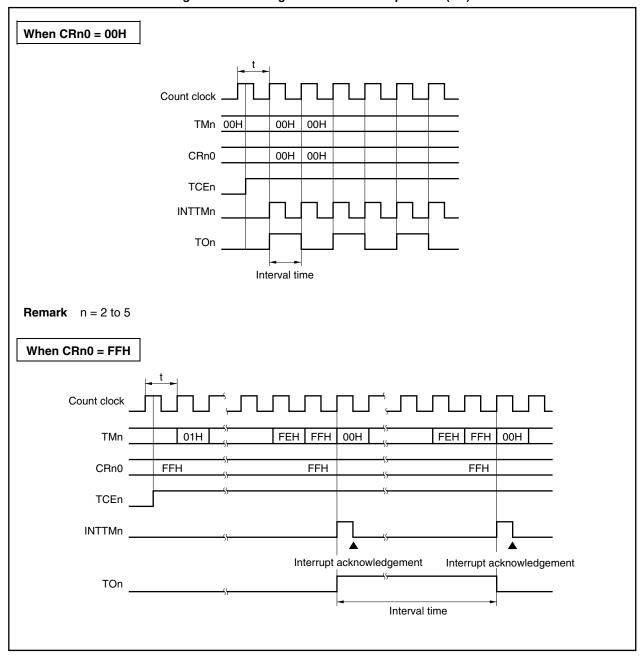

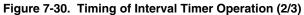

|              | 7.4.1 Operation as interval timer (8-bit operation)      |    |

|              | 7.4.2 Operation as external event counter                |    |

|              | 7.4.3 Operation as square wave output (8-bit resolution) |    |

|              | 7.4.4 Operation as 8-bit PWM output                      |    |

|              | 7.4.5 Operation as interval timer (16 bits)              |    |

|              | 7.4.6 Cautions                                           | 20 |

| HAPTE        | R 8 WATCH TIMER                                          | 20 |

| 8.1          | Functions                                                | 20 |

| 8.2          | Configuration                                            | 20 |

13

\*

$\star$

\*

| 8.4     | Operat           | tion                                                                                                           | 211 |

|---------|------------------|----------------------------------------------------------------------------------------------------------------|-----|

|         | 8.4.1            | Operation as watch timer                                                                                       | 211 |

|         | 8.4.2            | Operation as interval timer                                                                                    | 211 |

|         | 8.4.3            | Cautions                                                                                                       | 212 |

| CHAPTER | 8 9 W <i>A</i>   | ATCHDOG TIMER                                                                                                  | 213 |

| 9.1     | Functio          | ons                                                                                                            |     |

| 9.2     |                  | uration                                                                                                        |     |

| 9.3     | •                | dog Timer Control Register                                                                                     |     |

| 9.4     |                  | tion                                                                                                           |     |

| -       | 9.4.1            | Operating as watchdog timer                                                                                    |     |

|         | 9.4.2            | Operating as interval timer                                                                                    |     |

| 9.5     | Standt           | by Function Control Register                                                                                   |     |

|         | . 10 . 0         | ERIAL INTERFACE FUNCTION                                                                                       | 001 |

|         |                  |                                                                                                                |     |

| 10.1    |                  | ew                                                                                                             |     |

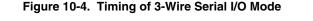

| 10.2    |                  | Serial I/O (CSI0 to CSI2)                                                                                      |     |

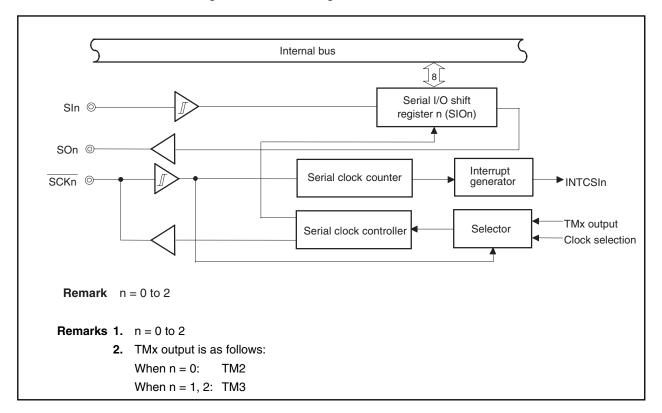

|         | 10.2.1           | Configuration                                                                                                  |     |

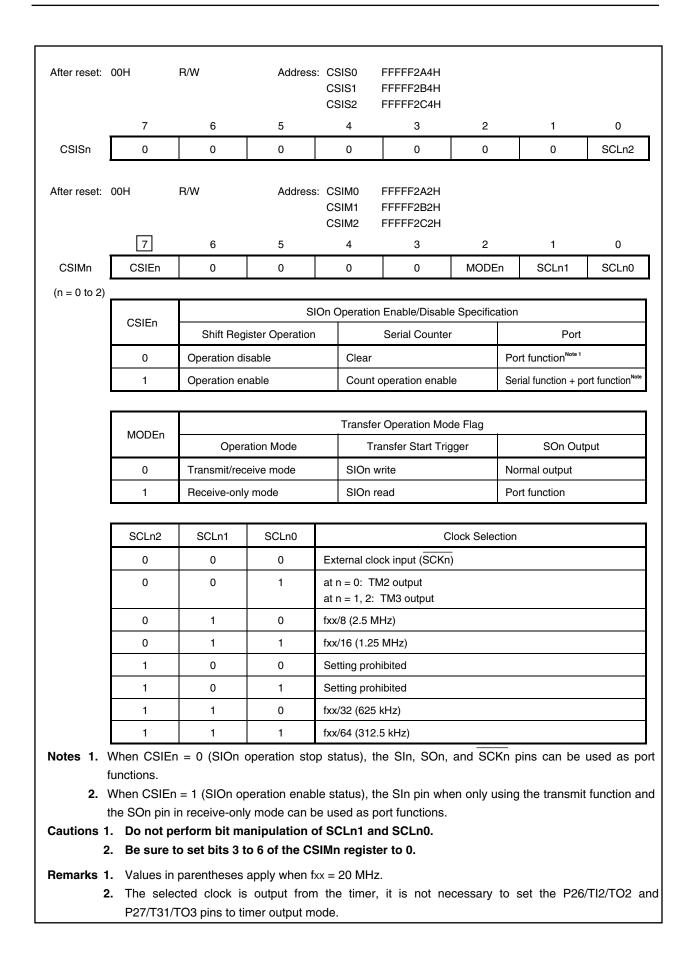

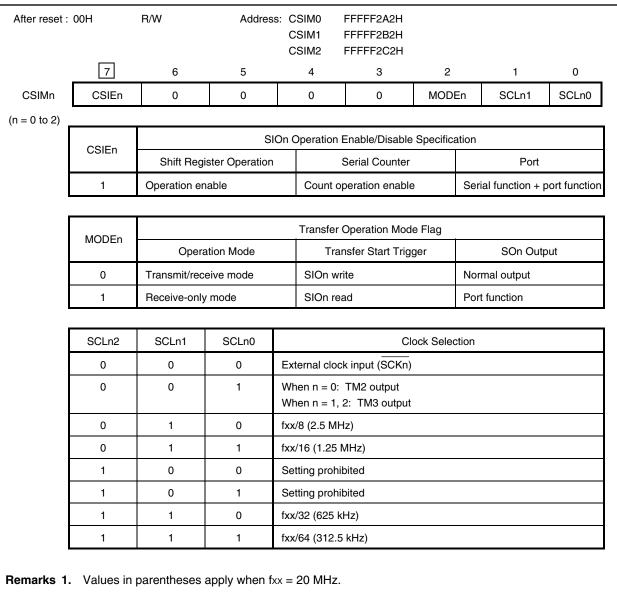

|         | 10.2.2           | CSIn control registers                                                                                         |     |

| 10.0    | 10.2.3           |                                                                                                                |     |

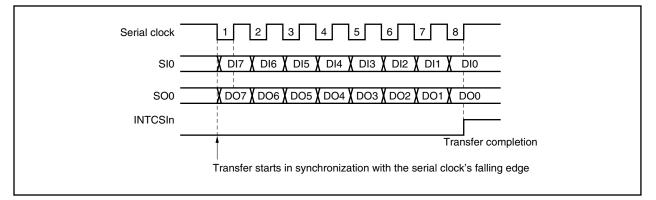

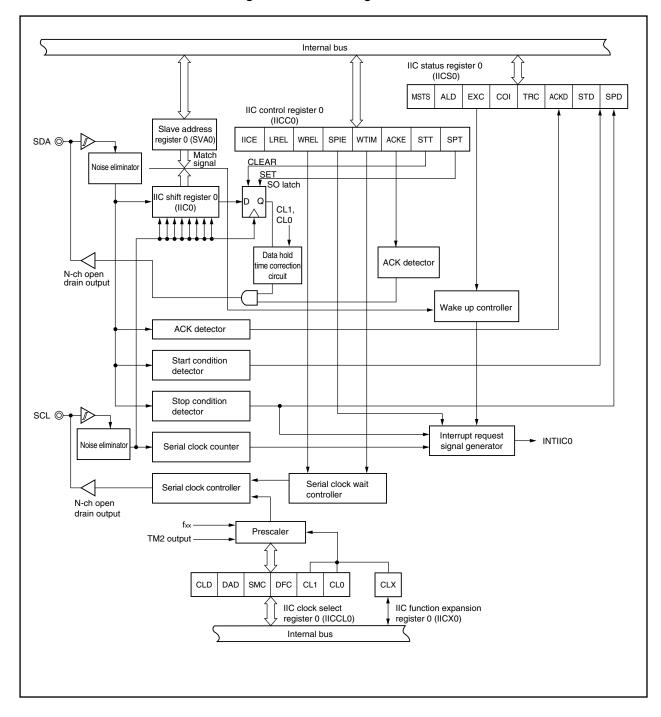

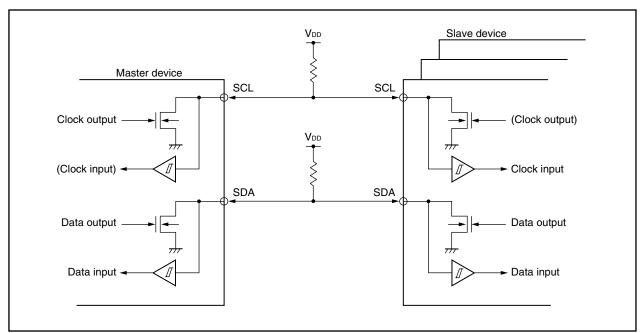

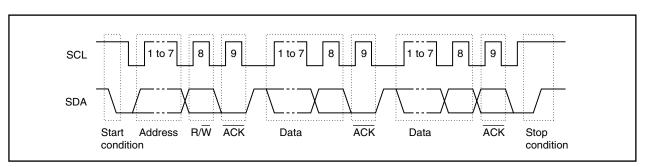

| 10.3    |                  | s (Interface I <sup>2</sup> C)                                                                                 |     |

|         | 10.3.1           | Configuration                                                                                                  |     |

|         | 10.3.2<br>10.3.3 | I <sup>2</sup> C control registers                                                                             |     |

|         |                  | I <sup>2</sup> C bus mode functions                                                                            |     |

|         | 10.3.4<br>10.3.5 | I <sup>2</sup> C bus definitions and control methods                                                           |     |

|         | 10.3.5           | I <sup>2</sup> C interrupt request (INTIIC0)<br>Interrupt request (INTIIC0) generation timing and wait control |     |

|         | 10.3.0           | Address match detection method                                                                                 |     |

|         | 10.3.7           | Error detection                                                                                                |     |

|         | 10.3.9           | Extension code                                                                                                 | -   |

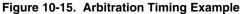

|         |                  | Arbitration                                                                                                    |     |

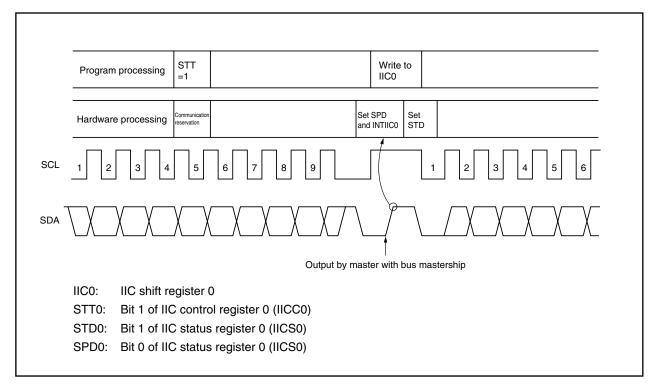

|         |                  | Wakeup function                                                                                                |     |

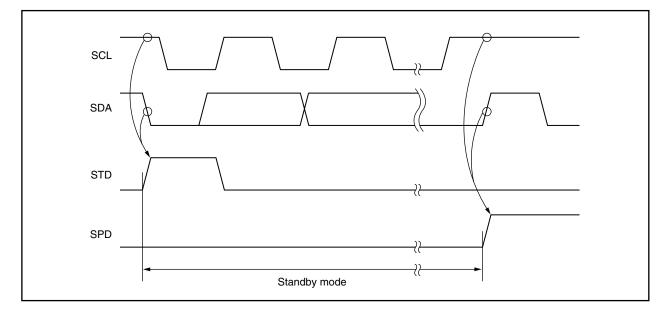

|         |                  | Communication reservation                                                                                      |     |

|         |                  | Cautions                                                                                                       |     |

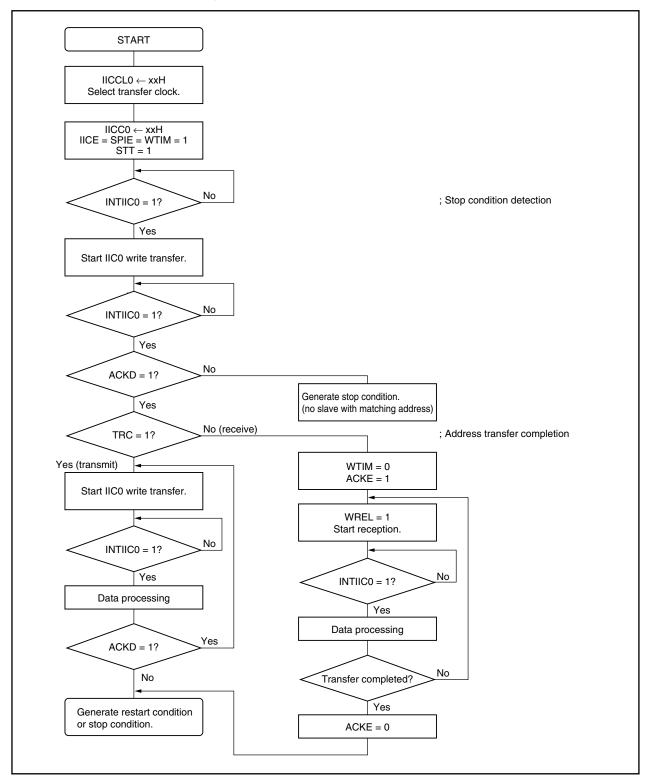

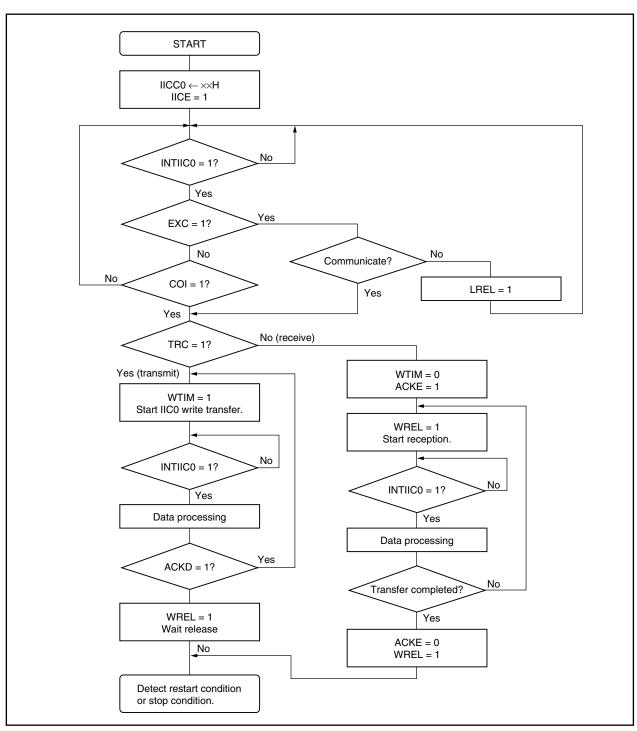

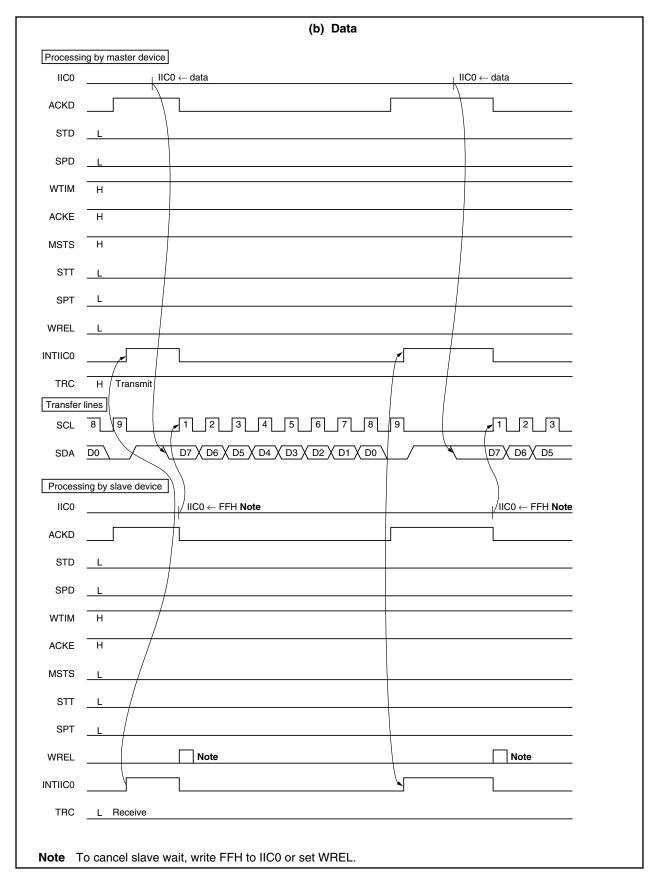

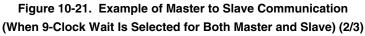

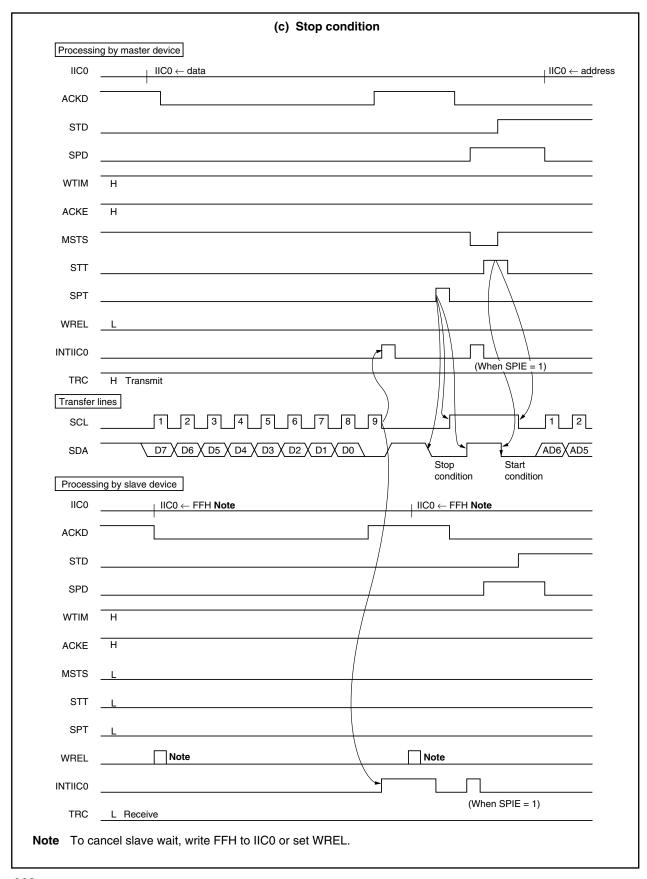

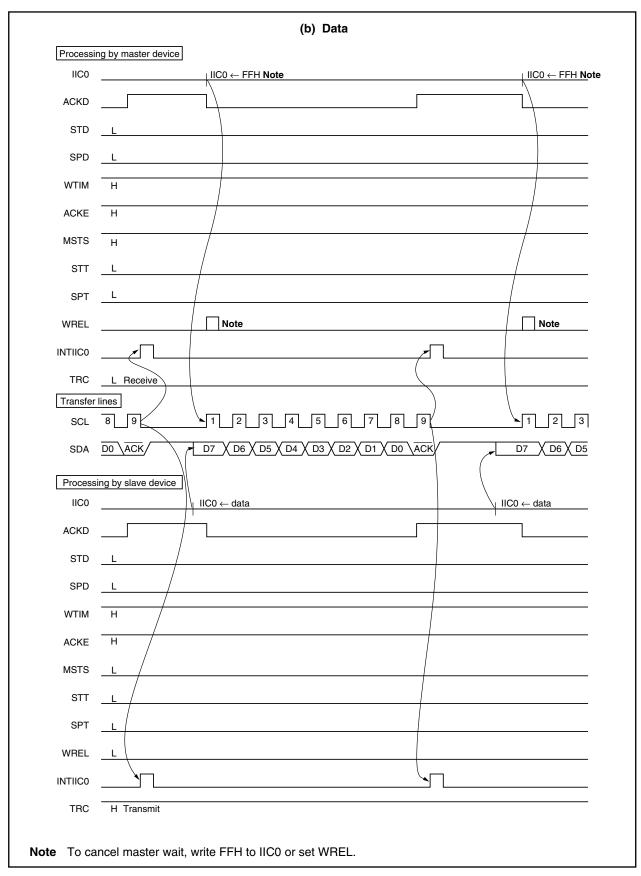

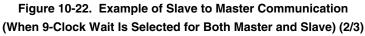

|         |                  | Communication operations                                                                                       |     |

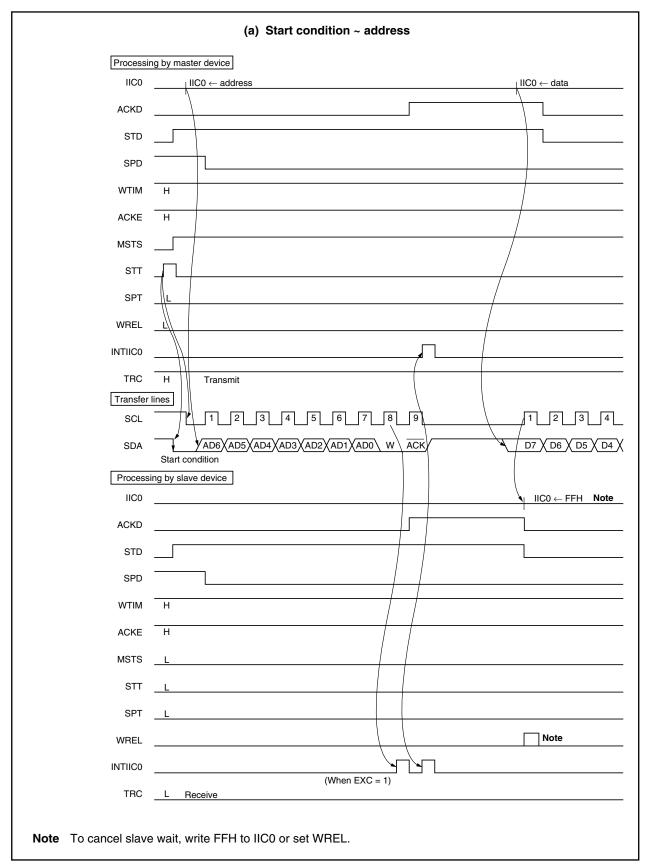

|         |                  | Timing of data communication                                                                                   |     |

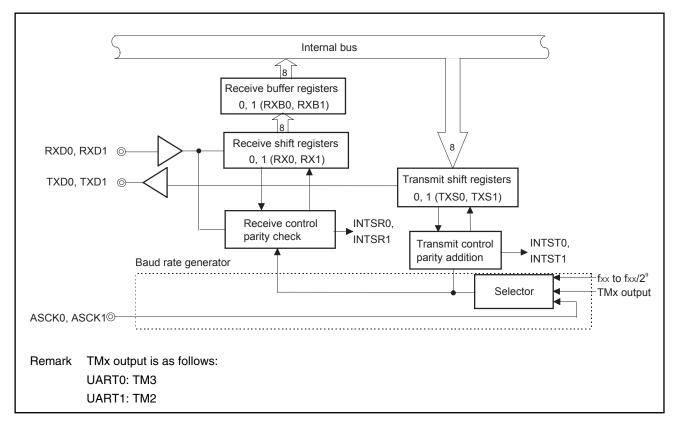

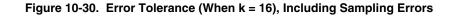

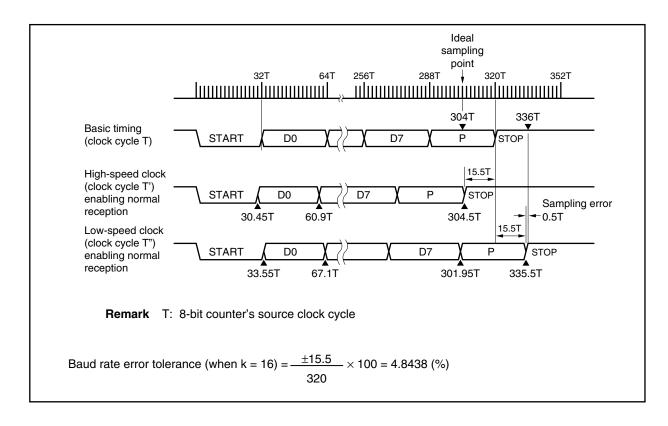

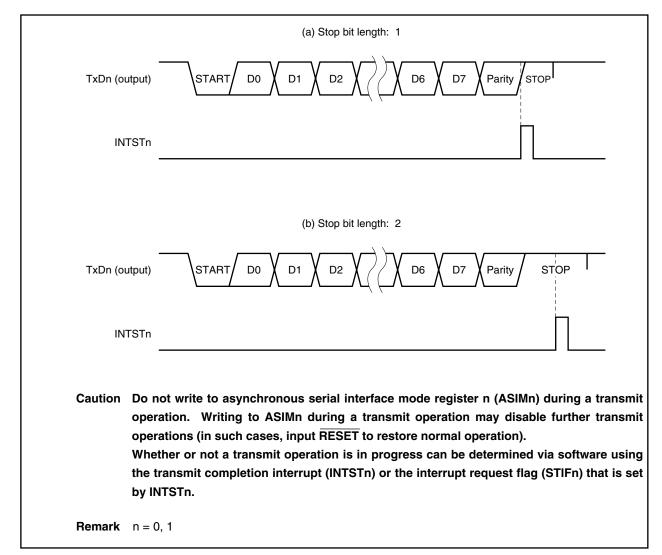

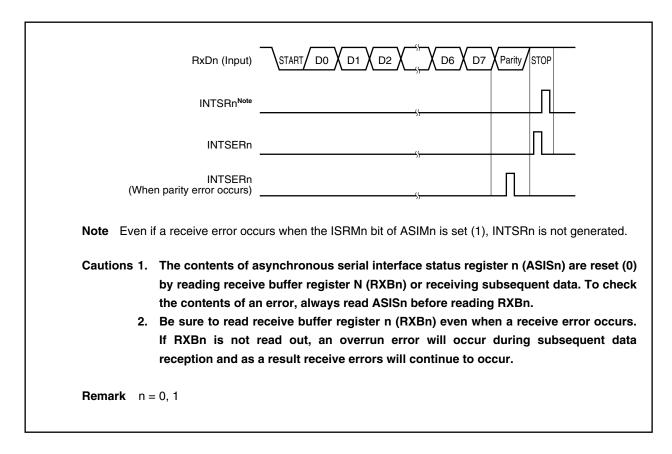

| 10.4    |                  | hronous Serial Interface (UART0, UART1)                                                                        |     |

|         | 10.4.1           | Configuration                                                                                                  |     |

|         | 10.4.2           | UARTn control registers                                                                                        |     |

|         | 10.4.3           | Operations                                                                                                     |     |

|         | 10.4.4           | Standby function                                                                                               |     |

|         |                  |                                                                                                                |     |

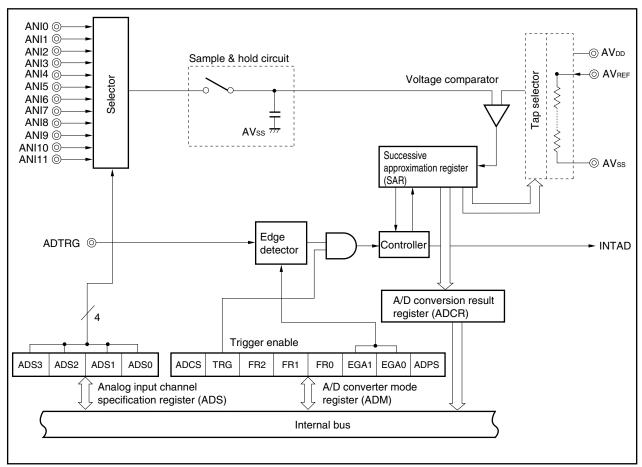

| CHAPTER | R 11 A           | /D CONVERTER                                                                                                   | 308 |

| 11.1    | Function         | on                                                                                                             |     |

|   | 11.4    | Operation                                           | 316  |

|---|---------|-----------------------------------------------------|------|

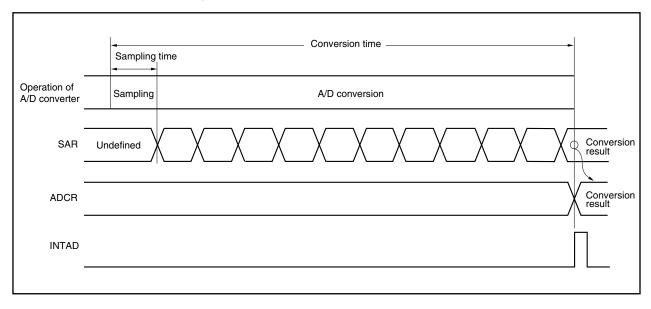

|   |         | 11.4.1 Basic operation                              |      |

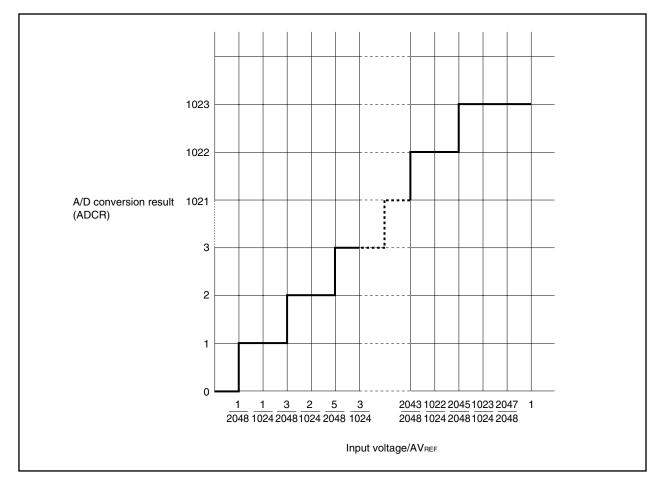

|   |         | 11.4.2 Input voltage and conversion result          |      |

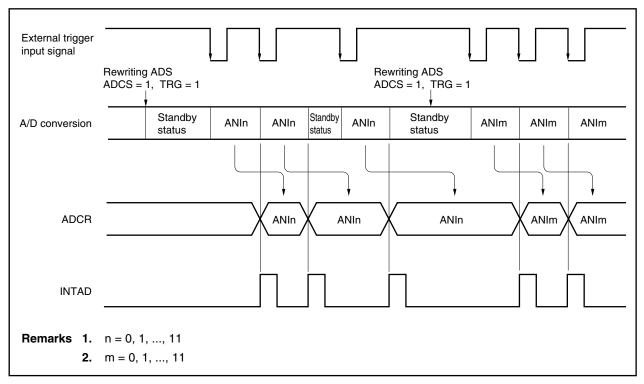

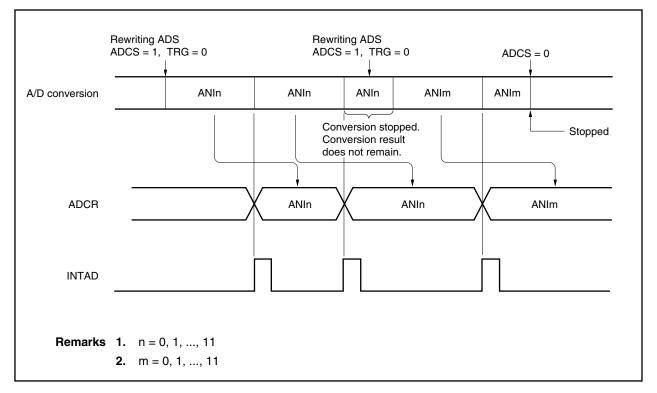

|   |         | 11.4.3 A/D converter operation mode                 |      |

|   | 11.5    | Notes on Using A/D Converter                        | 322  |

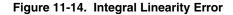

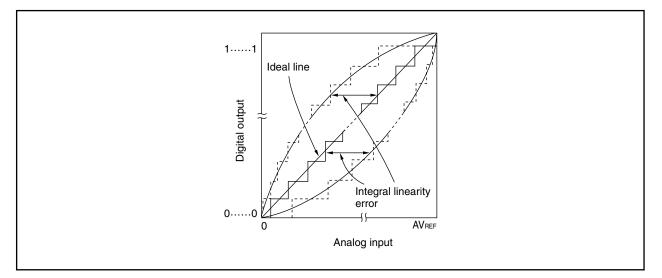

| * | 11.6    | How to Read A/D Converter Characteristics Table     | 326  |

|   |         |                                                     |      |

|   | CHAPTER | R 12 DMA FUNCTIONS                                  | 330  |

|   | 12.1    | Functions                                           | 330  |

| * | 12.2    | Features                                            | 330  |

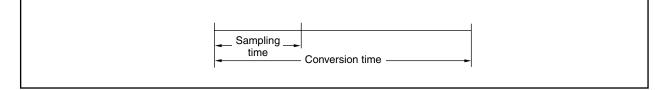

| * | 12.3    | Configuration                                       | 331  |

|   | 12.4    | Control Registers                                   | 332  |

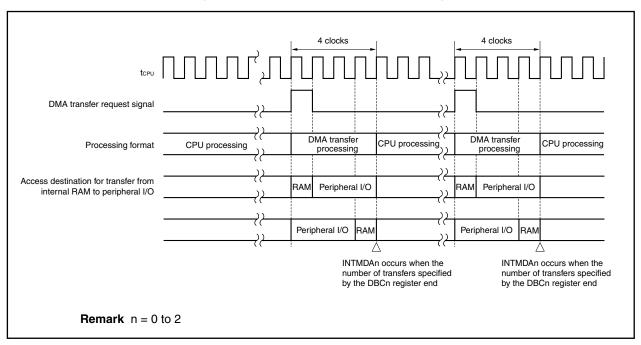

| * | 12.5    | Operation                                           | 338  |

| * | 12.6    | Cautions                                            | 339  |

|   |         |                                                     |      |

|   | CHAPTER | R 13 REAL-TIME OUTPUT FUNCTION (RTO)                | 340  |

|   | 13.1    | Function                                            | 340  |

| * | 13.2    | Features                                            | 340  |

|   | 13.3    | Configuration                                       | 341  |

|   |         | Control Registers                                   |      |

|   |         | Usage                                               |      |

|   |         | Operation                                           |      |

|   | 13.7    | Cautions                                            | 347  |

|   |         | R 14 PORT FUNCTION                                  | 0.40 |

|   |         |                                                     |      |

|   |         | Port Configuration                                  |      |

|   | 14.2    | Port Pin Function                                   |      |

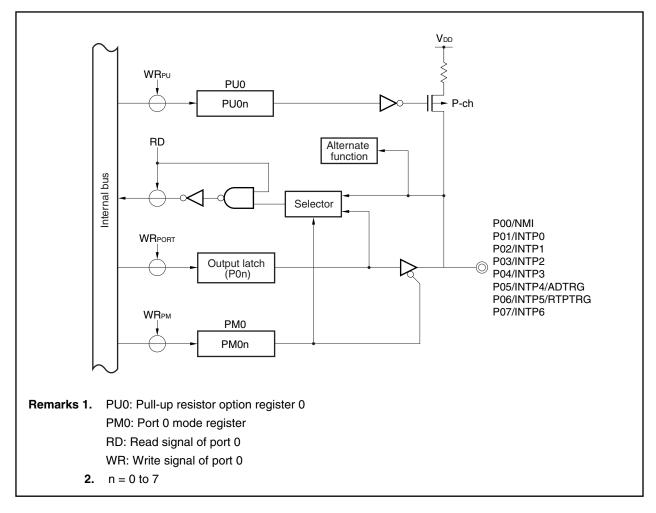

|   |         | 14.2.1 Port 0                                       |      |

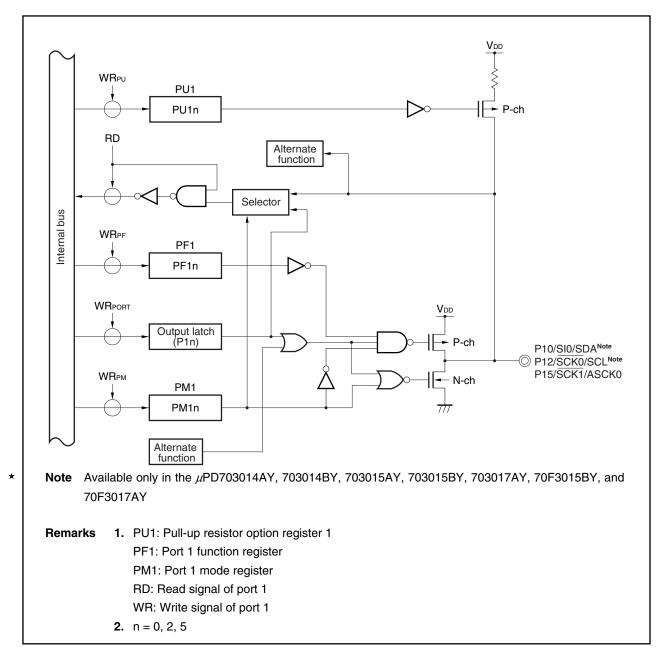

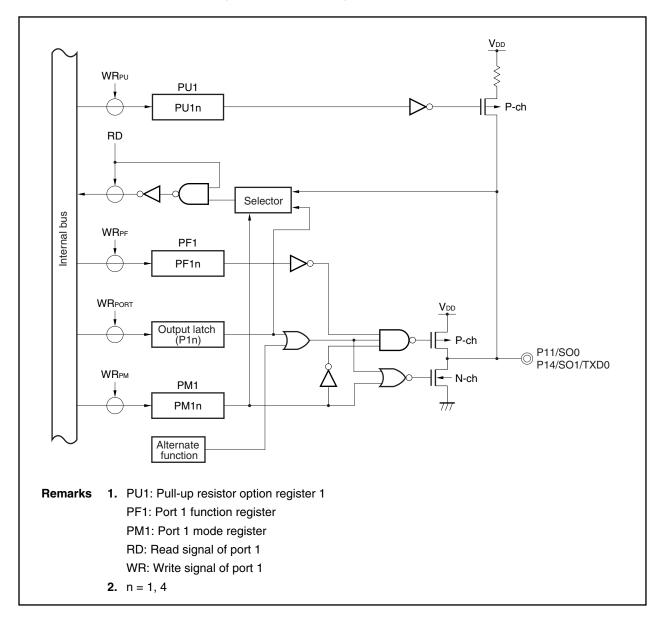

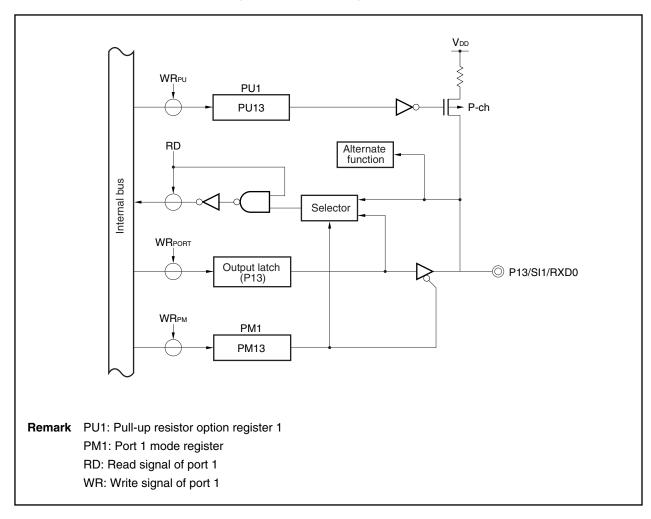

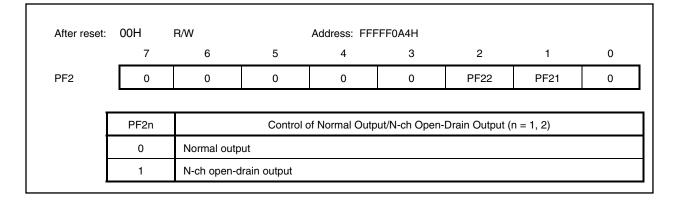

|   |         | 14.2.2 Port 1                                       |      |

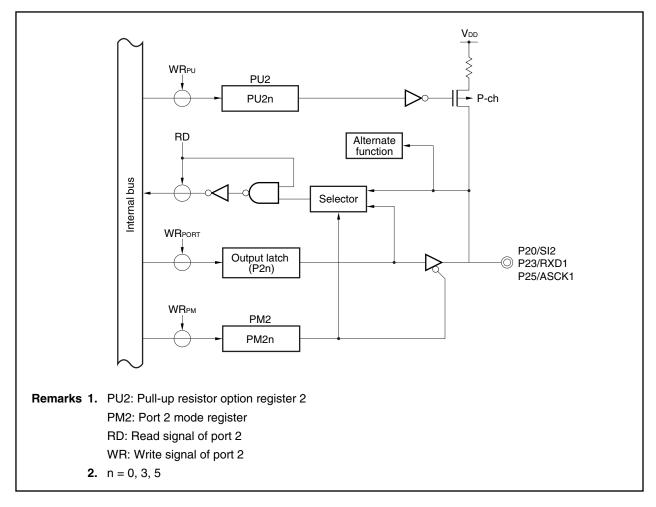

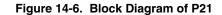

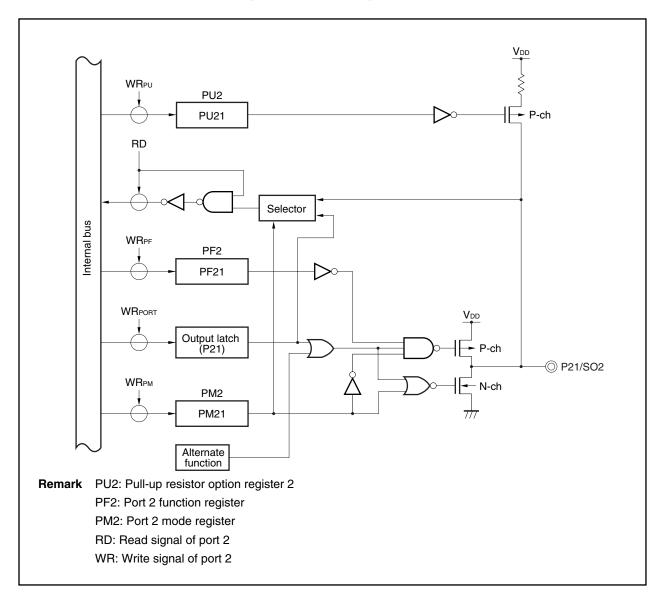

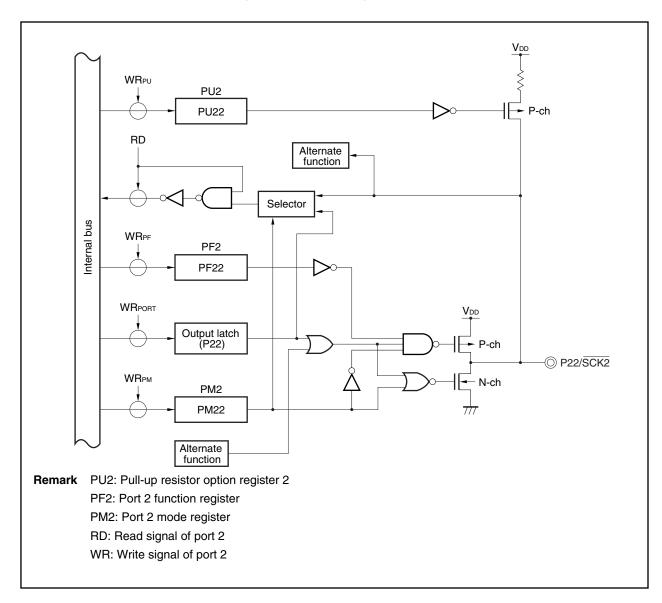

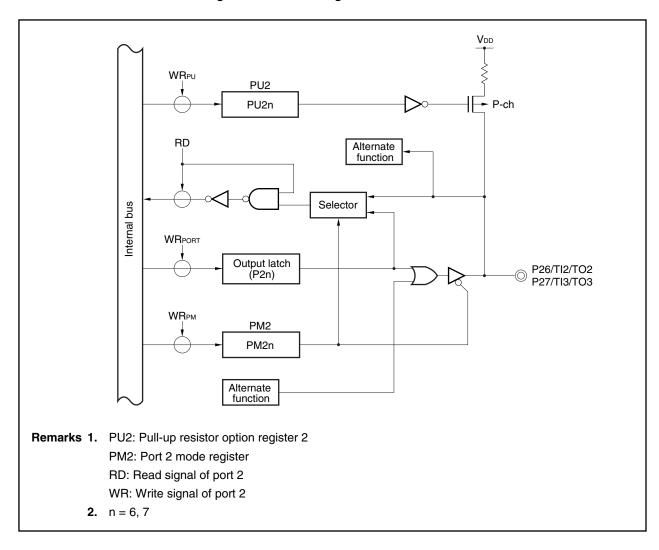

|   |         | 14.2.3 Port 2                                       |      |

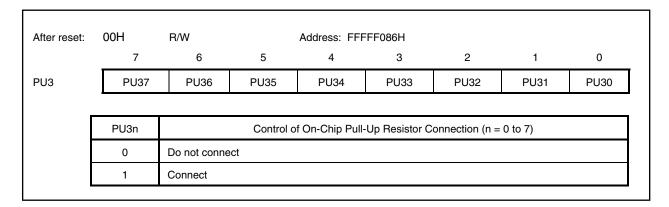

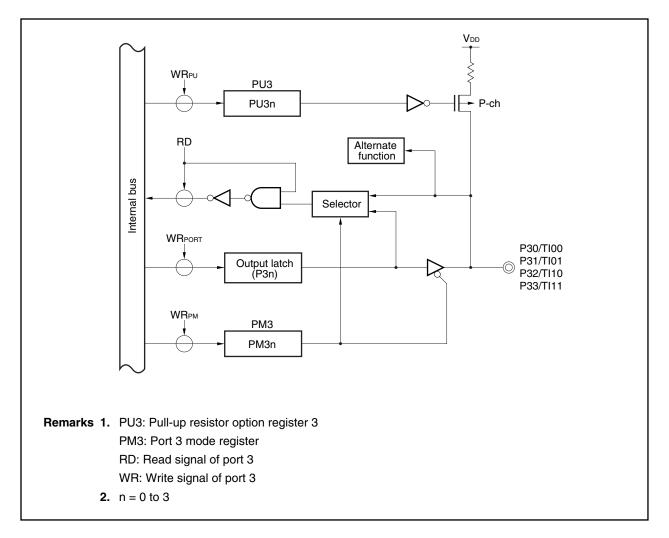

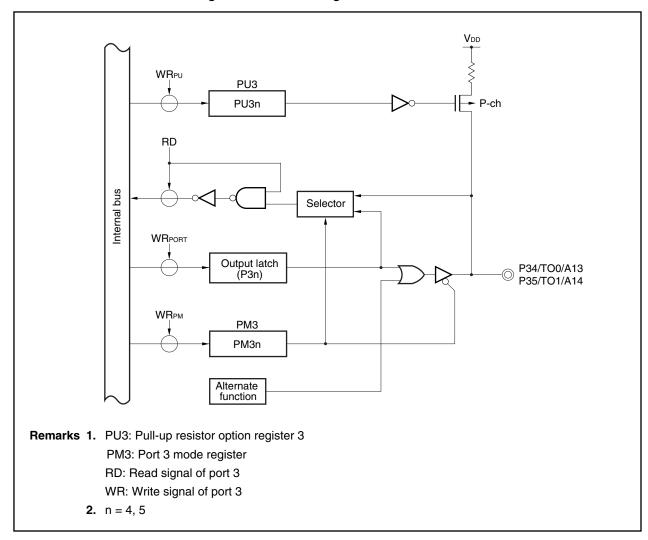

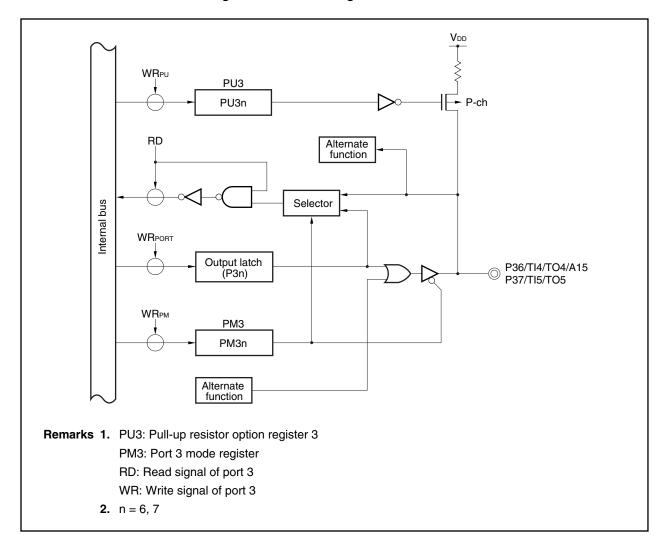

|   |         | 14.2.4 Port 3                                       |      |

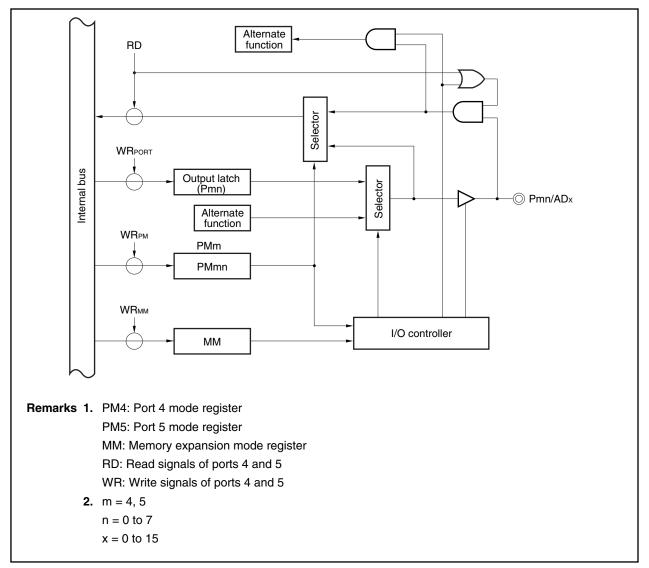

|   |         | 14.2.5 Ports 4 and 5                                | -    |

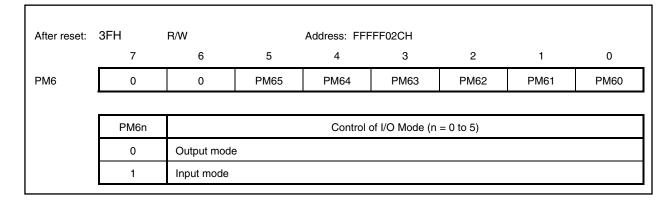

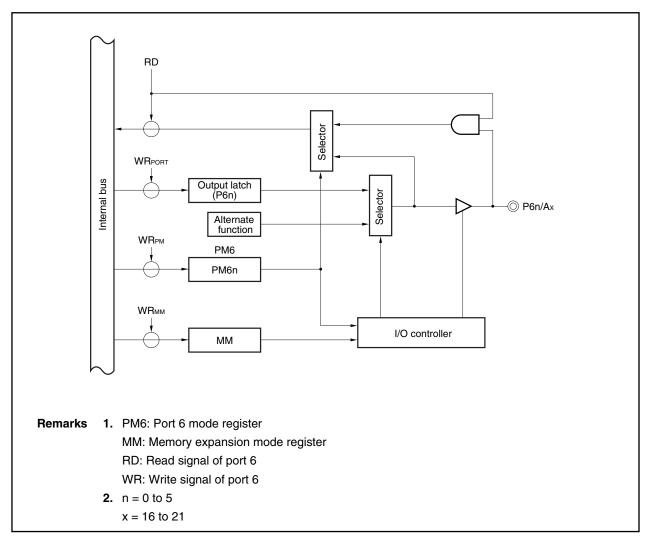

|   |         | 14.2.6 Port 6                                       |      |

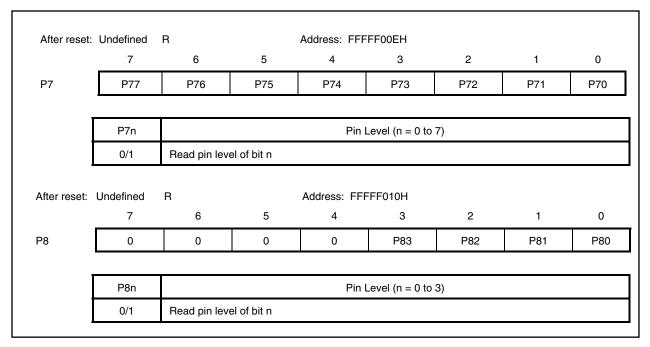

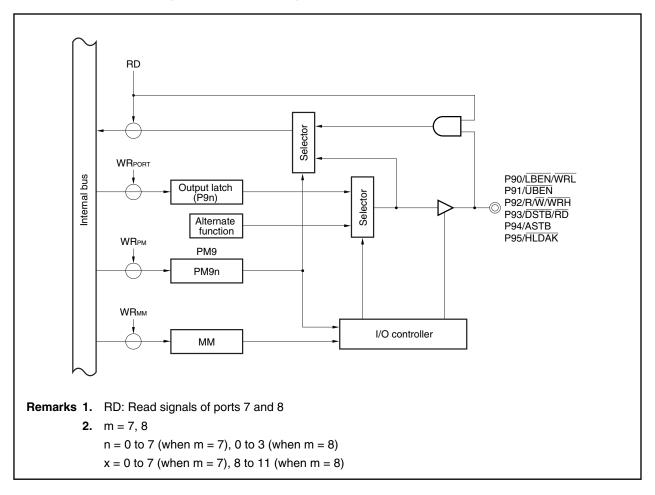

|   |         | 14.2.7 Ports 7 and 8                                |      |

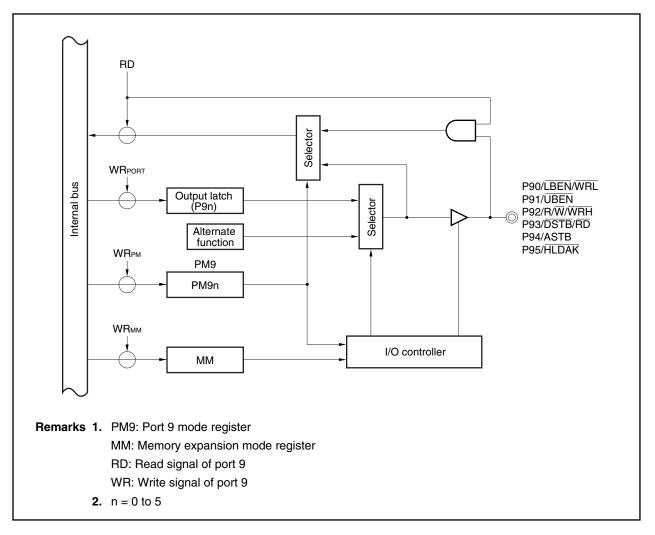

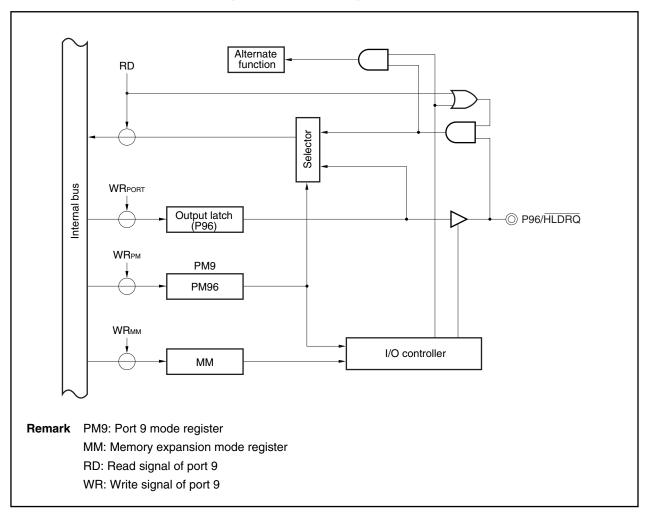

|   |         | 14.2.8 Port 9                                       |      |

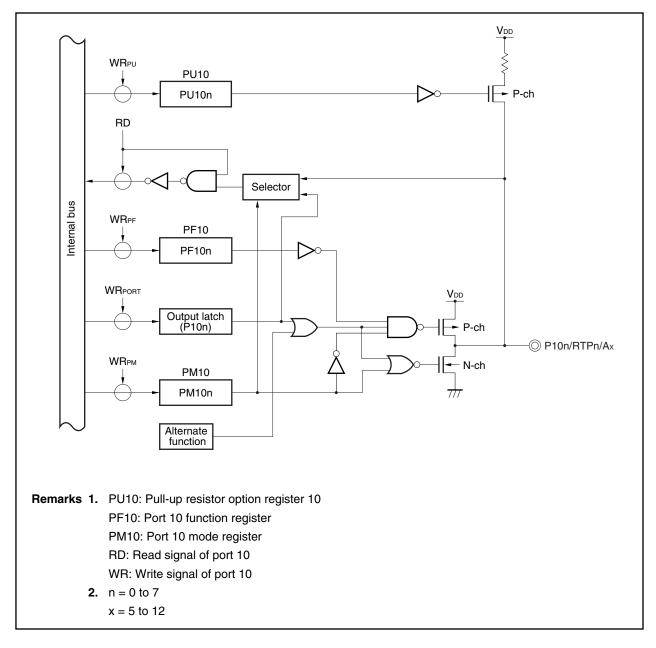

|   |         | 14.2.9 Port 10                                      |      |

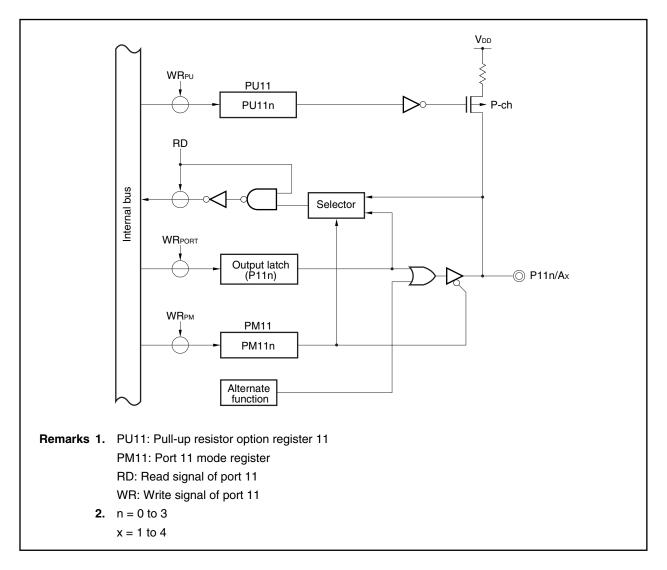

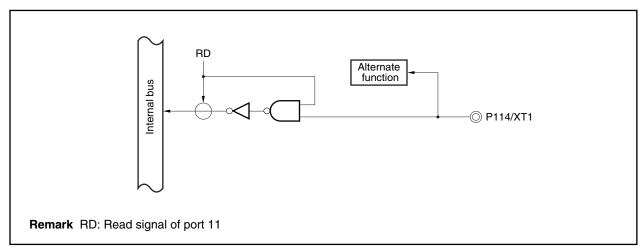

|   |         | 14.2.10 Port 11                                     |      |

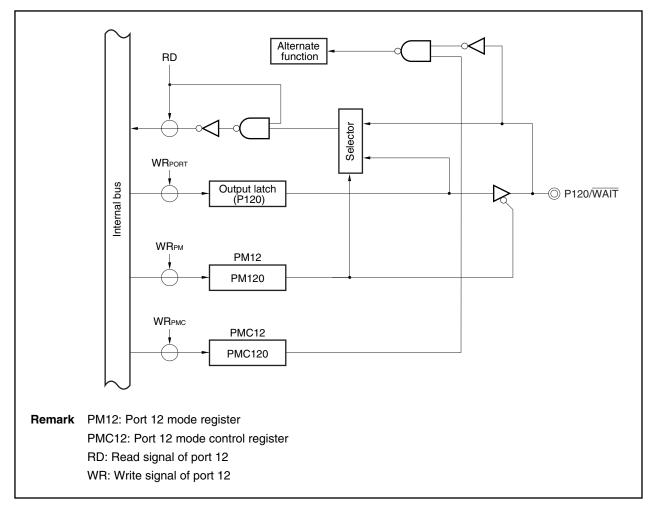

|   |         | 14.2.11 Port 12                                     |      |

|   |         | Setting When Port Pin Is Used as Alternate Function |      |

| * | 14.4    | Operation of Port Function                          |      |

|   |         | 14.4.1 Writing data to I/O port                     |      |

|   |         | 14.4.2 Reading data from I/O port                   |      |

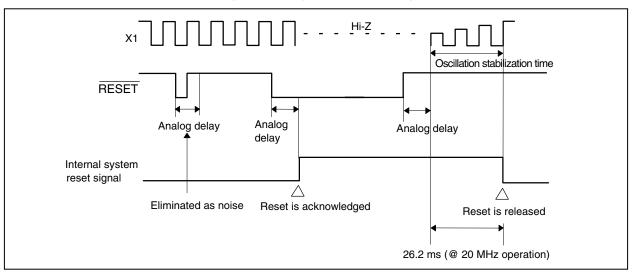

| CHAPTEF   | R 15 R            | ESET FUNCTION                                                 | 397 |

|-----------|-------------------|---------------------------------------------------------------|-----|

| 15.1      | Genera            | ۱                                                             | 397 |

| 15.2      | Pin Op            | erations                                                      | 397 |

|           |                   |                                                               |     |

| CHAPTER   | 8 16 FI           | _ASH MEMORY                                                   |     |

|           |                   |                                                               |     |

| 16.1      |                   | es                                                            |     |

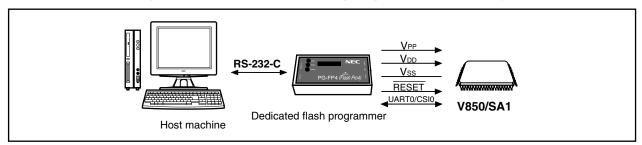

| 16.2      | 16.1.1<br>Writing | Erasing unit<br>by Flash Programmer                           |     |

| 16.3      | -                 | mming Environment                                             |     |

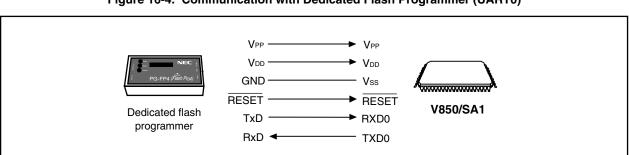

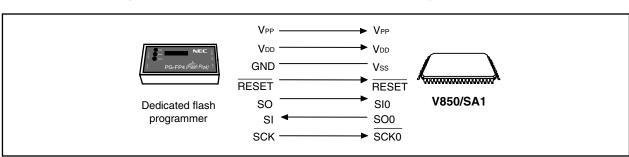

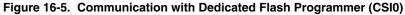

| 16.4      | -                 | unication System                                              |     |

| 16.5      |                   | nnection                                                      |     |

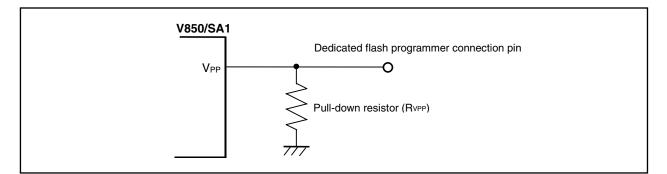

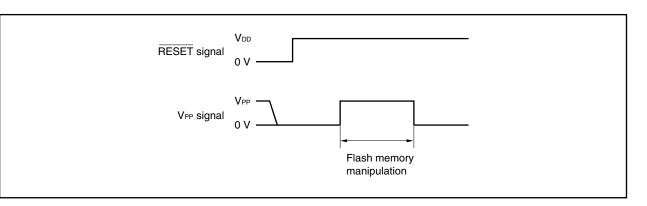

|           | 16.5.1            | VPP pin                                                       |     |

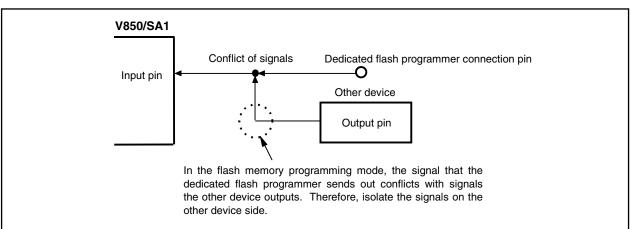

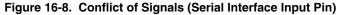

|           | 16.5.2            | Serial interface pin                                          |     |

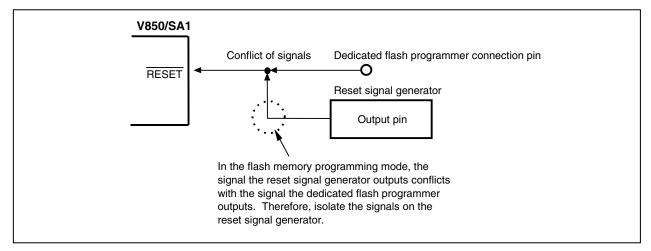

|           | 16.5.3            | RESET pin                                                     |     |

|           | 16.5.4            | Port pin (including NMI)                                      | 409 |

|           | 16.5.5            | Other signal pins                                             | 409 |

|           | 16.5.6            | Power supply                                                  | 409 |

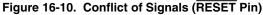

| 16.6      | Progra            | mming Method                                                  | 410 |

|           | 16.6.1            | Flash memory control                                          | 410 |

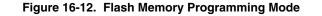

|           | 16.6.2            | Flash memory programming mode                                 |     |

|           | 16.6.3            | Selection of communication mode                               |     |

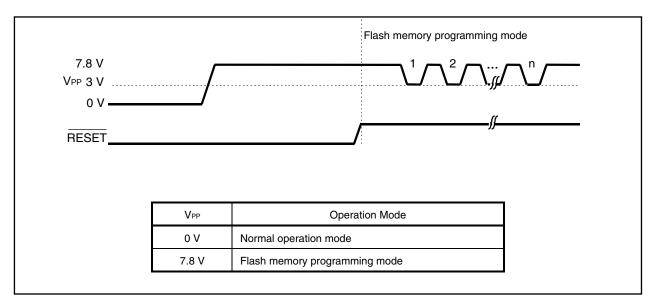

|           | 16.6.4            | Communication command                                         |     |

|           | 16.6.5            | Resources used                                                |     |

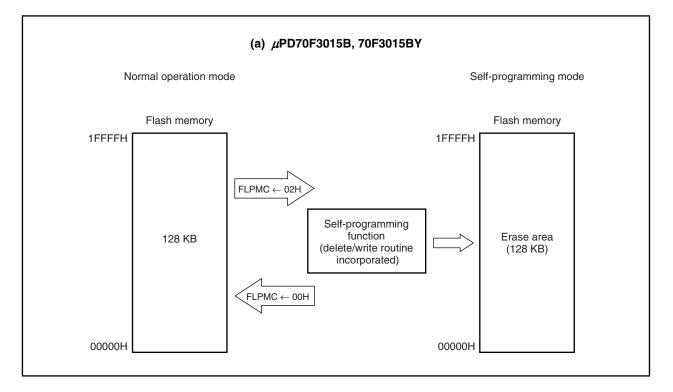

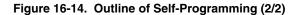

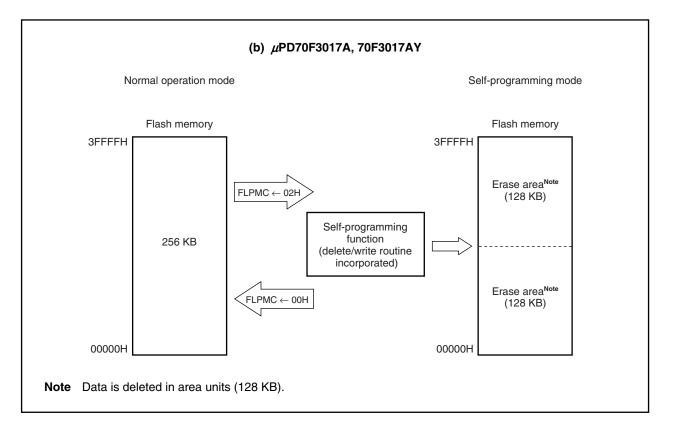

| * 16.7    |                   | Memory Programming by Self-Programming                        |     |

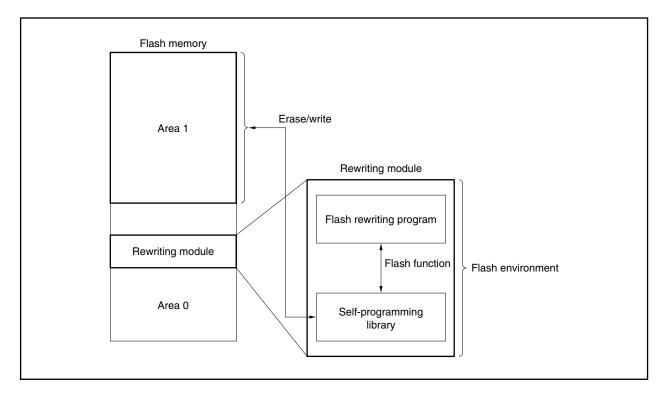

|           | 16.7.1            | Outline of self-programming                                   |     |

|           | 16.7.2            | Self-programming function                                     |     |

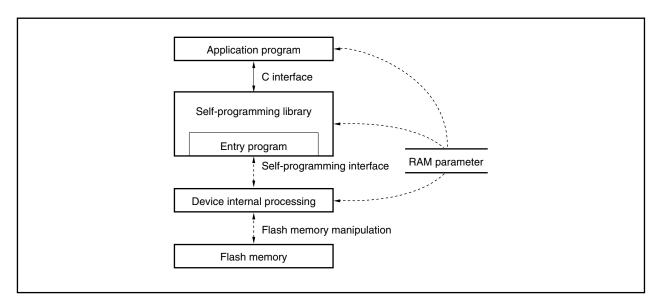

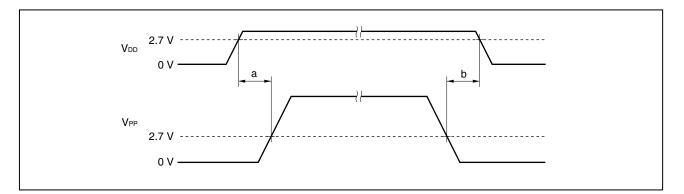

|           | 16.7.3<br>16.7.4  | Outline of self-programming interface<br>Hardware environment |     |

|           | 16.7.4            | Software environment                                          |     |

|           | 16.7.6            | Software environment                                          |     |

|           | 16.7.7            | Calling parameters                                            |     |

|           | 16.7.8            | Contents of RAM parameters                                    |     |

|           | 16.7.9            | Errors during self-programming                                |     |

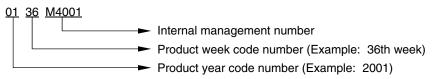

|           | 16.7.10           | Flash information                                             |     |

|           | 16.7.11           | Area number                                                   | 422 |

|           | 16.7.12           | Flash programming mode control register (FLPMC)               | 423 |

|           | 16.7.13           | Calling device internal processing                            | 425 |

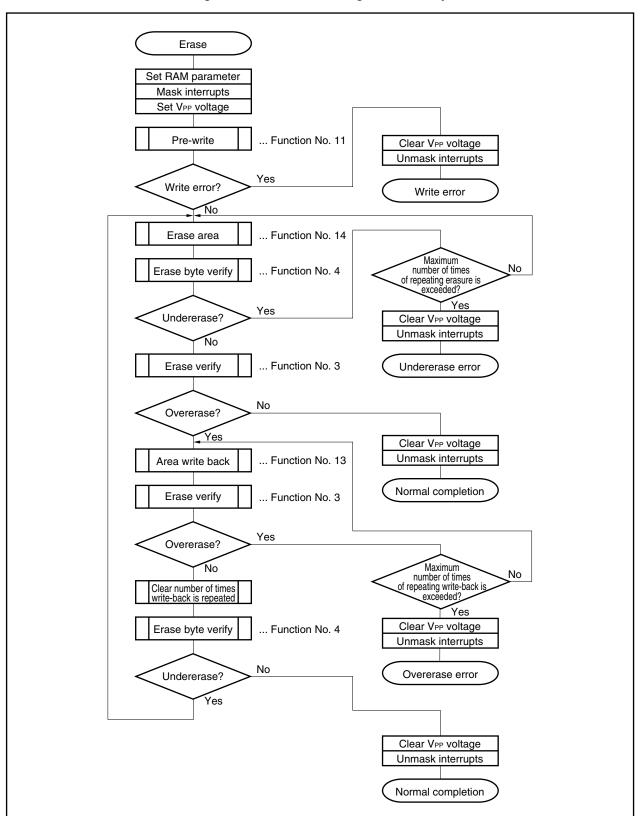

|           | 16.7.14           | Flow of erasing flash memory                                  | 428 |

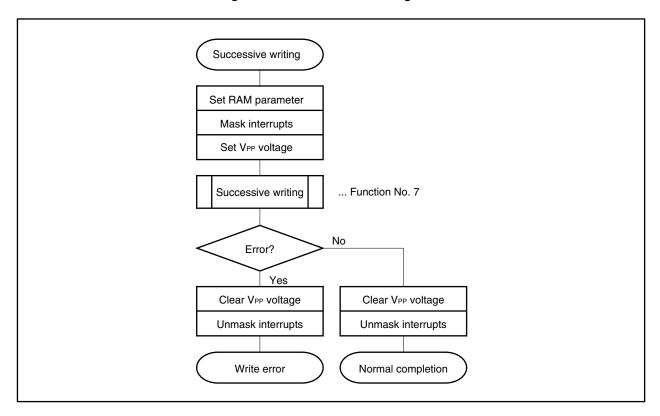

|           |                   | Successive writing flow                                       |     |

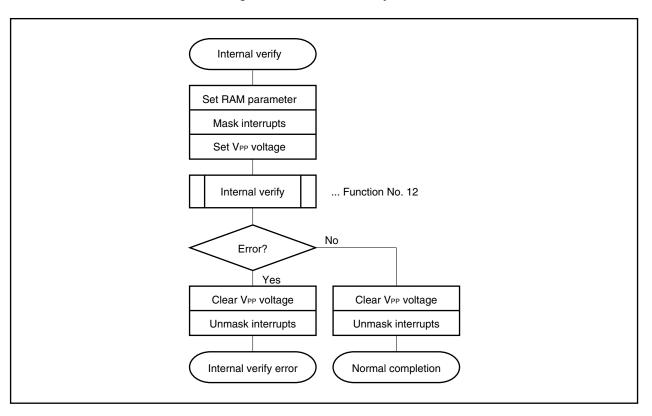

|           |                   | Internal verify flow                                          |     |

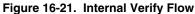

|           |                   | Flow of acquiring flash information                           |     |

|           | 16.7.18           | Self-programming library                                      | 432 |

|           |                   |                                                               |     |

|           | R 17 E            | LECTRICAL SPECIFICATIONS                                      | 434 |

|           | ) 10 F            |                                                               | 400 |

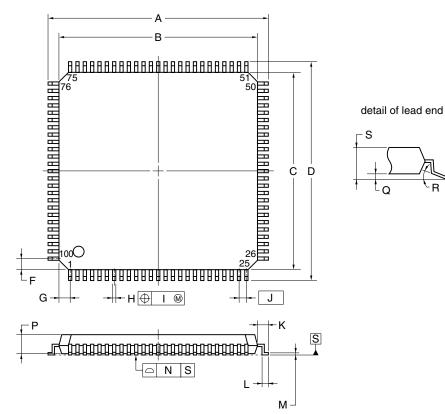

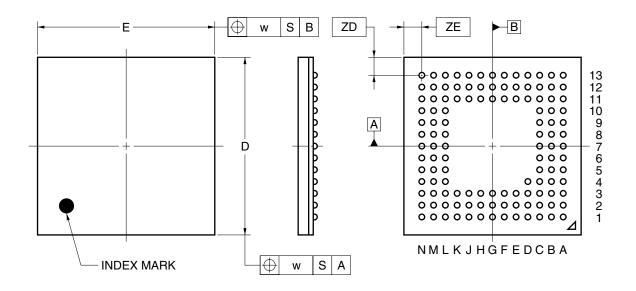

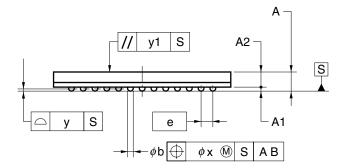

| * CHAPIEF | ι ιδ Ρ            | ACKAGE DRAWINGS                                               | 460 |

| * | CHAPTER 19 | RECOMMENDED SOLDERING CONDITIONS | 462 |

|---|------------|----------------------------------|-----|

| * | APPENDIX A | NOTES ON TARGET SYSTEM DESIGN    | 466 |

|   | APPENDIX B | REGISTER INDEX                   | 468 |

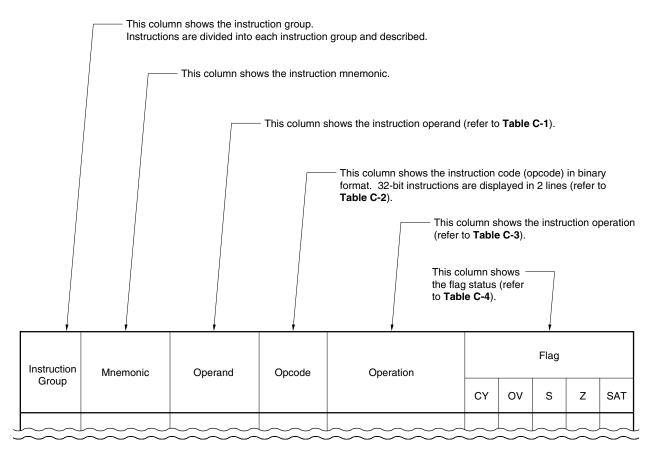

|   | APPENDIX C | LIST OF INSTRUCTION SETS         | 473 |

|   | APPENDIX D | INDEX                            | 480 |

| * | APPENDIX E | REVISION HISTORY                 | 486 |

# LIST OF FIGURES (1/6)

| Figure | e No. Title                                                    | Title Page |  |  |

|--------|----------------------------------------------------------------|------------|--|--|

| 3-1    | CPU Register Set                                               | 60         |  |  |

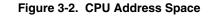

| 3-2    | CPU Address Space                                              |            |  |  |

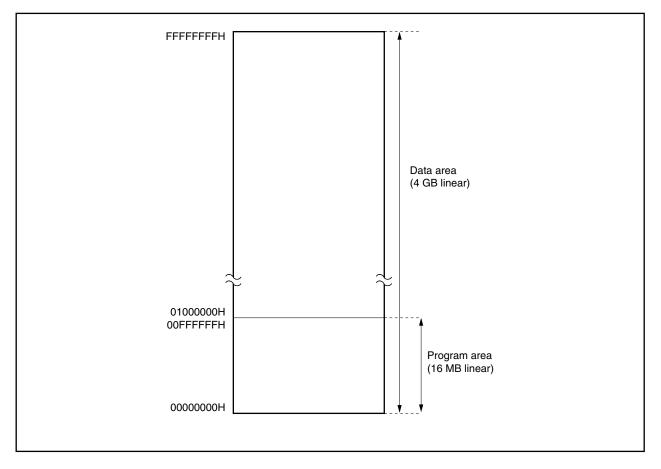

| 3-3    | Image on Address Space                                         |            |  |  |

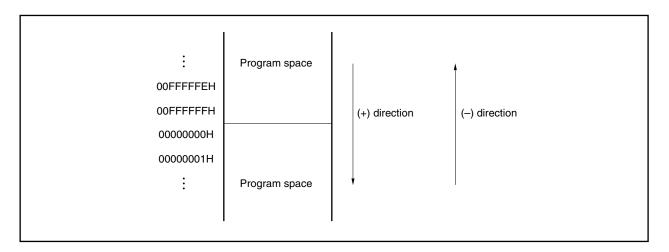

| 3-4    | Program Space                                                  |            |  |  |

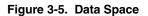

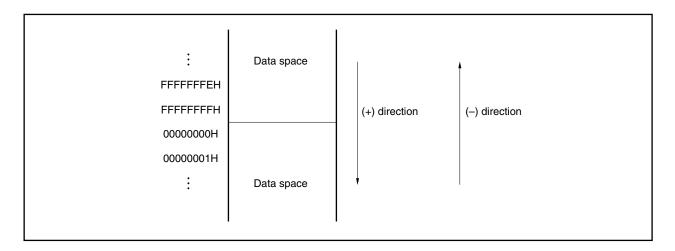

| 3-5    | Data Space                                                     |            |  |  |

| 3-6    | Memory Map                                                     |            |  |  |

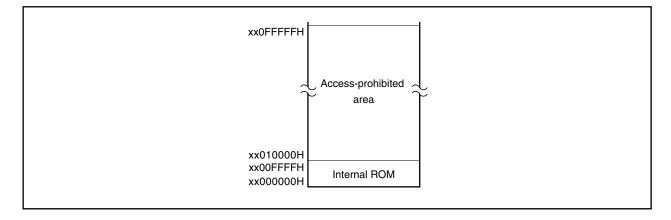

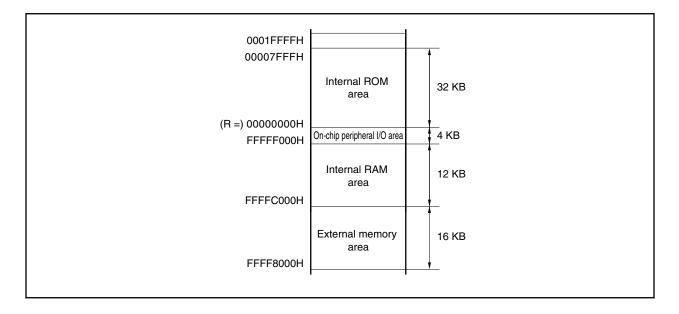

| 3-7    | Internal ROM Area (64 KB)                                      |            |  |  |

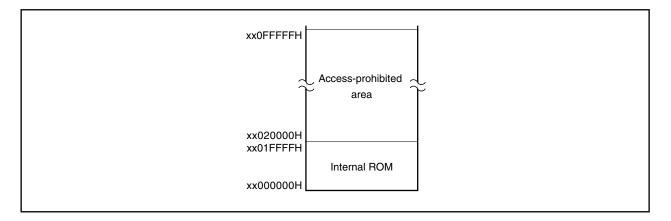

| 3-8    | Internal ROM Area (128 KB)                                     |            |  |  |

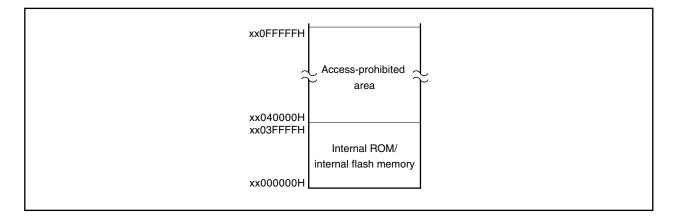

| 3-9    | Internal ROM/Internal Flash Memory Area (256 KB)               |            |  |  |

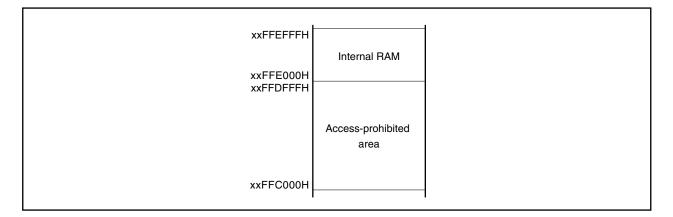

| 3-10   | Internal RAM Area (4 KB)                                       |            |  |  |

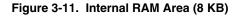

| 3-11   | Internal RAM Area (8 KB)                                       |            |  |  |

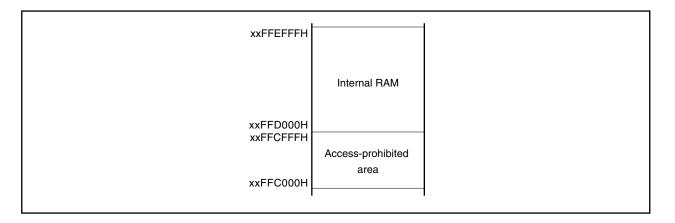

| 3-12   | On-Chip Peripheral I/O Area                                    |            |  |  |

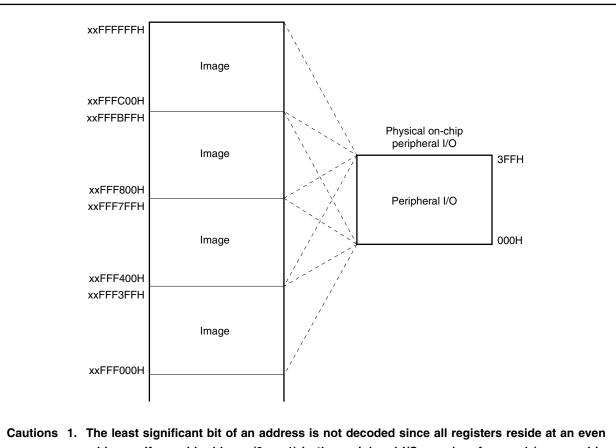

| 3-13   | External Memory Area (When Expanded to 64 KB, 256 KB, or       | 1 MB)75    |  |  |

| 3-14   | External Memory Area (When Expanded to 4 MB)                   |            |  |  |

| 3-15   | Application Example of Wraparound                              |            |  |  |

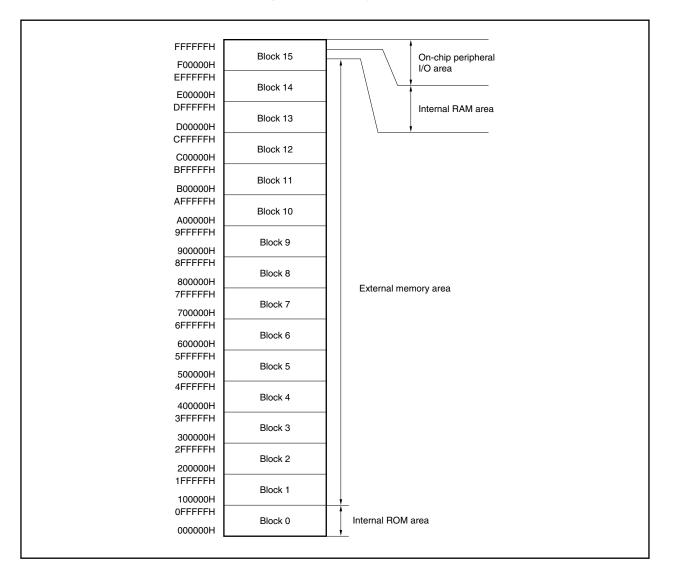

| 3-16   | Recommended Memory Map                                         | 80         |  |  |

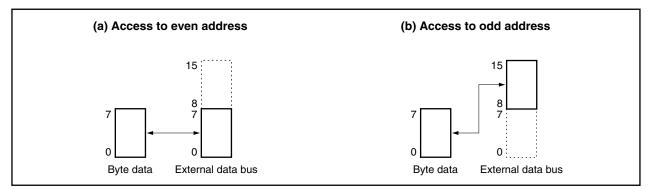

| 4-1    | Byte Access (8 Bits)                                           |            |  |  |

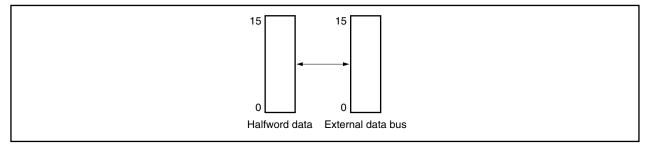

| 4-2    | Halfword Access (16 Bits)                                      | 91         |  |  |

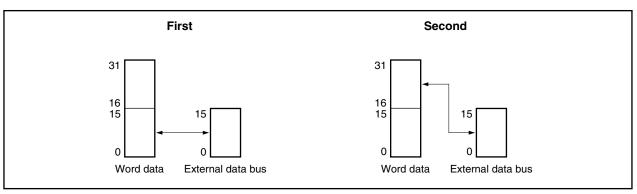

| 4-3    | Word Access (32 Bits)                                          | 91         |  |  |

| 4-4    | Memory Space                                                   |            |  |  |

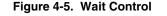

| 4-5    | Wait Control                                                   |            |  |  |

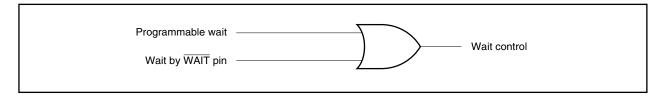

| 4-6    | Example of Inserting Wait States                               |            |  |  |

| 4-7    | Bus Hold Procedure                                             |            |  |  |

| 4-8    | Memory Read                                                    |            |  |  |

| 4-9    | Memory Write                                                   |            |  |  |

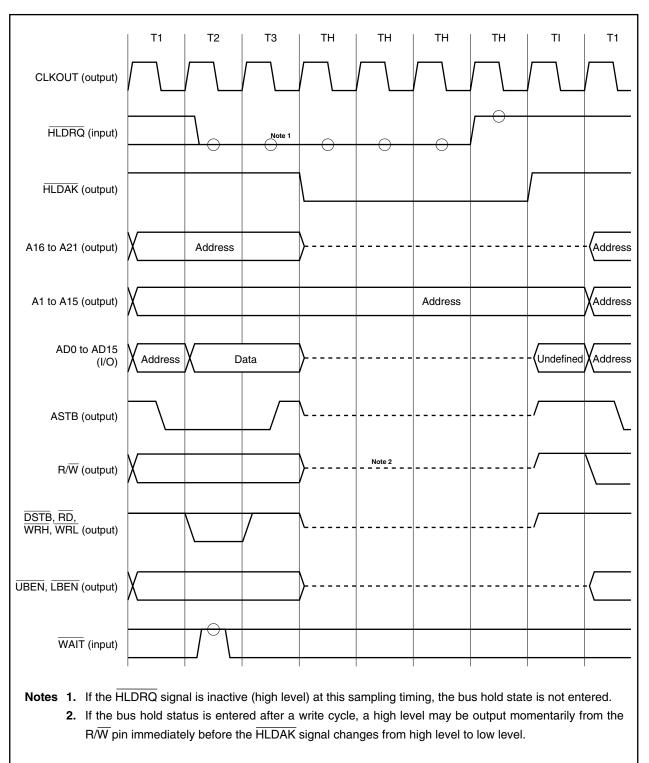

| 4-10   | Bus Hold Timing                                                |            |  |  |

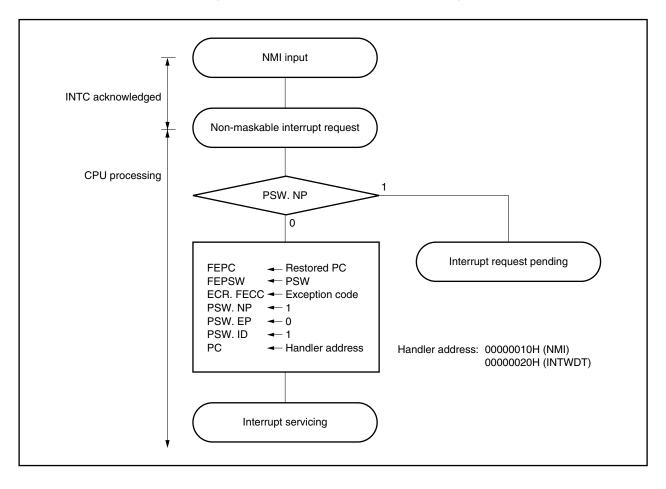

| 5-1    | Non-Maskable Interrupt Servicing                               |            |  |  |

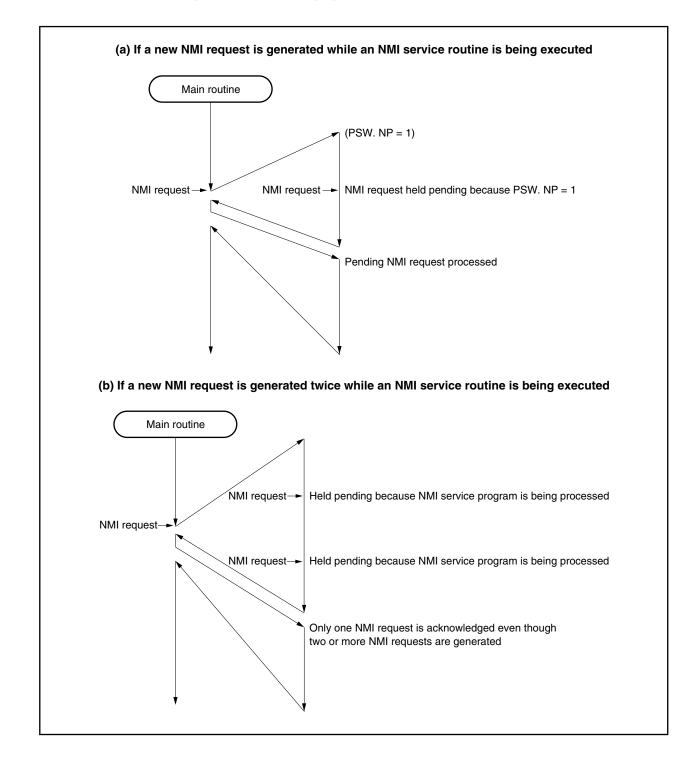

| 5-2    | Acknowledging Non-Maskable Interrupt Request                   |            |  |  |

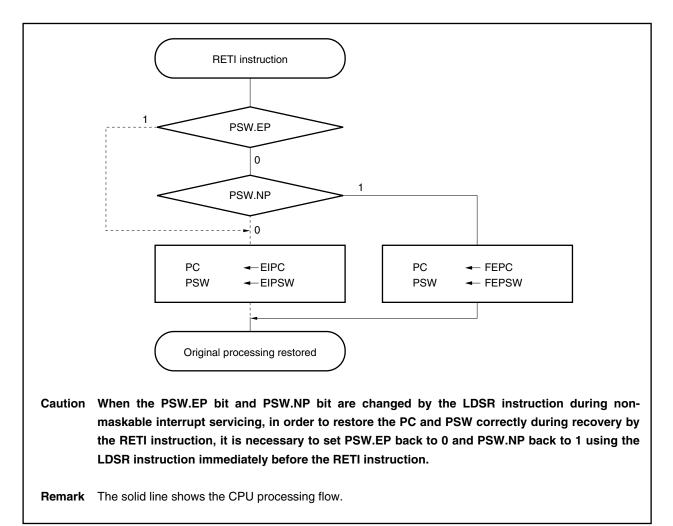

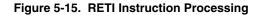

| 5-3    | RETI Instruction Processing                                    |            |  |  |

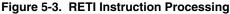

| 5-4    | NP Flag (NP)                                                   |            |  |  |

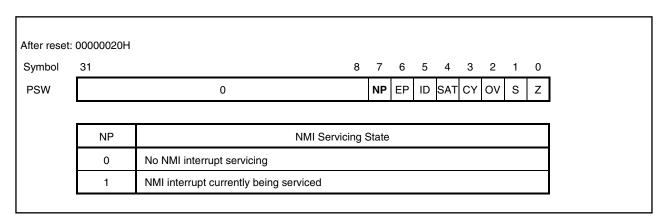

| 5-5    | Maskable Interrupt Servicing                                   |            |  |  |

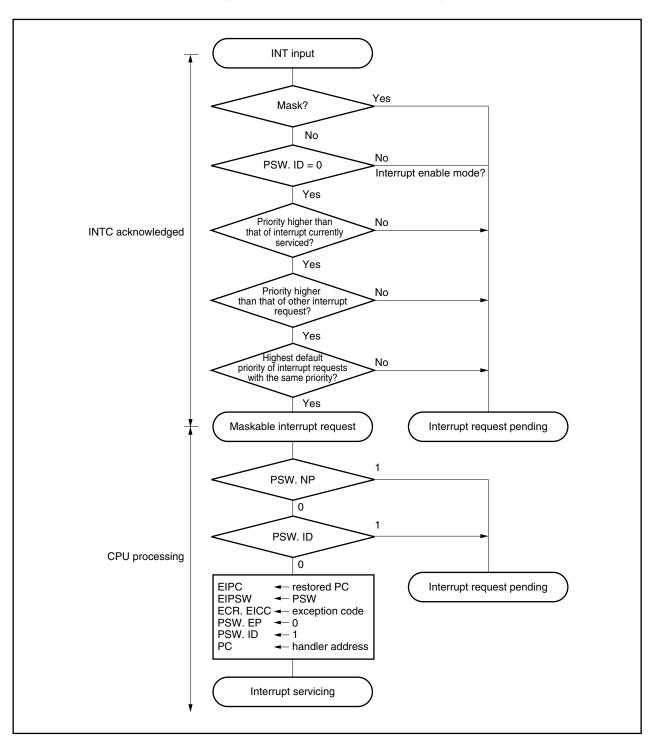

| 5-6    | RETI Instruction Processing                                    |            |  |  |

| 5-7    | Example of Multiple Interrupt Servicing                        |            |  |  |

| 5-8    | Example of Servicing Interrupt Requests Generated Simultaneous | ously121   |  |  |

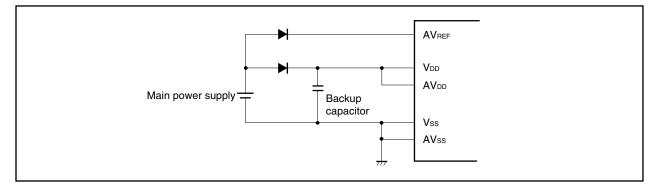

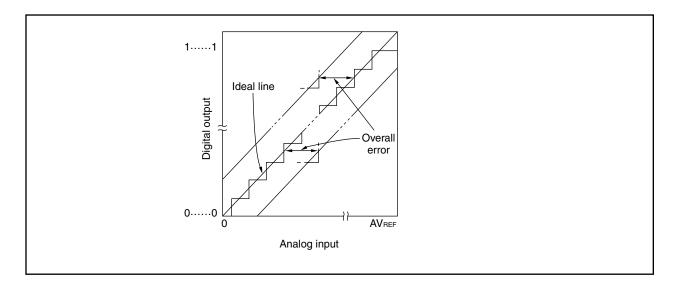

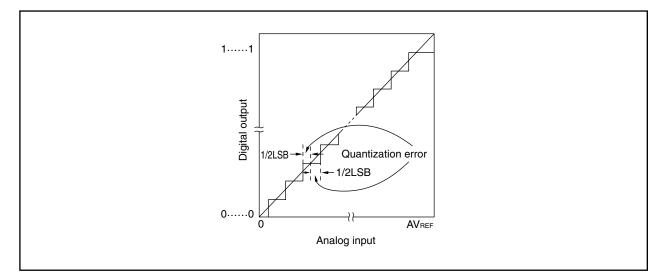

| 5-9    | Interrupt Disable Flag (ID)                                    |            |  |  |