# DATA SHEET

# MOS INTEGRATED CIRCUIT **μPD17053**

# ON-CHIP IMAGE DISPLAY CONTROLLER 4-BIT SINGLE-CHIP MICROCONTROLLER FOR VOLTAGE SYNTHESIZER

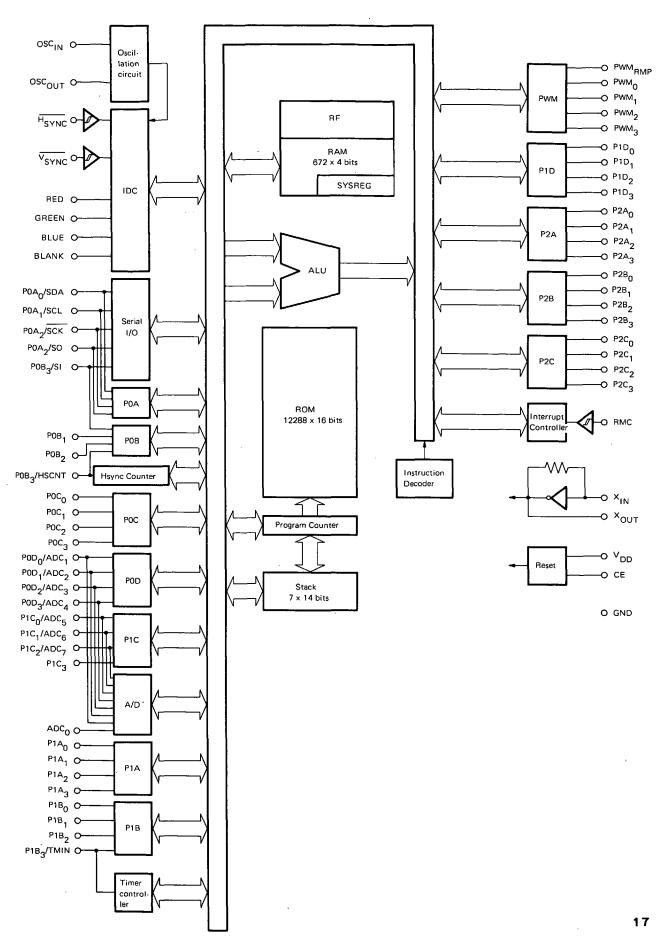

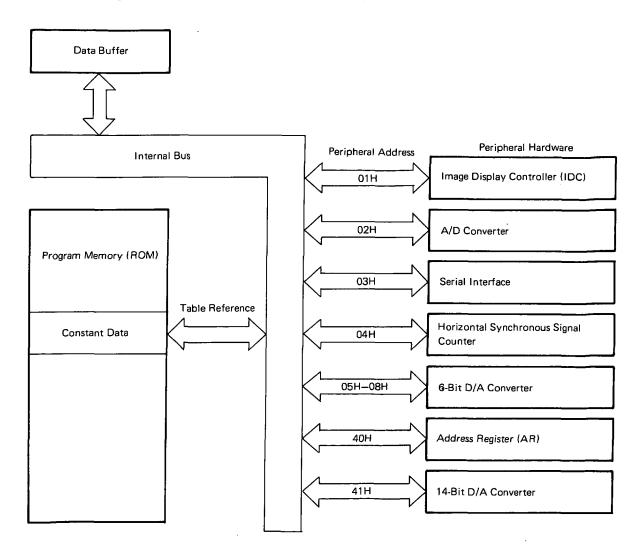

μPD17053 includes the image display controller (IDC) which is capable of various displays and the 4-bit singlechip microcontroller for the voltage synthesizer in which the 14-bit D/A converter for voltage synthesizer is incorporated.

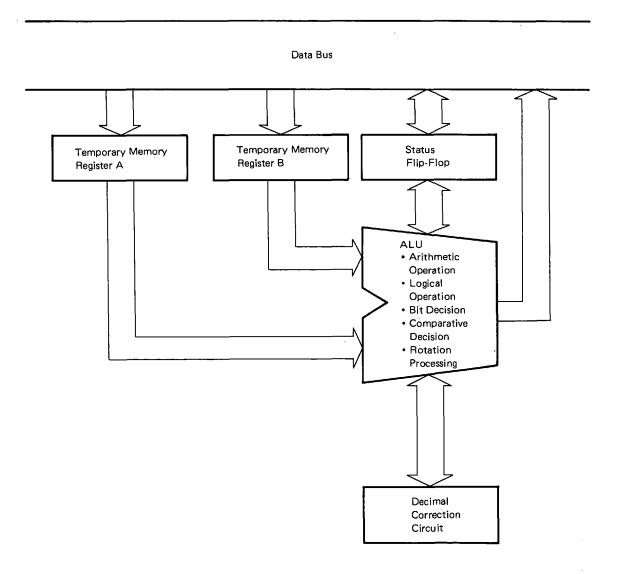

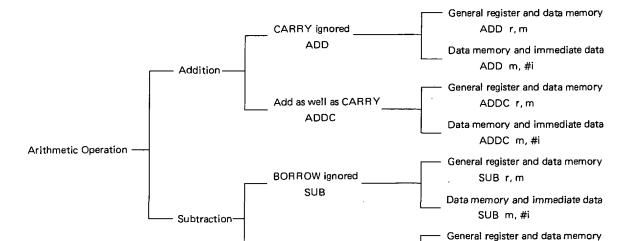

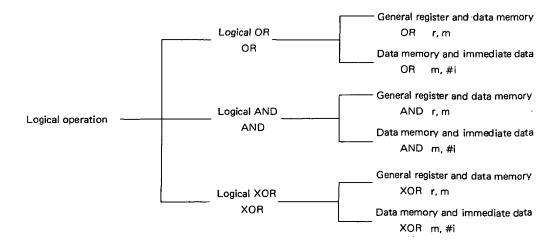

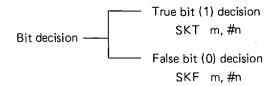

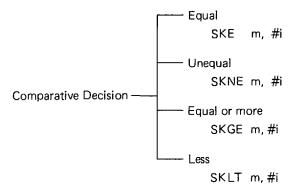

The CPU has such functions as 4-bit parallel addition, logical operation, multiple-bit testing, carry-flag set/reset, powerful interrupt and timer functions.

Incorporated with a user programmable image display controller for on-screen display, the CPU can control various displays with a simple program.

The appearance, which is 64-pin plastic sealing DIP, has the various I/O ports and serial interface functions controlled by powerful input/output commands as well as the 4-bit A/D converter and 6-bit D/A converter (PWM) outputs.

#### **FEATURE**

- 4-bit single-chip microcontroller for digital tuning system

- 14-bit D/A converter for voltage synthesizer

- Program memory (ROM): 12288 words x 16 bits

- Data memory (RAM): 672 words x 4 bits

- Stack levels: 7

- Instruction set comprising 36 easy-to-understand

- Decimal operation capability instruction

- Instruction execution time: 2 µs (when 8 MHz oscillator is connected)

- On-chip IDC (user programmable)

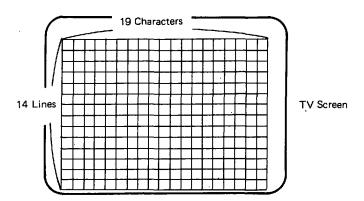

Number of display

characters : Up to 199 characters per screen

Display location: 14 lines x 19 columns

: 256 (A single screen can contain Character type

up to 64 simultaneously.)

Character format: 10 x 15 dots (burster trimming

possible)

: 8 Color

: Four types can be set vertically Character size

or horizontally independent of

each other.

(15, 30, 45, 60 H)

$(2.5, 5.0, 7.5, 10 \mu s)$

On-chip 8-bit serial interface (1 system: 3-wire and 2-wire)

On-chip 6-bit D/A converter: 4 outputs (PWM)

On-chip 4-bit A/D converter: 8 inputs

On-chip horizontal synchronous signal counter

On-chip commercial power frequency counter

On-chip power failure detection and power on reset circuits

Interrupt input for remote control signals (Noise canceller attached)

Various I/O ports

Input/output ports:

Input ports

Output ports 20

5 V±10 %

CMOS low power consumption

The information in this document is subject to change without notice.

Document No. IC-2725 (O.D.No. IC-8100) Date Published August 1991 P

Downloaded frame Elcodis.com electronic components distributor

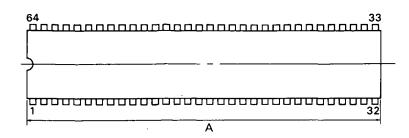

# **ORDERING INFORMATION**

| Order Code     | Package                             | Quality Grade |  |

|----------------|-------------------------------------|---------------|--|

| μPD17053CW-xxx | 64-pin plastic shrink DIP (750 mil) | Standard      |  |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# **FUNCTION OUTLINE**

| Item                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

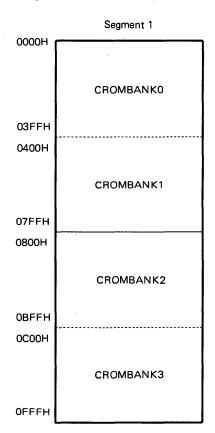

| Program memory                    | 12288 words x 16 bits Table reference area : 4096 words x 16 bits CROM shared area : 4096 words x 16 bits                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Data memory                       | <ul> <li>672 words x 4 bits</li> <li>Data buffer : 4 words x 4 bits</li> <li>General-purpose register : 16 words x 4 bits</li> <li>VRAM dual function area : 224 words x 4 bits</li> </ul>                                                                                                                                                                                                                                                                                 |  |  |

| System register                   | • 12 words x 4 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Register file                     | 28 words x 4 bits (control register)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Port register                     | • 11 words x 4 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Instruction execution time        | 2 μs (8 MHz ceramic oscillator used)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Stack level                       | 7 levels (stack manipulation possible)                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| General-purpose port              | <ul> <li>20 I/O ports</li> <li>4 input ports</li> <li>20 output ports</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| IDC (Image Display<br>Controller) | <ul> <li>Number of display characters</li> <li>Up to 199 characters per screen</li> <li>Display position</li> <li>14 lines x 19 digits</li> <li>Character type</li> <li>256 types (User programmable)         <ul> <li>(However, a single screen can contain up to 64 types simultaneously.)</li> </ul> </li> <li>Character format</li> <li>10 x 15 dots</li> <li>Color</li> <li>8 colors</li> <li>Character size</li> <li>Vertically 4 sizes (15, 30, 45, 60 H)</li></ul> |  |  |

| Serial interface                  | 1 system (2 channels)     8-bit 3-wire: 1 channel     8-bit 2 wire: 1 channel                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| D/A converter                     | <ul> <li>14 bits x 1 converter</li> <li>(PWM output, withstand voltage 12.5 V max.)</li> <li>6 bits x 4 converters</li> <li>(PWM output, withstand voltage 12.5 V max.)</li> </ul>                                                                                                                                                                                                                                                                                         |  |  |

| A/D converter                     | 4 bits x 8 converters     (non-periodical comparison method based on the software)                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

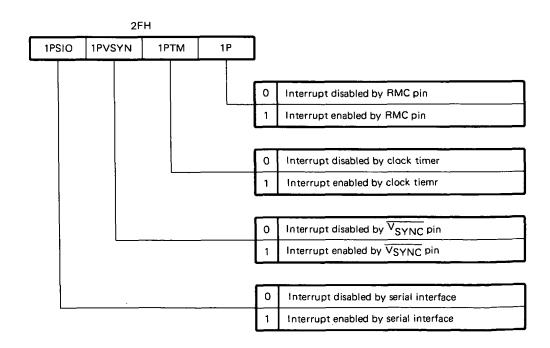

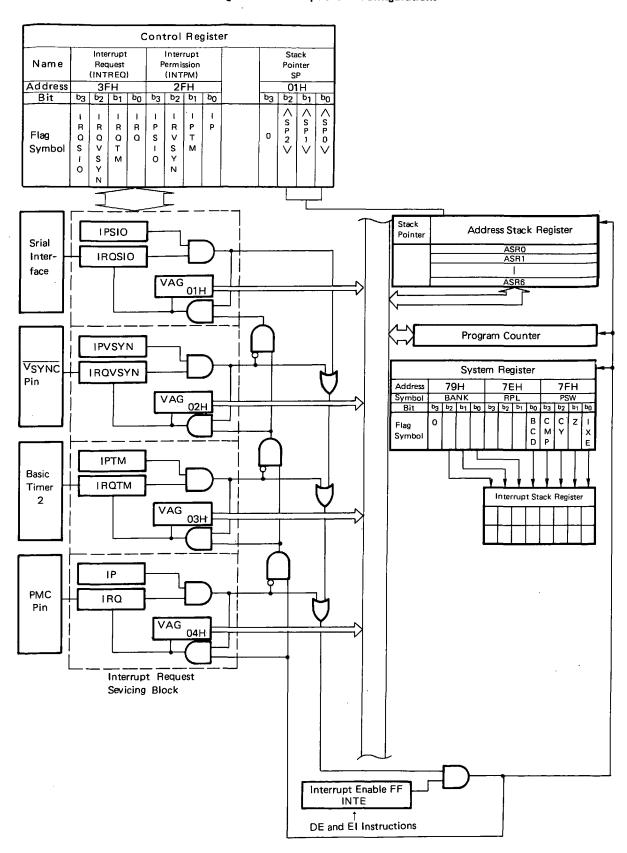

| Interrupt                         | 4 channel (maskable interrupt)  External interrupt: 2 channels (RMC pin, V <sub>SYNC</sub> pin)  Internal interrupt: 2 channels (timer, serial interface)                                                                                                                                                                                                                                                                                                                  |  |  |

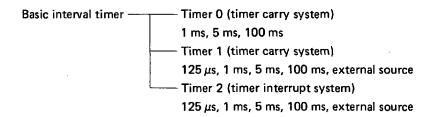

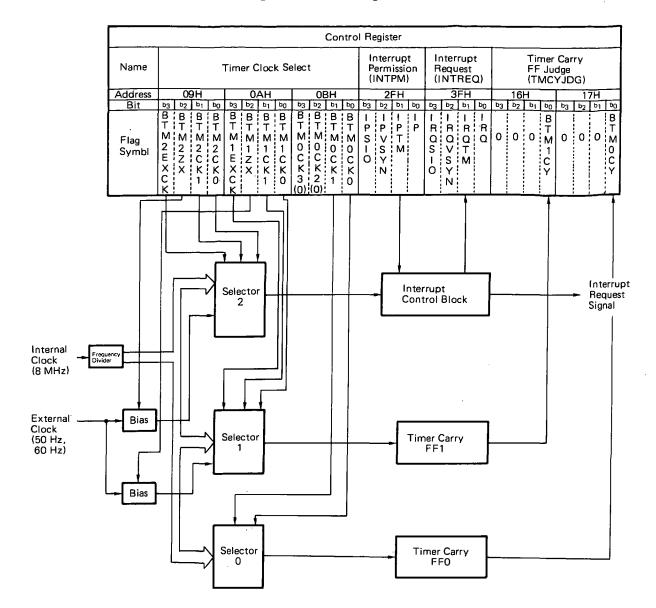

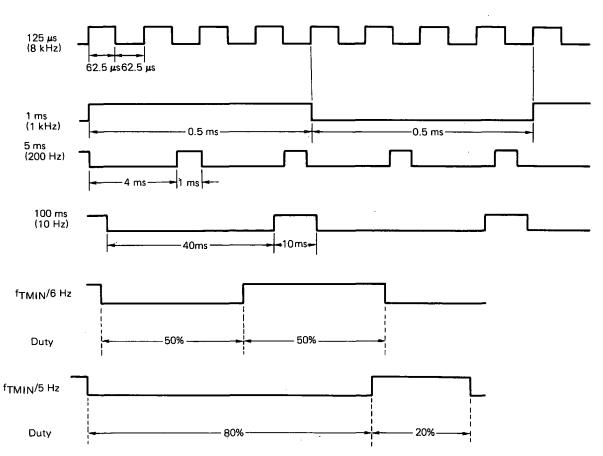

| Timer                             | <ul> <li>3 systems (interrupt: 1 system, carry flag: 2 systems)</li> <li>Internal timer: 125 μs, 1 ms, 5 ms, 100 ms,</li> <li>External timer: 1/5 and 1/6 of the frequency input in the P1B/TMIN pin</li> </ul>                                                                                                                                                                                                                                                            |  |  |

| Reset                             | <ul> <li>Power ON reset (When turning on the power)</li> <li>Reset by CE pin (CE pin: Low level → high level)</li> <li>Power failure detection function</li> </ul>                                                                                                                                                                                                                                                                                                         |  |  |

| Power supply voltage              | 5 V±10 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| <del></del>                       | 64-pin plastic shrink DIP (750 mil)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

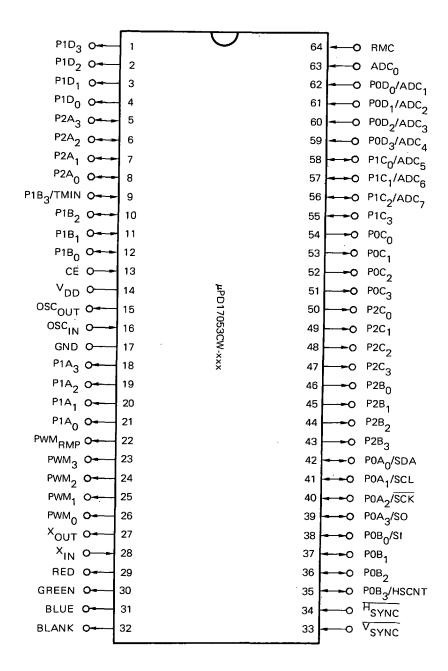

# PIN CONFIGURATION (Top View)

ADC<sub>0</sub> to ADC<sub>7</sub> : A/D converter input

CE : Chip enable

RMC : Interrupt signal input

$X_{IN}, X_{OUT}$  : Clock oscillation  $OSC_{IN}, OSC_{OUT}$  : LC oscillation

TMIN : External timer input PWM<sub>0</sub> to PWM<sub>3</sub> : D/A converter output

PWM<sub>RMP</sub> : Channel select D/A converter output

RED : Character signal output

GREEN : Character signal output

BLUE : Character signal output

BLANK : Blanking signal output

H<sub>SYNC</sub> : Horizontal synchronous signal input V<sub>SYNC</sub> : Vertical synchronous signal input

HSCNT : Horizontal synchronous signal counter input

V DD : Power input GND : Ground SI : Data input SO : Data output

SCK : Shift clock input/output

SCL : Shift clock input/output

SDA : Data input/output

Port 0A PDA<sub>0</sub> to PDA<sub>3</sub> Port 0B POB<sub>0</sub> to POB<sub>3</sub> POC<sub>0</sub> to POC<sub>3</sub> Port 0C POD<sub>0</sub> to POD<sub>3</sub> Port 0D P1A<sub>0</sub> to P1A<sub>3</sub> Port 1A  $P1B_0$  to  $P1B_3$ Port 1B P1C<sub>0</sub> to P1C<sub>3</sub> Port 1C P1D<sub>0</sub> to P1D<sub>3</sub> Port 1D P2A<sub>0</sub> to P2A<sub>3</sub> Port 2A P2B<sub>0</sub> to P2B<sub>3</sub> Port 2B P2C<sub>0</sub> to P2C<sub>3</sub> : Port 2C

# **CONTENTS**

| 1. PIN     | FUNCTION                                                               | 1          |

|------------|------------------------------------------------------------------------|------------|

| 1.1        | DESCRIPTION OF PIN FUNCTIONS                                           | 1          |

| 1.2        | PIN'S EQUIVALENT CIRCUIT                                               | 1:         |

| 2. BLO     | OCK DIAGRAM                                                            | 1          |

| 3. PRO     | GRAM MEMORY (ROM)                                                      | 18         |

| 3.1        | PROGRAM MEMORY CONFIGURATIONS                                          |            |

| 3.1        | PROGRAM MEMORY FUNCTION                                                | 18         |

| 3.3        | PROGRAM FLOW                                                           |            |

| 3.4        | BRANCH INSTRUCTION                                                     | 19         |

| 3.4<br>3.5 | SUBROUTINE                                                             | 21         |

| 3.5<br>3.6 | TABLE REFERENCE                                                        |            |

| 3.6<br>3.7 | PRECAUTIONS IN ASSEMBLER DESCRIPTION                                   |            |

| 3.7        | PRECAUTIONS IN ASSEMBLER DESCRIPTION                                   | 23         |

| 4. PRO     | GRAM COUNTER (PC)                                                      | 24         |

| 4.1        | PROGRAM COUNTER                                                        | 24         |

| 4.2        | SEGMENT RESISTER                                                       | 24         |

| 5. STA     | CK                                                                     | <b>2</b> 5 |

| 5.1        | CONFIGURATIONS                                                         |            |

| 5.2        | STACK POINTER (SP)                                                     |            |

| 5.3        | ADDRESS STACK REGISTER (ASR)                                           |            |

| 5.4        | INTERRUPT STACK REGISTER                                               |            |

|            |                                                                        |            |

| 6. DAT     | A MEMORY (RAM)                                                         | _          |

| 6.1        | DATA MEMORY CONFIGURATIONS                                             | 28         |

| 6.2        | DATA MEMORY FUNCTION                                                   | 33         |

| 6.3        | PRECAUTIONS IN USING DATA MEMORY                                       | 37         |

| 7. GEN     | IERAL REGISTER (GR)                                                    | 38         |

| 7.1        | GENERAL REGISTER CONFIGURATIONS                                        |            |

| 7.2        | •                                                                      | 38         |

| 7.3        | GENERAL REGISTER AND DATA MEMORY ADDRESS                               |            |

| 7.0        | GENERATION IN EACH INSTRUCTION                                         | 40         |

| 7.4        |                                                                        | 44         |

|            |                                                                        |            |

|            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                | 47         |

| •••        | ALO COM ILCOMPANION MANAGEMENT AND | 47         |

| 8.2        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                | 48         |

| 8.3        |                                                                        | 54         |

| 8.4        |                                                                        | 61         |

| •          |                                                                        | 64         |

|            |                                                                        | 66         |

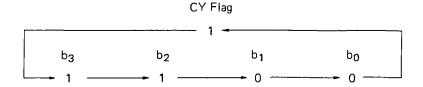

| 8.7        | ROTATION PROCESSING                                                    | 68         |

| 9. |        | TEM REGISTER (SYSREG)                                        |     |

|----|--------|--------------------------------------------------------------|-----|

|    |        | ADDRESS REGISTER                                             |     |

|    | 9.2    | WINDOW REGISTER (WR)                                         | 71  |

|    |        | BANK REGISTER (BANK)                                         |     |

|    | 9.4    | MEMORY POINTER ENABLE FLAG (MPE)                             | 72  |

|    | 9.5    | INDEX REGISTER (IX) AND DATA MEMORY ROW ADDRESS POINTER (MP) | 72  |

|    | 9.6    | GENERAL REGISTER POINTER (RP)                                | 79  |

|    | 9.7    | PROGRAM STATUS WORD (PSWORD)                                 | 80  |

|    |        |                                                              |     |

| 10 | ). REG | ISTER FILE (RF)                                              | 81  |

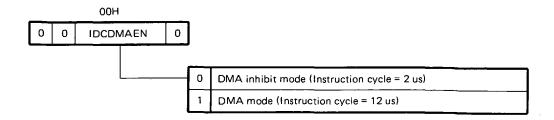

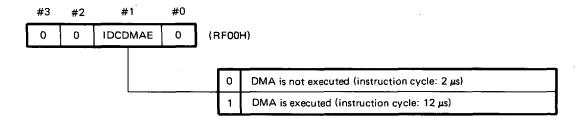

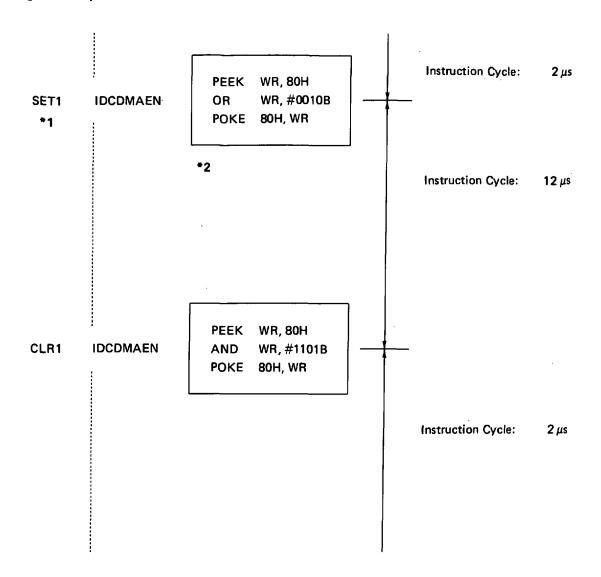

|    | 10.1   | IDCDMAEN                                                     | 84  |

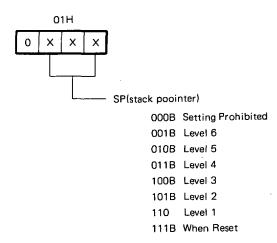

|    | 10.2   | SP                                                           | 84  |

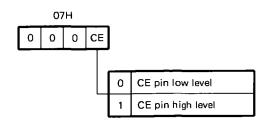

|    | 10.3   | CE                                                           | 84  |

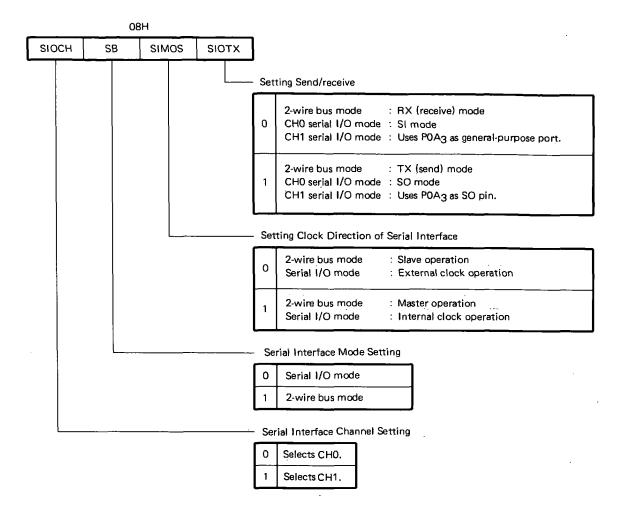

|    | 10.4   | SERIAL INTERFACE MODE REGISTER                               | 85  |

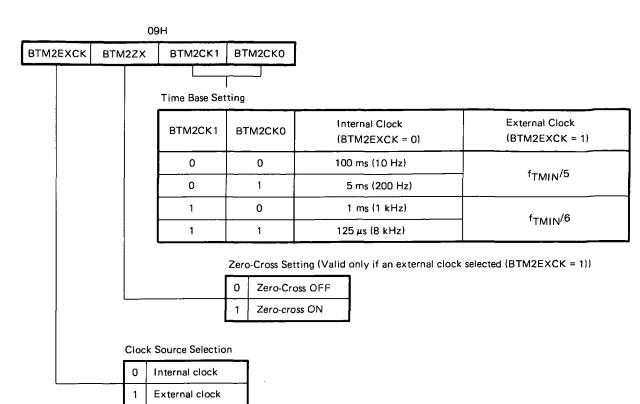

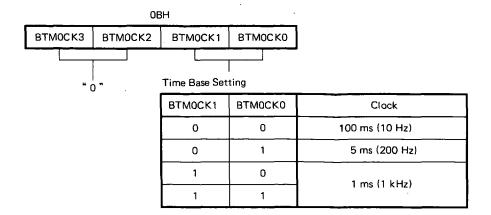

|    | 10.5   | BASIC TIMER 2                                                |     |

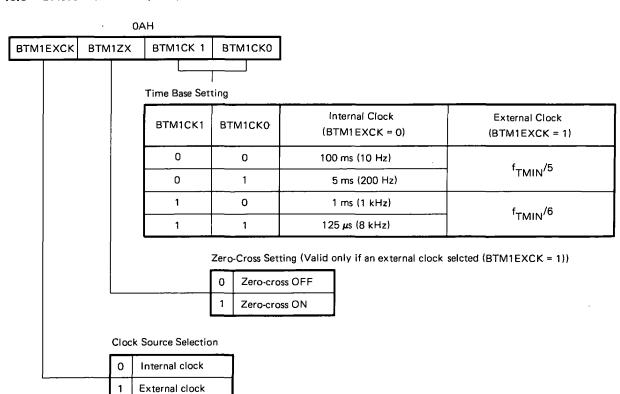

|    | 10.6   | BASIC TIMER 1                                                |     |

|    | 10.7   | BASIC TIMER 0                                                |     |

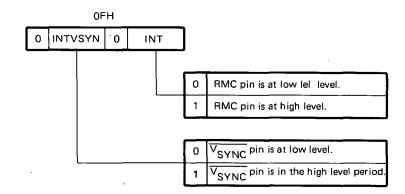

|    | 10.8   | INTVSYN                                                      |     |

|    | 10.9   | ÎNT                                                          |     |

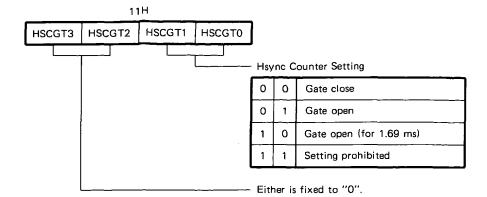

|    |        | HORIZONTAL SYNCHRONOUS SIGNAL COUNTER CONTROL                |     |

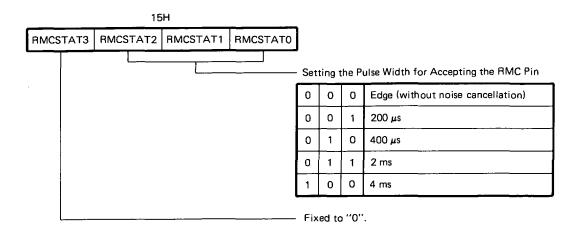

|    |        | SETTING THE PULSE WIDTH FOR ACCEPTING THE RMC PIN            |     |

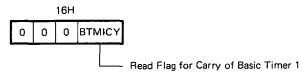

|    |        | CARRYING BASIC TIMER 1                                       |     |

|    |        | CARRYING BASIC TIMER 0                                       |     |

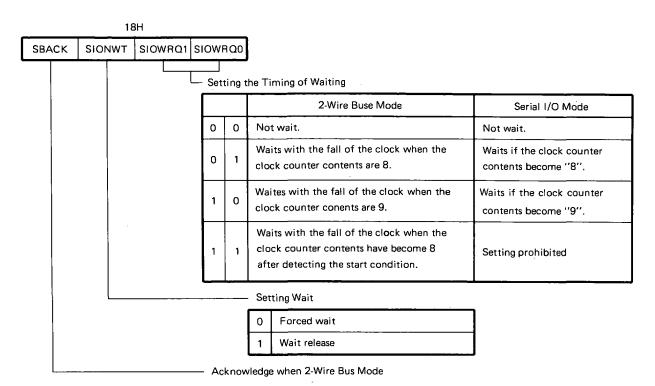

|    |        | SERIAL INTERFACE WAIT CONTROL                                |     |

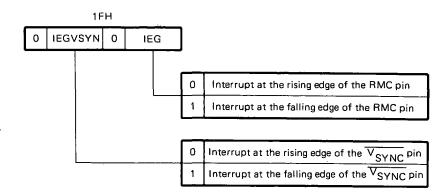

|    |        | IEG                                                          |     |

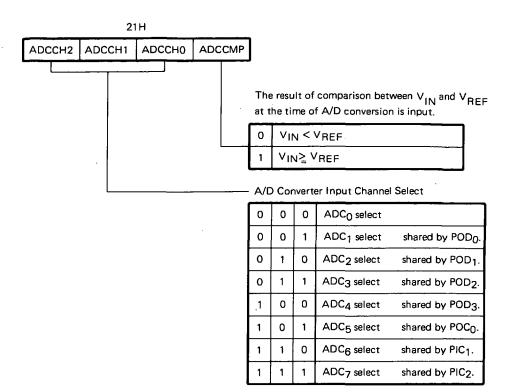

|    |        | A/D CONVERTER CONTROL                                        |     |

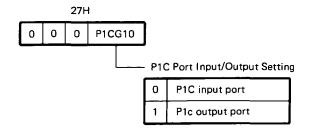

|    |        | SETTING PORT IC INPUT/OUTPUT                                 |     |

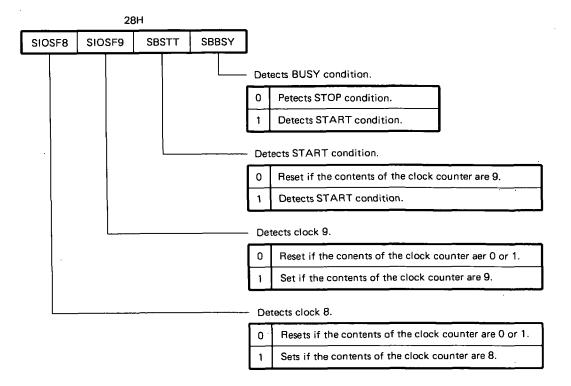

|    |        | SERIAL I/O STATUS REGISTER                                   |     |

|    |        | INTERRUPT ENABLE FLAG                                        |     |

|    |        |                                                              |     |

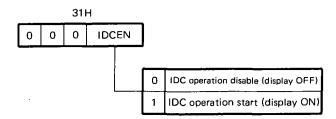

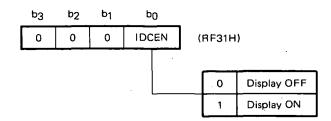

|    |        | IDCEN                                                        |     |

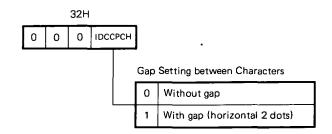

|    |        | IDCCPCH*                                                     |     |

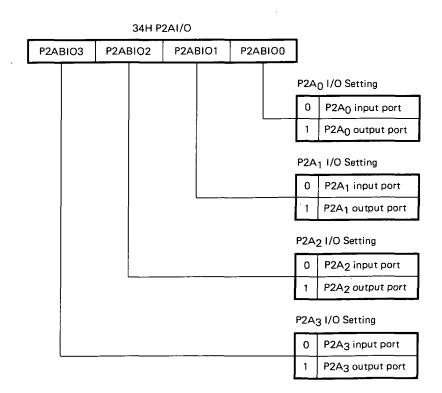

|    |        | P2ABIOn                                                      |     |

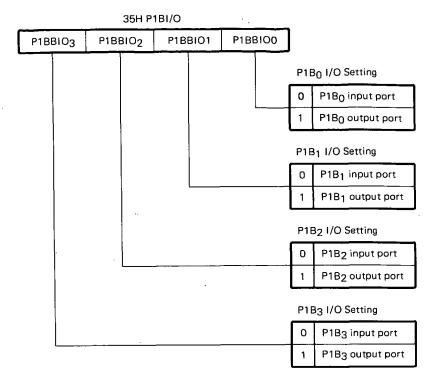

|    |        | P1BBIOn (35H)                                                |     |

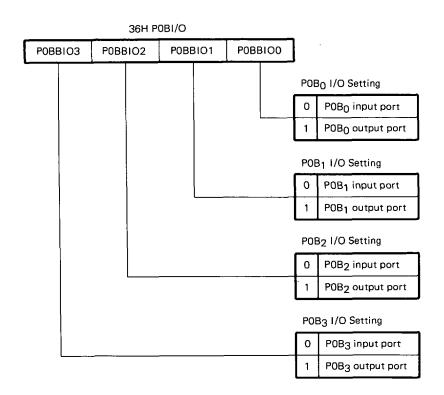

|    |        | P0BBIOn (36H)                                                |     |

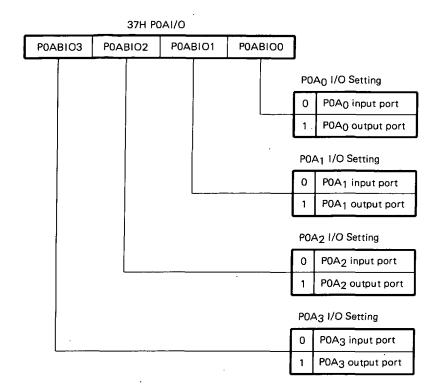

|    |        | P0ABIOn (37H)                                                | 94  |

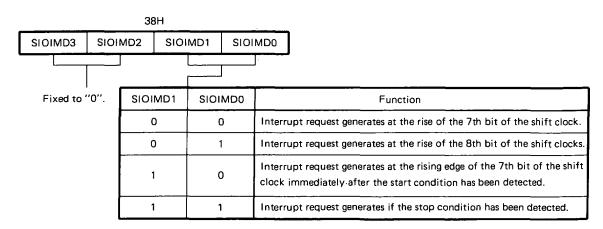

|    | 10.26  | SETTING THE INTERRUPT REQUEST GENERATION TIMING IN           |     |

|    |        | SERIAL INTERFACE MODE                                        | 94  |

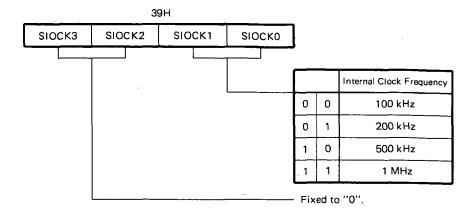

|    |        | SETTING THE SHIFT CLOCK FREQUENCY                            |     |

|    | 10.28  | IRQ                                                          | 95  |

|    |        |                                                              |     |

| 1  | 1. DA  | TA BUFFER (DBF)                                              | 96  |

|    | 11.1   | DATA BUFFER CONFIGURATIONS                                   |     |

|    | 11.2   | DATA BUFFER FUNCTION                                         |     |

|    | 11.3   | DATA BUFFER AND TABLE REFERENCE                              |     |

|    | 11.4   | DATA BUFFER AND PERIPHERAL HARDWARE                          |     |

|    | 11.5   | DATA BUFFER AND EACH PERIPHERAL REGISTER                     |     |

|    | 11.6   | PRECAUTIONS IN USING DATA BUFFER                             | 112 |

|    |        |                                                              |     |

| 1  | 2. INT | ERRUPT                                                       | 113 |

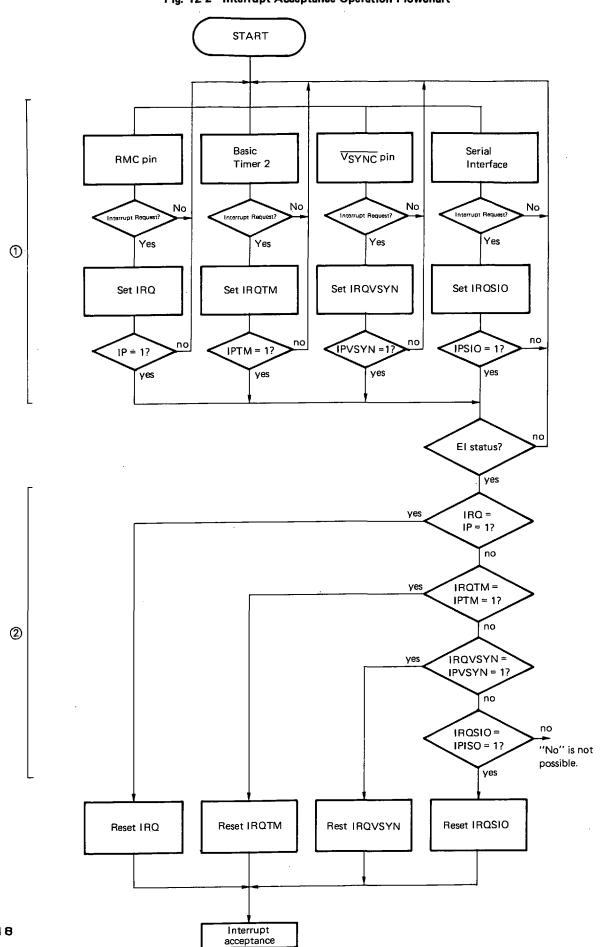

|    | 12.1   | INTERRUPT BLOCK CONFIGURATIONS                               | 113 |

# Phase-out/Discontinued

| 12.2    | INTERRUPT FUNCTION                                           | . 11  |

|---------|--------------------------------------------------------------|-------|

| 12.3    | INTERRUPT ACCEPTANCE OPERATION                               | , 11  |

| 12.4    | OPERATION AFTER INTERRUPT ACCEPTANCE                         | . 12  |

| 12.5    | RETURNING FROM INTERRUPT SERVICE ROUTINE                     | . 12: |

| 12.6    | INTERRUPT SERVICE ROUTINE                                    | . 12  |

| 12.7    | EXTERNAL INTERRUPT (RMC PIN AND VSYNC PIN)                   | . 120 |

| 12.8    | INTERNAL INTERRUPT (TIMER AND SERIAL INTERFACE)              | . 128 |

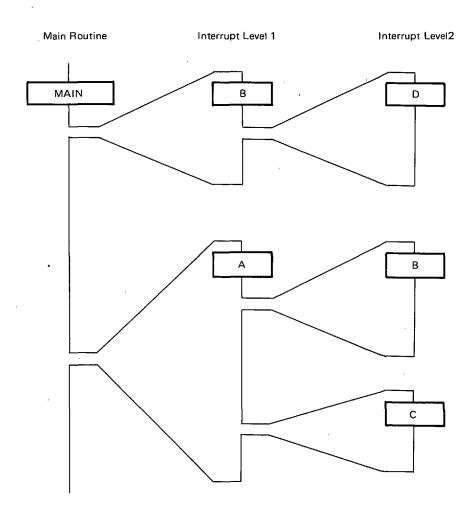

| 12.9    | MULTIPLE INTERRUPT                                           | . 129 |

| 13. TIN | MER FUNCTION                                                 |       |

| 13.1    | TIMER CONFIGURATIONS                                         | . 137 |

| 13.2    | TIMER FUNCTION                                               | . 139 |

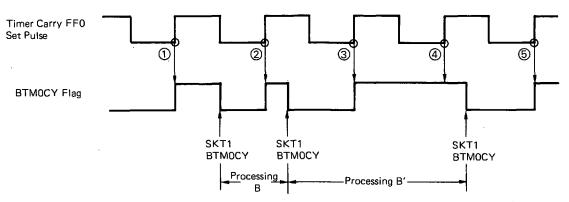

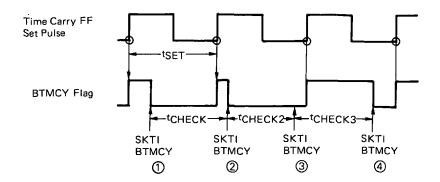

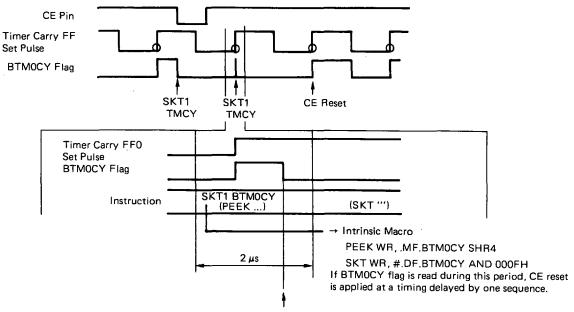

| 13.3    | TIMER CARRY FLIP-FLOP (TIMER CARRY FF)                       | . 140 |

| 13.4    | TIMER CARRY FFO OPERATING PRECAUTIONS                        |       |

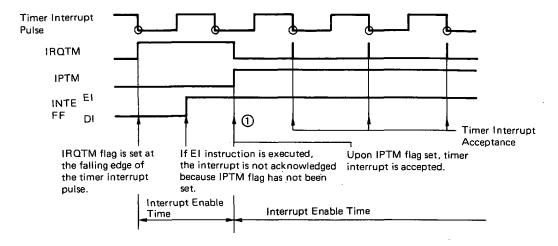

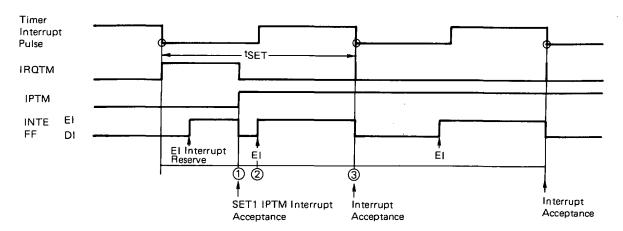

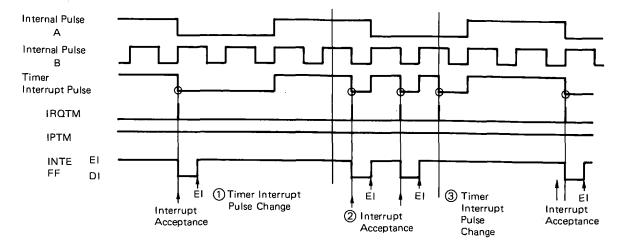

| 13.5    | TIMER INTERRUPT                                              | . 148 |

| 13.6    | PRECAUTIONS TIMER INTERRUPT USING                            | . 152 |

| 14. ST  | ANDBY FUNCTION                                               |       |

| 14.1    | STANDBY BLOCK CONFIGURATION                                  | . 154 |

| 14.2    | STANDBY FUNCTION                                             |       |

| 14.3    | DEVICE OPERATION MODE SETTING WITH CE PIN                    |       |

| 14.4    | HALT FUNCTION                                                | . 156 |

| 14.5    | CLOCK STOP FUNCTION                                          | . 162 |

| 14.6    | DEVICE OPERATIONS UPON HALT AND CLOCK STOP                   | . 165 |

| 15. RE  | SET FUNCTION                                                 |       |

| 15.1    | RESET BLOCK CONFIGURATION                                    |       |

| 15.2    | RESET FUNCTION                                               | 170   |

| 15.3    | CE RESET                                                     |       |

| 15.4    | POWER-ON RESET                                               |       |

| 15.5    | RELATIONS BETWEEN CE RESET AND POWER-ON RESET                | 178   |

| 15.6    | POWER FAILURE DETECTION                                      | 182   |

| 16. GE  | NERAL-PURPOSE PORTS                                          |       |

| 16.1    | GENERAL-PURPOSE PORT CONFIGURATION AND CLASSIFICATION        |       |

| 16.2    | OUTLINE OF GENERAL-PURPOSE PORT FUNCTION                     |       |

| 16.3    | GENERAL-PURPOSE INPUT/OUTPUT PORTS (POA, POB, P1B, P1C, P2A) |       |

| 16.4    | GENERAL-PURPOSE INPUT PORT (POD)                             |       |

| 16.5    | GENERAL-PURPOSE OUTPUT PORTS (POC, P1A, P1D, P2B, P2C)       | 199   |

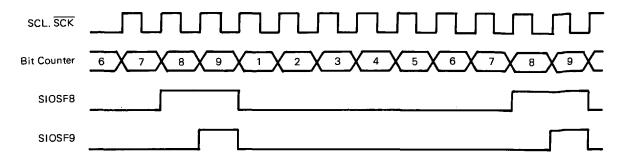

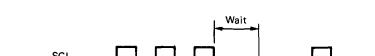

| 17. SEI | RIAL INTERFACE                                               |       |

| 17.1    | SERIAL INTERFACE MODE REGISTER                               |       |

| 17.2    | CLOCK COUNTER                                                |       |

| 17.3    | STATUS REGISTER                                              |       |

| 17.4    | WAIT REGISTER                                                |       |

| 17.5    | PRESETTABLE SHIFT REGISTER (PSR)                             |       |

| 17.6    | SERIAL INTERFACE INTERRUPT SOURCE REGISTER (SIOIMD)          |       |

| 17.7    | SHIFT CLOCK FREQUENCY REGISTER (SIOCK)                       | 215   |

# Phase-out/Discontinued

| 18. D/A | CONVERTER                                           |     |

|---------|-----------------------------------------------------|-----|

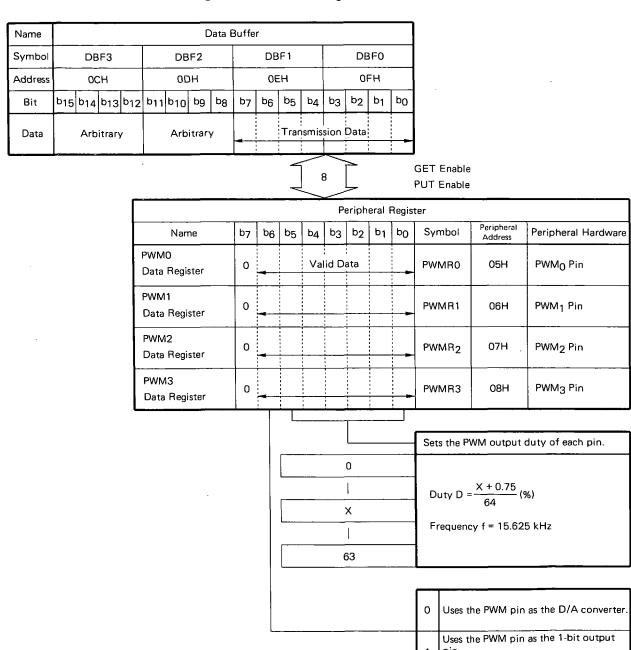

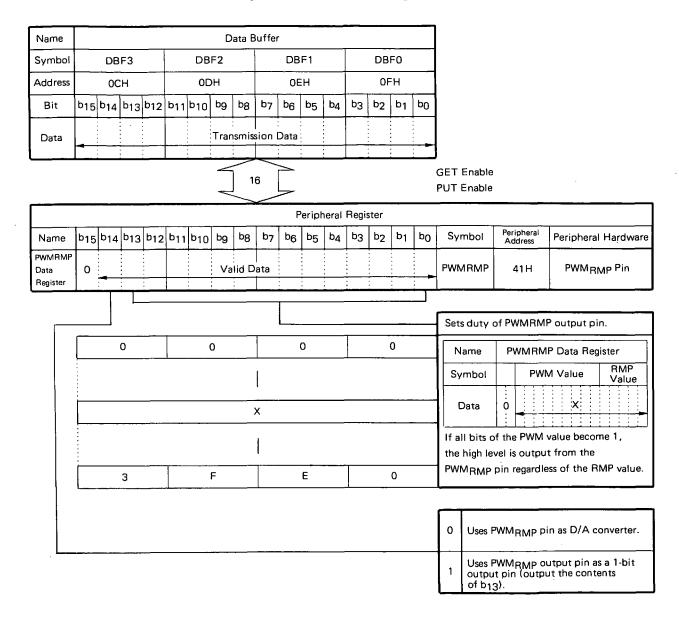

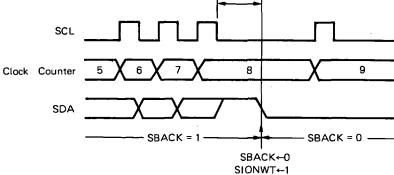

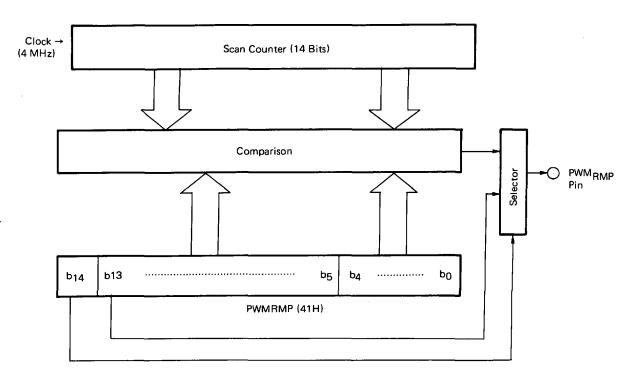

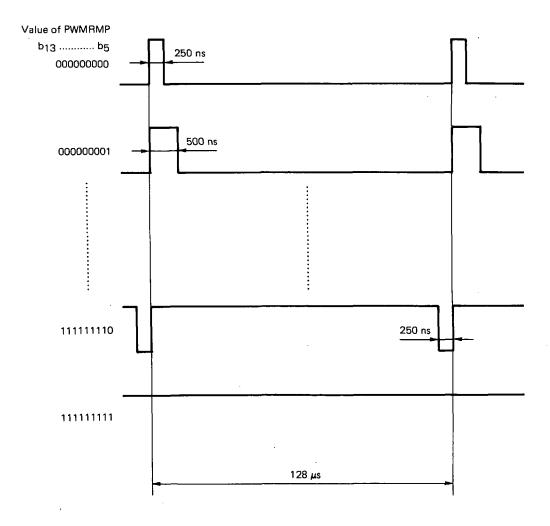

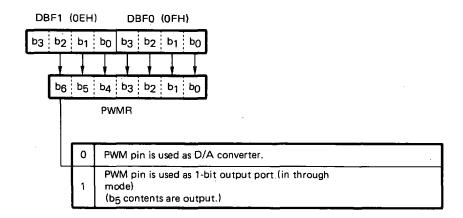

| 18.1    | PWM <sub>RMP</sub> PIN                              | 216 |

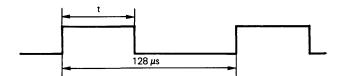

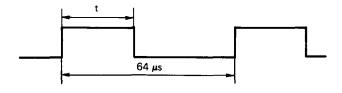

| 18.2    | PWM PIN                                             | 219 |

|         |                                                     |     |

| 19. A/D | CONVERTER                                           | 220 |

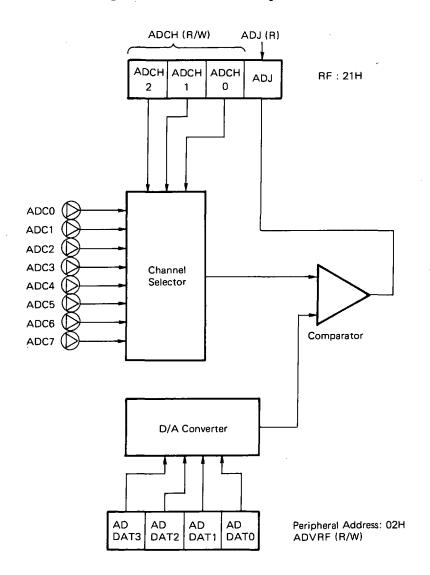

| 19.1    | OPERATING PRINCIPLE                                 | 220 |

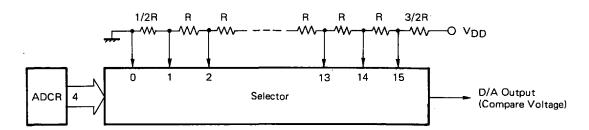

| 19.2    | D/A CONVERTER CONFIGURATION                         |     |

| 19.3    | COMPARE VOLTAGE SET REGISTER (ADCR)                 |     |

| 19.4    | COMPARE JUDGE REGISTER (ADCCMP)                     |     |

| 19.5    | ADC PIN SELECT REGISTER (ADCCHn)                    |     |

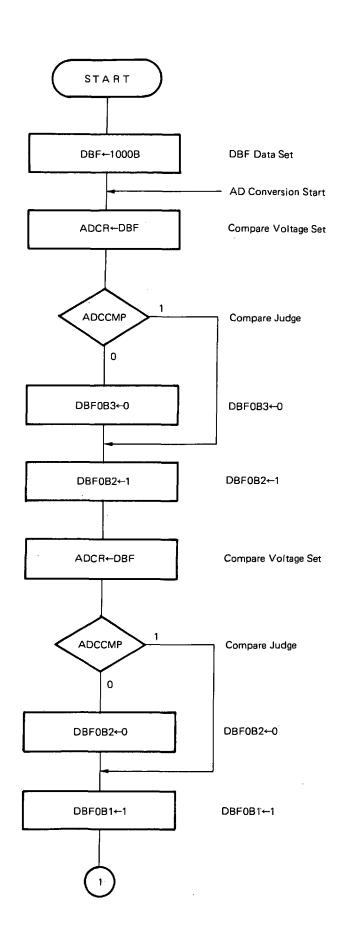

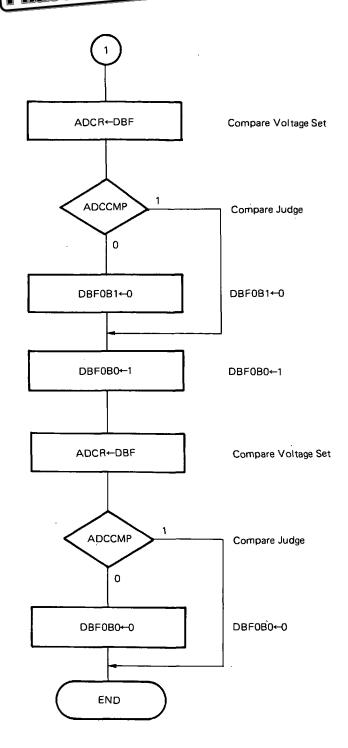

| 19.6    | A/D CONVERSION PROGRAM EXAMPLE                      |     |

| 15.0    | A/D CONVENDION I NOCHAMI EXAMILEE                   | 22. |

| 30 IDC  | (IMAGE DISPLAY CONTROLLER)                          | 226 |

|         | SPECIFICATIONS OUTLINE AND RESTRICTIONS             |     |

| 20.1    |                                                     |     |

| 20.2    | DMA                                                 |     |

| 20.3    | IDC ENABLE FLAG                                     |     |

| 20.4    | VRAM                                                |     |

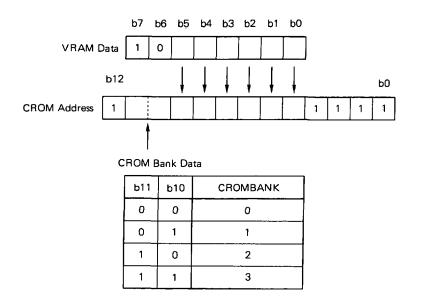

| 20.5    | CROM (CHARACTER ROM)                                |     |

| 20.6    | BLANK, R, G AND B PINS                              |     |

| 20.7    | DISPLAY START POSITION SETTING                      |     |

| 20.8    | PROGRAM EXAMPLE                                     | 251 |

|         |                                                     |     |

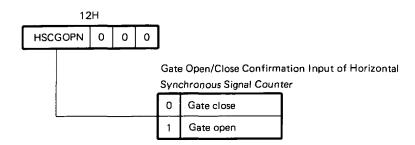

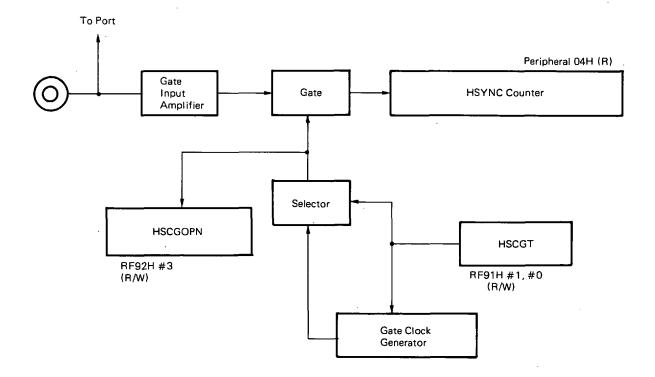

| 21. HOF | RIZONTAL SYNCHRONOUS SIGNAL COUNTER                 | 257 |

| 21.1    | HORIZONTAL SYNCHRONOUS SIGNAL COUNTER CONFIGURATION | 257 |

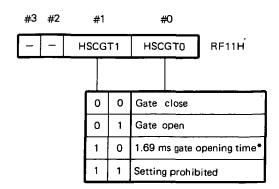

| 21.2    | GATE CONTROL REGISTER (HSCGT)                       | 258 |

| 21.3    | HSYNC COUNTER (HSC)                                 |     |

| 21.4    | HORIZONTAL SYNCHRONOUS COUNTER USAGE EXAMPLE        |     |

|         |                                                     |     |

| 22 uPD  | 17052 INSTRUCTIONS                                  | 260 |

| 22.1    | GENERAL DESCRIPTION OF INSTRUCTION SET              |     |

| 22.2    | LEGEND                                              |     |

| 22.2    | INSTRUCTION SET LIST                                |     |

|         | INTRINSIC MACRO INSTRUCTIONS                        |     |

| 22.4    | INTRINSIC MACRO INSTRUCTIONS                        | 264 |

| 22 DEG  | SERVED SYMBOLS OF ASSEMBLER                         | 205 |

|         |                                                     |     |

| 23.1    | SYSTEM REGISTER (SYSREG)                            |     |

| 23.2    | DATA BUFFER (DBF)                                   |     |

| 23.3    | GENERAL-PURPOSE PORT REGISTER                       |     |

| 23.4    | REGISTER FILE (CONTROL REGISTER)                    |     |

| 23.5    | PERIPHERAL HARDWARE ADDRESS                         | 271 |

|         |                                                     |     |

| 24. ELE | ECTRICAL SPECIFICATIONS                             | 272 |

|         |                                                     |     |

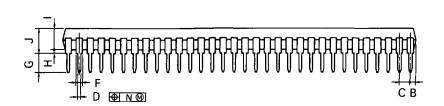

| 25. PAC | CKAGE DIMENSION                                     | 274 |

|         |                                                     |     |

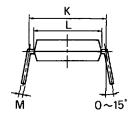

| 26. RE  | COMMENDED SOLDERING CONDITIONS                      | 275 |

|         |                                                     |     |

| APPEN   | DIX. DEVELOPMENT TOOLS                              | 276 |

# 1. PIN FUNCTION

#### 1.1 DESCRIPTION OF PIN FUNCTIONS

| PIN NO.             | SYMBOL                                                                             | PIN NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OUTPUT TYPE             |

|---------------------|------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1 to 4              | P1D <sub>3</sub><br>to<br>P1D <sub>0</sub>                                         | Port 1D     | These are 4-bit output ports, Port 1D's latch is allocated in address 73H of BANK1 of the data memory (RAM). The output state at the time of power-on reset is undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMOS push-              |

| 5 to 8              | P2A <sub>3</sub><br>to<br>P2A <sub>0</sub>                                         | Port 2A     | These are 4-bit I/O ports. It is possible to specify input/output for these ports bit-wise. Input/output is set with the P2ABIO words (34H) on the register file. The latch of this port is located in address 70H of BANK2 of the data memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CMOS push-<br>pull      |

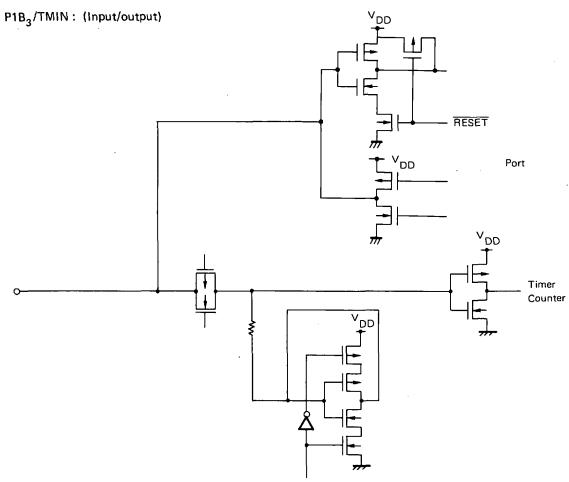

| 9<br>10<br>11<br>12 | P1B <sub>3</sub> /TMIN<br>P1B <sub>3</sub><br>P1B <sub>1</sub><br>P1B <sub>0</sub> | Port 1B     | These are 4-bit I/O ports. It is possible to specify input/output for these ports bit-wise. Input/output is set with the P1BBIO words (35H) on the register file. The latch of this port is located in address 71H of BANK1 of the data memory.  P1B/TMIN can be used as an external timer input as well. It is possible to interrupt the frequency that is input to this pin with 1/5 or 1/6 of the frequency. Normally, the frequency of the commercial power is input to this pin to be used as a reference clock.                                                                                                                                                                                                                                                                                        | CMOS push-pull<br>(I/O) |

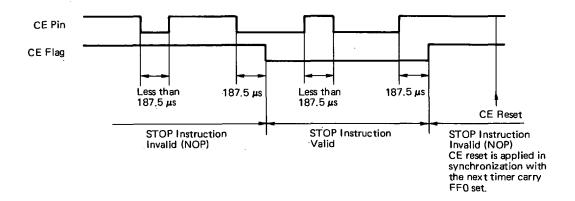

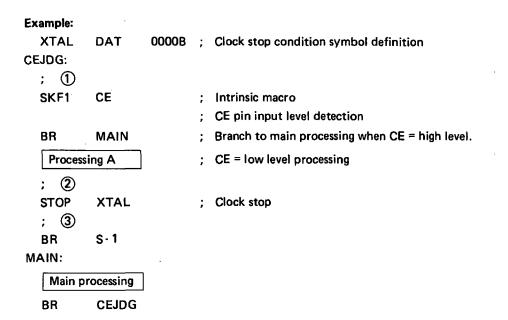

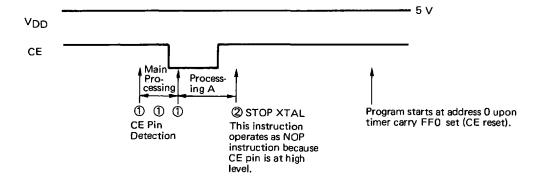

| 13                  | CE                                                                                 | Chip enable | This is the device selection signal input pin. The device is set to the high level for a normal operation and to the low level when not using it. If the STOP instruction is executed when this pin is at the low level, the clock oscillation is stopped thus making the backup at a low power consumption possible.  The STOP instruction is valid only when the CE pin is at the low level. When it is at the high level, it functions in the same manner as the NOP instruction. This pin plays the role of a reset pin as well. Therefore, if the CE pin is changed from the low level to high, the device is reset, thus restarting the program from address 0. If the device is reset, the bank becomes 0, thus placing the I/O port in the input mode.  However, the low level from 188 µs and below | Input                   |

| 14                  | V <sub>DD</sub>                                                                    | Power input | is not accepted.  This is the device power pin. A voltage of 5 V± 10 % is supplied to make the device operate all the functions. A voltage between 4 to 5.5 V is supplied when IDC is not used. It is possible to lower the voltage to about 2.2 V when holding the RAM data (when the clock oscillation is stopped). As µPD17053 is incorporated with the power-on reset circuit, if this is changed from 0 to 4.0 V, the system is reset thus making the program operate from address 0. Restrict the start-up time for changing from 0 to 4.0 V within 500 ms to make the power-on reset circuit operate normally.                                                                                                                                                                                        |                         |

| PIN NO.              | SYMBOL                                                                                  | PIN NAME                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OUTPUT TYPE                                           |

|----------------------|-----------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

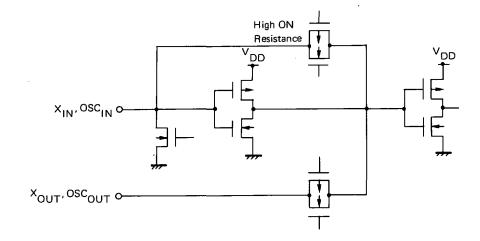

| 15<br>16             | osc <sub>out</sub><br>osc <sub>in</sub>                                                 | LC oscillation                            | These are the LC oscillation circuit pins for IDC.  They are oscillated at 4 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 17                   | GND                                                                                     | Ground                                    | This is the ground pin of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |

| 18<br>to<br>21       | P1A <sub>3</sub><br>to<br>P1A <sub>0</sub>                                              | Port 1A                                   | These are 4-bit output ports. The latch of this port is located in address 70H of BANK1 of the data memory. The format is N-ch open-drain (middle-voltage, high current).                                                                                                                                                                                                                                                                                                                                                                                                                | N-ch open-drain                                       |

| 22                   | PWMRMP                                                                                  | Channel select<br>D/A converter<br>output | This is the 14-bit D/A converter output or 1-bit output port for voltage synthesizer. The D/A converter outputs the pulse which has combined the 9-bit PWM and the 5-bit RMP (Rate Multiplier). Therefore, D/A conversion can be carried out by externally connecting a simple CR filter. The low level is output for power-on reset or clock stop.                                                                                                                                                                                                                                      | N-ch open-drain                                       |

| 23<br>to<br>26       | PWM <sub>3</sub><br>to<br>PWM <sub>o</sub>                                              | D/A converter                             | These are the VDP (Variable Duty Port) or 1-bit output ports. The VDP function is to output the 15.625 kHz pulse continuously and is capable of varying the duty of this pulse in 64-step programs.                                                                                                                                                                                                                                                                                                                                                                                      | N-ch open-drain                                       |

| 27<br>28             | X <sub>OUT</sub>                                                                        | Clock<br>oscillation                      | These are connection pins of ceramic oscillators or crystal resonators. Ensure to use 8 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMOS push-pull<br>(XOUT), input<br>(X <sub>IN</sub> ) |

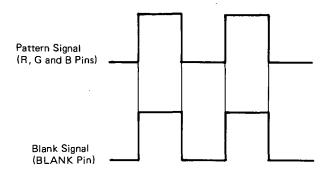

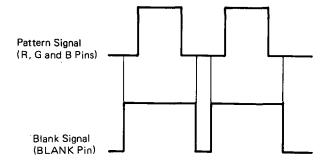

| 29<br>30<br>31       | RED<br>GREEN<br>BLUE                                                                    | Character signal output                   | These are the output pins of the character data corresponding to R, G and B. Output is made at active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CMOS<br>push-pull                                     |

| 32                   | BLANK                                                                                   | Blanking<br>signal output                 | This is the output pin of the blanking signal to cut image signals. Output is made at active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CMOS push-pull                                        |

| 33                   | VSYNC                                                                                   | Vertical synchron-<br>ous signal input    | This is the input pin of the vertical synchronous signal for IDC.  Ensure to make the input at active low. Interrupt can be applied with this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input                                                 |

| 34                   | HSYNC                                                                                   | Horizontal synchron-<br>ous signal input  | This is the input pin of the horizontal synchronous signal for IDC. Ensure to make the input at active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input                                                 |

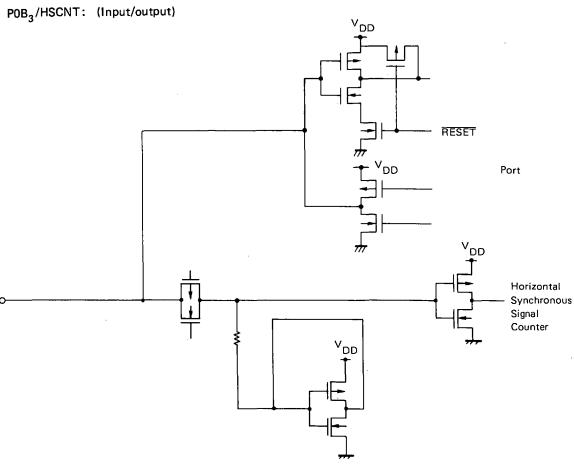

| 35<br>36<br>37<br>38 | POB <sub>3</sub> /HSCNT<br>POB <sub>2</sub><br>POB <sub>1</sub><br>POB <sub>6</sub> /SI | Port OB                                   | These are 4-bit I/O ports. It is possible to specify input/output bit-wise for these ports. This setting is made with the POBBIO words (36H) on the register file. The latch of this port is located in address 71H of BANKO of the data memory. Pin POB/SI can be used as the data input pin of the serial interface (serial I/O mode) as well. Pin POB/HSCNT can be used as the input pin of the horizontal synchronous signal counter as well. At this time, the own bias (VDD/2) is applied to the HSCNT pin. Port OB is ready for input in power-on reset, clock stop and CE reset. |                                                       |

| PIN NO.              | SYMBOL                                                                                                                                               | PIN NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OUTPUT TYPE                                                                                                                       |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 39<br>40<br>41<br>42 | POA <sub>3</sub> /SO<br>POA <sub>3</sub> /SCK<br>POA <sub>3</sub> /SCL<br>POA <sub>9</sub> /SDA                                                      | Port 0A                   | These are 4-bit I/O ports. It is possible to specify input/output bit-wise for these ports. This setting is made with the POABIO words (37H) on the register file. The latch of this port is located in address 70H of BANKO of the data memory. Pin POA <sub>3</sub> /SO can be used as the data output pin of the serial interface (serial I/O mode) and POA <sub>2</sub> /SCK can be used as the shift clock I/O pin. Pin POA/SDA can be used as the data I/O pin of the serial interface (two-wire mode and serial I/O mode) and pin POA <sub>1</sub> /SCL can be used as the shift clock I/O pin. | POA <sub>3</sub> /SO POA <sub>2</sub> /SCK CMOS push-pull (I/O) POA <sub>1</sub> /SCL POA <sub>0</sub> /SDA N-ch open-drain (I/O) |

| 43<br>to<br>46       | P2B <sub>3</sub><br>to<br>P2B <sub>0</sub>                                                                                                           | Port 2B                   | These are 4-bit output ports. The latch of this port is located in address 71H of BANK2 of the data memory. The format is N-ch open-drain (middle-voltage).                                                                                                                                                                                                                                                                                                                                                                                                                                            | N-ch open-drain                                                                                                                   |

| 47<br>to<br>50       | P2C <sub>3</sub><br>to<br>P2C <sub>0</sub>                                                                                                           | Port 2C                   | These are 4-bit output ports. The latch of this port is located in address 72H of BANK2 of the data memory. The format is N-ch open-drain (middle-voltage).                                                                                                                                                                                                                                                                                                                                                                                                                                            | N-ch open-drain                                                                                                                   |

| 51<br>to<br>54       | POC <sub>3</sub><br>to<br>POC <sub>0</sub>                                                                                                           | Port OC                   | These are 4-bit output ports. The latch of this port is located in address 72H of BANKO of the data memory. The output state is undefined in power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS push-pull                                                                                                                    |

| 55<br>56<br>57<br>58 | P1C <sub>3</sub><br>P1C <sub>2</sub> /ADC <sub>7</sub><br>P1C <sub>1</sub> /ADC <sub>6</sub><br>P1C <sub>0</sub> /ADC <sub>5</sub>                   | Port 1C                   | These are 4-bit I/O ports or A/D converter input pins. Input/output setting is carried every 4 bits, specifying with the P1CGIO bits (27H's #0 bit) on the register file. Ensure to specify when used as the A/D converter. The latch of this port is located in address 72H of BANK1 of the data memory. Port 1C is ready for input in power-on reset, clock stop and CE reset.                                                                                                                                                                                                                       | CMOS<br>push-pull (I/O)                                                                                                           |

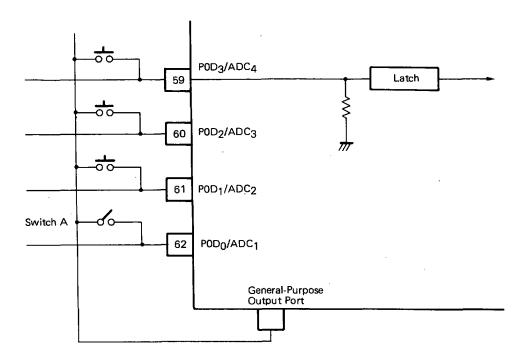

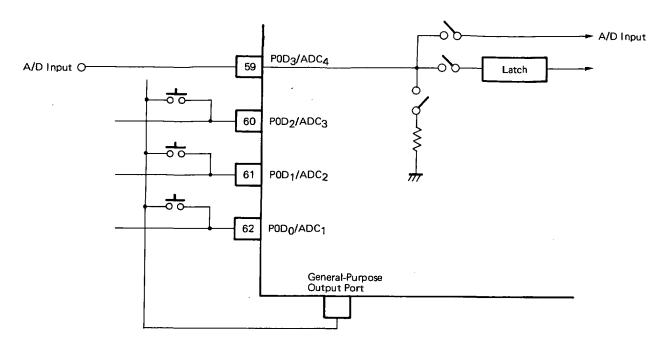

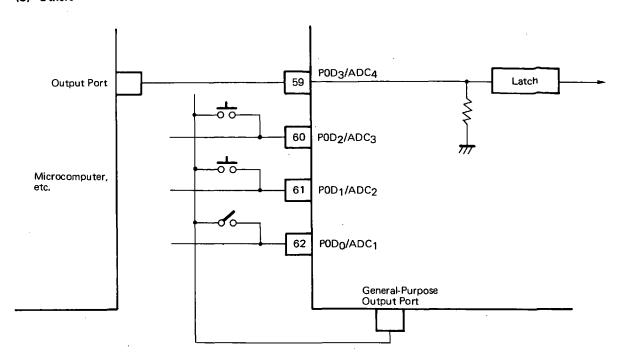

| 59<br>60<br>61<br>62 | POD <sub>3</sub> /ADC <sub>4</sub><br>POD <sub>2</sub> /ADC <sub>3</sub><br>POD <sub>1</sub> /ADC <sub>2</sub><br>POD <sub>0</sub> /ADC <sub>1</sub> | Port 0D                   | These are 4-bit input ports or A/D converter input pins. The pull-down resistor is installed (100 k TYP.) when these are used as ports.  The latch of Port 0D is located in address 73H of BANKO of the data memory.                                                                                                                                                                                                                                                                                                                                                                                   | Input<br>(Equipped with<br>pull-down resistor)                                                                                    |

| 63                   | ADC <sub>0</sub>                                                                                                                                     | A/D<br>converter input    | This is the A/D converter input pin. It is incorporated with the 4-bit A/D converter of the program-based random comparison method.  The reference voltage of the A/D converter is VDD.                                                                                                                                                                                                                                                                                                                                                                                                                | Input                                                                                                                             |

| 64                   | RMC                                                                                                                                                  | Interrupt<br>signal input | This is the interrupt input pin equipped with a noise canceller. If the signal is noisy such as the remote control signal, the program is made easier by using this pin. It is possible to specify in the program whether to apply an interrupt at the rise or the fall of the input signal to this pin. The interrupt is applied at the rise if the IEG flag is reset, and at the fall if the IEG flag is set. If the CE is reset, the IEG flag is reset thus applying the interrupt at the rising edge.                                                                                              | Input                                                                                                                             |

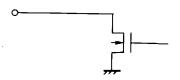

(Input/output)

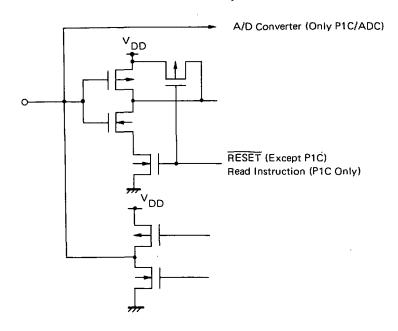

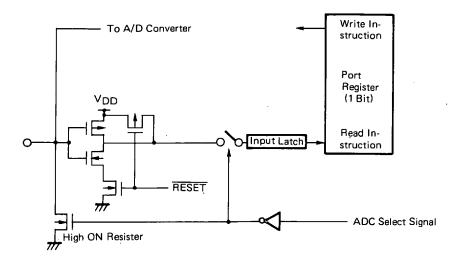

# 1.2 PIN'S EQUIVALENT CIRCUIT

POA (POA<sub>3</sub>/SO, POA<sub>2</sub>/SCK)

POB (POB<sub>2</sub>, POB<sub>1</sub>, POB<sub>0</sub>/SI)

P1B (P1B<sub>2</sub>, P1B<sub>1</sub>, P1B<sub>0</sub>)

P1C (P1C<sub>3</sub>, P1C<sub>2</sub>/ADC<sub>7</sub>, P1C<sub>1</sub>/ADC<sub>6</sub>, P1C<sub>0</sub>/ADC<sub>5</sub>)

P2A (P2A<sub>3</sub>, P2A<sub>2</sub>, P2A<sub>1</sub>, P2A<sub>0</sub>)

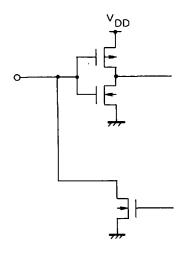

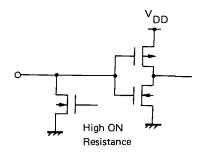

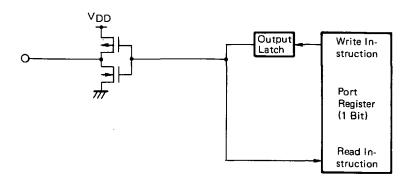

# POA (POA<sub>1</sub>/SCL, POA<sub>0</sub>/SDA): (Input/output)

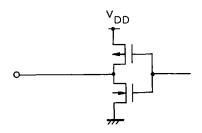

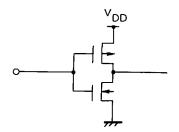

$\begin{array}{c} \operatorname{POC}\left(\operatorname{POC}_{3},\operatorname{POC}_{2},\operatorname{POC}_{1},\operatorname{POC}_{0}\right) \\ \operatorname{P1D}\left(\operatorname{P1D}_{3},\operatorname{P1D}_{2},\operatorname{P1D}_{1},\operatorname{P1D}_{0}\right) \\ \operatorname{RED},\operatorname{GREEN},\operatorname{BLUE},\operatorname{BLANK} \end{array} \right\} \quad \text{(Output)}$

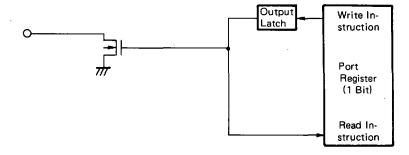

$\begin{array}{c} \mathsf{PWM} \; (\mathsf{PWM}_3, \mathsf{PWM}_2, \mathsf{PWM}_1, \mathsf{PWM}_0, \mathsf{PWM}_{\mathsf{RMP}}) \\ \mathsf{P1A} \; (\mathsf{P1A}_3, \mathsf{P1A}_2, \mathsf{P1A}_1, \mathsf{P1A}_0) \\ \mathsf{P2B} \; (\mathsf{P2B}_3, \mathsf{P2B}_2, \mathsf{P2B}_1, \mathsf{P2B}_0) \\ \mathsf{P2C} \; (\mathsf{P2C}_3, \mathsf{P2C}_2, \mathsf{P2C}_1, \mathsf{P2C}_0) \end{array}$

${\rm POD} \; ({\rm POD_3/ADC_7, POD_2/ADC_6, POD_1/ADC_5, POD_0/ADC_4}) : \quad ({\rm Input})$

ADC<sub>0</sub>: (Input)

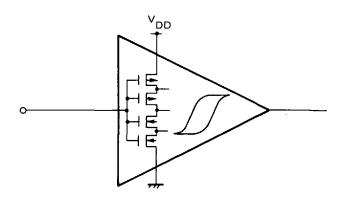

H<sub>SYNC</sub>, V<sub>SYNC</sub>, RMC, CE: (Schmitt trigger input)

$X_{IN}, OSC_{IN}$  : (Input)  $X_{OUT}, OSC_{OUT}$  : (Output)

# 2. BLOCK DIAGRAM

## 3. PROGRAM MEMORY (ROM)

#### 3.1 PROGRAM MEMORY CONFIGURATIONS

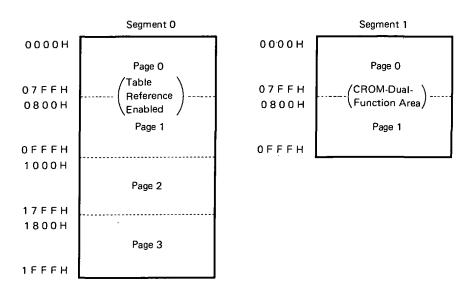

ROM is configured with 12288 words x 16 bits and is used to store programs. The usable ROM address range is 8192 words of addresses 0000H to 1FFFH. Every 2048 words are divided into 4 pages.

1800H to 1FFFH are also used as the CROM (Character ROM) area to store the display patterns for IDC. When not used as CROM, they can be used as the program area.

0000H to 00FFH are the area for table reference and used with BR, MOVT, PUSH and POP instructions.

Fig. 3-1 ROM Configurations

#### 3.2 PROGRAM MEMORY FUNCTION

The program memory has the following two major functions.

- (1) To store programs

- (2) To store constant data

A program is a collection of "instructions" for operating the CPU. The CPU processes the work sequentially in accordance with the "instructions" written in the program. In other words, the CPU reads "instructions" sequentially from a program stored in the program memory and executes the work in accordance with each "instruction".

As all instructions are in "one word" of 16-bit length, it is possible to store one instruction in one address of the program memory.

Constant data are pre-determined data such as the patterns for display. By using the special-purpose MOVT instruction, the content of the program memory can be read into the data buffer (DBF) on the memory (RAM). As such, reading the constant data on the program memory is called "table reference".

As the program memory is the memory for reading only, it cannot be reloaded by the instruction. Therefore, the program memory and the ROM are used with the same meaning.

#### 3.3 PROGRAM FLOW

Programs stored in the program memory are normally executed address by address starting from address 0000H.

However, when, for example, executing a different program for a certain condition, it is necessary to branch the program flow. In this case, the branch instruction is used.

If the same program needs to be executed repeatedly, using the same program each time the execution is performed will reduce the efficiency of the program memory. In this case, keep the program in a certain location. Then, the same program can be executed as many as desired by calling it with the dedicated CALL instruction. This program is called the "subroutine". In contrast, a normally executed program is called the "main routine".

When a program needs to be executed because a certain condition is satisfied regardless of the program flow, the interrupt function is used. With the interrupt function, is possible to branch to a decided address (called header address) regardless of the program flow if conditions are met.

Such a program flow as was described above is controlled by the program counter (PC) which specifies the program memory address.

#### 3.4 BRANCH INSTRUCTION

In any segment, the Branch (BR) instruction is effective for a branch in any direction. Branching from Segment 0 to Segment 1 can be performed with the SYSCAL instruction, which can be reset by the RET or RETSK instruction.

Branch instructions (BR) include two types, i.e., the direct branch instruction (BR addr) which directly branches into the program memory address specified with the instruction operand (addr) and the indirect branch instruction (BR @AR) which branches to the program memory address specified with the address register (AR).

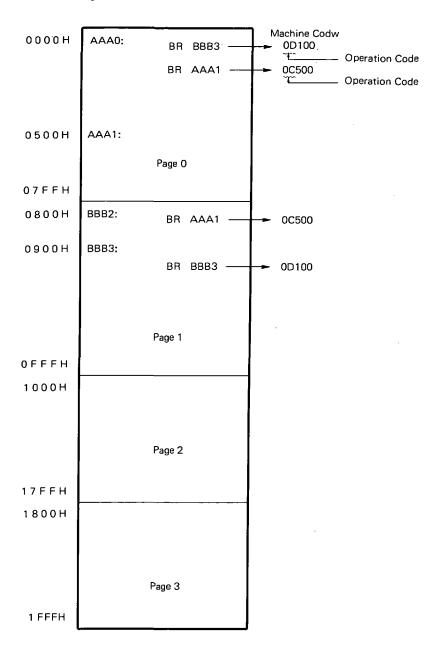

The direct branch instruction specifies the program memory address of the branch destination with 11 bits of the instruction operand. The addresses that can be specified with the 11 bits are one page portion of 0000H to 07FFH. Therefore, the direct branch instruction is available for each page to be branched and each has a different operation code. However, when programming with the  $\mu$ PD17000 series assembler (AS17K), the BR instruction can be used without the page concept.

The indirect branch instruction specifies the address of the branch destination with the 12 bits of the address register. Therefore, the branch destination addresses of the indirect branch instruction are limited to addresses 0000H to 00FFH.

#### (1) Precautions in debugging

As shown in Fig. 3-2, the direct branch instruction can be used with the same description between data memory addresses 0000H to 1FFFH without the page concept when describing with the assembler.

However, the operation code of the direct branch instruction differs depending on the page to be branched.

For example, the operation code of the direct branch instruction into page 0 is "OCH", while the operation code of the direct branch instruction into page 1 is "ODH". If the 17K series assembler is used for assembling, these are automatically converted by the assembler referring to the jump destination. Here, what requires attention is that, if patch correction is performed in debugging, the program itself must decide on the branch destination page. At this time, the operation code is selected according to the branch destination page of the direct branch page and the lower 11 bits of the address is used as the operand.

For example, if the assembler description is "BR BBB2" (BBB2 is address 0800H), "0D000" is input to perform the patch correction. "BR AAA0" (AAA0 is address 0000H) is "0C000".

Fig. 3-2 Machine Code of Direct Branch Instruction

#### 3.5 SUBROUTINE

The subroutine is used by dedicated subroutine call (CALL) and subroutine return (RET, RETSK) instructions.

Subroutine call instructions include the direct subroutine call instruction (CALL addr) which directly calls the program memory address specified with the instruction's operand (addr) and the indirect subroutine call instruction (CALL @AR) which calls the program memory address specified by the content of the address register.

As the return instruction from the subroutine, the RET instruction and the RETSK instruction are used. By executing the RET or RETSK instruction, the operation is returned to the program memory address following the address on which the subroutine call instruction (CALL) was executed. At this time, the RETSK instruction executes the first returned instruction as the no operation instruction (NOP).

#### 3.5.1 Examples of Using the Subroutine

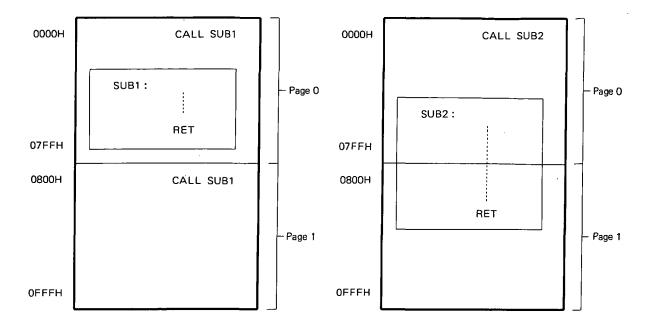

Fig. 3-3 shows the example of using the subroutine.

When using the "CALL addr" instruction, it is necessary to place its call address, i.e., the subroutine's start address within page 0 (addresses 0000H to 07FFH) of segment 0 or segment 1. The subroutine whose start address is located in any of the other pages cannot be called.

However, the return instruction (RET, RETSK) can be placed on any page. The CALL instruction itself can be on any page, too.

#### Example 1: Subroutine start address is within page 0:

If the subroutine's start address is located within page 0 as shown in Fig. 3-3, both the return address and the return instruction can be located either within page 0 or page 1.

As long as the subroutine start address is in page 0, the CALL instruction can be used without any page concept. However, if is not possible to place the subroutine start address within page 0 for reasons related to program preparation, the method shown in example 2 is used.

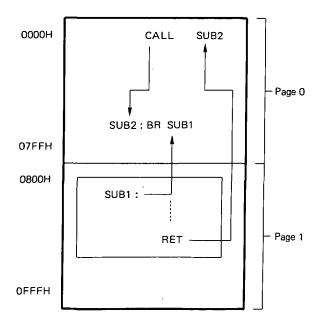

#### 2: Subroutine start address is within page 1:

As shown in the example in Fig. 3-3, this method actually calls the subroutine (SUB1) via the BR instruction which is set within page 0.

The subroutine call instruction (CALL @AR) which is based on indirect address specification calls the subroutine of the address specified by the contents of the address register. The address register consists of 12 bits. Therefore, the program memory addresses that can be called by the CALL @AR instruction are 0000H to 0FFFH.

Fig. 3-3 Examples of Using the Subroutine

# (a) Subroutine start address is within page 0:

# (b) Subroutine start address is within page 1:

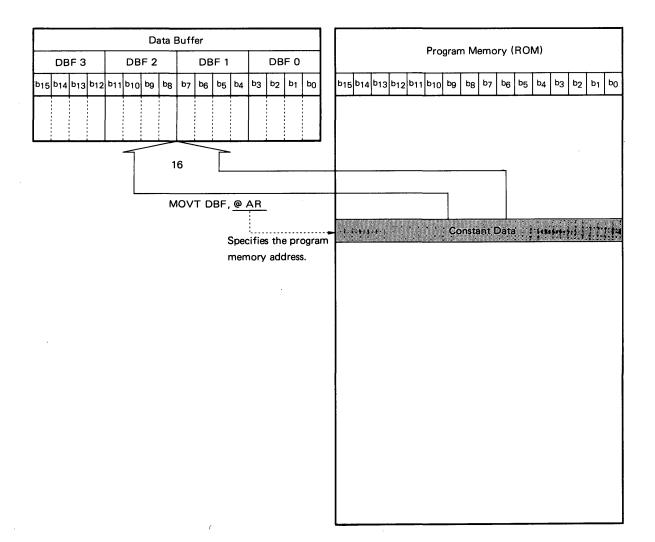

#### 3.6 TABLE REFERENCE

Example

The table reference is used when referring to the constant table in the program memory.

If the "MOVT DBF, @AR" instruction is executed, the content of the program memory address specified by the address register is stored in the data buffer.

The contents of the program memory are 16-bit configurations. Therefore, the constant data stored in the data buffer by the MOVT instruction becomes 16 bits (4 words). The address register consists of 12 bits.

Therefore, the program memory addresses that can be referenced by the MOVT instruction become 0000H to 0FFFH.

Be careful because the stack is used temporarily when executing the MOVT instruction.

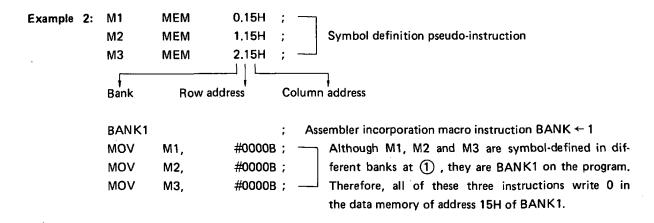

#### 3.7 PRECAUTIONS IN ASSEMBLER DESCRIPTION

When using the assembler, error occurs if the program memory address (address based on numerals) is specified directly in the operand of the branch instruction (BR) or subroutine call instruction (CALL).

| 1: | Case of error                                      | occurrence                   |                                       |                                                                                                                                                                                                          |

|----|----------------------------------------------------|------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | BR<br>CALL                                         |                              | 0005H;<br>00F0H;                      | Error occurs in the assembler.                                                                                                                                                                           |

| 2: | Case of non-                                       | error                        |                                       |                                                                                                                                                                                                          |

|    | BR<br>LOOP1:<br>SUB1:<br>CALL<br>LOOP2<br>BR<br>BR | SUB1<br>LAB<br>LOOP2<br>.LD. | ; —<br>;<br>; —<br>0005H; —<br>0005H; | Labels are used in the program. And the BR or CALL instruction is executed to these labels.  0005H is assigned to LOOP2 as the label type.  Numeric value of the operand is converted to the label type. |

For details, see "AS17K User's Manual".

# 4. PROGRAM COUNTER (PC)

#### 4.1 PROGRAM COUNTER

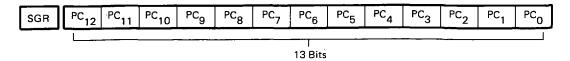

The program counter addresses the program memory, i.e., the program and consists of 13-bit binary counters. In addition to the binary counters, it has a segment register (SGR) that specifies a segment.

Fig. 4-1 Program Counter

Normally, one increment is made by executing one instruction. However, when the jump instruction or the sub-routine call instruction is executed, the address specified in the operand part is loaded. When the skip instruction has been executed, the address of the instruction following the skip instruction is specified regardless of the content of the skip condition. At this time, if the condition is to be skipped, the instruction following the skip instruction is regarded as the NOP instruction. In other words, execution of the NOP instruction results in specification of the address of the following instruction.

The program counter is linear only in a segment. This registers address 0000H to be specified after address 1FFFH.

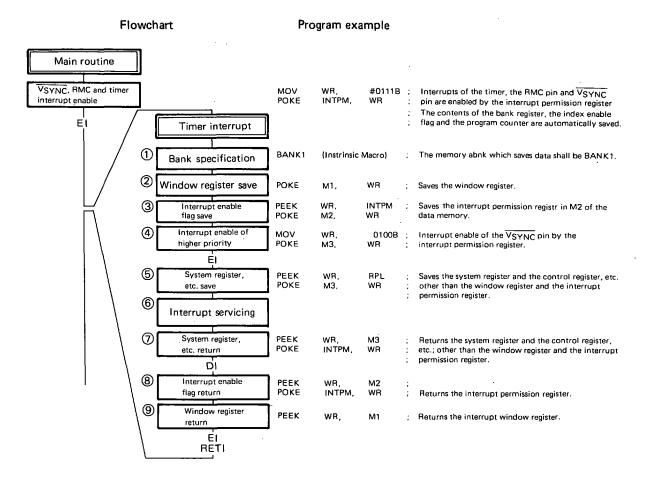

When accepting the interrupt request, SEGMENT 0 addresses 1 to 4 (differing on the interrupt source) is unconditionally loaded on the Program Counter.

The program counter is segment 0 reset to 0 in power-on reset or CE reset.

Priority Order

Interrupt Source

Vector Address

1

RMC pin

4H

2

Basic timer 2

3H

3

V<sub>SYNC</sub> pin

2H

4

Serial interface

1H

Table 4-1 Vector Address in Interrupt

#### 4.2 SEGMENT REGISTER

The segment register is a register used to specify the segment.

The segment is specified by the SGR value shown in Table 4-2 below. When resetting, the SGR is reset to 0. The SGR is set to 1 by the SYSCAL instruction only. The SGR value does not change with the BR or CALL instruction.

Table 4-2 Segment Register

| SGR | Segment Specified |  |

|-----|-------------------|--|

| 0   | Segment 0         |  |

| 1   | Segment 1         |  |

#### 5. STACK

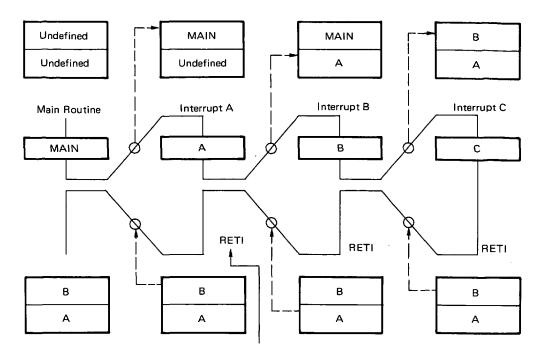

The stack is a register to save the return address of the program and contents of the system register to be described later when accepting the subroutine call or interrupt.

#### 5.1 CONFIGURATIONS

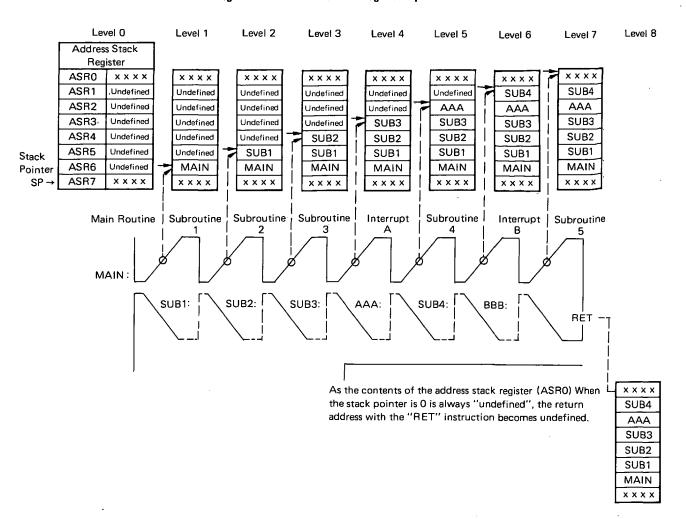

The stack consists of a stack pointer (SP) which is a 4-bit binary counter, seven 14-bit address stack registers (ASR) and two 8-bit interrupt stack registers.

#### 5.2 STACK POINTER (SP)

The stack pointer is located in address 01H on the register file and specifies the address stack register. It is made -1 by the PUSH manipulation (CALL, MOVT, PUSH, SYSCAL instruction and interrupt acceptance) and +1 by the POP manipulation (RET, RETSK, RETI, MOVT and POP instructions).

High-order 1 bit of the stack pointer is always "0". The obtainable stack pointer values include eight values of 0H to 7H. However, there is no stack matching 7H.

Fig. 5-1 Stack Pointer Configurations

| MSB |                  |                  | LSB              |

|-----|------------------|------------------|------------------|

| "0" | SPb <sub>2</sub> | SPb <sub>1</sub> | SPb <sub>0</sub> |

Table 5-1 Stack Pointer Operation

| Instruction          | Stack Pointer Value |

|----------------------|---------------------|

| CALL addr            |                     |

| CALL @AR             |                     |

| MOVT DBF, @AR        | CD 1                |

| PUSH AR              | SP - 1              |

| SYSCAL F             |                     |

| Interrupt acceptance |                     |

| RET                  |                     |

| RETSK                |                     |

| MOVT DBF, @AR        | SP + 1              |

| POP AR               |                     |

| RETI                 |                     |

#### 5.3 ADDRESS STACK REGISTER (ASR)

The address stack register consists of 7 x 14 bits. When executing the subroutine call instruction or accepting the interrupt request, the value of the content of the program counter plused by +1, in other words, the return address is stored here. The content of the stack register is loaded on the program counter by executing the return instruction to be returned to the flow of the original program.

The stack register is used for both the subroutine call and the interrupt. Therefore, if two levels are used for the interrupt, the remaining five levels of the stack register are available for the subroutine call.

If the MOVT instruction is executed, the stack register is used temporarily.

Fig. 5-2 Address Stack Register Configurations

| Stack Pointer | · Value            |                             |

|---------------|--------------------|-----------------------------|

| он            | SGRSR <sub>0</sub> | ASR <sub>0</sub><br>13 Bits |

| 1H            | SGRSR <sub>1</sub> | ASR <sub>1</sub>            |

| 2H            | SGRSR <sub>2</sub> | ASR <sub>2</sub>            |

| 3H            | SGRSR <sub>3</sub> | ASR <sub>3</sub>            |

| 4H            | SGRSR <sub>4</sub> | ASR <sub>4</sub>            |

| 5H            | SGRSR <sub>5</sub> | ASR <sub>5</sub>            |

| 6H            | SGRSR <sub>6</sub> | ASR <sub>6</sub>            |

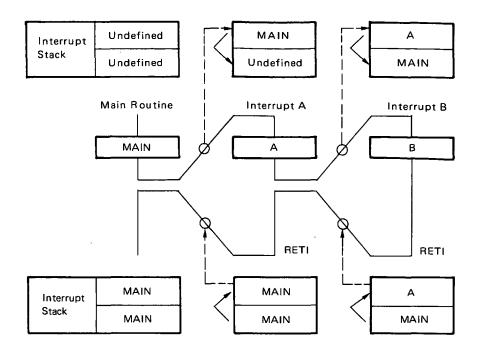

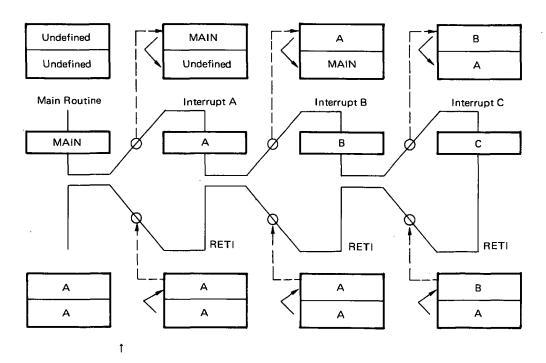

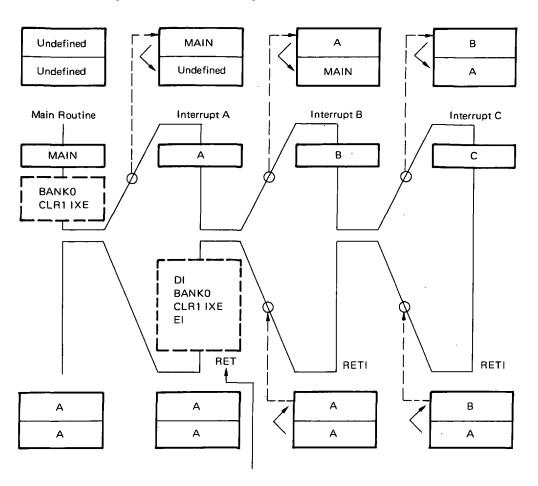

#### 5.4 INTERRUPT STACK REGISTER

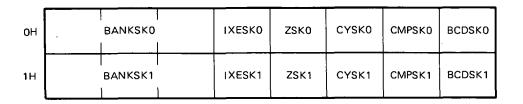

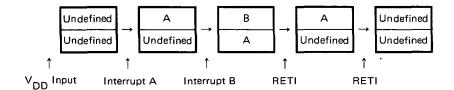

The interrupt stack register is configured with 2 x 8 bits as shown in Fig. 5-3.

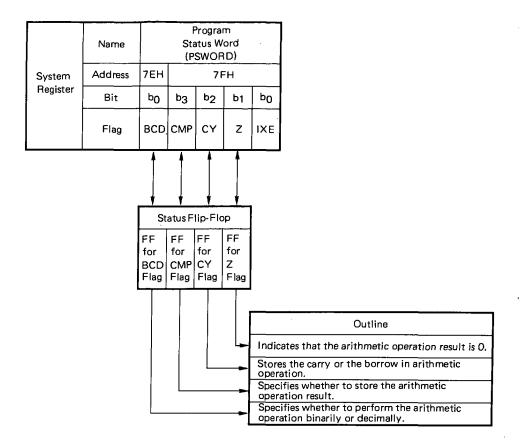

If the interrupt is accepted, a total of 8 bits, i.e., 3 bits of the bank register (BANK) and 5 bits of the program status word in the system register to be described later are saved. Then, if the interrupt return instruction (RETI) is executed, the content to the interrupt stack register is returned to the system register's bank register and the program status word.

The interrupt stack register does not have the address specified by the stack pointer as in the address stack register. It saves data everytime an interrupt is accepted as shown in Fig. 5-4. If an interrupt exceeding two levels is received, the initial data is omitted forth. Therefore, it is necessary to save it in the program.

The contents of the interrupt stack register is undefined in power-on reset. The previous state is held when resetting the CE or executing the CLOCK STOP instruction.

Fig. 5-3 Interrupt Stack Register Configurations

Fig. 5-4 Interrupt Stack Register Operation

# 6. DATA MEMORY (RAM)

The data memory stores such data as operation and control, etc. Data are constantly written or read by the instruction.

#### 6.1 DATA MEMORY CONFIGURATIONS

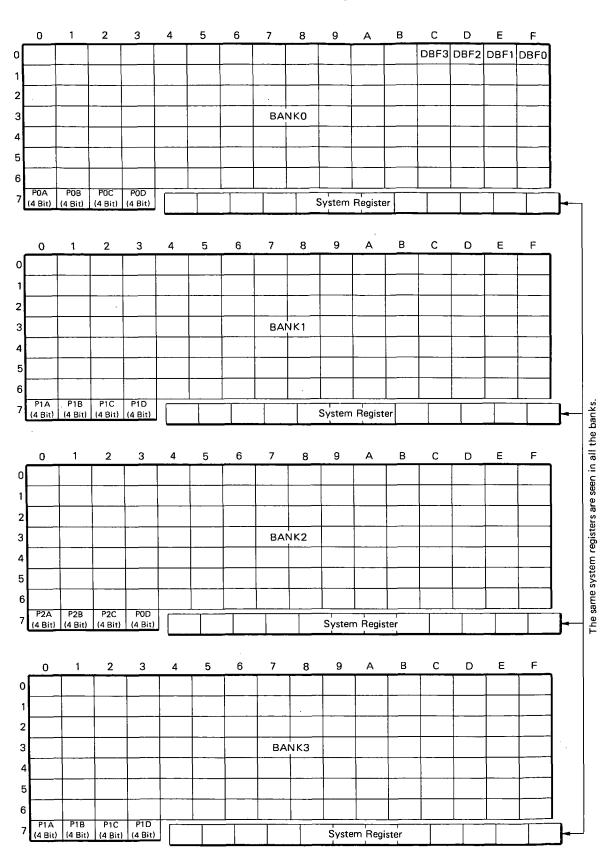

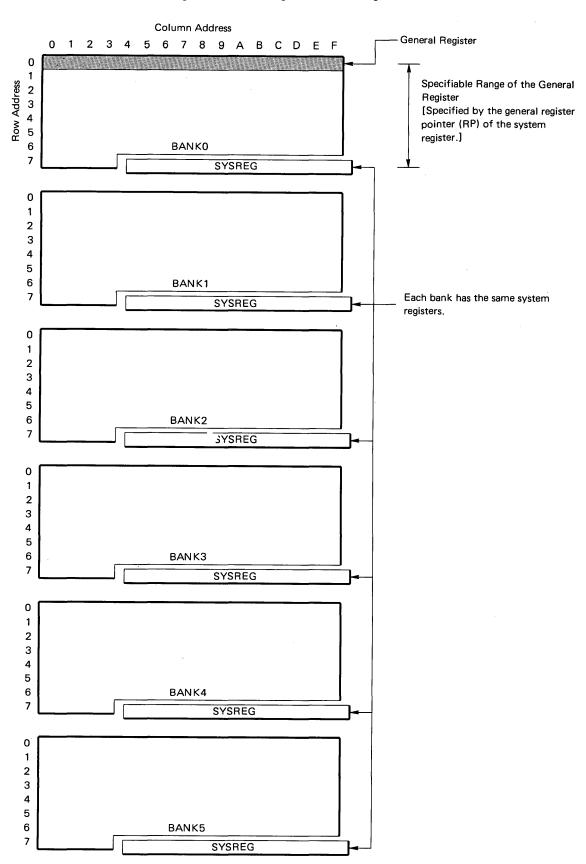

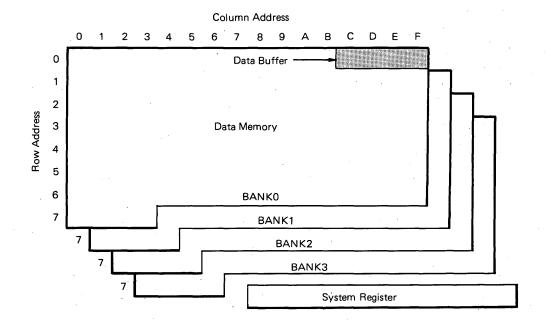

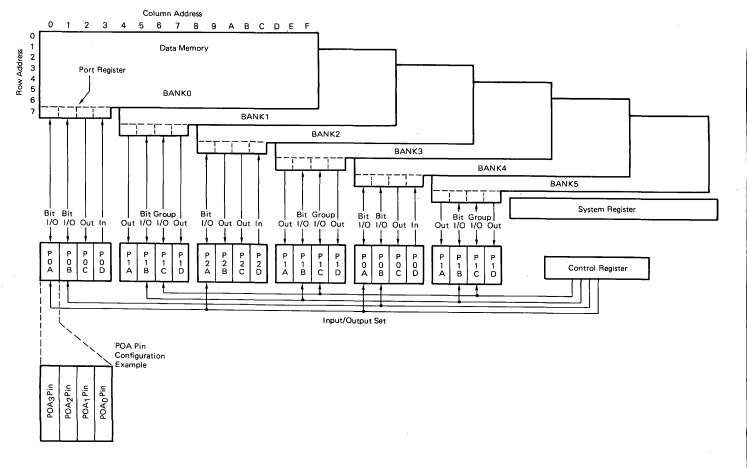

Fig. 6-1 shows the data memory configurations.

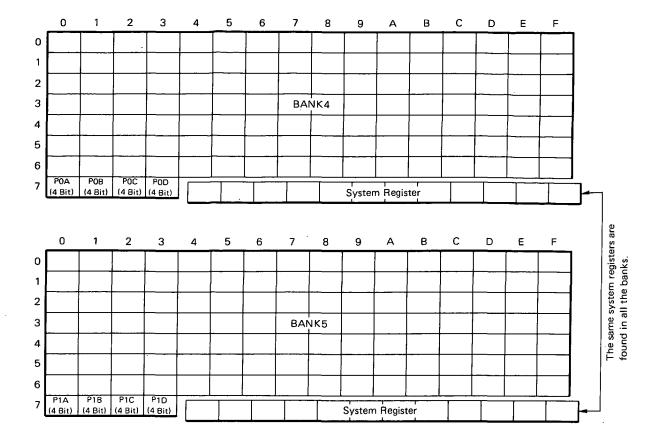

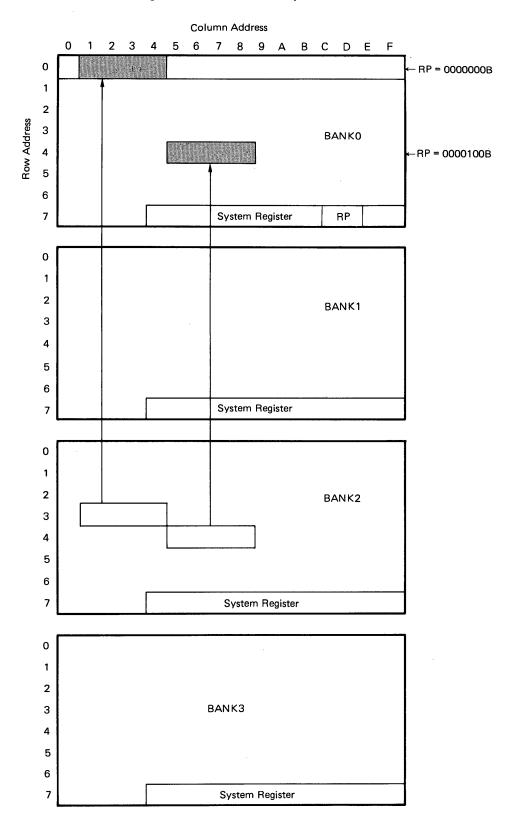

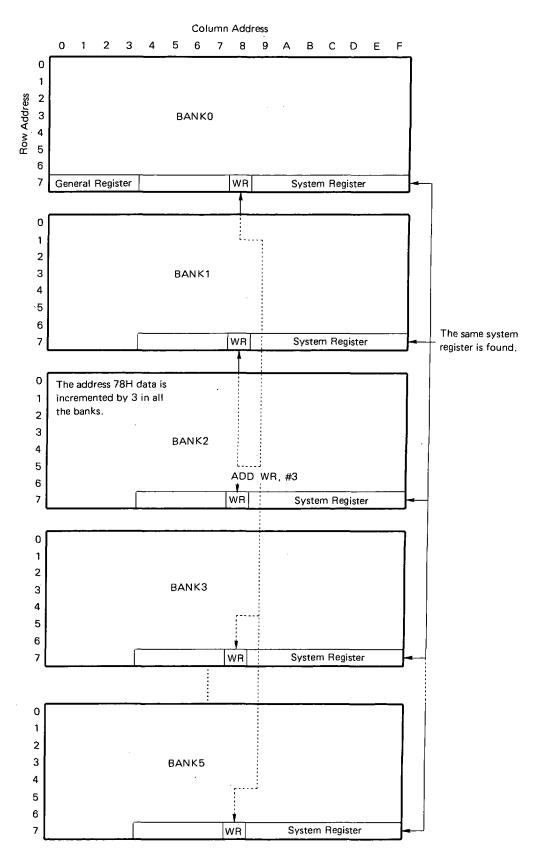

As shown in Fig. 6-1, the data memory is divided in six units called "bank". These six banks are called BANKO, BANK1, BANK2, BANK3, BANK4 and BANK5 respectively.

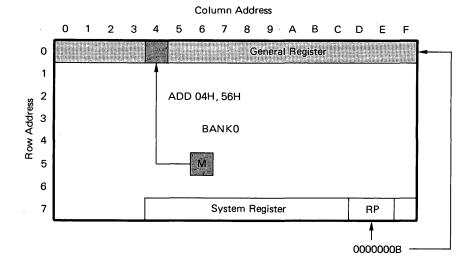

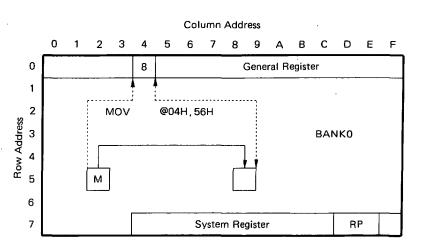

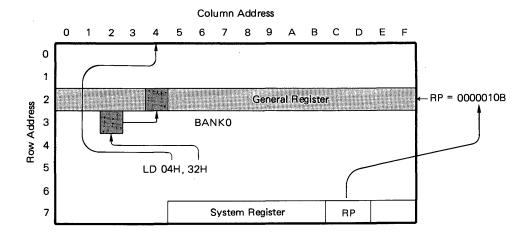

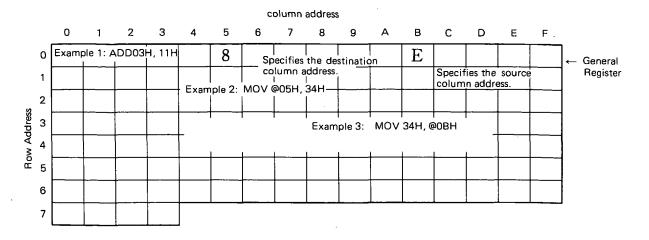

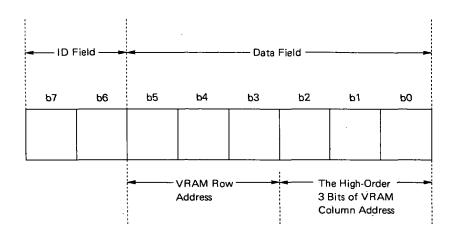

Each bank is assigned with the address at every 4 bits of data. High-order 3 bits are called "row address" and the lower 4 bits "column address". For example, the data memory whose row address is 1H and column address is AH is called the data memory of address 1AH. One address consists of the memory of 4 bits, which is called "1 nibble".

Also, the data memory is divided into functional blocks as shown in 6.1.1 to 6.1.5 below.

#### 6.1.1 System Register (SYSREG) Configurations

The system register consists of 12 nibbles assigned to addresses 74H to 7FH of the data memory. System registers are assigned regardless of the bank. In other words, any bank has the same system registers in its addresses 74H to 7FH.

The configurations are shown in Fig. 6-2.

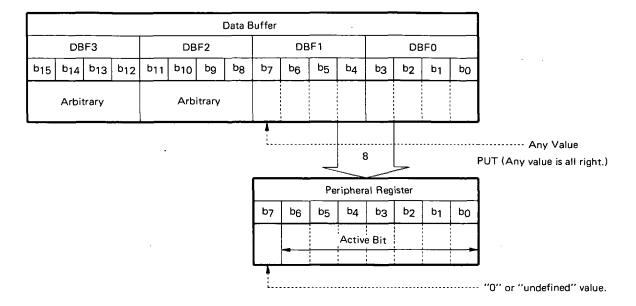

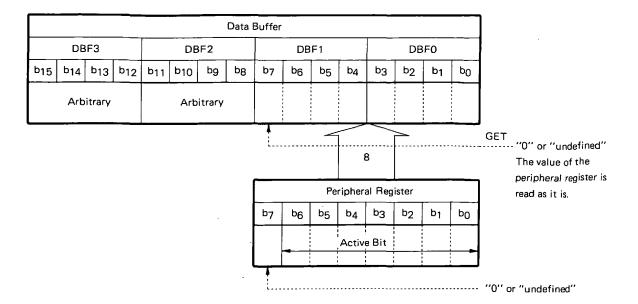

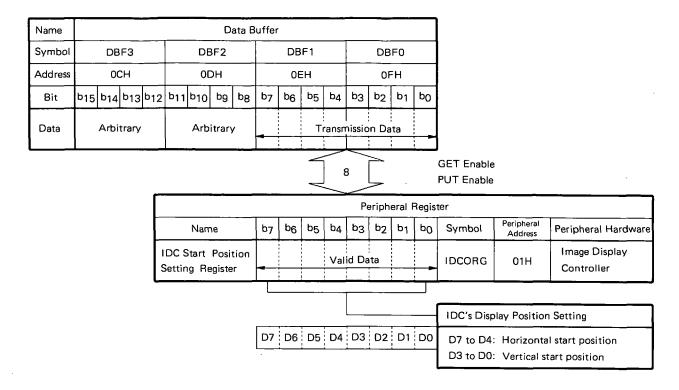

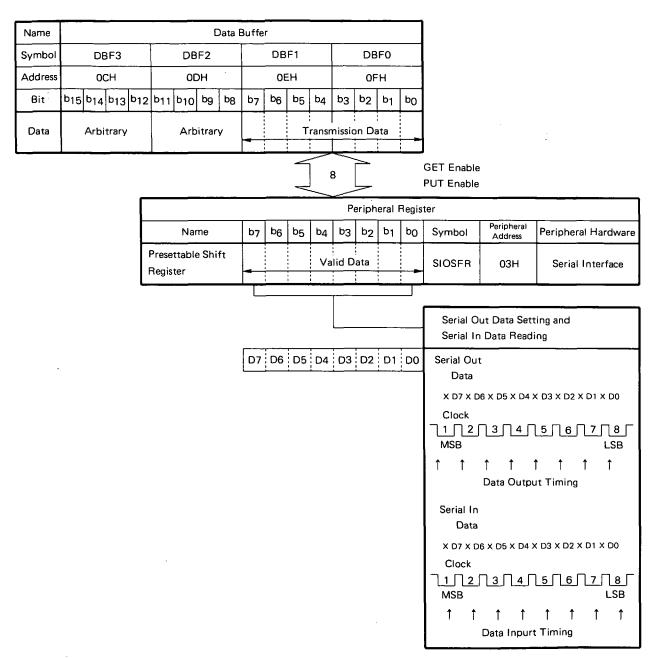

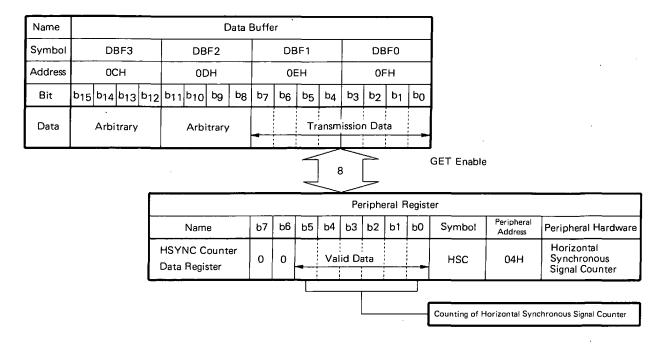

#### 6.1.2 Data Buffer (DBF) Configurations

The data buffer consists of 4 nibbles assigned to addresses 0CH to 0FH of BANKO of the data memory. The configurations are shown in Fig. 6-3.

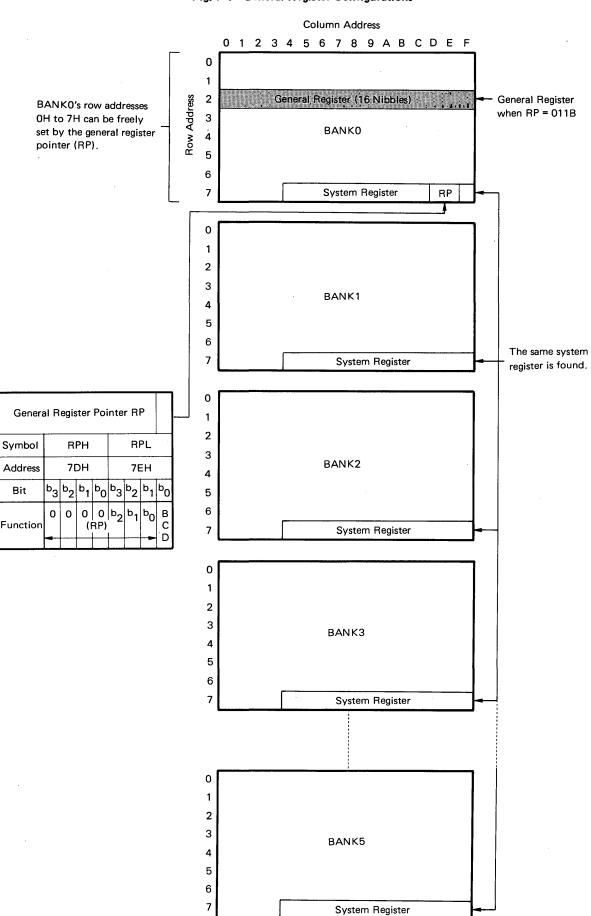

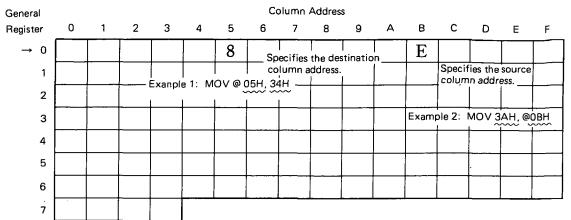

#### 6.1.3 General Register (GR) Configurations

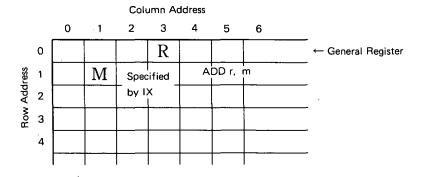

The general register consists of 16 nibbles specified by any row addresses of the data memory.

The arbitrary row address is specified by the general register pointer in the system register.

The configurations are shown in Fig. 6-4.

#### 6.1.4 Port Data Register (PORT REGISTER) Configurations

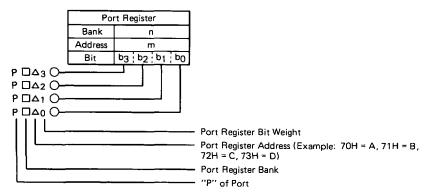

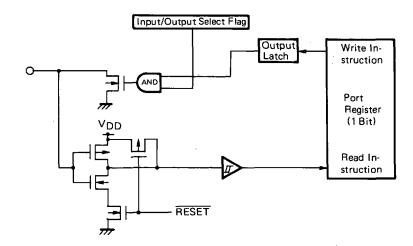

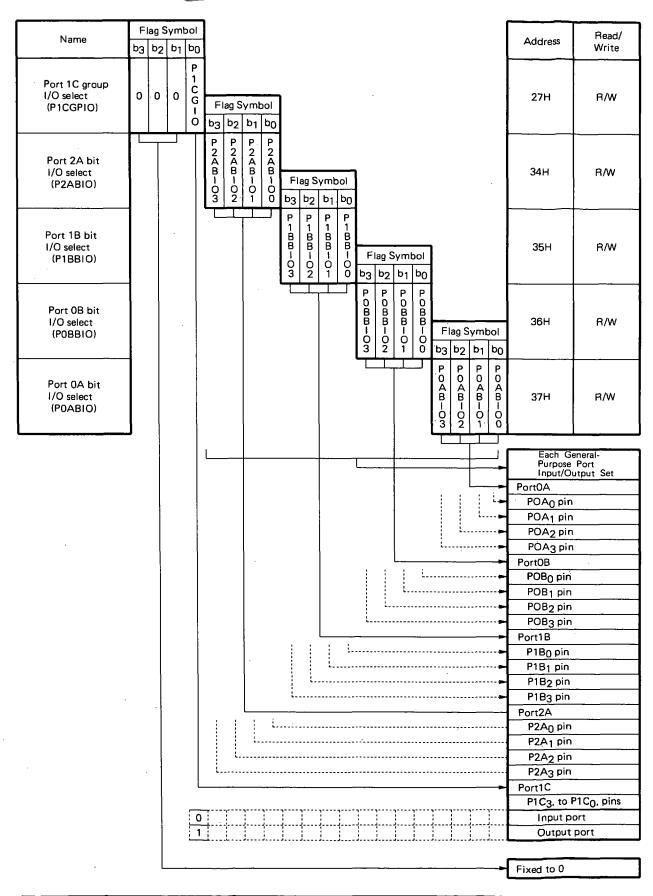

The port data register consists of 16 nibbles assigned to addresses 70H to 73H of each bank of the data memory. The configurations are shown in Fig. 6-5.

As shown in Fig. 6-5, the same port register is assigned to BANK0's address 73H, BANK2's address 73H, BANK0 and BANK4, BANK1 and BANK3 and BANK5. Therefore, in reality, the register consists of 11 nibbles.

#### 6.1.5 General-Purpose Data Memory Configurations

The general-purpose data memory refers to the remaining area of the data memory excluding the system register and the port register.

It consists of total 672 nibbles of the 112 nibbles of each of BANKO to BANK5.

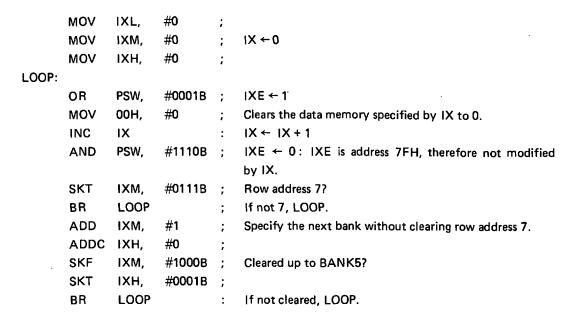

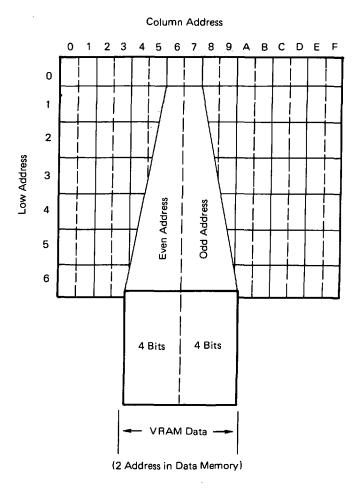

Address 00H to address 6FH of BANK2 to BANK5 can be used as VRAM with IDC. If not used as VRAM, it can be used as ordinary data memory.

The above mentioned data memory is undefined when being reset. This requires the 0 initialization (RAM CLEAR) at the early stage of the program. The neglected 0 initialization might result in the occurrence of a bug.

Fig. 6-1 Data Memory Configuration (1/2)

Fig. 6-1 Data Memory Configuration (2/2)

# Fig. 6-2 System Register Configurations

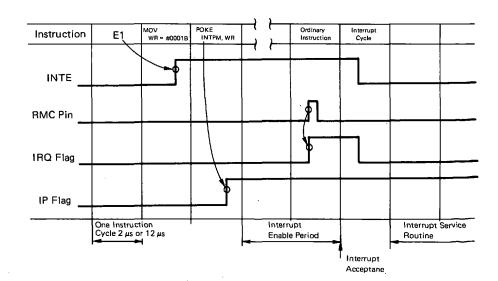

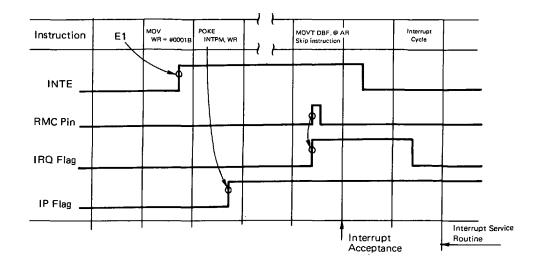

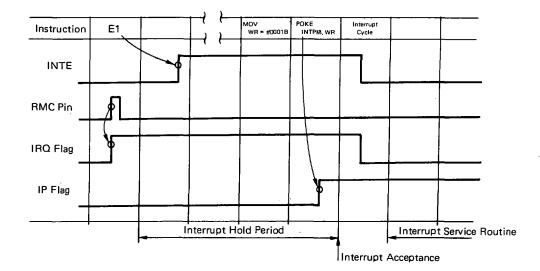

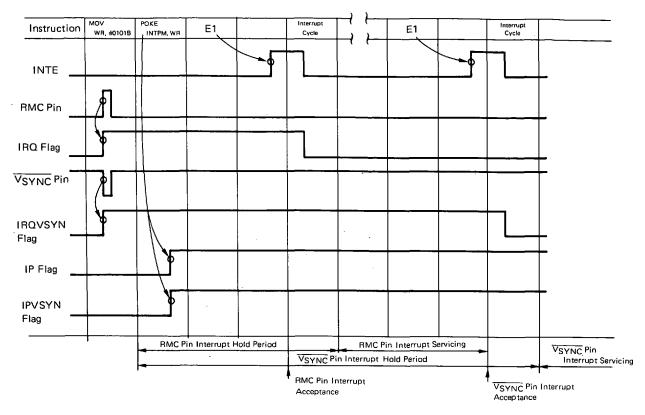

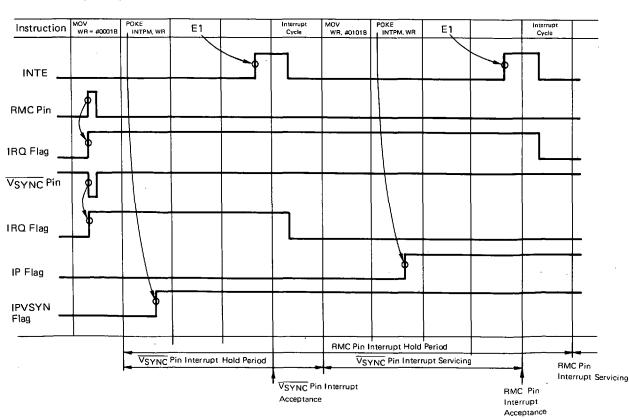

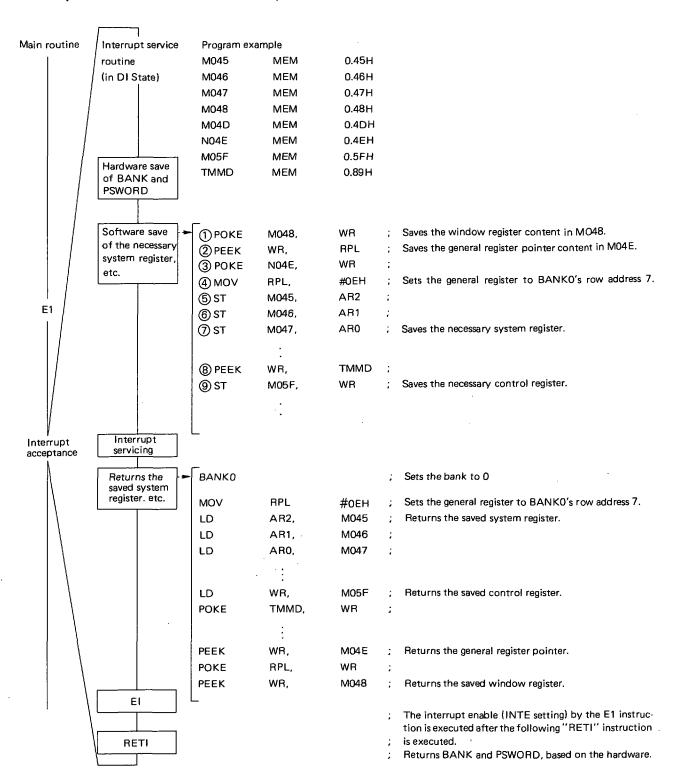

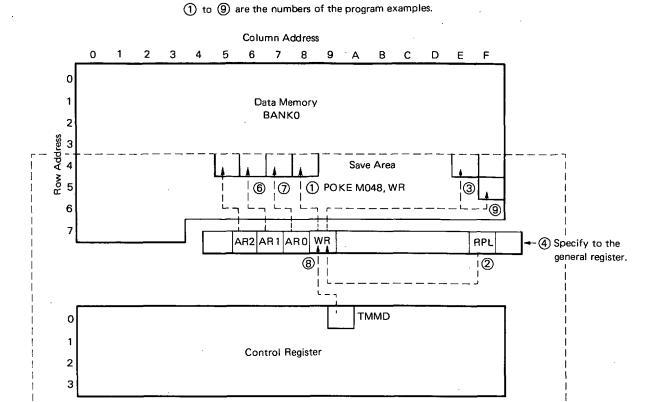

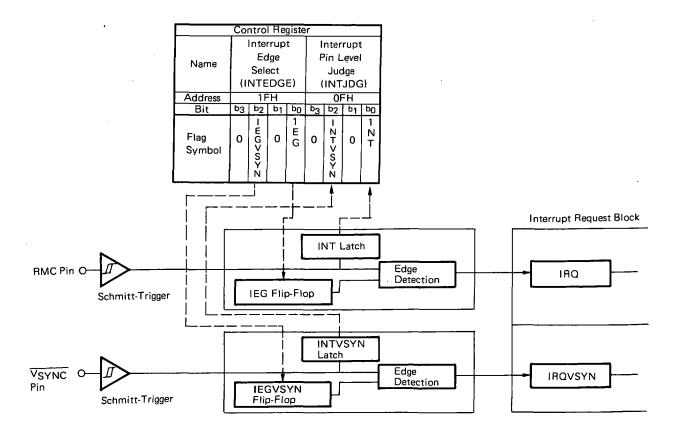

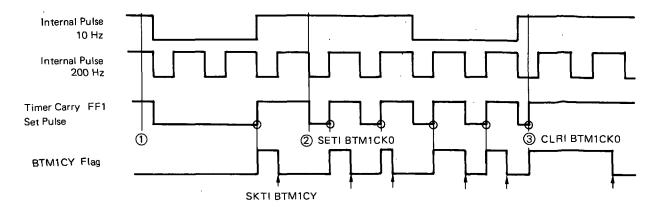

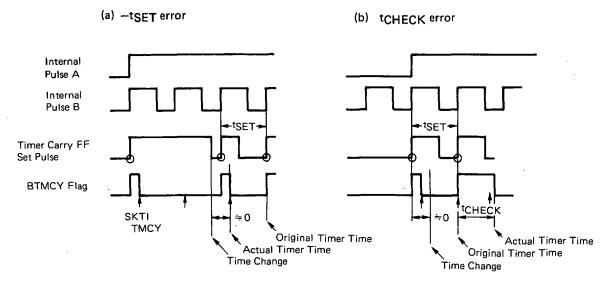

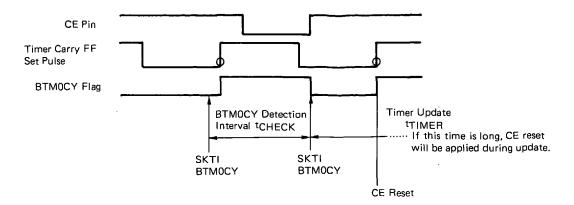

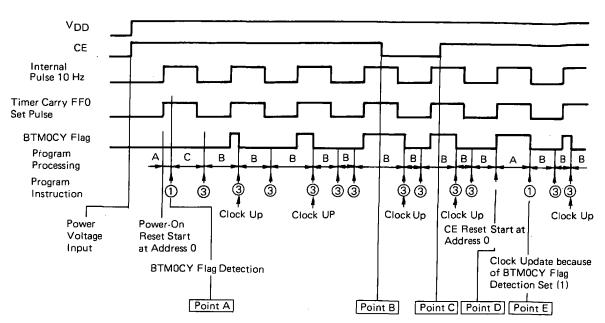

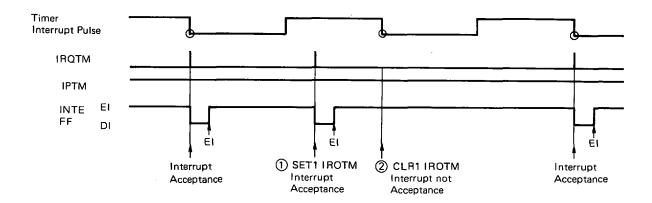

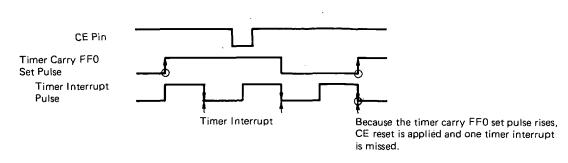

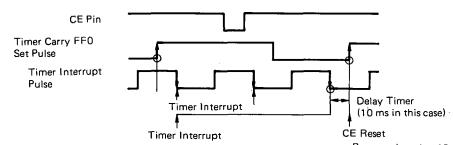

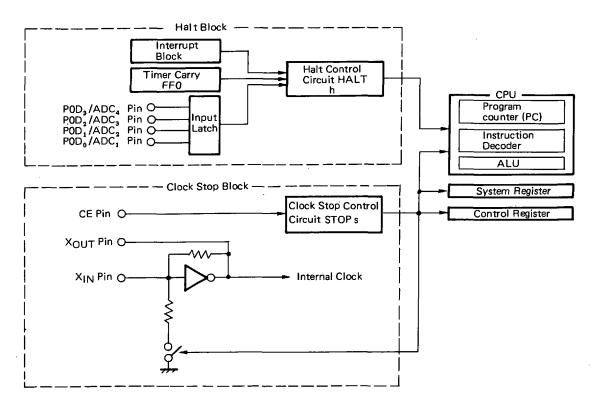

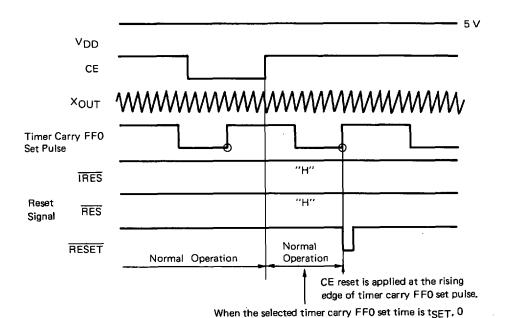

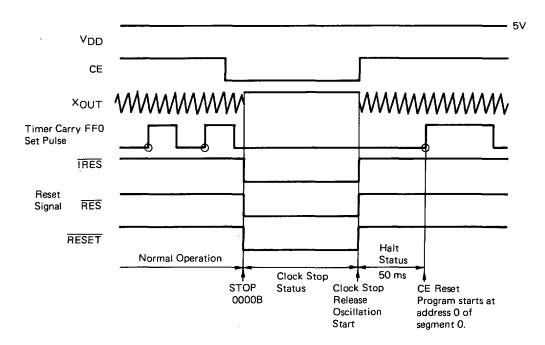

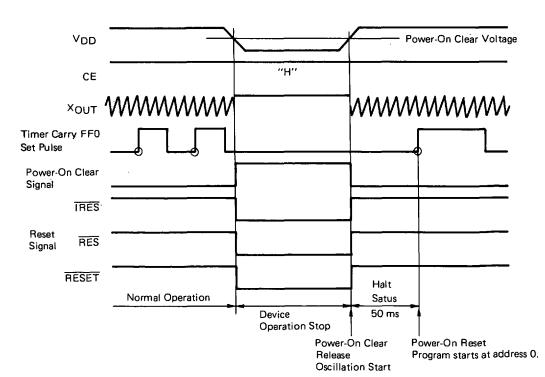

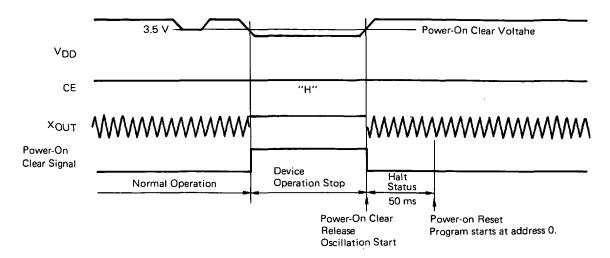

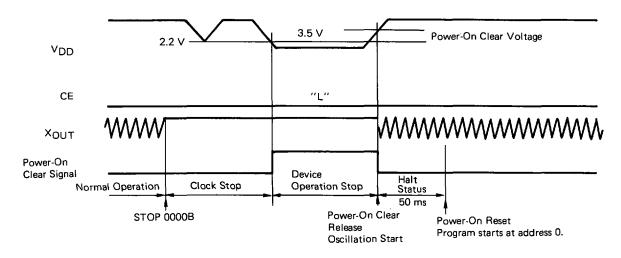

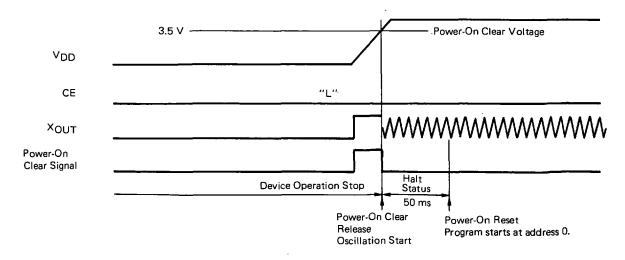

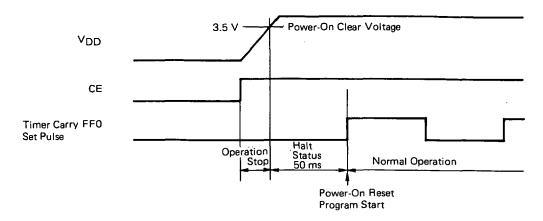

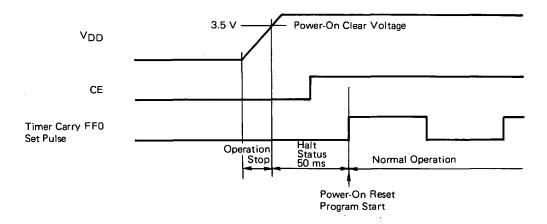

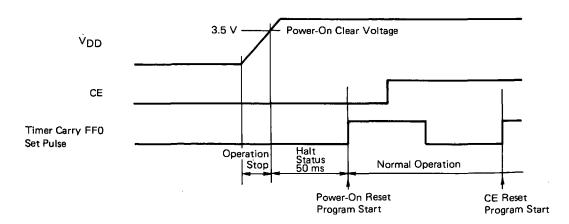

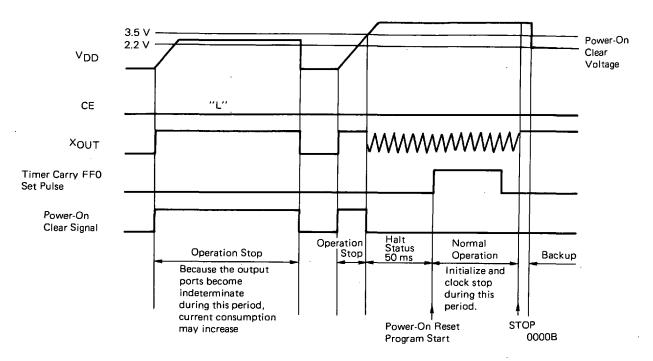

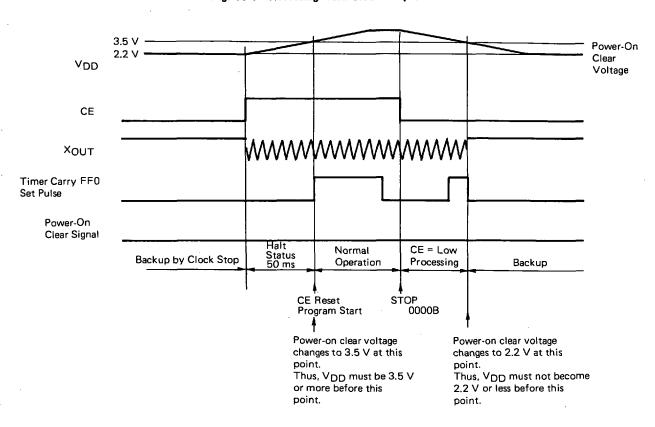

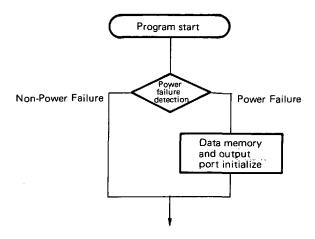

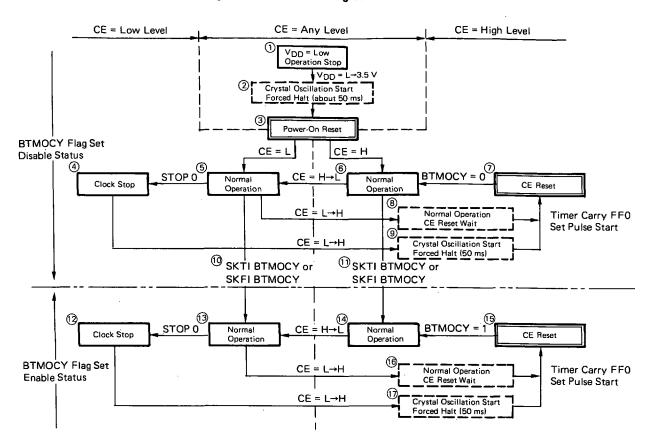

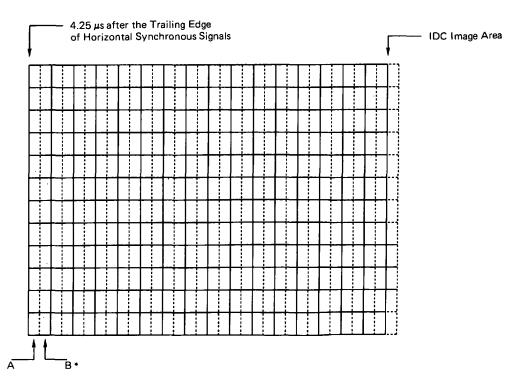

|                  | System Register (SYSREG) |     |                 |     |                            |                            |                                                                                                   |     |                            |      |     |                   |