# MOS INTEGRATED CIRCUIT $\mu$ PD6461, 6462

## CMOS LSI CHIP FOR CAMCORDER ON-SCREEN CHARACTER DISPLAY (12 ROWS $\times$ 24 COLUMNS)

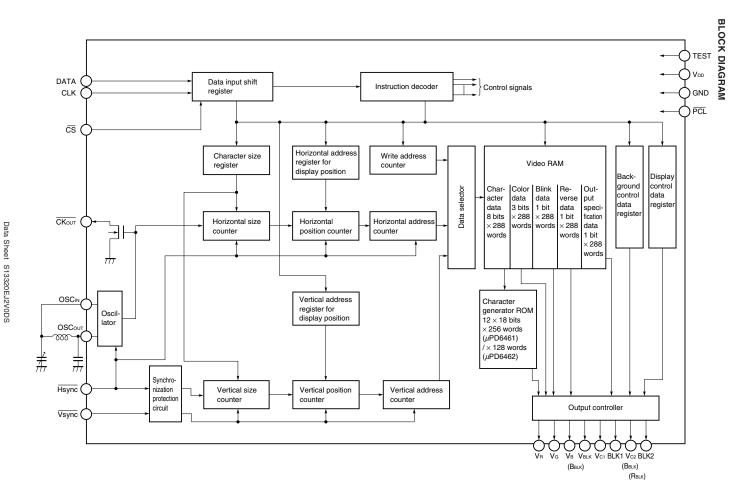

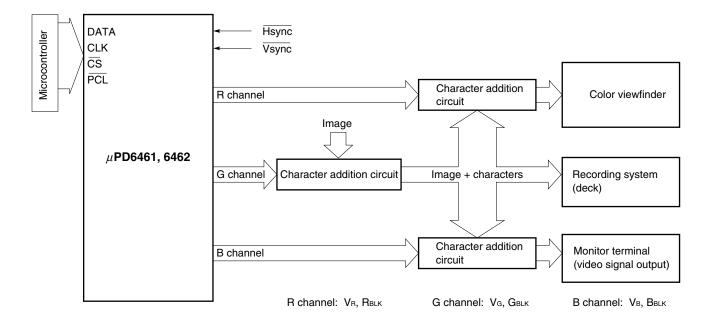

The  $\mu$ PD6461, 6462 are CMOS LSI chips designed to provide on-screen character display for camcorders. When combined with a microcontroller, the  $\mu$ PD6461, 6462 control the display of the characters displayed in the viewfinder (count, time, date, etc.) and the recording of characters onto video tape (time, date, etc.).

Each character is created using 12 (width)  $\times$  18 (height) dots. Kanji characters and graphic symbols can also be displayed by using two or more characters. The  $\mu$ PD6461, 6462 are compatible with color viewfinders and can output character signals to three channels, the RGB channel for the color viewfinder and the Vc1 and Vc2 channels for the recording system and monitor terminal.

The  $\mu$ PD6461, 6462 also have a power-on clear function and video RAM batch clear command, enabling the number of operations assigned to the microcontroller to be reduced.

#### **FEATURES**

Maximum number of characters: 12 rows × 24 columns (288 characters)

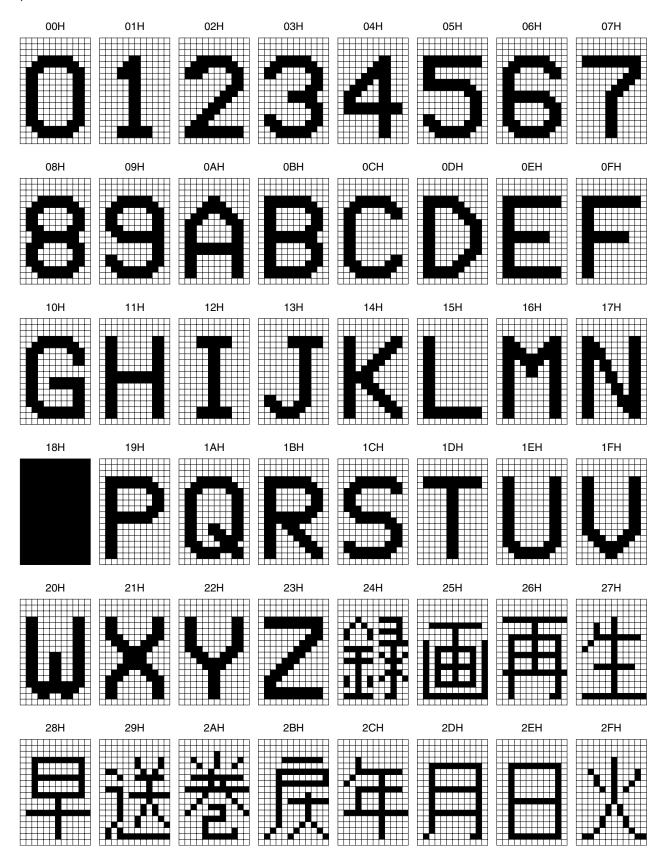

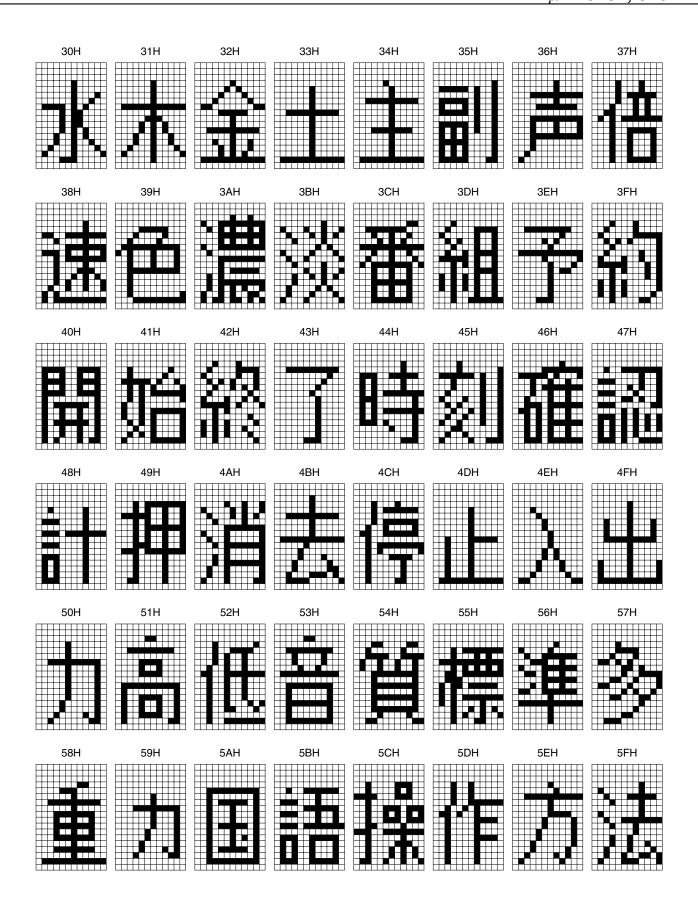

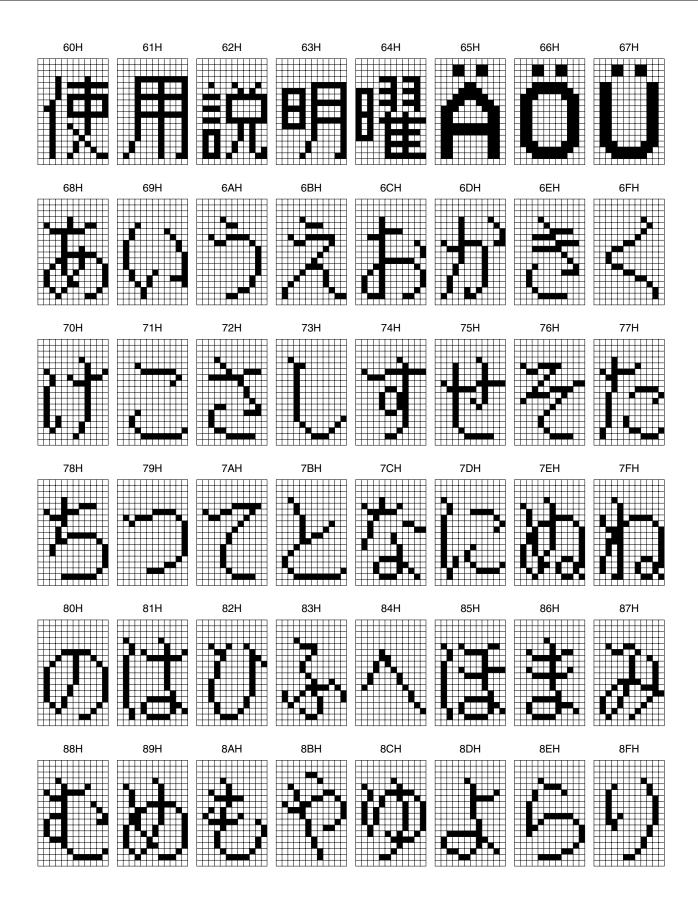

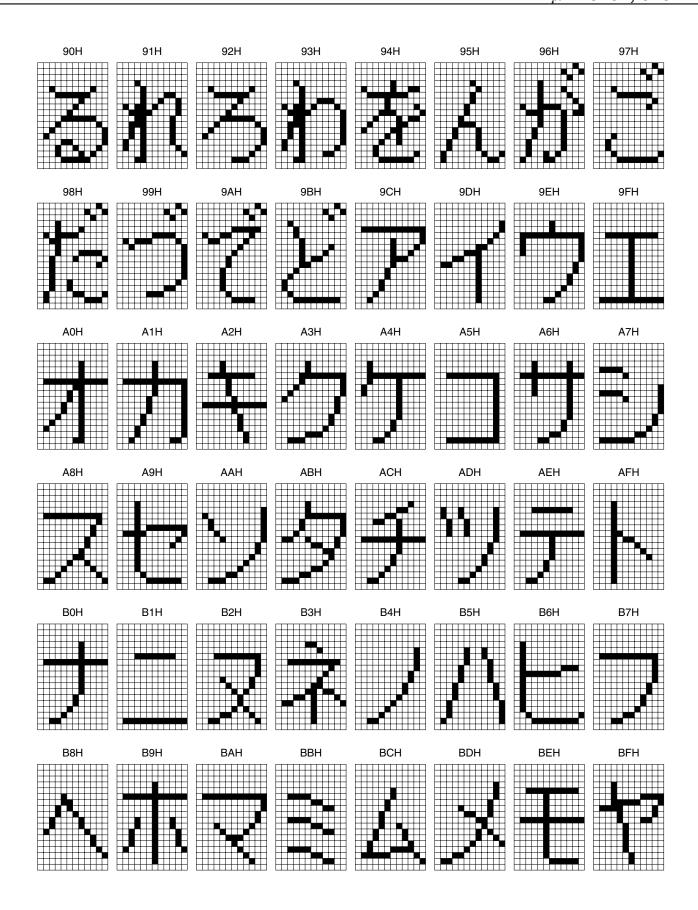

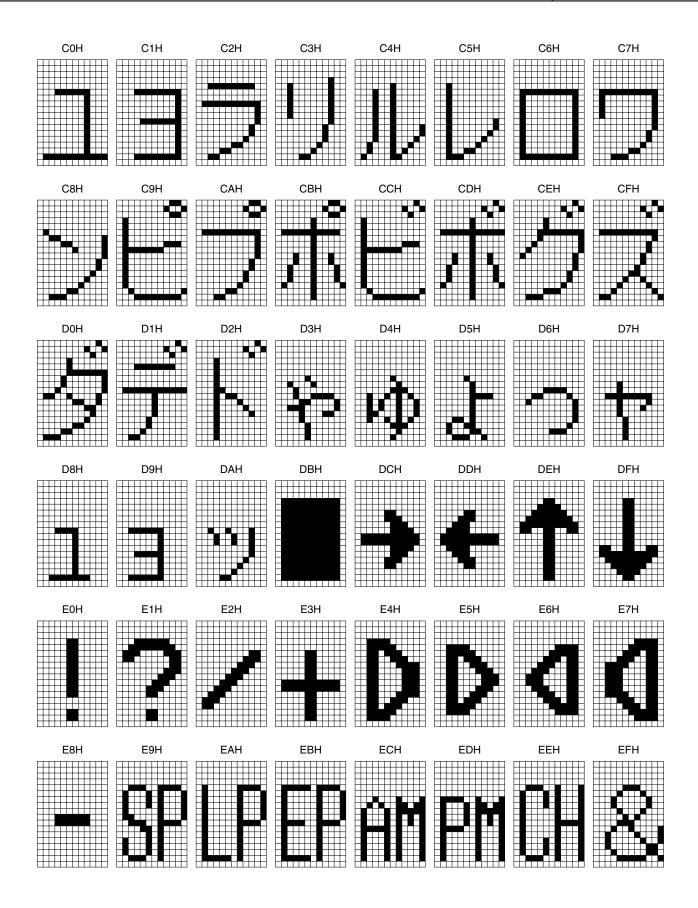

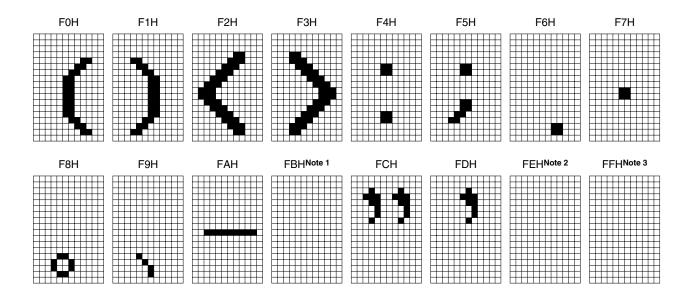

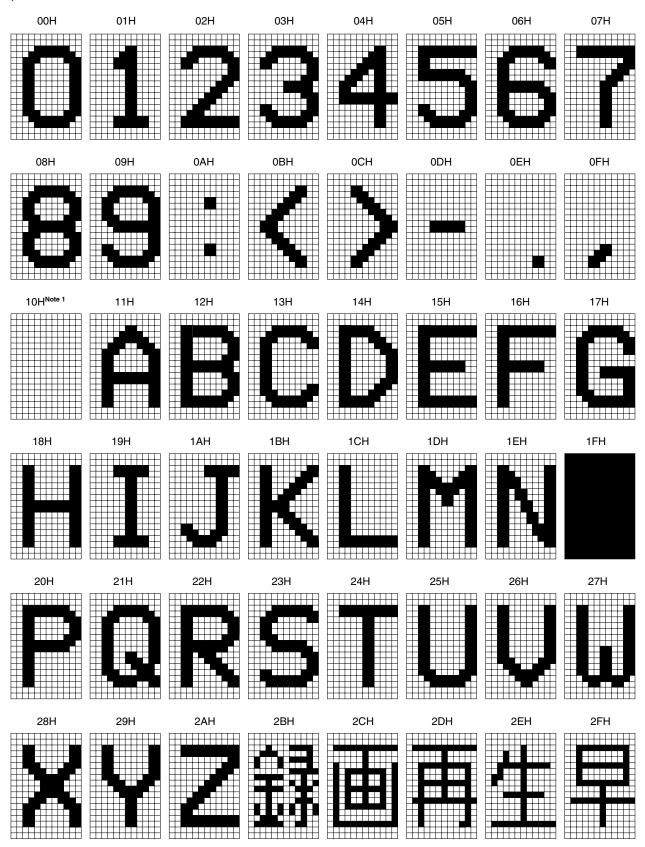

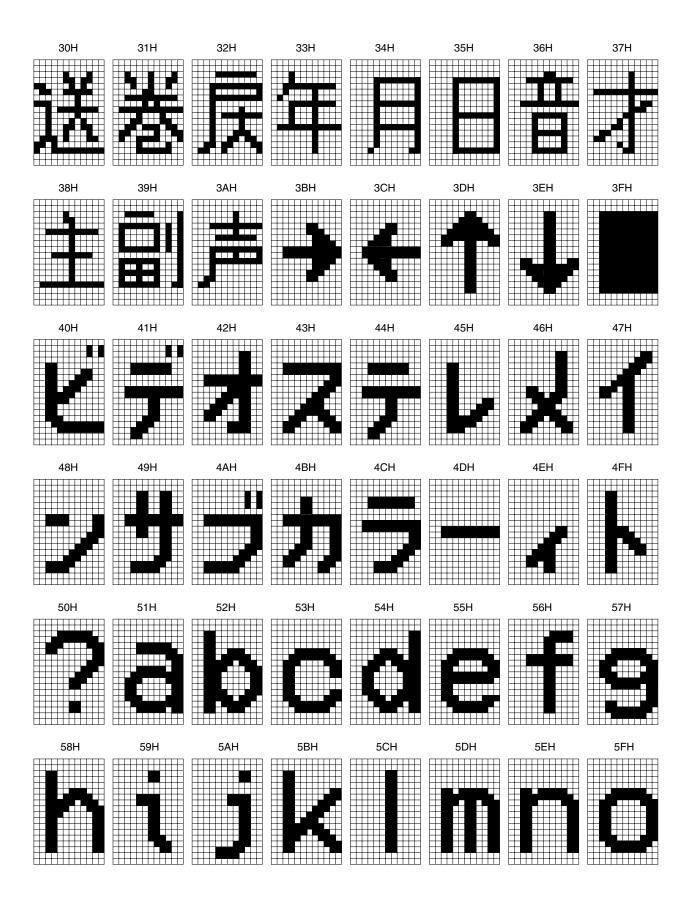

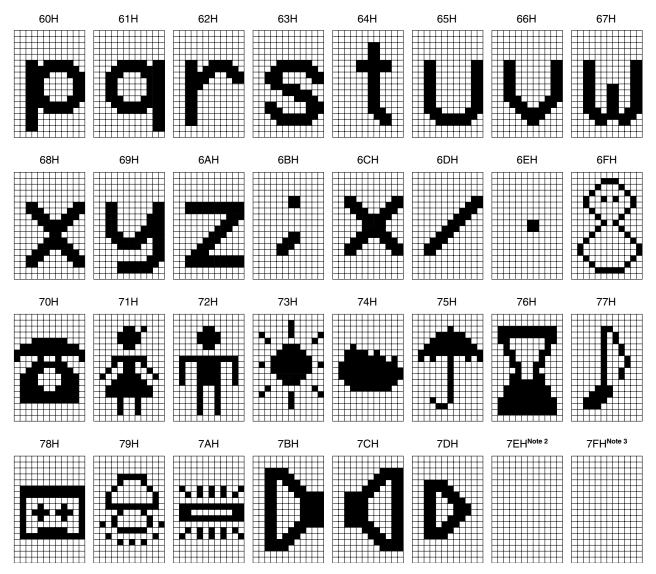

• Number of character patterns : 256 ( $\mu$ PD6461)/128 ( $\mu$ PD6462) (stored in ROM). Each pattern can be changed by

specifying a mask code option.

• Character size : One dot per line or one dot per two lines (field)

• Number of character colors : 8

Background

No background, minimum background, or overall background can be selected for the

entire screen, together with rimming ON/OFF function. Any one of 8 different colors is selectable as the background color and together with the rim color (black or white)

selectable per screen.

$\bullet$  Dot matrix : Each character consists of 12 (width) imes 18 (height) dots. There is no gap between

adjacent characters.

• Blinking : Blinking can be turned on/off for each character. The blinking ratio is 1:1. The blinking

frequency can be selected from approx. 1 Hz, 2 Hz, and 0.5 Hz for the entire screen.

Reversed characters

Specified characters can be displayed in reverse video.

Character signal output

Character signals can be output to three channels. Output mode (1) (RGB + BLK, Vc1

+ V<sub>BLK1</sub>, and V<sub>C2</sub> + V<sub>BLK2</sub>) or output mode (2) (R + R<sub>BLK</sub>, B + B<sub>BLK</sub>, and G + G<sub>BLK</sub>) can be selected by specifying a mask option. For output mode 1, three output formats are

available for the Vc1 and Vc2 channels (options A, B, and C).

Clearing of video RAM

Video RAM batch clear command and power-on clear function

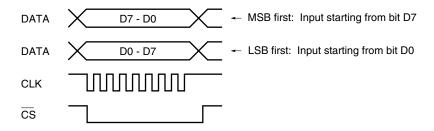

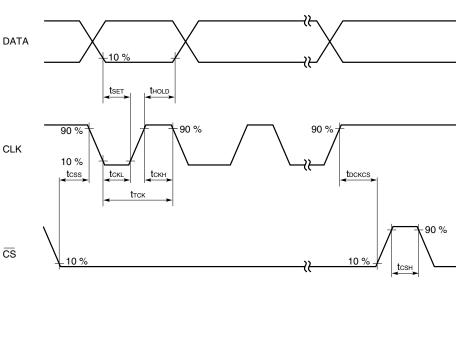

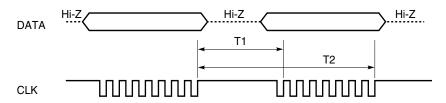

Interface with a microcontroller: 8-bit serial input supporting variable word length (LSB first or MSB first can be selected

by specifying a mask option.)

Supply voltage

Low-voltage operation possible (supply voltage range: 2.7 to 5.5 V)

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

#### **ORDERING INFORMATION**

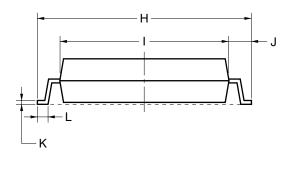

| Part number        | Package                             |

|--------------------|-------------------------------------|

| μPD6461GS-xxx      | 20-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD6461GT-xxx | 24-pin plastic SOP (9.53 mm (375))  |

| $\mu$ PD6462GS-xxx | 20-pin plastic SSOP (7.62 mm(300))  |

#### Remarks 1. xxx is a ROM code suffix.

**2.** NEC's standard models are the  $\mu$ PD6461GS-101/102,  $\mu$ PD6462GS-001. For the details of the character generator ROM, refer to **5.** CHARACTER PATTERNS.

$\mu$ PD6461GS-101: MSB first/Specified in three-line units/RGB+3BLK/Option B/LC oscillation  $\mu$ PD6461GS-102: MSB first/Specified in three-line units/RGB+Vc<sub>1</sub>+Vc<sub>2</sub>/Option B/LC oscillation  $\mu$ PD6462GS-001: MSB first/Specified in three-line units/RGB+Vc<sub>1</sub>+Vc<sub>2</sub>/Option C/LC oscillation

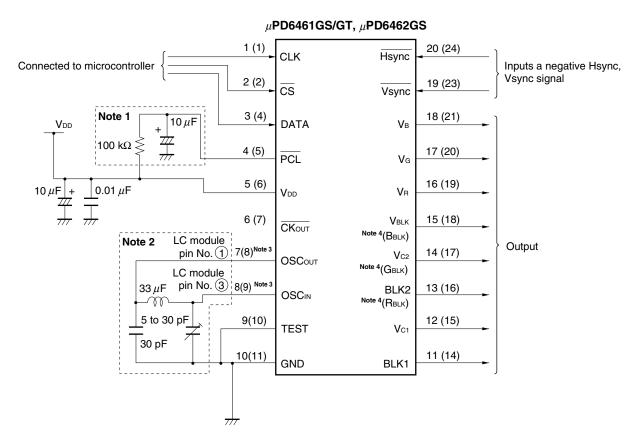

Remark Signals in ( ) are set by a mask option (RGB + RGB compatible blanking).

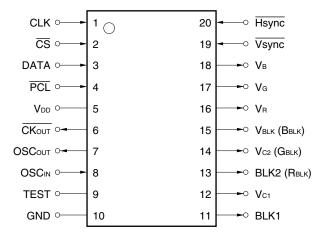

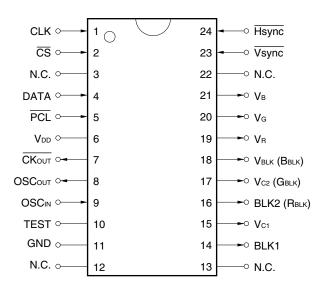

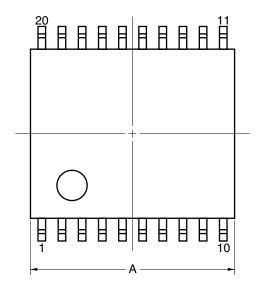

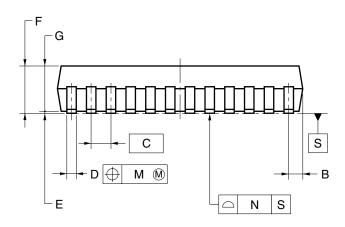

#### **PIN CONFIGURATION (TOP VIEW)**

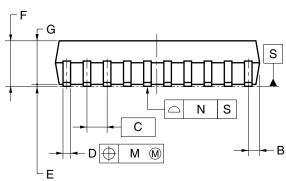

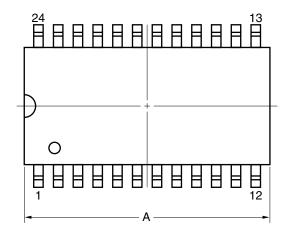

20-pin plastic SSOP (7.62 mm (300))  $\mu$ PD6461GS-xxx  $\mu$ PD6462GS-xxx

24-pin plastic SOP (9.53 mm (375))  $\mu \text{PD6461GT-xxx}$

Remarks 1. xxx indicates a ROM code suffix.

2. Signals in ( ) are set by a mask option (RGB + RGB compatible blanking).

**NEC**  $\mu$ PD6461, 6462

BBLK : Blanking B

BLK1, BLK2: Blanking Output 1, 2

CKOUT : Clock Output

CLK : Clock Input

CS : Chip Select

DATA : Data Input

GBLK : Blanking G

GND : Ground

Hsync : Horizontal Synchronous Signal Input

N.C. : No Connection

OSCIN : Oscillator Input

OSCOUT : Oscillator Output

PCL : Power-on Clear

RBLK : Blanking R

TEST : Test

V<sub>B</sub> : Character Signal Output

$V_{\mathsf{BLK}}$  : Blanking Signal Output for  $V_{\mathsf{R}},\,V_{\mathsf{G}},\,V_{\mathsf{B}}$

Vc1, Vc2 : Character Signal Output 1, 2

V<sub>DD</sub> : Power Supply

$V_{\rm G}$  : Character Signal Output  $V_{\rm R}$  : Character Signal Output

Vsync : Vertical Synchronous Signal Input

#### **PIN FUNCTIONS**

| Pin No. Note 1                | Symbol <sup>Note 2</sup>               | FunctionNote 2                                                                | Description                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|----------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | CLK                                    | Clock input                                                                   | Input pin for the data read clock. The data input to the DATA pin is read at rising edges of the clock.                                                                                                                                                                                                                         |

| 2                             | CS                                     | Chip select input                                                             | Serial transfer is accepted when this pin is low.                                                                                                                                                                                                                                                                               |

| 3 (4)                         | DATA                                   | Serial data input                                                             | Input pin for control data. Data is read in synchronization with the clock input to the CLK pin.                                                                                                                                                                                                                                |

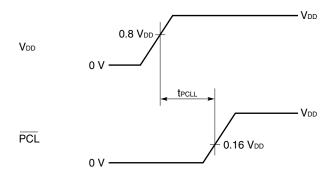

| 4 (5)                         | PCL                                    | Power-on clear                                                                | Pin used for the power-on clear function. After power-on, set this pin from low to high to initialize the IC.                                                                                                                                                                                                                   |

| 5 (6)                         | V <sub>DD</sub>                        | Power supply                                                                  | Power supply pin                                                                                                                                                                                                                                                                                                                |

| 6 (7)                         | СКоит                                  | Clock output                                                                  | N-ch open-drain output pin used to check the oscillation frequency                                                                                                                                                                                                                                                              |

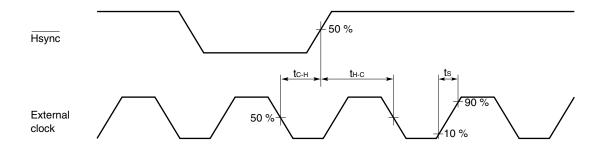

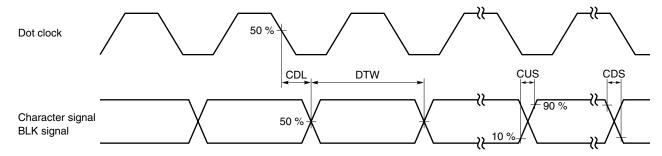

| 7 (8)<br>8 (9)                | OSCOUT<br>OSCIN                        | LC oscillator input/<br>output<br>OSC <sub>IN</sub> : External clock<br>input | Input and output pins for the oscillator for generating a dot clock. Connect the oscillation coil and capacitors to these pins.  (When an external clock input is selected by specifying a mask option, input an external clock (synchronized with Hsync) to the OSC <sub>IN</sub> pin. Leave the OSC <sub>OUT</sub> pin open.) |

| 9 (10)                        | TEST                                   | Test pin                                                                      | Pin used for testing the IC. Usually, connect this pin to ground. The IC cannot enter test mode while this pin is connected to ground.                                                                                                                                                                                          |

| 10 (11)                       | GND                                    | Ground pin                                                                    | Connect this pin to the system ground.                                                                                                                                                                                                                                                                                          |

| 11 (14)                       | BLK1                                   | Blanking signal output 1                                                      | Pin used to output the blanking signal for the video signal output from the Vc <sub>1</sub> pin. The blanking signal is high active.  (When RGB compatible blanking has been selected by specifying a mask option, this pin outputs the logical OR of RBLK, GBLK, and BBLK.)                                                    |

| 12 (15)                       | V <sub>C1</sub>                        | Character signal output 1                                                     | Pin used to output a high-active character signal.  (When RGB compatible blanking has been selected by specifying a mask option, this pin outputs the logical OR of V <sub>R</sub> , V <sub>G</sub> , and V <sub>B</sub> .)                                                                                                     |

| 13 (16)                       | BLK2<br>(R <sub>BLK</sub> )            | Blanking signal output 2<br>(blanking R)                                      | Pin used to output the blanking signal for the video signal output from the $V_{\rm C2}$ pin. The blanking signal is high active. (This pin outputs the blanking signal for the video signal output from the $V_{\rm R}$ pin. The blanking signal is high active.)                                                              |

| 14 (17)                       | V <sub>C2</sub><br>(G <sub>BLK</sub> ) | Character signal output<br>2<br>(blanking G)                                  | Pin used to output a high-active character signal. (This pin outputs the blanking signal for the video signal output from the $V_{\rm B}$ pin. The blanking signal is high active.)                                                                                                                                             |

| 15 (18)                       | VBLK<br>(BBLK)                         | Blanking signal output<br>(blanking B)                                        | Pin used to output the blanking signal for the video signals output from the $V_R$ , $V_G$ , and $V_B$ pins. The blanking signal is high active. (This pin outputs the blanking signal for the video signal output from the $V_B$ pin. The blanking signal is high active.)                                                     |

| 16 (19)<br>17 (20)<br>18 (21) | VR<br>VG<br>VB                         | Character signal output                                                       | Pins used to output high-active character signals.                                                                                                                                                                                                                                                                              |

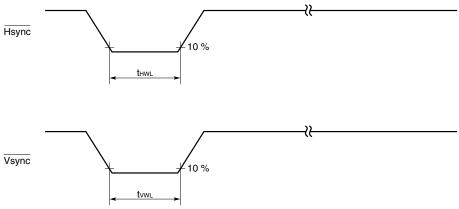

| 19 (23)                       | Vsync                                  | Vertical synchronizing signal input                                           | Input a low-active vertical synchronizing signal to this pin.                                                                                                                                                                                                                                                                   |

| 20 (24)                       | Hsync                                  | Horizontal synchroniz-<br>ing signal input                                    | Input a low-active horizontal synchronizing signal to this pin.                                                                                                                                                                                                                                                                 |

| (3, 12, 13, 22)               | N.C.                                   | No connection                                                                 | Vacant pin                                                                                                                                                                                                                                                                                                                      |

**Notes 1.** Pin numbers indicated in ( ) are that of the  $\mu$ PD6461GT-xxx.

2. Signals in ( ) are set by a mask option (RGB + RGB compatible blanking).

#### **CONTENTS**

| 1. | MAS        | K CODE OPTIONS                                          | 8  |

|----|------------|---------------------------------------------------------|----|

|    | 1.1        | MASK CODE OPTIONS                                       | 8  |

|    | 1.2        | HOW TO SELECT MASK OPTIONS                              | 9  |

|    | 1.3        | APPLICATION BLOCK DIAGRAMS                              | 10 |

|    | 1.4        | DISPLAY IN RGB+Vc1+Vc2 MODE                             | 11 |

|    |            | 1.4.1 Character Signal Output When Option A is Selected | 14 |

|    |            | 1.4.2 Character Signal Output When Option B is Selected | 15 |

|    |            | 1.4.3 Character Signal Output When Option C is Selected | 16 |

|    |            | 1.4.4 Display of Vc2-Specified Characters               | 17 |

|    | 1.5        | OUTPUTTING BACKGROUND                                   | 18 |

|    |            |                                                         |    |

| 2. | COM        | MANDS                                                   | 19 |

|    | 2.1        | COMMAND FORMAT                                          |    |

|    | 2.2        | COMMANDS AND THEIR BITS                                 | 19 |

|    | 2.3        | POWER-ON CLEAR FUNCTION                                 | 21 |

| 3. | COM        | MAND DETAILS                                            | 22 |

| ٥. | 3.1        | VIDEO RAM BATCH CLEAR COMMAND                           |    |

|    | 3.2        | CHARACTER DISPLAY CONTROL COMMAND                       |    |

|    | 3.3        | BACKGROUND/RIM COLOR CONTROL COMMAND                    |    |

|    | 3.4        | 3-CHANNEL INDEPENDENT DISPLAY ON/OFF COMMAND            |    |

|    | 3.5        | CHARACTER REVERSE ON/OFF COMMAND                        |    |

|    | 3.6        | CHARACTER DISPLAY POSITION CONTROL COMMAND              |    |

|    | 3.7        | WRITE ADDRESS CONTROL COMMAND                           |    |

|    | 3.8        | OUTPUT PIN CONTROL COMMAND                              |    |

|    | 3.9        | CHARACTER SIZE CONTROL COMMAND                          |    |

|    | 3.10       | 3-CHANNEL INDEPENDENT BACKGROUND CONTROL COMMAND        |    |

|    | 3.11       | TEST MODE COMMAND                                       |    |

|    | 3.12       | DISPLAYED CHARACTER CONTROL COMMAND                     |    |

| 4. | 0014       | MAND TRANSFER                                           | 00 |

| 4. |            | 1-BYTE COMMANDS                                         |    |

|    | 4.1        |                                                         |    |

|    | 4.2<br>4.3 | 2-BYTE COMMANDS                                         |    |

|    | 4.3        | CONTINUOUS INPUT OF COMMAND                             |    |

|    | 4.4        | 4.4.1 When End Code is Not Used                         |    |

|    |            | 4.4.2 When End Code is Used                             |    |

|    |            | 4.4.2 Wileli Eliu Coue is Oseu                          | 39 |

| 5. | СНА        | RACTER PATTERNS                                         | 40 |

| 6. | ELEC       | CTRICAL CHARACTERISTICS                                 | 50 |

| 7. | APPI       | LICATION CIRCUIT EXAMPLE                                | 54 |

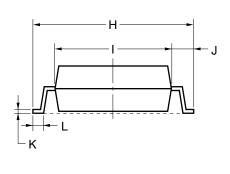

| 8. | PAC        | KAGE DRAWINGS                                           | 55 |

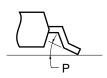

| 9. | REC        | OMMENDED SOLDERING CONDITIONS                           | 57 |

#### 1. MASK CODE OPTIONS

#### 1.1 MASK CODE OPTIONS

The  $\mu$ PD6461,  $\mu$ PD6462 provide mask options for selecting the following items:

|     | Item                            |                        | Selec      | tions                        |          |  |

|-----|---------------------------------|------------------------|------------|------------------------------|----------|--|

| (1) | Data transfer                   | LSB first              |            | MSB first                    |          |  |

| (2) | Vertical display start position | Specified in three-lin | ne units   | Specified in nine-line units |          |  |

| (3) | Pin selection                   | RGB+Vc1+Vc2            |            | RGB+3BLK                     |          |  |

| (4) | Output distribution format      | Option A               | A Option B |                              | Option C |  |

| (5) | Dot clock                       | LC oscillation         |            | External clock input         |          |  |

#### (1) Data transfer

Select the command transfer format.

#### (2) Vertical display start position

Select the units used for specifying the vertical display start position of the character display area. In three-line units, the vertical display start position can be set more finely than in nine-line units.

#### (3) Pin selection

Select the pins used to output character signals. In RGB+Vc<sub>1</sub>+Vc<sub>2</sub> mode, character signals are output from the  $V_R$ ,  $V_G$ ,  $V_B$ ,  $V_{BLK}$ ,  $V_{C1}$ , BLK1,  $V_{C2}$ , and BLK2 pins. In RGB+3BLK mode, character signals are output from the  $V_R$ ,  $V_G$ ,  $V_B$ ,  $V_{BLK}$ ,  $V_{BLK}$ ,  $V_{C1}$ , and  $V_{C1}$ , and  $V_{C1}$  pins.

When displaying colored characters in a color viewfinder, select RGB+Vc1+Vc2 mode. When assigning a separate character signal for each color, select RGB+3BLK mode.

#### (4) Output distribution format

Select the format to be used to distribute character signals to the Vc1 and Vc2 channels when RGB+Vc1+Vc2 mode is selected. (When RGB+3BLK mode is selected, select option A as the output distribution format. Options B and C are invalid.)

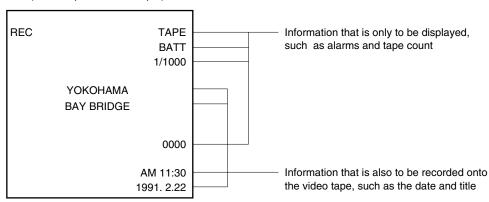

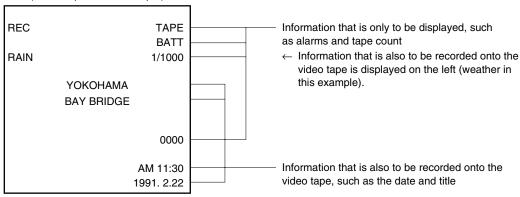

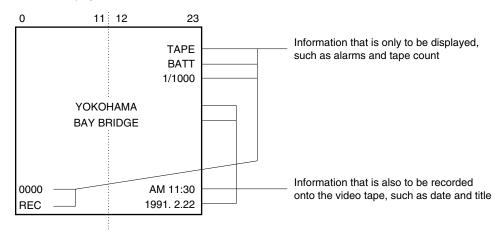

When an on-screen IC is used in a camcorder, some information is displayed in the viewfinder and recorded onto video tape (such as a date and title). Other information, however, need only be displayed in the viewfinder (battery or focus alarm and tape count). The  $\mu$ PD6461, 6462 can distribute such information to different output channels in units of rows or half rows. You can select option A, option B, and option C as the output distribution format (only when RGB+Vc1+Vc2 mode is selected).

#### (5) Dot clock

Select the dot clock to be used to display characters. When an external clock input is selected, refer to **EXTERNAL CLOCK INPUT** in 6. **ELECTRICAL CHARACTERISTICS**.

#### 1.2 HOW TO SELECT MASK OPTIONS

To select mask options, use the option setting command (OC) of the Character Pattern Editor, a tool designed for editing character pattern data.

Activate the Character Pattern Editor, then display the following setting menu:

```

OC (COMMAND INPUT)

OPTION DATA (0---LSB FAST , 1---MSB FAST

.....(1)

OPTION DATA (0---V:9H

, 1---V:3H

.....(2)

) :

OPTION DATA (0---RGB+3BLK, 1---RGB+Vc1+Vc2):

.....(3)

OPTION DATA (0---OUTPUT 20, 1---OUTPUT 21 ) :

.....(4)

OPTION DATA (0---OUTPUT 10, 1---OUTPUT 11 ) :

.....(5)

OPTION DATA (0---EXT CLK

, 1---LC

.....(6)

) :

OPTION DATA (0---LC

, 1---EXT CLK

) :

.....(7)

```

Actually, the above menu is displayed one line at a time. Once you have selected an option, the next line is displayed. Select 0 or 1 for lines (1), (2), (3), (6), and (7), according to the setting to be made. For the dot clock, however, make the same settings (different values) for lines (6) and (7). For example, when selecting LC oscillation, select "LC" for both lines (1 for (6) and 0 for (7)). Don't select external clock input for lines (6) and/or (7).

When selecting the output distribution format, select the values on lines (4) and (5) as follows:

|          | (4)          | (5)          |  |  |

|----------|--------------|--------------|--|--|

| Option A | 1(OUTPUT 21) | 0(OUTPUT 10) |  |  |

| Option B | 0(OUTPUT 20) | 0(OUTPUT 10) |  |  |

| Option C | 1(OUTPUT 21) | 1(OUTPUT 11) |  |  |

The settings are valid only when RGB+ $Vc_1+Vc_2$  mode has been selected. Select option A (1, 0) when RGB+3BLK mode has been selected.

The following table lists the correspondence between the command bits and the lines of the setting menu. Specify 0 or 1 for each bit.

| D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|----|-----|-----|-----|-----|-----|-----|-----|

| 0  | (1) | (2) | (3) | (4) | (5) | (6) | (7) |

Command OD displays the result of the selection, as a hexadecimal number.

Example: When the mask options are selected as follows:

| Mask option                       | Bit | Command |

|-----------------------------------|-----|---------|

| MSB first                         | D6  | 1       |

| Specification in three-line units | D5  | 1       |

| RGB+3BLK                          | D4  | 0       |

| Option A (only option A can be    | D3  | 1       |

| specified in RGB+3BLK mode)       | D2  | 0       |

| LC oscillation                    | D1  | 1       |

|                                   | D0  | 0       |

The command bits are set as follows:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  |

$\rightarrow$ Command OD displays 6AH.

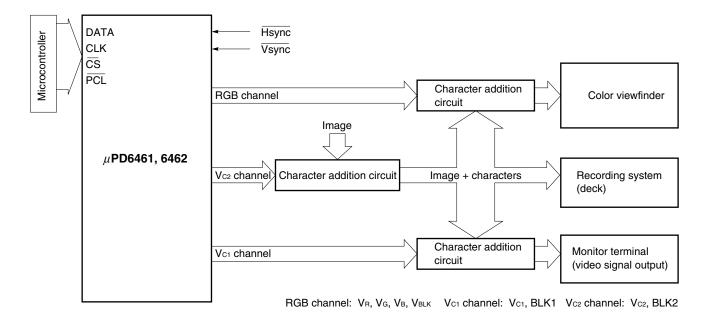

#### 1.3 APPLICATION BLOCK DIAGRAMS

Example of application to a camcorder (1) (in RGB+ $Vc_1+Vc_2$  mode) (The  $V_B$ ,  $V_G$ ,  $V_B$ ,  $V_{BLK}$ ,  $V_{C1}$ , BLK1,  $Vc_2$ , and BLK2 pins are used.)

Example of application to a camcorder (2) (in RGB+3BLK mode for RGB compatible blanking) (The V<sub>R</sub>, V<sub>G</sub>, V<sub>B</sub>, R<sub>BLK</sub>, G<sub>BLK</sub>, and B<sub>BLK</sub> pins are used.)

#### 1.4 DISPLAY IN RGB+Vc1+Vc2 MODE

The  $\mu$ PD6461, 6462 provide three options, A, B, and C, for the output distribution format. This section describes how character signals are output when each option is selected. Output is controlled with the output pin control command (refer to **3.8 OUTPUT PIN CONTROL COMMAND** for details).

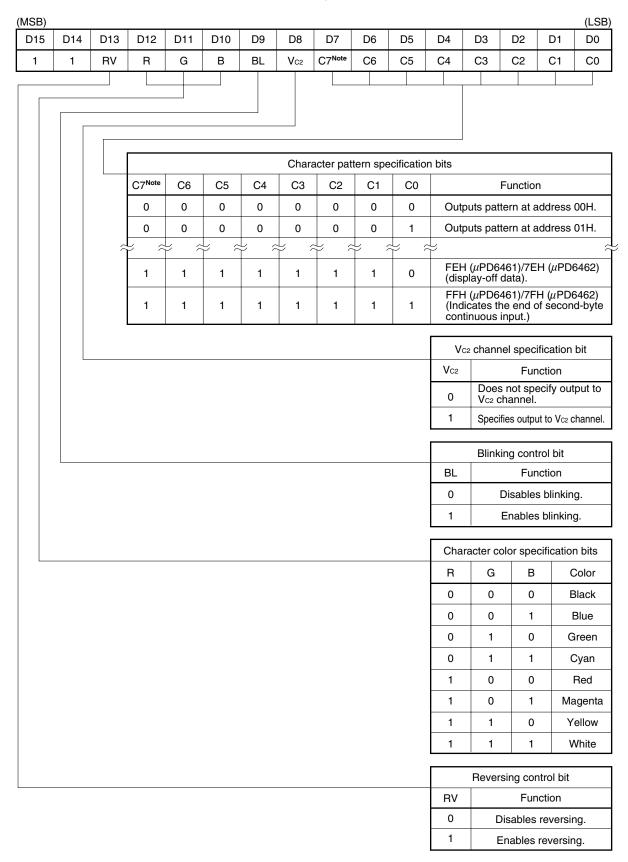

Output pin control command for MSB-first transfer (Command bits are input starting from the most significant bit (MSB), D15.)

(This command is a 2-byte command. 16 bits must be input for each command, even for continuous input.)

| (MSB) |     |     |     |     |     |    |        |                                                                |                 |          |                |            |            |               | (LSB)         |

|-------|-----|-----|-----|-----|-----|----|--------|----------------------------------------------------------------|-----------------|----------|----------------|------------|------------|---------------|---------------|

| D15   | D14 | D13 | D12 | D11 | D10 | D9 | D8     | D7                                                             | D6              | D5       | D4             | D3         | D2         | D1            | D0            |

| 1     | 0   | 0   | 1   | 1   | 1   | 0  | 0      | V <sub>C2</sub>                                                | V <sub>C1</sub> | 0        | 0              | AR3        | AR2        | AR1           | AR0           |

|       |     |     |     |     |     |    |        |                                                                |                 |          |                |            |            |               |               |

|       |     |     |     |     |     |    |        |                                                                |                 |          |                |            |            |               |               |

|       |     |     |     |     |     |    |        |                                                                |                 |          | Row spe        | cificatio  | n bits     |               |               |

|       |     |     |     |     |     |    |        | AR3                                                            | AR2             | AR1      | AR0            |            | Fι         | ınction       |               |

|       |     |     |     |     |     |    |        | 0 0 0 0 Specifies row 0.                                       |                 |          |                |            |            |               |               |

|       |     |     |     |     |     |    |        | 0 0 0 1 Specifies row 1.                                       |                 |          |                |            |            |               | 1.            |

|       |     |     |     |     |     |    | ?      |                                                                | <u> </u>        | ¥        | <del>ک</del> ۶ | ¥          |            |               |               |

|       |     |     |     |     |     |    |        | 1                                                              | 0               | 1        | 1              |            | Specif     | ies row       | 11.           |

|       |     |     |     |     |     |    |        |                                                                |                 | 0        | ther valu      | ıes are i  | nvalid.    |               |               |

|       |     |     |     |     |     | Op | tion A |                                                                |                 |          | Output p       | in contro  | ol bits    |               |               |

|       |     |     |     |     |     |    |        | V <sub>C2</sub>                                                | V <sub>C1</sub> |          | Output f       |            |            |               |               |

|       |     |     |     |     |     |    |        | 0                                                              | 0               |          |                |            |            | : Fixed t     | o low level   |

|       |     |     |     |     |     |    |        | 0                                                              | 1               | Vc1: Fix | ed to lov      | v level. ` | Vc2: Out   | puts a sp     | ecified row   |

|       |     |     |     |     |     |    |        |                                                                |                 | ı        |                |            |            | •             |               |

|       |     |     |     |     |     | Ор | tion B |                                                                |                 |          | Output p       |            |            |               |               |

|       |     |     |     |     |     |    |        | V <sub>C2</sub>                                                | V <sub>C1</sub> | _        | Output f       |            |            |               |               |

|       |     |     |     |     |     |    |        | 0                                                              | 0               |          | ·              |            | c2: Fixed  |               |               |

|       |     |     |     |     |     |    |        | 0                                                              | 1               | Vc1: Ot  | tputs all      | rows. V    | c2: Outp   | uts a spe     | ecified row.  |

|       |     |     |     |     |     | Ор | tion C |                                                                |                 | (        | Output p       | in contro  | ol bits    |               |               |

|       |     |     |     |     |     |    |        | V <sub>C2</sub> V <sub>C1</sub> Output from each pin           |                 |          |                |            |            |               |               |

|       |     |     |     |     |     |    |        | 0 0 Vc1: Outputs columns 0 to 23. Vc2: Fixed to low leve       |                 |          |                |            | low level. |               |               |

|       |     |     |     |     |     |    |        | 0 1 Vc1: Outputs columns 0 to 11. Vc2: Outputs columns 12 to 3 |                 |          |                |            |            | mns 12 to 23. |               |

|       |     |     |     |     |     |    |        | 1                                                              | 0               | Vc1: Out | outs colum     | ns 12 to 2 | 23. Vc2: O | utputs col    | umns 0 to 11. |

|       |     |     |     |     |     |    |        | 1                                                              | 1               | Vc1: Fix | ed to low      | level. V   | c2: Outpu  | ıts colum     | ns 0 to 23.   |

#### · Row specification

You can specify whether the Vc1 or Vc2 pin is used to output the character signals for each row (or each 12 columns).

#### · Output pin control

The signals output from the Vc1 and Vc2 pins depend on whether option A, B, or C is selected (the corresponding blanking signals are output in the same way).

#### Option A output

|                 | Output pin control bits |                                                          |     |  |  |  |  |  |

|-----------------|-------------------------|----------------------------------------------------------|-----|--|--|--|--|--|

| V <sub>C2</sub> | V <sub>C1</sub>         | Output from each pin                                     |     |  |  |  |  |  |

| 0               | 0                       | Vc1: Outputs the specified row. Vc2: Fixed to low level. | (1) |  |  |  |  |  |

| 0               | 1                       | Vc1: Fixed to low level. Vc2: Outputs specified row.     | (2) |  |  |  |  |  |

|                       | Output<br>channel       | Character signal                                                                                                                                                                              | Background signal (if specified)                                                                              |

|-----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| For case<br>(1) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the $V_B$ , $V_G$ , and $V_B$ pins (for the specified rows), excluding those characters for which the $V_{C2}$ channel has been specified. | Outputs a background signal for areas other than those for which the Vc2 channel has been specified.          |

|                       | Vc2 channel             | Fixed to low level (for the specified rows)                                                                                                                                                   | Outputs a background signal for those the areas for which the V <sub>C2</sub> channel has been specified.     |

| For case (2) above    | V <sub>C1</sub> channel | Fixed to low level (for the specified rows)                                                                                                                                                   | Outputs a background signal for areas other than those for which the $V_{\rm C2}$ channel has been specified. |

| . ,                   | Vc2 channel             | Outputs those characters for which the Vc2 channel has been specified (for the specified rows).                                                                                               | Outputs a background signal for those the areas for which the V <sub>C2</sub> channel has been specified.     |

#### Option B output

|                 | Output pin control bits |                                                      |     |  |  |  |  |

|-----------------|-------------------------|------------------------------------------------------|-----|--|--|--|--|

| V <sub>C2</sub> | V <sub>C1</sub>         | Output from each pin                                 |     |  |  |  |  |

| 0               | 0                       | Vc1: Outputs all rows. Vc2: Fixed to low level.      | (1) |  |  |  |  |

| 0               | 1                       | Vc1: Outputs all rows. Vc2: Outputs a specified row. | (2) |  |  |  |  |

|                       | Output<br>channel       | Character signal                                                                                                                                                                                                      | Background signal (if specified)                                                                                 |

|-----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| For case<br>(1) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the $V_{\text{R}}$ , $V_{\text{G}}$ , and $V_{\text{B}}$ pins (for all rows), excluding those characters for which the $V_{\text{C2}}$ channel has been specified. | Outputs a background signal for areas other than those for which the V <sub>C2</sub> channel has been specified. |

|                       | Vc2 channel             | Fixed to low level (for the specified rows)                                                                                                                                                                           | Outputs a background signal for those areas for which the $V_{\rm C2}$ channel has been specified.               |

| For case<br>(2) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the $V_{\text{R}}$ , $V_{\text{G}}$ , and $V_{\text{B}}$ pins (for all rows), excluding those characters for which the $V_{\text{C2}}$ channel has been specified. | Outputs a background signal for areas other than those for which the V <sub>C2</sub> channel has been specified. |

|                       | Vc2 channel             | Outputs the characters for which the $V_{\rm C2}$ channel is specified (for the specified rows).                                                                                                                      | Outputs a background signal for those areas for which the Vc2 channel has been specified.                        |

#### Option C output

|                 | Output pin control bits  |                                                              |     |  |  |  |  |  |  |

|-----------------|--------------------------|--------------------------------------------------------------|-----|--|--|--|--|--|--|

| V <sub>C2</sub> | Vc1 Output from each pin |                                                              |     |  |  |  |  |  |  |

| 0               | 0                        | Vc1: Outputs columns 0 to 23. Vc2: Fixed to low level.       | (1) |  |  |  |  |  |  |

| 0               | 1                        | Vc1: Outputs columns 0 to 11. Vc2: Outputs columns 12 to 23. | (2) |  |  |  |  |  |  |

| 1               | 0                        | Vc1: Outputs columns 12 to 23. Vc2: Outputs columns 0 to 11. | (3) |  |  |  |  |  |  |

| 1               | 1                        | Vc1: Fixed to low level. Vc2: Outputs columns 0 to 23.       | (4) |  |  |  |  |  |  |

|                       | Output<br>channel       | Character signal                                                                                                                                                                                                                                   | Background signal (if specified)                                                                                 |

|-----------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| For case<br>(1) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the $V_B$ , $V_G$ , and $V_B$ pins (for columns 0 to 23 in the specified rows), excluding those characters for which the $V_{C2}$ channel has specified.                                        | Outputs a background signal for areas other than those for which the Vc2 channel has been specified.             |

|                       | Vc2 channel             | Fixed to low level (for the specified rows)                                                                                                                                                                                                        | Outputs a background signal for those areas for which the $V_{\rm C2}$ channel has been specified.               |

| For case<br>(2) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the V <sub>R</sub> , V <sub>G</sub> , and V <sub>B</sub> pins (for columns 0 to 11 of the specified rows), excluding those characters for which the V <sub>C2</sub> channel has been specified. | Outputs a background signal for areas other than those for which the Vc2 channel has been specified.             |

|                       | V <sub>C2</sub> channel | Outputs the characters for which the Vc2 channel has been specified (for columns 12 to 23 of the specified rows).                                                                                                                                  | Outputs a background signal for those areas for which the V <sub>C2</sub> channel has been specified.            |

| For case<br>(3) above | V <sub>C1</sub> channel | Outputs the logical OR of the character signals at the $V_B$ , $V_G$ , and $V_B$ pins (for columns 12 to 23 of the specified rows), excluding those characters for which the $V_{C2}$ channel has been specified.                                  | Outputs a background signal for areas other than those for which the V <sub>C2</sub> channel has been specified. |

|                       | Vc2 channel             | Outputs the characters for which the V <sub>C2</sub> channel has been specified (for columns 0 to 11 of the specified rows).                                                                                                                       | Outputs a background signal for those areas for which the V <sub>C2</sub> channel has been specified.            |

| For case<br>(4) above | V <sub>C1</sub> channel | Fixed to low level (for the specified rows)                                                                                                                                                                                                        | Outputs a background signal for areas other than those for which the V <sub>C2</sub> channel has been specified. |

|                       | Vc2 channel             | Outputs the characters for which the V <sub>C2</sub> channel has been specified (for columns 0 to 23 in the specified rows).                                                                                                                       | Outputs a background signal for those areas for which the V <sub>C2</sub> channel has been specified.            |

The RGB and  $V_{C1}$  channels do not output character signals for characters for which the  $V_{C2}$  channel has been specified. Background signals are output separately as listed above.

In addition, the  $\mu$ PD6461, 6462, when set to RGB+Vc<sub>1</sub>+Vc<sub>2</sub> mode, provide the following output control:

- Independent on/off control of character display for each channel (3-channel independent display on/off command)

- Independent control of the background for each channel (3-channel independent background control command)

#### 1.4.1 Character Signal Output When Option A is Selected

#### Option A

The  $Vc_1$  bit of the output pin control command can be used to specify whether the characters of each row are output to the  $Vc_1$  channel. Each character can be specified to be output to the  $Vc_2$  channel, and the  $Vc_1$  channel outputs only characters for which the  $Vc_2$  channel in the rows for which the  $Vc_1$  bit is set to 1. Characters for which the  $Vc_2$  channel is specified are not output to the RGB or  $Vc_1$  channel.

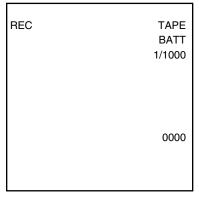

Display example (when the Vc2 channel is used for information to be recorded)

Display in viewfinder (RGB output and Vc2 output)

#### Output example with mask code option A specified

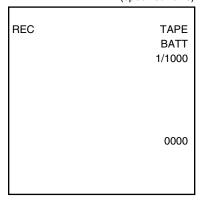

Characters output via RGB channel (colored characters)

|     | (colored orial actors) |

|-----|------------------------|

| REC | TAPE<br>BATT<br>1/1000 |

|     | 0000                   |

| I   |                        |

The RGB channel does not output the characters for which the V<sub>C2</sub> channel has been specified. Characters output via Vc1 channel (specified rows)

- The Vc1 channel outputs the characters in the rows for which the Vc1 bit is set to 0, excluding the characters for which the Vc2 channel is specified.

- Rows for which the V<sub>C1</sub> bit is set to 1 are not output (the V<sub>C1</sub> pin is fixed to low level).

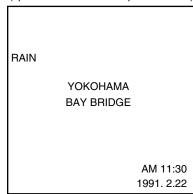

Characters output via  $V_{\text{C2}}$  channel (specified characters of specified rows)

| _ | OKOHAMA<br>Y BRIDGE |                        |

|---|---------------------|------------------------|

|   |                     | AM 11:30<br>1991. 2.22 |

- Rows for which the V<sub>C1</sub> bit is set to 0 are not output (the V<sub>C2</sub> pin is fixed to low level).

- The V<sub>C2</sub> channel outputs only those characters for which the V<sub>C2</sub> channel has been specified in the rows for which the V<sub>C1</sub> bit is set to 1.

#### 1.4.2 Character Signal Output When Option B is Selected

#### Option B

The Vc1 channel outputs characters of all rows regardless of setting of the Vc1 and Vc2 bits. Each character can be specified to be output to the Vc2 channel, and the Vc2 channel outputs only characters for which the Vc2 channel in the rows for which the Vc1 bit is set to 1. Characters for which the Vc2 channel is specified are not output to the RGB or Vc1 channel.

Display example (when the Vc2 channel is used for information to be recorded)

### Display in viewfinder (RGB output and Vc2 output)

#### Output example with mask code option B specified

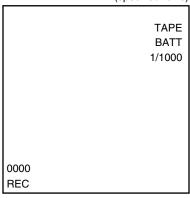

Characters output via RGB channel (colored characters)

| REC | TAPE<br>BATT<br>1/1000 |

|-----|------------------------|

|     | 0000                   |

The RGB channel does not output the characters for which the V<sub>C2</sub> channel has been specified. Characters output via Vc1 channel (all rows)

The Vc1 channel outputs the characters of all rows regardless of the setting of the Vc1 bit, excluding the characters for which the Vc2 channel is specified. Characters output via V<sub>C2</sub> channel (specified characters of specified rows)

- The Vc2 channel outputs only those characters for which the Vc2 channel has been specified in those rows for which the Vc1 bit has been set to 1.

- The Vc2 channel outputs no characters in those rows for which the Vc1 bit has been set to 0.

#### 1.4.3 Character Signal Output When Option C is Selected

#### Option C

The V<sub>C1</sub> and V<sub>C2</sub> bits of the output pin control command can be used to specify whether the characters in columns 0 to 11 of each row and those in columns 12 to 23 are output to the V<sub>C1</sub> channel or to the V<sub>C2</sub> channel.

#### Display example

#### Display in viewfinder

#### Output example with mask code option C specified

Characters output via RGB channel (colored characters)

TAPE BATT 1/1000

The RGB channel does not output the characters for which the V<sub>C2</sub> channel has been specified. Characters output via Vc1 channel (specified rows)

- In the case of setting V<sub>C2</sub> bit to 0, the V<sub>C1</sub> channel outputs the characters of columns 0 to 23 in specified rows for which the V<sub>C1</sub> bit is set to 0, or the characters of columns 0 to 11 in specified rows for which the V<sub>C1</sub> bit is set to 1, excluding the characters for which the V<sub>C2</sub> channel specified.

- In the case of setting V<sub>C2</sub> bit to 1, the V<sub>C1</sub> channel outputs the characters of columns 12 to 23 in specified rows for which the V<sub>C1</sub> bit is set to 0, and the rows for which the V<sub>C1</sub> bit is set to 1 are not output (the V<sub>C1</sub> pin is fixed to low level), excluding the characters for which the V<sub>C2</sub> channel specified.

Characters output via Vc2 channel (specified characters)

YOKOHAMA BAY BRIDGE AM 11:30 1991. 2.22

- In the case of setting Vc1 bit to 0, the Vc2 channel outputs the characters of columns 0 to 11 in specified rows for which the Vc2 bit is set to 1, and the rows for which the Vc2 bit is set to 0 are not output (the Vc2 pin is fixed to low level).

- In the case of setting Vc1 bit to 1, the Vc2 channel outputs the characters of columns 12 to 23 in specified rows for which the Vc2 bit is set to 0, or the characters of columns 0 to 23 in specified rows for which the Vc2 bit is set to 1.

16

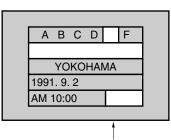

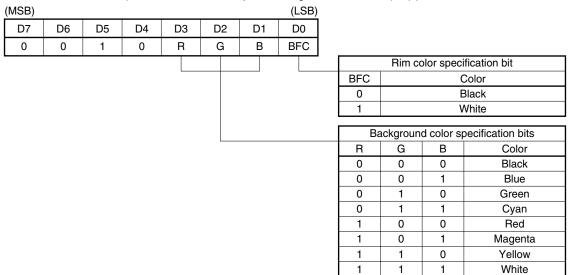

#### 1.4.4 Display of Vc2-Specified Characters

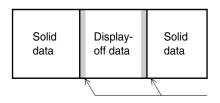

When the displayed character control command specifies the  $V_{C2}$  channel for a character, that character is not output to the RGB or  $V_{C1}$  channel (display for the RGB and  $V_{C1}$  channels is usually the same as when display-off data is written Note). If background display (overall/minimum) is specified for the RGB or  $V_{C1}$  channel, no background is displayed for those characters for which the  $V_{C2}$  channel has been specified.

Note In some cases, the display will differ slightly from the display-off data.

Solid data: Character for which all  $12 \times 18$  dots are filled

- When display-off data is displayed for the RGB, Vc1, or Vc2 channel

If a character adjacent to the display-off data is rimmed or has a

background, the rim or background encroaches into the area for the display off data by one dot (minimum size). (The rim encroaches only at the filled

dots at the left or right edge of the rimmed character.)

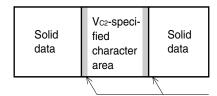

- Display of Vc2-specified character area for the RGB or Vc1 channel

If a character adjacent to a Vc2-specified character is rimmed, the rim

encroaches into the area for the Vc2-specified character by one dot (minimum size). If the adjacent character has a background, however, the

background does not encroach into the Vc2-specified character area.

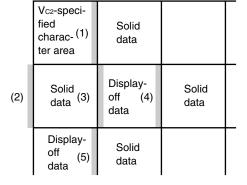

- Display of Vc2-specified character area for the Vc2 channel

If a rimmed Vc2-specified character is adjacent to another Vc2-specified character, the rim encroaches into the area for the latter Vc2-specified character. The background does not encroach into the adjacent area (The rim encroaches only at the filled dots on the left or right edge of the rimmed character).

- When a Vc2-specified character area exists at the right or left edge of the entire display area

(The figure shows an area at the left edge. The case of an area at the right edge is similar).

Encroachment of rim or background (with a width of one dot for the minimum character size)

| Encroachment of rim | Encroachment of background |

|---------------------|----------------------------|

| (1) – (5)           | (2) – (5)                  |

Background does not encroach into the Vc2-specified character area.

#### 1.5 OUTPUTTING BACKGROUND

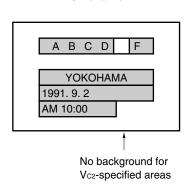

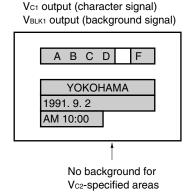

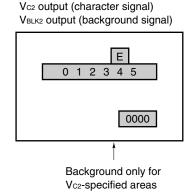

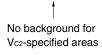

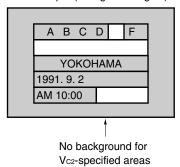

The figures below show the screen display when minimum background or overall background is specified for each output channel in RGB+Vc1+Vc2 mode.

#### (1) Minimum background

RGB channel

#### (2) Overall background

RGB channel

Vc1 output (character signal)

VBLK1 output (background signal)

V<sub>C2</sub> output (character signal) V<sub>BLK2</sub> output (background signal)

Vc2-specified areas

- **Remarks 1.** The above figures are only examples. Actually, the background can be controlled independently for each output channel (only in RGB+Vc1+Vc2 mode), for example, by applying background (overall/minimum) for the RGB channel but not for the other channels.

- 2. No background is applied to the Vc2-specified areas for the RGB or Vc1 channel. If a character adjacent to a Vc2-specified character is rimmed, the rim encroaches into the area for the Vc2-specified character by one dot (minimum size) only at the filled dots at the left or right edge of the area of the rimmed character, in the same way as for display-off data. The background, however, does not encroach into the adjacent area.

#### 2. COMMANDS

#### 2.1 COMMAND FORMAT

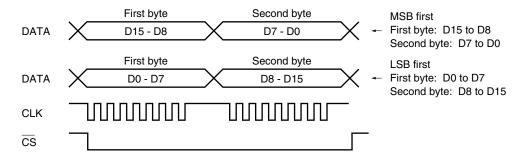

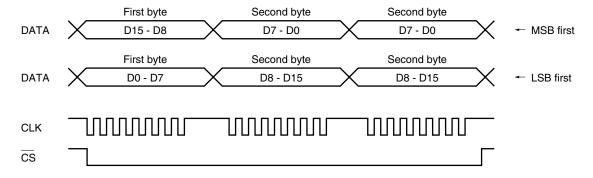

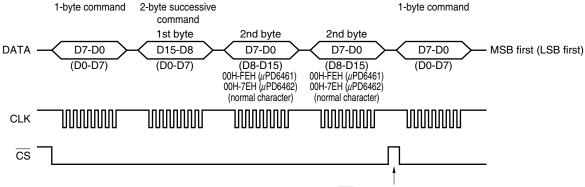

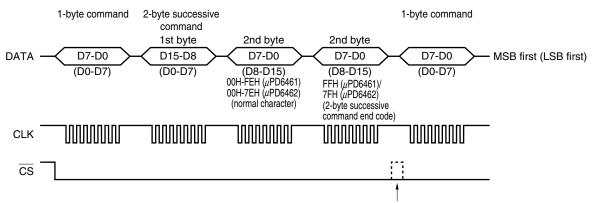

Control commands are serially input in 8-bit units with a variable word length. There are three types of commands: 1-byte commands consisting of eight bits including an instruction and data, 2-byte commands consisting of sixteen bits including an instruction and data, and a 2-byte continuous command which can be input in an abbreviated format. Commands are input with the MSB first or LSB first according to the specified mask option.

#### 2.2 COMMANDS AND THEIR BITS

#### (1) For MSB first

#### 1-byte commands

(MSB)

| Function                             | D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0   |

|--------------------------------------|----|----|----|----|----|-----|-----|------|

| Video RAM batch clear                | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    |

| Character display control            | 0  | 0  | 0  | 1  | D0 | LC  | BL1 | BL0  |

| Background/rim color control         | 0  | 0  | 1  | 0  | R  | G   | В   | BFC  |

| 3-channel independent display on/off | 0  | 1  | 1  | 1  | 0  | DOA | DOB | DOC  |

| Character reverse on/off             | 0  | 0  | 1  | 1  | 1  | 0   | 0   | BCRE |

#### 2-byte commands

(MSB)

|                                          | - |     |     |     |     |     |    |     |                 |                 |     |     |     |     |     |     |

|------------------------------------------|---|-----|-----|-----|-----|-----|----|-----|-----------------|-----------------|-----|-----|-----|-----|-----|-----|

| Function                                 |   | D14 | D13 | D12 | D11 | D10 | D9 | D8  | D7              | D6              | D5  | D4  | D3  | D2  | D1  | D0  |

| Character display position control       |   | 0   | 0   | 0   | 0   | 0   | V4 | V3  | V2              | V1              | V0  | H4  | НЗ  | H2  | H1  | H0  |

| Write address control                    |   | 0   | 0   | 0   | 1   | 0   | 0  | AR3 | AR2             | AR1             | AR0 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Output pin control                       | 1 | 0   | 0   | 1   | 1   | 1   | 0  | 0   | V <sub>C2</sub> | V <sub>C1</sub> | 0   | 0   | AR3 | AR2 | AR1 | AR0 |

| Character size control                   | 1 | 0   | 0   | 1   | 1   | 0   | 0  | 0   | 0               | S               | 0   | 0   | AR3 | AR2 | AR1 | AR0 |

| 3-channel independent background control | 1 | 0   | 1   | 1   | 0   | 0   | 1  | BA1 | BA0             | BFA             | BB1 | BB0 | BFB | BC1 | BC0 | BFC |

| Test mode <sup>Note</sup>                | 1 | 0   | 1   | 1   | 0   | 0   | 0  | T8  | T7              | T6              | T5  | T4  | Т3  | T2  | T1  | T0  |

Note Not to be used

#### 2-byte continuous command

(MSB)

| Function                    | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8              | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------------------------|-----|-----|-----|-----|-----|-----|----|-----------------|----|----|----|----|----|----|----|----|

| Displayed character control | 1   | 1   | RV  | R   | G   | В   | BL | V <sub>C2</sub> | C7 | C6 | C5 | C4 | С3 | C2 | C1 | C0 |

Not

**Note** C7 bit is "don't care" at the  $\mu$ PD6462. However, this data sheet explains the  $\mu$ PD6462 with "0" in the C7 bit.

#### (2) For LSB first

#### 1-byte commands

(LSB)

| Function                             | D0   | D1  | D2  | D3 | D4 | D5 | D6 | D7 |

|--------------------------------------|------|-----|-----|----|----|----|----|----|

| Video RAM batch clear                | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  |

| Character display control            | BL0  | BL1 | LC  | DO | 1  | 0  | 0  | 0  |

| Background/rim color control         | BFC  | В   | G   | R  | 0  | 1  | 0  | 0  |

| 3-channel independent display on/off | DOC  | DOB | DOA | 0  | 1  | 1  | 1  | 0  |

| Character reverse on/off             | BCRE | 0   | 0   | 1  | 1  | 1  | 0  | 0  |

#### 2-byte commands

(LSB)

| Function                                 | D0  | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8  | D9  | D10 | D11 | D12 | D13 | D14             | D15             |

|------------------------------------------|-----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----------------|-----------------|

| Character display position control       |     | V4 | 0  | 0  | 0  | 0  | 0  | 1  | H0  | H1  | H2  | НЗ  | H4  | V0  | V1              | V2              |

| Write address control                    | AR3 | 0  | 0  | 1  | 0  | 0  | 0  | 1  | AC0 | AC1 | AC2 | АС3 | AR4 | AR0 | AR1             | AR2             |

| Output pin control                       | 0   | 0  | 1  | 1  | 1  | 0  | 0  | 1  | AR0 | AR1 | AR2 | AR3 | 0   | 0   | V <sub>C1</sub> | V <sub>C2</sub> |

| Character size control                   | 0   | 0  | 0  | 1  | 1  | 0  | 0  | 1  | AR0 | AR1 | AR2 | AR3 | 0   | 0   | S               | 0               |

| 3-channel independent background control | BA1 | 1  | 0  | 0  | 1  | 1  | 0  | 1  | BFC | BC0 | BC1 | BFB | BB0 | BB1 | BFA             | BA0             |

| Test mode <sup>Note</sup>                | T8  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | T0  | T1  | T2  | Т3  | T4  | T5  | T6              | T7              |

Note Not to be used

#### 2-byte continuous command

(LSB)

| Function                    | D0              | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 |

|-----------------------------|-----------------|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|

| Displayed character control | V <sub>C2</sub> | BL | В  | G  | R  | RV | 1  | 1  | C0 | C1 | C2  | СЗ  | C4  | C5  | C6  | C7  |

Note

**Note** C7 bit is "don't care" at the  $\mu$ PD6462. However, this data sheet explains the  $\mu$ PD6462 with "0" in the C7 bit.

#### 2.3 POWER-ON CLEAR FUNCTION

The internal state of the IC is unstable immediately after the power is turned on. It is therefore necessary to keep the PCL pin low for the time shown below to allow the system to initialize. This power-on clear places the system in the following state:

- · Test mode is not specified.

- All character data in video RAM (12 rows × 24 columns) is cleared (to display-off data (FEH: μPD6461/7EH: μPD6462)) and blinking is turned off.

- The video RAM write address is (row 0, column 0).

- The character size is single (minimum) for all rows.

- The output distribution format is set to the default (the Vc1 and Vc2 bits are set to 0).

- · Display is turned off and LC oscillation is turned on.

The time required for power-on clear is calculated as follows. No commands must be input during this time.

```

Time required for power-on clear = t_{PCLL}Note + {Time required for clearing video RAM}

= 10(\mu s) + \{10(\mu s) + 12/f_{osc}(MHz) \times 288\}

```

fosc(MHz): LC oscillation frequency or external clock frequency

Note Refer to POWER-ON CLEAR SPECIFICATIONS in 6. ELECTRICAL CHARACTERISTICS.

A dot clock input (to the OSC<sub>IN</sub> pin) is necessary to clear video RAM. Input a dot clock when an external clock input is selected.

#### 3. COMMAND DETAILS

#### 3.1 VIDEO RAM BATCH CLEAR COMMAND

This command clears the entire video RAM by means of a single operation (the bit configuration is the same as for MSB-first and LSB-first transfer).

(MSB) (LSB) D7 D6 D5 D2 D1 D0 D4 D3 0 0 0 0 0 0

The video RAM batch clear command places the system in the following state:

- All character data in video RAM (12 rows  $\times$  24 columns) is cleared (to display-off data (FEH:  $\mu$ PD6461/7EH:  $\mu$ PD6462)) and blinking is turned off.

- The video RAM write address is (row 0, column 0).

- The character size is single (minimum) for all rows.

- The output distribution format is set to the default (the Vc1 and Vc2 bits are set to 0).

- · Display is turned off and LC oscillation is turned on.

The time required for clearing video RAM is calculated as follows. No command must be input while the video RAM is being cleared.

Time required to clear video RAM =  $10(\mu s) + 12/fosc(MHz) \times 288$ fosc(MHz) : LC oscillation frequency or external clock frequency

A dot clock input (to the OSC<sub>IN</sub> pin) is necessary to clear the video RAM. Input a dot clock when external clock input is selected.

**Remark** Power-on clear using the PCL pin is hardware reset, initializing the IC, including clearing the video RAM and releasing test mode. The video RAM batch clear command, in contrast, performs software reset by initializing the IC without first releasing test mode.

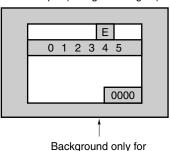

#### 3.2 CHARACTER DISPLAY CONTROL COMMAND

This command turns on/off character display, LC oscillation, and the blinking of characters.

(1) For MSB-first transfer (Command bits are input starting from the MSB (D7).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

| (LSB) |     |    |    |    |    |    | (MSB) |

|-------|-----|----|----|----|----|----|-------|

| D0    | D1  | D2 | D3 | D4 | D5 | D6 | D7    |

| BL0   | BL1 | LC | DO | 1  | 0  | 0  | 0     |

· Blinking control bits

These bits are used to turn on or off the blinking of characters for which blinking has been enabled with the displayed character control command. The blinking ratio is 1:1, one of three blinking frequencies being selectable for the entire screen.

· LC oscillation control bit

This bit is used to turn the oscillator on or off. You can stop the oscillator when no character is being displayed, thus reducing the power consumption.

While the oscillator is stopped, it is not possible to write to video RAM. Turn on the oscillator before attempting to write to video RAM.

- Cautions 1. When using LC oscillation (LC oscillation control bit = 1): When character display is turned on, the oscillation is synchronized with Hsync, stopping when Hsync goes low. When character display is turned off, oscillation continues regardless of the state of Hsync.

- When using an external clock (LC oscillation control bit = 1): While the oscillator is turned on, clock pulses are supplied to the IC internal circuit. While the oscillator is turned off, no clock pulses are supplied.

- · Character display on/off control bit

This bit is used to turn character display on or off. Character display is turned on or off upon the detection of a falling edge of Hsync.

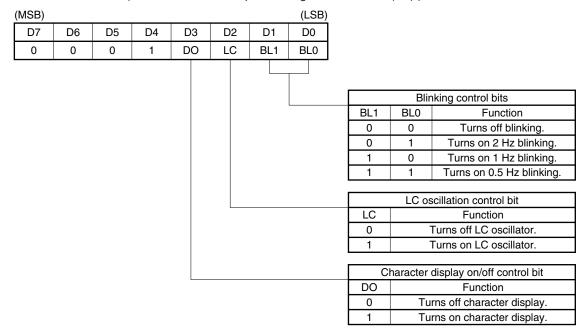

#### 3.3 BACKGROUND/RIM COLOR CONTROL COMMAND

This command specifies the color of the background or rim when overall background, minimum background, or rimming is specified.

(1) For MSB-first transfer (Command bits are input starting from the MSB (D7).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

| (LSB) |    |    |    |    |    |    | (MSB) |

|-------|----|----|----|----|----|----|-------|

| D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7    |

| BFC   | В  | G  | R  | 0  | 1  | 0  | 0     |

· Rim color specification bit

This bit is used to specify the color (white or black) of the rim added to all characters displayed on the screen (only for the RGB channel). When rimming is specified for the Vc1 or Vc2 channel, the rim color is always black.

· Background color specification bits

These bits are used to specify one of eight colors to be used for the background of the entire screen (only for the RGB channel). When background (overall/minimum) is specified for the Vc1 or Vc2 channel, the background color is always black.

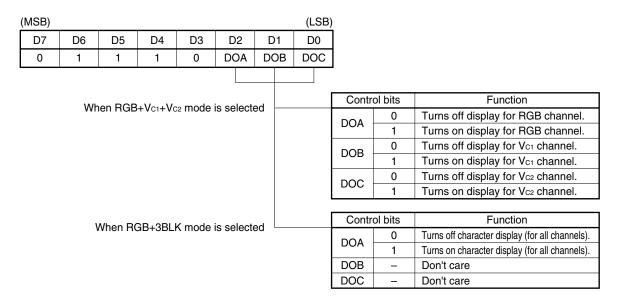

#### 3.4 3-CHANNEL INDEPENDENT DISPLAY ON/OFF COMMAND

This command turns character display on or off independently for each of the three channels.

(1) For MSB-first transfer (Command bits are input starting from the MSB (D7).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

| (LSB) |     |     |    |    |    |    | (MSB) |

|-------|-----|-----|----|----|----|----|-------|

| D0    | D1  | D2  | D3 | D4 | D5 | D6 | D7    |

| DOC   | DOB | DOA | 0  | 1  | 1  | 1  | 0     |

#### 3.5 CHARACTER REVERSE ON/OFF COMMAND

This command specifies whether all characters displayed on the screen are reversed.

(1) For MSB-first transfer (Command bits are input starting from the MSB (D7).)

| (MSB) |    |    |    |    |    |    | (LSB) |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

| 0     | 0  | 1  | 1  | 1  | 0  | 0  | BCRE  |

|       |    |    |    |    |    |    |       |

| Cont | rol bit | Function                     |

|------|---------|------------------------------|

| DCDE | 0       | Does not reverse characters. |

| BUNE | 1       | Reverses characters.         |

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

| (LSB) |    |    |    |    |    |    | (MSB) |

|-------|----|----|----|----|----|----|-------|

| D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7    |

| BCRE  | 0  | 0  | 1  | 1  | 1  | 0  | 0     |

Each character is reversed only when reversing of the character is enabled with the displayed character control command.

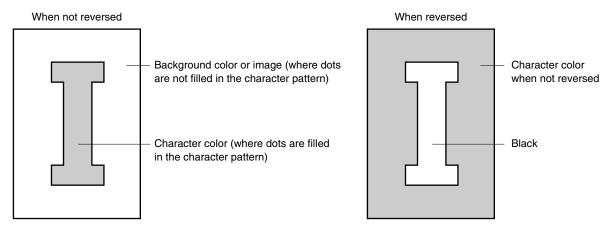

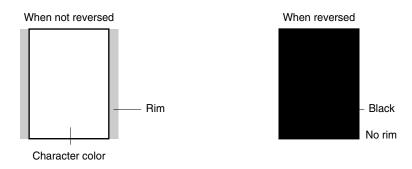

• Example of reversed character (uppercase letter "I")

**Remark** When the character is not reversed, one of eight colors can be selected for the background color for the RGB channel. For the Vc1 and Vc2 channels, which can display only white or black, the background is always black (characters are white).

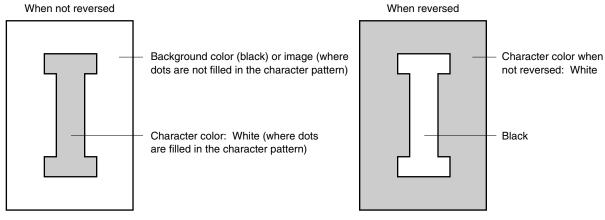

When characters are rseversed for the Vc1 or Vc2 channel, the display is as follows:

• Example of reversed character for Vc1 or Vc2 channel (uppercase letter "I")

26

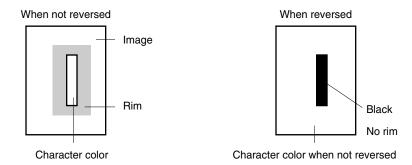

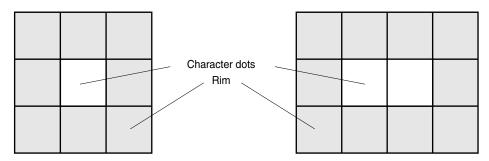

• Rimming of reversed character For an ordinary character

#### For a solid character (character pattern 18H ( $\mu$ PD6461)/1FH ( $\mu$ PD6462): Refer to 5. CHARACTER PATTERNS)

Display-off data does not change when reversed. When blank data is reversed, it becomes a solid character for which the character color is initially set. The character color can be set only for the RGB channel. It is always white (black when reversed) for the  $V_{C1}$  and  $V_{C2}$  channels.

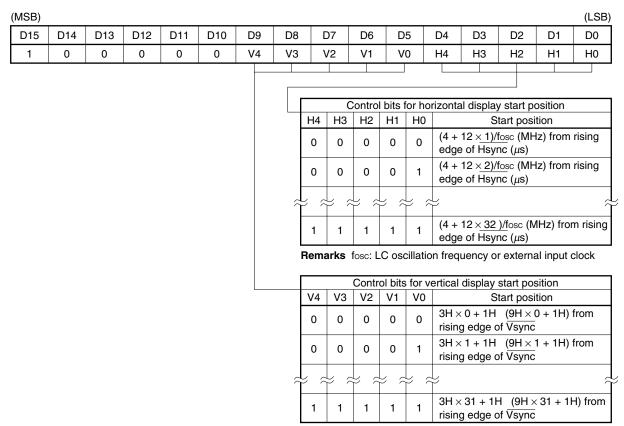

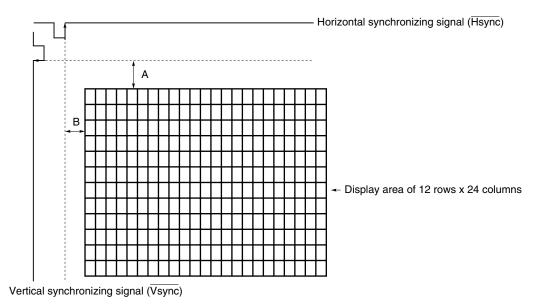

#### 3.6 CHARACTER DISPLAY POSITION CONTROL COMMAND

This command specifies the character display start position with one of 32 steps in 12-dot units for the horizontal direction, and one of 32 steps in three-line units for the vertical direction (this command is a 2-byte command, requiring 16 bits for each command even when continuously input).

(1) For MSB-first transfer (Command bits are input starting from the MSB (D15).)

Remarks 1. H: Line

- **2.** ( ) shows when units of nine lines are selected by specifying a mask option.

- (2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

| (LSB) |    |    |    |    |    |    |    |    |    |     |     |     |     |     | (MSB) |

|-------|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-------|

| D0    | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15   |

| V3    | V4 | 0  | 0  | 0  | 0  | 0  | 1  | H0 | H1 | H2  | НЗ  | H4  | VO  | V1  | V2    |

· Control bits for the horizontal display start position

These bits are used to specify the horizontal display start position (timing) as one of 32 steps in units of 12 dots (12/fosc (MHz)). Settable positions are based on the rising edge of the horizontal synchronizing signal input to the Hsync pin. The 32 positions are calculated by adding 12 dots, one to 32 times, to the position equivalent to 16 clock pulses (16/fosc (MHz)) from the rising edge (fosc (MHz): LC oscillation frequency or external input clock frequency).

· Control bits for the vertical display start position

These bits are used to specify the vertical display start position as one of 32 steps in units of three lines (or 32 steps in units of nine lines when specified with a mask option). The minimum settable position is three lines from a rising edge of the vertical synchronizing signal input to the Vsync pin.

A:  $3H \times (2^4V4 + 2^3V3 + 2^2V2 + 2^1V1 + 2^0V0) + 1H$

—— 9H when units of nine lines are selected by specifying a mask option

$$\mathsf{B}: \frac{12}{\mathsf{fosc}(\mathsf{MHz})} \times (2^4\mathsf{H4} + 2^3\mathsf{H3} + 2^2\mathsf{H2} + 2^1\mathsf{H1} + 2^0\mathsf{H0} + 1) + \frac{4}{\mathsf{fosc}(\mathsf{MHz})}$$

fosc: LC oscillation frequency or external input clock frequency H: Line

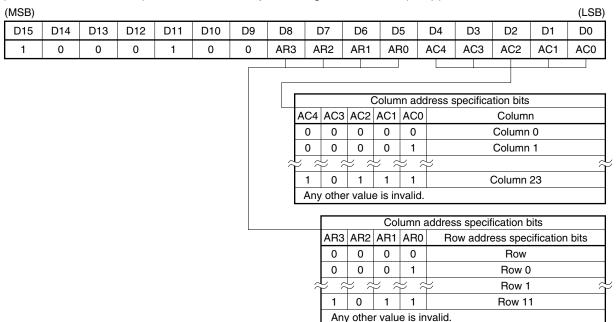

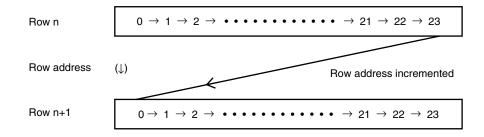

#### 3.7 WRITE ADDRESS CONTROL COMMAND

This command specifies the address at which a character is written in the display area (video RAM) of 12 rows × 24 columns (this command is a 2-byte command, requiring 16 bits for each command, even when continuously input).

(1) For MSB-first transfer (Command bits are input starting from the MSB (D15).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

(LSB) (MSB) D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 AR3 1 1 AC0 AC1 AC2 AC3 AR4 AR0 AR1 AR2

Column write address specification bits

The display area has 24 columns. These bits are used to specify the column in which a character is to be written.

· Row write address specification bits

The display area has 12 rows. These bits are used to specify the row in which a character is to be written.

#### 3.8 OUTPUT PIN CONTROL COMMAND

This command distributes character signals to the  $Vc_1$  and  $Vc_2$  channels (this command is a 2-byte command, requiring 16 bits for each command, even when continuously input). The  $\mu$ PD6461, 6462 support a mask option for selecting one of three formats for the output distribution format for the  $Vc_1$  and  $Vc_2$  channels.

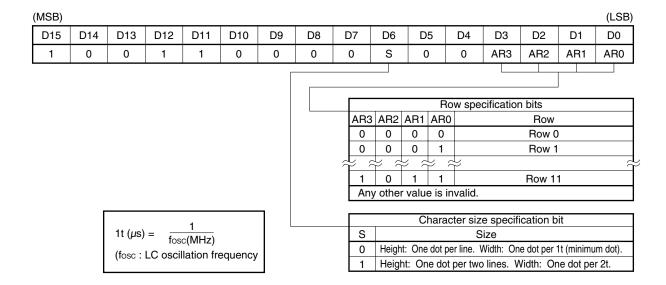

(1) For MSB-first transfer (Command bits are input starting from the MSB (D15).)

| (MSB) |     |     |     |     |     |    |         |                            |                 |          |            |              |           |           | (LSB)        |  |  |

|-------|-----|-----|-----|-----|-----|----|---------|----------------------------|-----------------|----------|------------|--------------|-----------|-----------|--------------|--|--|

| D15   | D14 | D13 | D12 | D11 | D10 | D9 | D8      | D7                         | D6              | D5       | D4         | D3           | D2        | D1        | D0           |  |  |

| 1     | 0   | 0   | 1   | 1   | 1   | 0  | 0       | V <sub>C2</sub>            | V <sub>C1</sub> | 0        | 0          | AR3          | AR2       | AR1       | AR0          |  |  |

|       |     |     |     |     |     |    |         |                            |                 |          |            |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         |                            |                 |          |            |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         |                            |                 |          | Row spe    | cificatio    | n bits    |           |              |  |  |

|       |     |     |     |     |     |    |         | AR3                        | AR2             | AR1      | AR0        |              | Fu        | ınction   |              |  |  |

|       |     |     |     |     |     |    |         | 0                          | 0               | 0        | 0          |              | Specif    | fies row  | 0.           |  |  |

|       |     |     |     |     |     |    |         | 0                          | 0               | 0        | 1          |              | Speci     | fies row  | 1.           |  |  |

|       |     |     |     |     |     |    | ล์      | \<br>\<br>\                | ۶ <u> </u>      | = =      | 2          | <del>\</del> | _         |           |              |  |  |

|       |     |     |     |     |     |    |         | 1                          | 0               | 1        | 1          |              | Specifi   | es row    | 11.          |  |  |

|       |     |     |     |     |     |    |         | Other values are invalid.  |                 |          |            |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         | A Quitaut ain control hite |                 |          |            |              |           |           |              |  |  |

|       |     |     |     |     |     | 0  | ption A | <u> </u>                   |                 |          |            |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         | V <sub>C2</sub>            | V <sub>C1</sub> |          |            |              |           | Fire de   |              |  |  |

|       |     |     |     |     |     |    |         | 0                          | 0               |          | •          |              |           |           | o low leve   |  |  |

|       |     |     |     |     |     |    |         | U                          | ı               | VC1: FI  | ked to lov | v ievei.     | VC2: Out  | puis a sp | ecified rov  |  |  |

|       |     |     |     |     |     | О  | ption B |                            |                 |          | Output p   | in contro    | ol bits   |           |              |  |  |

|       |     |     |     |     |     |    |         | V <sub>C2</sub>            | V <sub>C1</sub> |          | Output f   |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         | 0                          | 0               | Vc1: OI  | utputs all | rows. V      | c2: Fixed | to low l  | evel.        |  |  |

|       |     |     |     |     |     |    |         | 0                          | 1               | Vc1: O   | utputs all | rows. V      | c2: Outp  | uts a spe | ecified row  |  |  |

|       |     |     |     |     |     |    |         |                            |                 |          | •          |              | ·         | •         |              |  |  |

|       |     |     |     |     |     | 0  | ption C |                            |                 |          | Output p   |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         | V <sub>C2</sub>            | V <sub>C1</sub> |          | Output f   |              |           |           |              |  |  |

|       |     |     |     |     |     |    |         | 0                          | 0               |          | •          |              |           |           | low level.   |  |  |

|       |     |     |     |     |     |    |         | 0                          | 1               |          | <u> </u>   |              |           | <u> </u>  | mns 12 to 23 |  |  |

|       |     |     |     |     |     |    |         | 1                          | 0               |          |            |              |           |           | umns 0 to 1  |  |  |

|       |     |     |     |     |     |    |         | 1                          | 1               | Vc1: Fix | ed to low  | level. V     | c2: Outpu | ıts colum | ns 0 to 23.  |  |  |

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

(LSB) (MSB) D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 0 0 0 1 AR0 AR1 AR2 AR3 0  $V_{C1}$  $V_{\text{C2}}$

· Row specification bits

Output distribution to the  $V_{C1}$  and  $V_{C2}$  pins is specified for each row (or for 12 columns). These bits are used to specify the row.

· Output pin control bits

These bits are used to distribute character output signals to the Vc1 and Vc2 pins depending on whether option A, B, or C has been selected by specifying a mask option (the corresponding blanking signals are output likewise).

#### 3.9 CHARACTER SIZE CONTROL COMMAND

This command specifies the character size (height and width at one time) for each row (this command is a 2-byte command, requiring 16 bits for each command, even when continuously input).

(1) For MSB-first transfer (Command bits are input starting from the MSB (D15).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)

(LSB) (MSB) D7 D0 D1 D10 D12 D13 D14 D15 D2 D3 D4 D5 D6 D8 D9 D11 0 0 0 1 1 0 0 1 AR0 AR1 AR2 AR3 0 0 S 0

- · Row specification bits

- The character size is specified for each row. These bits are used to specify the row.

- · Character size specification bit

- This bit is used to select either of two supported sizes.

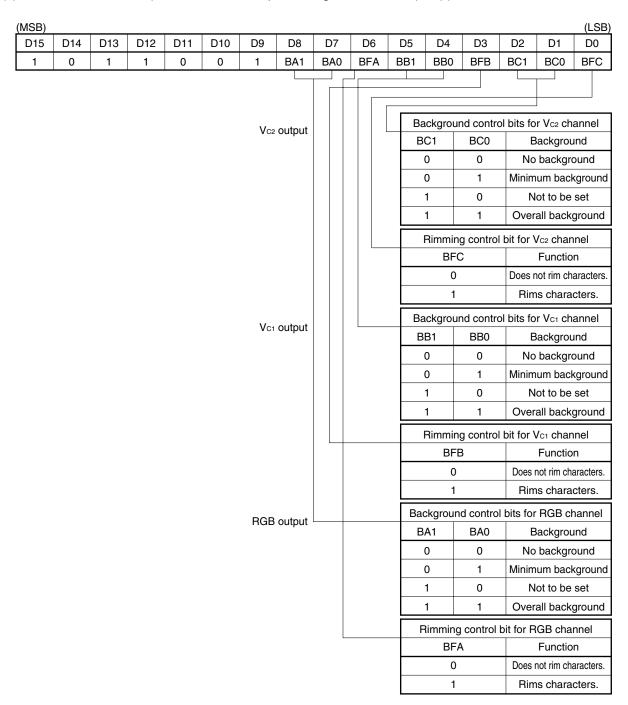

#### 3.10 3-CHANNEL INDEPENDENT BACKGROUND CONTROL COMMAND

This command specifies the background for each of the three output channels (this command is a 2-byte command, requiring 16 bits for each command, even when continuously input).

(1) For MSB-first transfer (Command bits are input starting from the MSB (D15).)

(2) For LSB-first transfer (Command bits are input starting from the LSB (D0). The function of each bit is the same as that for MSB-first transfer.)