## DS96F172MQML/ DS96F174MQML

#### EIA-485/EIA-422 Quad Differential Drivers

#### **General Description**

The DS96F172 and the DS96F174 are high speed quad differential line drivers designed to meet EIA-485 Standards. The DS96F172 and the DS96F174 offer improved performance due to the use of L-FAST bipolar technology. The use of LFAST technology allows the DS96F172 and DS96F174 to operate at higher speeds while minimizing power consumption.

The DS96F172 and the DS96F174 have TRI-STATE® outputs and are optimized for balanced multipoint data bus transmission at rates up to 15 Mbps. The drivers have wide positive and negative common mode range for multipoint applications in noisy environments. Positive and negative current-limiting is provided which protects the drivers from line fault conditions over a +12V to -7.0V common mode range. A thermal shutdown feature is also provided. The DS96F172 features an active high and active low Enable, common to all four drivers. The DS96F174 features separate active high Enables for each driver pair.

#### **Features**

- Meets EIA-485 and EIA-422 standards

- Monotonic differential output switching

- TRI-STATE outputs

- Designed for multipoint bus transmission

- Common mode output voltage range: -7.0V to +12V

- Operates from single +5.0V supply

- Reduced power consumption

- Thermal shutdown protection

- DS96F172 and DS96F174 are lead and function compatible with the SN75172/174 or the AM26LS31/ MC3487

#### **Ordering Information**

| NS Part Number  | SMD Part Number | NS Package Number | Package Description        |

|-----------------|-----------------|-------------------|----------------------------|

| DS96F172ME/883  | 5962-9076501M2A | E20A              | 20LD Leadless Chip Carrier |

| DS96F172MJ/883  | 5962-9076501MEA | J16A              | 16LD Ceramic Dip           |

| DS96F174ME/883  | 5962-9076502M2A | E20A              | 20LD Leadless Chip Carrier |

| DS96F174MJ/883  | 5962-9076502MEA | J16A              | 16LD Ceramic Dip           |

| DS96F174MJ-QMLV | 5962-9076502VEA | J16A              | 16LD Ceramic Dip           |

TRI-STATE® is a registered trademark of National Semiconductor Corporation

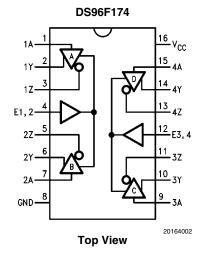

### **Connection Diagrams**

16-Lead Ceramic Dual-In-Line Package (NS Package Number J16A)

# DS96F172 1A 1 16 VCC 11Y 2 15 4A 12 4 13 4Z 2Z 5 12 Ē 2Y 6 11 3Z 2A 7 10 3Y GND 8 9 3A Top View

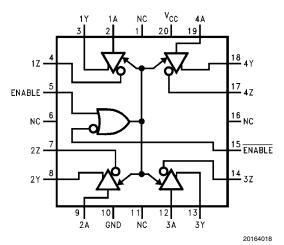

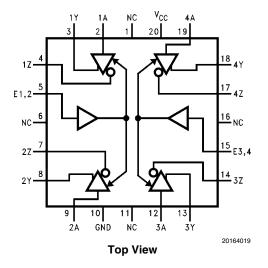

20-Lead Ceramic Leadless Chip Carrier (NS Package Number E20A)

NC = No connection

**Top View**

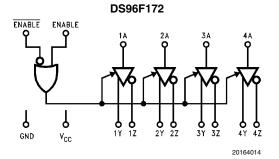

# **Logic Diagrams**

# DS96F174 20164015

#### **Function Tables**

#### DS96F172

#### (Each Driver)

| Input | Enable |   | Outp | uts |

|-------|--------|---|------|-----|

| Α     | E      | Ē | Y    | Z   |

| Н     | Н      | Х | Н    | L   |

| L     | Н      | Х | L    | Н   |

| Н     | Х      | L | Н    | L   |

| L     | Х      | L | L    | Н   |

| Х     | L      | Н | Z    | Z   |

#### DS96F174

| Input | Enable | Outputs |   |  |

|-------|--------|---------|---|--|

| Α     | E      | Y       | Z |  |

| Н     | Н      | Н       | L |  |

| L     | Н      | L       | Н |  |

| Х     | L      | Z       | Z |  |

H = High Level L = Low Level X = Don't Care Z = High Impedance (Off)

#### **Absolute Maximum Ratings** (Note 1)

Storage Temperature Range ( $T_{Stg}$ )  $-65^{\circ}C \le T_{A} \le +175^{\circ}C$ Lead Temperature (Soldering, 60 sec.) 300°C

Maximum Package Power Dissipation at 25°C (Note 2)

Ceramic LCC (E)

2,000 mW

Ceramic DIP (J)

1,800 mW

Ceramic Flatpak (W)

1,000 mW

Supply Voltage

7.0V

Enable Input Voltage

5.5V

#### **Recommended Operating Conditions**

|                                               | Min  | Max   | Units |

|-----------------------------------------------|------|-------|-------|

| Supply Voltage (V <sub>CC</sub> )             | 4.50 | 5.50  | V     |

| Common Mode Output Voltage (V <sub>OC</sub> ) | -7.0 | +12.0 | V     |

| Output Current High (I <sub>OH</sub> )        |      | -60   | mA    |

| Output Current Low (I <sub>OL</sub> )         |      | 60    | mA    |

| Operating Temperature (T <sub>A</sub> )       | -55  | +125  | °C    |

#### **Quality Conformance Inspection**

Mil-Std-883, Method 5005 - Group A

| Subgroup | Description         | Temp (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | +25       |

| 2        | Static tests at     | +125      |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | +25       |

| 5        | Dynamic tests at    | +125      |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | +25       |

| 8A       | Functional tests at | +125      |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | +25       |

| 10       | Switching tests at  | +125      |

| 11       | Switching tests at  | -55       |

| 12       | Settling time at    | +25       |

| 13       | Settling time at    | +125      |

| 14       | Settling time at    | -55       |

### **DS96F172/DS96F174 Electrical Characteristics**

#### **AC/DC Parameters** (Note 5)

The following conditions apply, unless otherwise specified.

DC:  $V_{CC} = 5.5V$ AC:  $V_{CC} = 5.0V$

| Symbol            | Parameter                               | Conditions                                   | Notes               | Min  | Max | Unit | Sub-<br>groups |

|-------------------|-----------------------------------------|----------------------------------------------|---------------------|------|-----|------|----------------|

| V <sub>IL</sub>   | Logical 0 Input Voltage                 |                                              |                     |      | 0.8 | V    | 1              |

|                   |                                         |                                              |                     |      | 0.7 | V    | 2, 3           |

| V <sub>IH</sub>   | Logical 1 Input Voltage                 |                                              |                     | 2.0  |     | V    | 1, 2, 3        |

| V <sub>IC</sub>   | Input Clamp Voltage                     | I = -18mA                                    |                     | -1.5 |     | V    | 1, 2, 3        |

| V <sub>OD1</sub>  | Differential Output Voltage             | I <sub>O</sub> = 0mA                         |                     |      | 6.0 | V    | 1, 2, 3        |

| $V_{OD2}$         | Differential Output Voltage             | $V_{CC} = 4.5V, R_L = 54\Omega$              |                     | 1.5  |     | V    | 1, 2           |

|                   | ·                                       | Figure 1                                     | (Note 3)            | 1.2  |     | V    | 3              |

| V <sub>OD2</sub>  | Differential Output Voltage             | $V_{CC} = 4.5V, R_L = 100\Omega$<br>Figure 1 |                     | 2.0  |     | V    | 1, 2, 3        |

|                   |                                         |                                              | (Note 6)            | -200 | 200 | mV   | 1, 2           |

| $\Delta V_{OD1}$  | Change In Magnitude of V <sub>OD2</sub> | $V_{CC} = 4.5V, R_L = 54\Omega$              | ( <i>Note 3</i> ,   | -400 | 400 | mV   | 3              |

|                   |                                         |                                              | Note 6)             |      |     |      |                |

| A \ /             | Change In Magnitude of V                | V 4.5V D = 4000                              | (Note 6)            | -200 | 200 | mV   | 1, 2           |

| ΔV <sub>OD2</sub> | Change In Magnitude of V <sub>OD2</sub> | $V_{CC} = 4.5V$ , $R_L = 100\Omega$          | (Note 3,<br>Note 6) | -400 | 400 | mV   | 3              |

| V <sub>oc</sub>   | Common Mode Output Voltage              | $R_L = 54\Omega$ Figure 1                    |                     |      | 3.0 | V    | 1, 2, 3        |

| V <sub>OC</sub>   | Common Mode Output Voltage              | $R_L = 100\Omega$ Figure 1                   |                     |      | 3.0 | V    | 1, 2, 3        |

| ΔV <sub>OC</sub>  | Change in Magnitude of V <sub>OC</sub>  | $V_{CC} = 4.5V, R_L = 54\Omega$ Figure 1     | (Note 6)            | -200 | 200 | mV   | 1, 2, 3        |

| ΔV <sub>OC</sub>  | Change in Magnitude of V <sub>OC</sub>  | $V_{CC} = 4.5V, R_L = 100\Omega$ Figure 1    | (Note 7)            | -200 | 200 | mV   | 1, 2, 3        |

| I <sub>O</sub>    | Output Current With Power Off           | $V_{CC} = 0V, V_{O} = -7V \text{ to } 12V$   |                     | -50  | 50  | μA   | 1, 2, 3        |

| l <sub>oz</sub>   | High Impedance State Output Current     | V <sub>O</sub> = -7V to 12V                  |                     | -50  | 50  | μΑ   | 1, 2, 3        |

| I <sub>IH</sub>   | Logical 1 Input Current                 | V <sub>I</sub> = 2.4V                        |                     |      | 20  | μA   | 1, 2, 3        |

| I <sub>IL</sub>   | Logical 0 Input Current                 | V <sub>I</sub> = 0.4V                        |                     | -50  |     | μA   | 1, 2, 3        |

| I <sub>cc</sub>   | Supply Current                          | Outputs Enabled                              |                     |      | 50  | mA   | 1, 2, 3        |

| I <sub>ccx</sub>  | Supply Current                          | Outputs Disabled                             |                     |      | 30  | mA   | 1, 2, 3        |

| I <sub>OS1</sub>  | Short Circuit Output Current            | V <sub>O</sub> = -7V                         | (Note 4)            | -250 |     | mA   | 1, 2, 3        |

| I <sub>OS2</sub>  | Short Circuit Output Current            | V <sub>O</sub> = 0V                          | (Note 4)            | -150 |     | mA   | 1, 2, 3        |

| I <sub>OS3</sub>  | Short Circuit Output Current            | $V_O = V_{CC}$                               | (Note 4)            |      | 150 | mA   | 1, 2, 3        |

| I <sub>OS4</sub>  | Short Circuit Output Current            | V <sub>O</sub> = 12V                         | (Note 4)            |      | 250 | mA   | 1, 2, 3        |

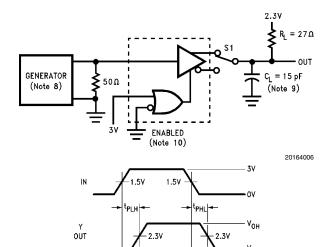

| _                 |                                         | $R_L = 27\Omega, C_L = 15pF$                 |                     |      | 25  | ns   | 10, 11         |

| t <sub>PLH</sub>  | Propagation Delay Lo to Hi level        | Figure 4                                     |                     |      | 16  | ns   | 9              |

| +                 | Propagation Delay Hi to Low             | $R_L = 27\Omega, C_L = 15pF$                 |                     |      | 25  | ns   | 10, 11         |

| t <sub>PHL</sub>  | Level                                   | Figure 4                                     |                     |      | 16  | ns   | 9              |

| SKEW              | Output to Output Delay Time             | $R_L = 60\Omega$                             |                     |      | 10  | ns   | 10, 11         |

| OKEVV             | Output to Output Delay Time             |                                              |                     |      | 4   | ns   | 9              |

| $t_LZ$            | Output Disable Time From Low            | $R_L = 110\Omega, C_L = 50pF$                |                     |      | 40  | ns   | 10, 11         |

| LZ                | Level                                   | Figure 6                                     |                     |      | 25  | ns   | 9              |

| Symbol          | Parameter                        | Conditions                       | Notes | Min | Max | Unit | Sub-<br>groups |

|-----------------|----------------------------------|----------------------------------|-------|-----|-----|------|----------------|

| +               | Output Disable Time From High    | $R_L = 110\Omega, C_L = 50pF$    |       |     | 80  | ns   | 10, 11         |

| t <sub>HZ</sub> | Level                            | Figure 5                         |       |     | 30  | ns   | 9              |

| +               | Output Enable Time to Low Level  | $R_L = 110\Omega, C_L = 50pF$    |       |     | 100 | ns   | 10, 11         |

| t <sub>ZL</sub> |                                  | Figure 6                         |       |     | 40  | ns   | 9              |

| +               | Output Enable Time to High Level | $R_L = 110\Omega, C_L = 50pF$    |       |     | 40  | ns   | 10, 11         |

| <sup>L</sup> ZH | t <sub>ZH</sub>                  | Figure 4                         |       |     | 32  | ns   | 9              |

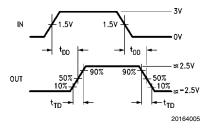

| +               | Differential Output Delay Time   | $R_{L} = 60\Omega, C_{L} = 15pF$ |       |     | 30  | ns   | 10, 11         |

| ι <sub>DD</sub> | Differential Output Delay Time   | Figure 3                         |       |     | 22  | ns   | 9              |

| +               | Differential Output Transition   | $R_{L} = 60\Omega, C_{L} = 15pF$ |       |     | 40  | ns   | 10, 11         |

| ι <sub>TD</sub> | Time                             | Figure 3                         |       |     | 22  | ns   | 9              |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: Above  $T_A = 25$ °C, derate "E" package 13.3, "J" package 12.5, "W" package 7.1 mW/°C

Note 3: -55°C limit exceeds EIA standard RS-485 specification

Note 4:  $0.2\mu F$  cap is connected between the output and Gnd to reduce oscillation.

Note 5: All currents into the device pins are positive; all currents out of the device pins are negative. All voltages are reference to ground unless otherwise specified.

$\textbf{Note 6: } \Delta |V_{OD}| \text{ is the change in magnitude of } V_{OD}, \text{ that occurs when the input is changed between high and low levels.}$

Note 7:  $\Delta |V_{OC}|$  is the change in magnitude of the  $V_{OC}$  that occurs when the input is changed between high and low levels.

#### **Parameter Measurement Information**

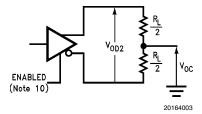

V<sub>CM</sub> = -7V to +12V (Note 10)

FIGURE 1. Differential and Common

Mode Output Voltage

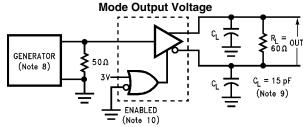

FIGURE 2. Differential Output Voltage with Varying Common Mode Voltage

FIGURE 3. Differential Output Delay and Transition Times

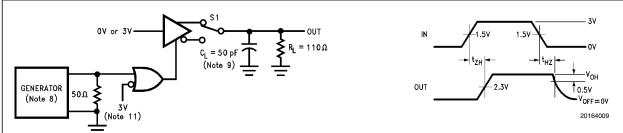

**FIGURE 4. Propagation Delay Times**

V<sub>0L</sub>

OUT

FIGURE 5.  $t_{ZH}$  and  $t_{HZ}$

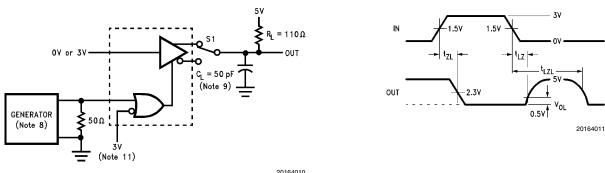

FIGURE 6.  $t_{ZL}$ ,  $t_{LZ}$ ,  $t_{LZL}$

8

Note 8: The input pulse is supplied by a generator having the following characteristics: f = 1.0 MHz, duty cycle = 50%,  $t_r \le 5.0$  ns,  $t_$

Note 10: DS96F172 with active high and active low Enables is shown. DS96F174 has active high Enable only.

Note 11: To test the active low Enable  $\overline{E}$  of DS96F172 ground  $\overline{E}$  and apply an inverted waveform to  $\overline{E}$ . DS96F174 has active high Enable only.

Note 12: For more information see Application Bulletin, Contact Product Marketing.

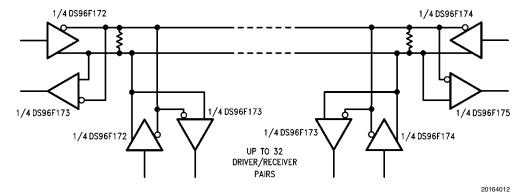

# **Typical Application**

The line length should be terminated at both ends in its characteristic impedance. Stub lengths off the main line should be kept as short as possible.

# **Revision History**

| Released | Revision | Section | Changes                                                                                                                       |

|----------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| 8–Apr-11 | А        | , ' '   | 2 MDS data sheets converted into one Corp. data sheet format. MNDS96F172M-X Rev 1A0 & MNDS96F174M-X Rev 1B0 will be archived. |

|          |          |         |                                                                                                                               |

|          |          |         |                                                                                                                               |

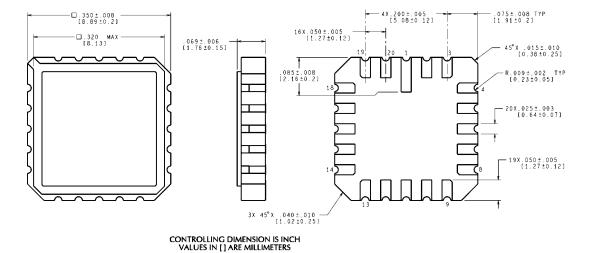

E20A (Rev F)

#### Physical Dimensions inches (millimeters) unless otherwise noted

20-Lead Ceramic Leadless Chip Carrier (E)

NS Package Number E20A

0.785 [19.94] MAX 0.220-0.310 [5.59-7.87] R [0.025 [0.64] 0.005-0.020 TYP [0.13-0.51] 0.037 ± 0.005 [0.94 ± 0.13] 0.005 0.055 ± 0.005 [1.40 ± 0.13] TYP [0.13] GLASS SEALANT 0.020-0.060 [0.51-1.52] 0.200 0.180 MAX [5.08] 0.010 ± 0.002 [0.25 ± 0.05] TYP MAX TYP 0.125-0.200 TYP 90° ± 4° / TYP ± 5° 0.080 [2.03] MAX → BOTH ENDS 0.310-0.410 [7.87-10.41] 0.018 ± 0.003 TYP JI6A (REV L) 0.100 ± 0.010 [2.54 ± 0.25] TYP —

16-Lead Ceramic Dual-In-Line Package (J) NS Package Number J16A

#### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pro                            | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com