# 10-output, 400-MHz LVPECL Zero Delay Buffer

#### **Features**

- 400-ps max Total Timing Budget<sup>™</sup> (TTB<sup>™</sup>) window

- 10 LVPECL outputs

- 1 LVPECL differential input

- Selectable output frequency range from 100 to 400 MHz

- · Multiply by 2 option

- 15-ps RMS Cycle-Cycle Jitter

- Power-down mode

- Lock indicator

- · 3.3V power supply

- Available in 48-pin QFN package

#### Overview

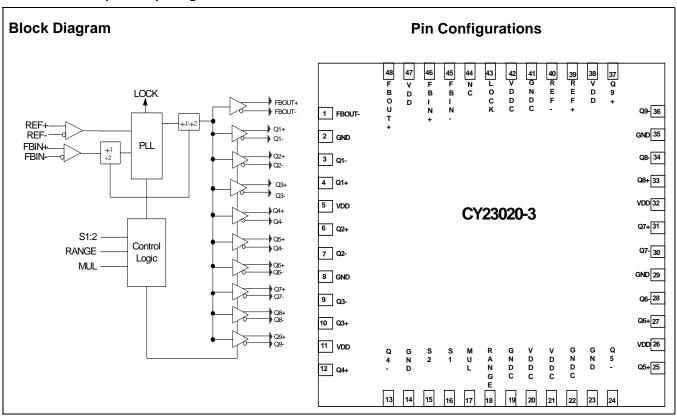

TheCY23020-3 is a high-performance 400-MHz LVPECL Output phase-locked loop (PLL)-based zero delay buffer (ZDB) designed for high- speed clock distribution applications. The device features a guaranteed TTB window specifying all occurrences of output clocks with respect to the input reference clock across variations in voltage, temperature, process, frequency, and ramp rate.

Additionally, the CY23020-3 can be used as a fan-out buffer via the S[1:2] control pins. In this mode, the PLL is bypassed and the reference clock is routed to the output buffers.

## Pin Definitions<sup>[1]</sup>

| Pin Name           | Pin No.                  | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------|--------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REF+<br>REF-       | 39<br>40                 | I           | <b>Reference Inputs.</b> Output signals are synchronized to the crossing point of REF+ and REF-signals. In DC mode, the REF+/REF- inputs must be held at opposite logical states. For optimal performance, the impedances seen by these two inputs must be equal.                                                                                                                                                                                                                                                  |  |  |

| FBIN+<br>FBIN-     | 46<br>45                 | I           | <b>Feedback Inputs</b> . Input FBIN+/FBIN- must be fed by one of the outputs to ensure proper functionality. If the trace between FBIN+/FBIN- and FBOUT+/FBOUT- is equal in length to the traces between the outputs and the signal destinations, then the signals received at the destinations will be synchronized to the clock signal at REF+/REF- inputs. In DC mode, FBIN+/FBIN- inputs must be held at opposite logical states. For best performance, the impedances seen by these two inputs must be equal. |  |  |

| FBOUT+<br>FBOUT-   | 48<br>1                  | 0           | <b>Feedback Output</b> . In order to complete the phase locked loop, similar polarity outputs must be connected back to the FBIN+ and FBIN- pins. Any of the outputs may actually be used as the feedback source.                                                                                                                                                                                                                                                                                                  |  |  |

| Q1+, Q1-           | 4, 3                     | 0           | Differential Q1 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q2+, Q2-           | 6, 7                     | 0           | Differential Q2 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q3+, Q3-           | 10, 9                    | 0           | Differential Q3 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q4 +, Q4-          | 12, 13                   | 0           | Differential Q4 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q5+, Q5-           | 25, 24                   | 0           | Differential Q5 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q6+, Q6-           | 27, 28                   | 0           | Differential Q6 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q7+, Q7-           | 31, 30                   | 0           | Differential Q7 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q8+, Q8-           | 33, 34                   | 0           | Differential Q8 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Q9+, Q9-           | 37, 36                   | 0           | Differential Q9 Outputs. Refer to Tables 1,2, and 3 for configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| RANGE <sup>1</sup> | 18                       | Ι           | Frequency Range Selection Input. To determine the correct connection for this pin, refer to Table 2. This should be a static input                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| LOCK               | 43                       | 0           | <b>PLL Locked Output.</b> When this output is HIGH, the PLL in the CY23020-3 is in steady state operation mode (Locked). When this signal is LOW, the PLL is in the process of locking onto the reference signal.                                                                                                                                                                                                                                                                                                  |  |  |

| S1:2               | 16, 15                   | ı           | Output/PLL Enable Selection Bits. Refer to Table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VDDC               | 20, 21, 42               | Р           | Analog Power Connection. Connect to 3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| GNDC               | 19, 22, 41               | G           | Analog Ground Connection. Connect to common system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| VDD                | 5, 11, 26, 32,<br>38, 47 | Р           | Output Buffer Power Connections. Connect 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| GND                | 2, 8, 14, 23,<br>29, 35  | G           | Ground Connections. Connect to common system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| MUL <sup>[2]</sup> | 17                       | I           | <b>Multiplication Factor Select</b> . When set HIGH, the outputs will run at twice the speed of the reference signal. This should be a static input.                                                                                                                                                                                                                                                                                                                                                               |  |  |

| NC                 | 44                       | NC          | <b>Do Not Connect</b> . This pin must be left floating. This pin is used by the factory for testing purposes.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

## **Table 1. Output Configuration**

| S1 | S2 | Outputs                  | PLL      |  |

|----|----|--------------------------|----------|--|

| 0  | 0  | Three-state              | Shutdown |  |

| 0  | 1  | Reserved                 |          |  |

| 1  | 0  | Reference Input Shutdown |          |  |

| 1  | 1  | LL Output Enabled        |          |  |

## Notes:

- There are no power-up sequence requirements on the power supply pins of the CY23020-3.

RANGE and MUL have a ~100k pull-down.

Page 2 of 9 Document #: 38-07473 Rev. \*A

Table 2. Frequency Range Setting

| RANGE Output Frequency Range |             |

|------------------------------|-------------|

| 0                            | 100–200 MHz |

| 1                            | 200–400 MHz |

**Table 3. Frequency Multiplication Table**

| MUL | Output Frequency |

|-----|------------------|

| 0   | = REF            |

| 1   | = 2 * REF        |

## **How to Implement Zero Delay**

Typically, ZDBs multiply (fan-out) single-clock signals quantity while simultaneously reducing or mitigating the time delay associated with passing the clock through a buffering device. In many cases the output clock is adjusted, in phase, to occur later or more often before the device's input clock to compensate for a design's physical delay inadequacies. Most commonly this is done using a simple PCB trace as a time delay element. The longer the trace the earlier the output clock edges occur with respect to the reference input clock edges.

In this way such effects as undesired transit time of a clock signal across a PCB can be compensated for.

## Inserting Other Devices in Feedback Path

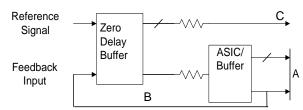

Due to the fact that the device has an external feedback path the user has a wide range of control over its output to input skewing effect. One of these is to be able to synchronize the outputs of an external clock that is resultant from any of the output clocks. This implementation can be applied to any device (ASIC, multiple output clock buffer/driver, etc.) which is put into the feedback path.

Referring to Figure 1, if the traces between the ASIC/buffer and the destination of the clock signal(s) (A) are equal in length to the trace between the buffer and the FBIN pin (B), the signals at the destination(s) device (C) will be driven high at the same time the Reference clock provided to the ZDB goes high. Synchronizing the other outputs of the ZDB to the outputs from the ASIC/Buffer is more complex however, as any propagation delay in the ASIC/Buffer must be accounted for.

There are constraints when inserting other devices. If the devices contain PLLs or excessively long delay times they can easily cause the overall clocking system to become unstable as the components interact. For these designs it is advisable to contact Cypress for applications support.

Figure 1. Output Buffer in Feedback Path

Table 4. Absolute Maximum Ratings<sup>[3]</sup>

| Parameter        | Description                                            | Rating                        | Unit |

|------------------|--------------------------------------------------------|-------------------------------|------|

| $V_{DD}$         | Voltage on any V <sub>DD</sub> pin with respect to GND | -0.5 to +5.0                  | V    |

| V <sub>IN</sub>  | Voltage on any input pin with respect to GND           | –0.5 to V <sub>DD</sub> + 0.5 | V    |

| T <sub>STG</sub> | Storage Temperature                                    | -65 to +150                   | °C   |

| T <sub>A</sub>   | Operation Temperature (QFN)                            | -40 to 85                     | °C   |

| T <sub>J</sub>   | Junction Temperature                                   | 135                           | °C   |

Table 5. PECL DC Output Specification [4]

|                                                           |                           |            | V <sub>CC</sub> = | 3.135 | V <sub>CC</sub> | = 3.3 | V <sub>CC</sub> = | 3.465 |

|-----------------------------------------------------------|---------------------------|------------|-------------------|-------|-----------------|-------|-------------------|-------|

| Parameter                                                 | Description               | Conditions | Min.              | Max.  | Min.            | Max.  | Min.              | Max.  |

| V <sub>OH</sub>                                           |                           |            | 1.835             | 2.435 | 2               | 2.6   | 2.165             | 2.765 |

| V <sub>OL</sub>                                           |                           |            | 1.135             | 1.735 | 1.3             | 1.9   | 1.465             | 2.065 |

| V <sub>OH</sub> (rel to V <sub>CC</sub> )                 |                           |            | -1.3              | -0.7  | -1.3            | -0.7  | -1.3              | -0.7  |

| V <sub>OL</sub> (rel to V <sub>CC</sub> )                 |                           |            | -2                | -1.4  | -2              | -1.4  | -2                | -1.4  |

| These result in the follow                                | owing mid point values:[4 | 1]         |                   |       |                 |       |                   |       |

| V <sub>MID</sub> ((V <sub>OH +</sub> V <sub>OL</sub> )/2) |                           |            | 1.485             | 2.085 | 1.65            | 2.25  | 1.815             | 2.415 |

| V <sub>MID</sub> Relative to V <sub>CC</sub>              |                           |            | -1.65             | -1.05 | -1.65           | -1.05 | -1.65             | -1.05 |

#### Notes:

- Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

- 4. The midpoint voltage is average value of a waveform. For differential signals the midpoint is assumed to be the same for both the true and complement since the V<sub>OH</sub> and V<sub>OL</sub> of both the true and complement signals in general should be the same. V<sub>MID</sub> is not necessarily equal to the differential crossover voltage, which may be skewed if there is differential time delays between the signals.

Table 5. PECL DC Output Specification (continued) $^{[4]}$

|                 |           |                                              |                     | V <sub>CC</sub> = | 3.135 | V <sub>CC</sub> | = 3.3 V <sub>CC</sub> = 3.46 |      | 3.465 |

|-----------------|-----------|----------------------------------------------|---------------------|-------------------|-------|-----------------|------------------------------|------|-------|

|                 | Parameter | Description                                  | Conditions          | Min.              | Max.  | Min.            | Max.                         | Min. | Max.  |

|                 |           |                                              | •                   | М                 | in.   | Ma              | ax.                          | Uı   | nit   |

| $I_{PD}$        |           | Power-down Current 70°C, V <sub>DD</sub> max |                     |                   | 100   |                 | μΑ                           |      |       |

| I <sub>IL</sub> |           |                                              | V <sub>IN</sub> = 0 |                   |       | 1               | 0                            | μ    | A     |

| I <sub>IH</sub> |           |                                              | $V_{IN} = V_{DD}$   |                   |       | 10              | 00                           | μ    | A     |

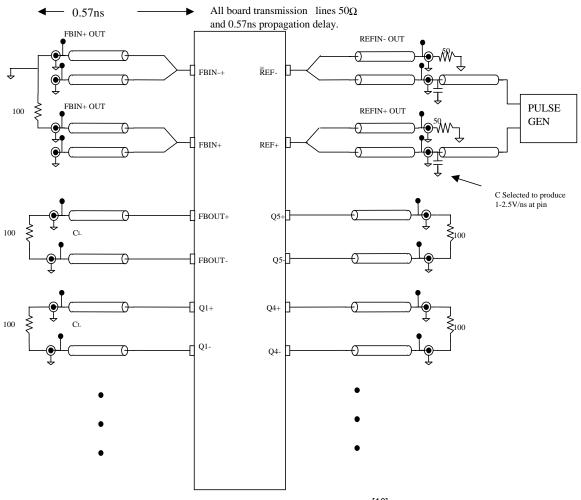

Table 6.  $V_{DDC}$  = 3.3V ±5%,  $V_{DD}$  = 3.3V ±5% (See Test Set-ups,  $C_L$  = 5 pF)

| Parameter                     | Description                                                      | Condition                                                                                               | Min.                        | Тур. | Max.                     | Unit |

|-------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|------|--------------------------|------|

| I <sub>DD</sub>               |                                                                  | Loaded, V <sub>DD</sub> max, Cold, 400 MHz, all outputs switching                                       |                             |      | 300                      | mA   |

| C <sub>IN</sub>               | REF or FBIN ± Pin Capacitance                                    |                                                                                                         | 4                           | 5    | 6                        | pF   |

| C <sub>L</sub> <sup>[5]</sup> | Load Cap                                                         |                                                                                                         |                             | 5    |                          | pF   |

| V <sub>ISW</sub>              | Single Ended Input Swing                                         |                                                                                                         | 0.5                         |      | 1.25                     | V    |

| V <sub>IX</sub> [6]           | Input Crossover Voltage (expressed relative to V <sub>DD</sub> ) |                                                                                                         | V <sub>DD</sub> – 1.79      |      | V <sub>DD</sub> – 0.96   |      |

| Sı                            | Input Slew Rate                                                  | Measured from $V_{\rm IX\ MEAS}$ + 0.15 to $V_{\rm IX\ MEAS}$ -0.15. (20–80% of a min input swing sig.) | 0.9                         |      | 4                        | V/ns |

| V <sub>OSW</sub>              | Single Ended Output Swing                                        |                                                                                                         | 0.6                         |      | 1.1                      | V    |

| V <sub>OX</sub> [7]           | Output Crossing Point                                            | VO <sub>MID</sub> = (VH <sub>MEAS</sub> )/2                                                             | VO <sub>MID</sub> –<br>0.20 |      | VO <sub>MID</sub> – 0.20 |      |

| V <sub>OX</sub> [8]           | Output Crossing Point (relative to V <sub>DD</sub> )             | VO <sub>MID</sub> = (VH <sub>MEAS</sub> )/2                                                             | V <sub>DD</sub> – 1.79      |      | V <sub>DD</sub> – 0.96   |      |

Table 7.  $V_{DDC}$  = 3.3V ±5%,  $V_{DD}$  = 3.3V ±5% (See Test Set-ups,  $C_L$  = 5 pF)

| Parameter            | Description                          | Condition                                                                                                   | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|------|

| S <sub>O</sub>       | Output Rise/Fall Slew<br>Rate        | Measured from V <sub>IX MEAS</sub> + 0.15 to V <sub>IX MEAS</sub> -0.15. (20–80% of a min input swing sig.) |      |      | 2    | V/ns |

| D <sub>I</sub>       | Input Duty Cycle                     | Input duty cycle                                                                                            | 40   |      | 60   | %    |

| D <sub>O</sub>       | Output Duty Cycle                    | Differential crossing point                                                                                 | 45   |      | 55   | %    |

| T <sub>PDIO</sub>    | REFin-FBin prop delay                | External feedback REF, FB same frequency                                                                    | -50  |      | 200  | ps   |

| T <sub>PDIOD</sub>   | REFin-FBin prop delay                | External feedback REF, FB same frequency x2                                                                 | -50  |      | 150  | ps   |

| T <sub>PDO</sub>     | FBout to any output prop delay       |                                                                                                             | -325 |      | -100 | ps   |

| T <sub>PDOB</sub>    |                                      | Output-Output skew within a bank                                                                            |      |      | 150  | ps   |

| T <sub>PDOB133</sub> |                                      | Output-Output skew @133 MHz                                                                                 |      | 75   |      | ps   |

| T <sub>TB</sub>      | Total Timing Budget                  |                                                                                                             |      |      | 400  | ps   |

| T <sub>JCCPP</sub>   | Cycle-Cycle Jitter (1000 cycles) p-p | REF and outputs, same frequency                                                                             |      |      | 100  | ps   |

| T <sub>JCCRMS</sub>  | RMS Cycle-Cycle Jitter               | REF and outputs, same frequency                                                                             |      |      | 15   | ps   |

| Tjccop               |                                      | Ref = x2                                                                                                    |      |      | 125  | ps   |

| Tjrms                |                                      | Ref = x2                                                                                                    |      |      | 30   | ps   |

#### Notes:

- Same as input. PECL is assumed to drive single point loads.

This is the output DC mid-voltage range ± the crossover voltage tolerance. Refer Input Voltage is assumed to be derived from same supply as part. This is why it is spec'd relative to V<sub>DD</sub>.

Crossover is within ± 20% of the center of the minimum swing.

Crossover is within ± 20% of the center of the minimum swing.

Document #: 38-07473 Rev. \*A Page 4 of 9

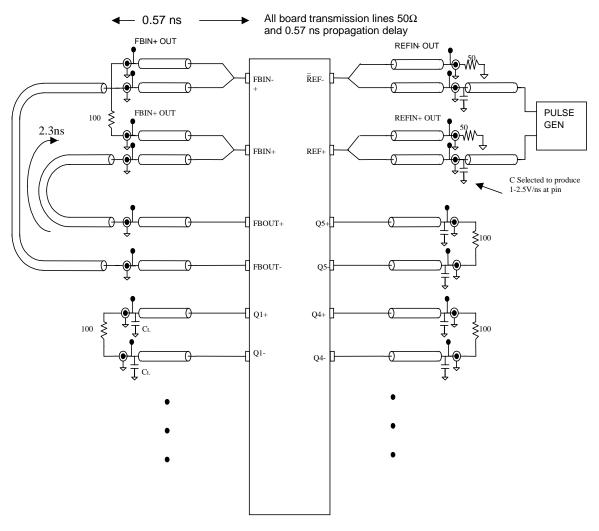

Figure 2. Test Set-up 1 Example

[+] Feedback

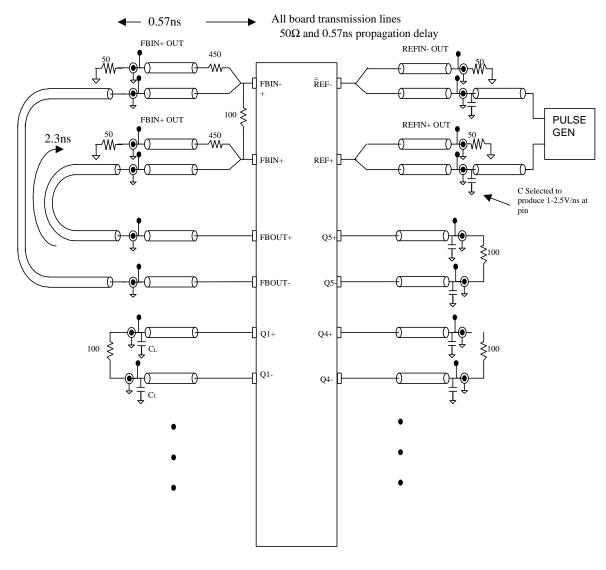

Figure 3. Test Set-up 2 Example<sup>[9]</sup>

#### Note:

9. The above configuration may provide better termination at the FBIN input.

Document #: 38-07473 Rev. \*A

Figure 4. Test Set-up 3 Example<sup>[10]</sup>

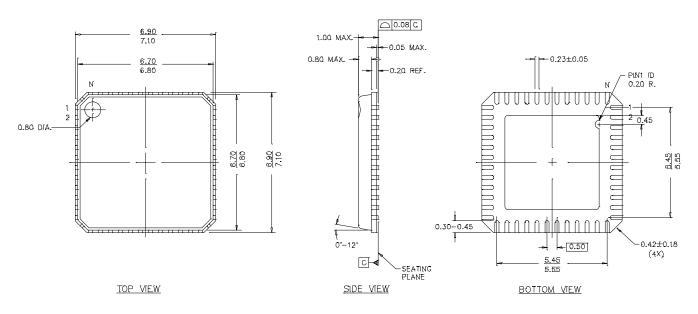

## **Ordering Information**

| Ordering Code | Package Type             | Temperature Range          |

|---------------|--------------------------|----------------------------|

| CY23020LFI-3  | 48-pin QFN               | Industrial, -40°C to +85°C |

| CY23020LFI-3T | 48-pin QFN-Tape and Reel | Industrial, -40°C to +85°C |

#### Note:

10. If accurate pin-pin skew is not obtainable with the load capacitors, a third configuration can be made with no load C. In this case only pin-pin skew is characterized. Part must be in PLL bypass mode.

Document #: 38-07473 Rev. \*A

[+] Feedback

## **Package Drawing and Dimension**

## 48-lead QFN (7 × 7 mm) LF48

DIMENSIONS IN mm MIN. MAX.

51-85152-\*A

Total Timing Budget and TTB are trademarks of Cypress Semiconductor. All product and company names listed in this document are the trademarks of their respective holders.

## **Document History Page**

| Document Title: CY23020-3 10-output, 400-MHz LVPECL Zero Delay Buffer Document Number: 38-07473 |                                       |          |     |                                                |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------|----------|-----|------------------------------------------------|--|

| REV. ECN NO. Date Change Description of Change                                                  |                                       |          |     |                                                |  |

| **                                                                                              | ** 118965 11/05/02 HWT New Data Sheet |          |     |                                                |  |

| *A                                                                                              | 126939                                | 06/10/03 | RGL | Fixed the block diagram (removed the C1 input) |  |

Document #: 38-07473 Rev. \*A Page 9 of 9