## CY25C01/02/04/08/16

# 1 Kbit, 2 Kbit, 4 Kbit, 8 Kbit, and 16 Kbit (x8) SPI Serial EEPROM

## Features

- Continuous voltage operation  $\Box V_{CC} = 1.8V$  to 5.5V

- Internally organized as 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K), 1024 x 8 (8K), or 2048 x 8 (16K)

- Serial peripheral interface compatible

- Supports SPI modes 0 (0,0) and 3 (1,1)

- Block write protection

Protect 1/4,1/2, or entire array

- Fast clock rate

20 MHz clock rate (V<sub>CC</sub> = 4.5V to 5.5V)

10 MHz clock rate (V<sub>CC</sub> = 1.8V to 5.5V)

- Write protect (WP) pin and write disable instructions for both hardware and software data protection

- 32-byte page write mode

- Self timed write cycle (5 ms max)

- High reliability

Endurance: 1 million write cycles

Data retention: 100 years

- Industrial temperature range

- 8-Pin SOIC and 8-Pin TSSOP packages

- Pb-free and RoHS compliant

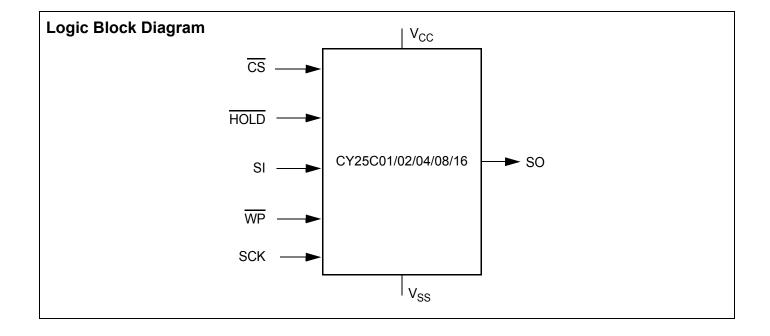

## **Functional Description**

The CY25C01/02/04/08/16 provides 1024, 2048, 4096, 8192, and 16384 bits of serial Electrically Erasable and Programmable Read Only Memory (EEPROM) organized as 128, 256, 512, 1024, or 2048 words of eight bits each. The device is optimized for use in many industrial applications where low power and low voltage operations are essential. The CY25C01/02/04/08/16 is available in space saving 8-Pin SOIC, and 8-Pin TSSOP packages.

The <u>CY</u>25C01/02/04/08/16 is enabled through the Chip Select pin (CS) and accessed via a three-wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self timed and no separate erase cycle is required before write.

Block write protection is enabled by programming the status register with one of four blocks of write protection. Separate program enable and program disable instructions are provided for additional data <u>protection</u>. Hardware data protection is provided through the WP pin to protect against inadvertent write attempts to the status register. The HOLD pin can be used to suspend any serial communication without resetting the serial sequence.

**Cypress Semiconductor Corporation** Document #: 001-15633 Rev. \*C 198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised February 05, 2009

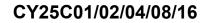

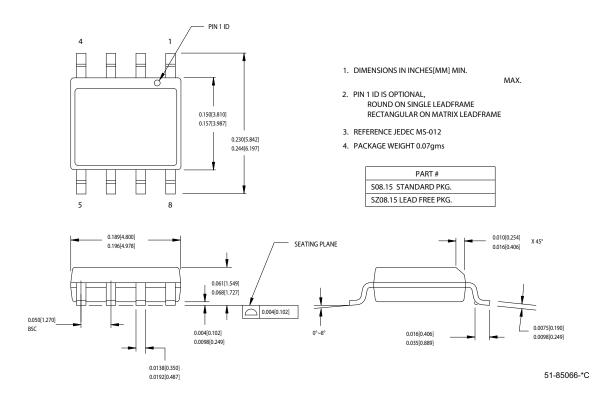

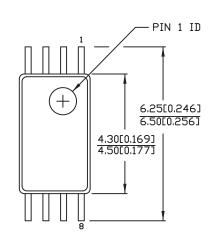

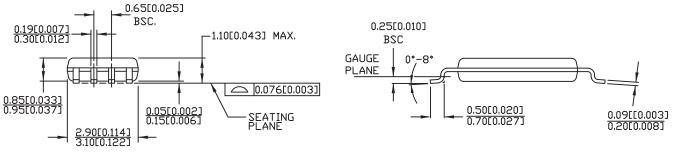

## **Pin Configuration**

Figure 1. Pin Diagram - 8-Pin SOIC/TSSOP

## Table 1. Pin Definitions - 8 Pin SOIC/TSSOP

| Pin Name        | 8-SOIC/PDIP/TSSOP<br>Pin Number | I/O Type            | Description           |

|-----------------|---------------------------------|---------------------|-----------------------|

| CS              | 1                               | Input               | Chip Select           |

| SO              | 2                               | Output              | Serial Data Output    |

| WP              | 3                               | Input Write Protect |                       |

| GND             | 4                               | Input               | Ground                |

| SI              | 5                               | Input               | Serial Data Input     |

| SCK             | 6                               | Input               | Serial Data Clock     |

| HOLD            | 7                               | Input               | Suspends Serial Input |

| V <sub>CC</sub> | 8                               | Input               | Power Supply          |

## Serial Interface Description

### Master

The device that generates the serial clock.

### Slave

The CY25C01/02/04/08/16 always operates as a slave because the Serial Clock pin (SCK) is always an input.

### **Transmitter or Receiver**

The CY25C01/02/04/08/16 has separate pins designated for data transmission (SO) and reception (SI).

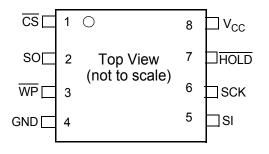

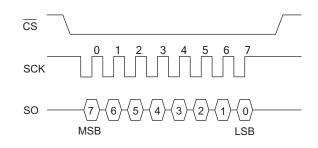

### MSB

The Most Significant Bit (MSB) is the first bit transmitted and received.

## Serial Op-Code

After the device is selected with  $\overline{\text{CS}}$  going low, the first byte is received. This byte contains the op-code that defines the operations to be performed.

### Invalid Op-Code

If an invalid op-code is received, no data is shifted to the CY25C01/02/04/08/16. The serial output pin (SO) remains in a high impedance state until the falling edge of CS is detected again. This reinitializes the serial communication.

### **Chip Select**

The CY25C01/02/04/08/16 is selected when the  $\overline{\text{CS}}$  pin is low. When the device is not selected, data is not accepted through the SI pin and the serial output pin (SO) remains in a high impedance state.

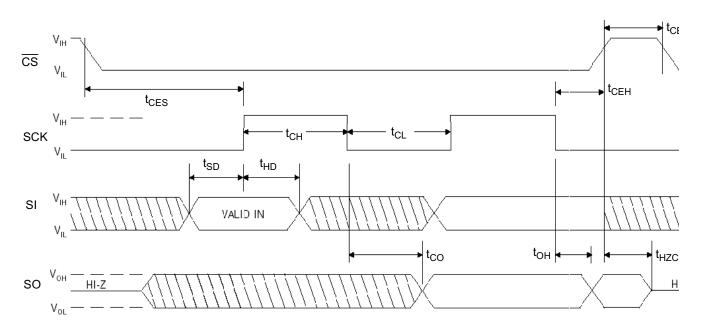

### Hold

The HOLD pin is used in conjunction with the CS pin to select the CY25C01/02/04/08/16. When the device is selected and a serial sequence is underway, HOLD can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the HOLD pin must be brought low when the SCK pin is low. To resume serial communication, the HOLD pin is brought high when the SCK pin is low (SCK may still toggle during HOLD). The HOLD signal behaves as a level sensitive signal. This means, if the HOLD signal is asserted when SCK is high, its value is latched and when SCK becomes low, the latched value is considered to halt the transmission. Inputs to the SI pin are ignored when the SO pin is in the high impedance state.

### Write Protect

The write protect pin  $(\overline{WP})$  enables normal read or write operations when held high. When the WP pin is brought low, all write

operations are inhibited. WP going low while  $\overline{CS}$  is still low interrupts a write to the CY25C01/02/04/08/16. If the internal write cycle is already initiated, WP going low has no effect on the write operation.

## **SPI Modes**

These devices can be driven by a microcontroller with its SPI peripheral running in either of the following modes:

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (SCK) and output data is available from the falling edge of Serial Clock (SCK).

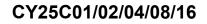

The difference between the two modes, shown in Figure 2 and Figure 3, is the clock polarity when the bus master is in standby mode and not transferring data:

- SCK remains at 0 for (CPOL=0, CPHA=0)

- SCK remains at 1 for (CPOL=1, CPHA=1)

Figure 2. SPI Mode 0

### Figure 3. SPI Mode 3

## **Operating Features**

### Power Up

When the power supply is turned on, V<sub>CC</sub> rises from V<sub>SS</sub> to V<sub>CC</sub>. During this time, the Chip Select ( $\overline{CS}$ ) must be allowed to follow the V<sub>CC</sub> voltage. It must not be allowed to float, but must be connected to V<sub>CC</sub> through a suitable pull up resistor. As a built in safety feature, Chip Select ( $\overline{CS}$ ) is edge sensitive and level sensitive. After power up, the device is not selected until a falling edge is first detected on Chip Select ( $\overline{CS}$ ). This ensures that the Chip Select ( $\overline{CS}$ ) was high, before going low to start the first operation.

### **Device Internal Reset**

To prevent inadvertent write operations during power up, a Power On Reset (POR) circuit is included. During power up (continuous rise up of V<sub>CC</sub>), the device does not respond to any instruction until the V<sub>CC</sub> reaches the POR threshold voltage (this threshold is lower than the minimum V<sub>CC</sub> operating voltage

During power down (continuous decay of  $V_{CC}$ ), as soon as  $V_{CC}$  drops from the normal operating voltage, below the POR threshold voltage, the device stops responding to any instruction sent to it.

### **Power Down**

During power down, the device must be deselected and in standby <u>power mode</u> (no internal write cycle in progress). Chip Select (CS) must be allowed to follow the voltage applied on  $V_{CC}$ .

### **Active Power and Standby Power Modes**

When Chip Select ( $\overline{CS}$ ) is low, the device is selected in the active power mode. The device consumes  $I_{CC}$ , as specified in

DC Electrical Characteristics on page 9. When Chip Select ( $\overline{\text{CS}}$ ) is high, the device is deselected. If an erase or write cycle is currently not in progress, the device goes into the standby power mode, and the device consumption drops to I<sub>SB1</sub>.

## **Functional Description**

The CY25C01/02/04/08/16 supports the SPI bus data transmission protocol. The synchronous Serial Peripheral Interface (SPI) helps the CY25C01/02/04/08/16 to interface directly with many of the popular microcontrollers.

The CY25C01/02/04/08/16 uses an 8-bit instruction register. The list of instructions and their operation codes are contained in Table 2. All instructions, addresses, and data are transferred with the MSB, and it starts with a high to low  $(\overline{CS})$  transition.

defined). When  $V_{CC}$  passes over the POR threshold, the device is reset and is in the following state:

- Standby power mode

- Deselected (after power up, a falling edge is required on Chip Select (S) before any instructions are started)

- Not in the hold condition

Status register state:

- The Write Enable (WEN) bit is reset to 0

- (RDY) is set to 1

The WPEN<sup>[1]</sup>, BP1 and BP0 bits of the status register are unchanged from the previous power down (they are non volatile bits). Before selecting and issuing instructions to the memory, a valid and stable  $V_{CC}$  voltage must be applied. This voltage must remain stable and valid until the end of the transmission of the instruction and for a write instruction, until the completion of the internal write cycle (t<sub>WR</sub>).

| Table | 2. | Instruction | Set |

|-------|----|-------------|-----|

|-------|----|-------------|-----|

| Instruction<br>Name | Instruction<br>Format | Operation                   |

|---------------------|-----------------------|-----------------------------|

| WREN                | 0000 X110             | Set Write Enable Latch      |

| WRDI                | 0000 X100             | Reset Write Enable Latch    |

| RDSR                | 0000 X101             | Read Status Register        |

| WRSR                | 0000 X001             | Write Status Register       |

| READ                | 0000 X011             | Read Data From Memory Array |

| WRITE               | 0000 X010             | Write Data To Memory Array  |

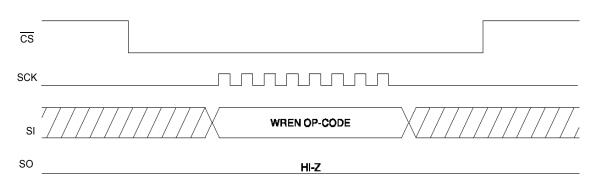

### Write Enable (WREN)

The device powers up in the write disable state when  $V_{CC}$  is applied. All programming instructions must therefore be preceded by a Write Enable instruction.

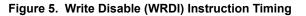

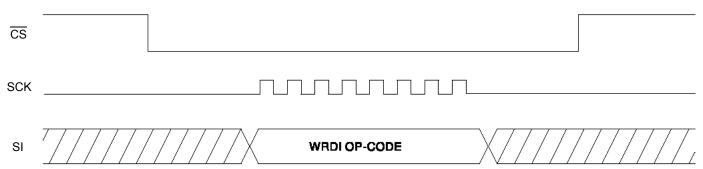

### Write Disable (WRDI)

To protect the device against inadvertent writes, the Write Disable instruction disables all programming modes. The WRDI instruction is independent of the status of the WP pin.

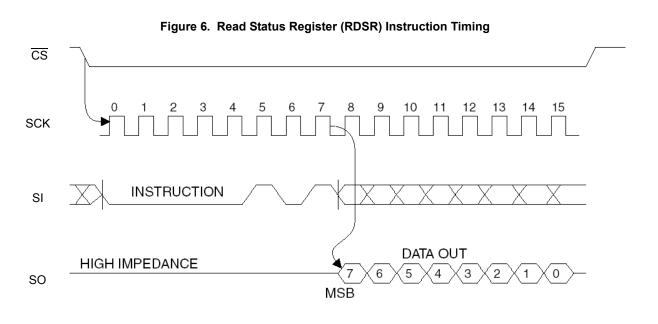

### **Read Status Register (RDSR)**

The Read Status Register instruction provides access to the status register. The READY/BUSY and Write Enable status of the device is determined by the RDSR instruction. Similarly, the block write protection bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.

Note

1. WPEN bit is applicable only for 8K and 16K devices.

#### Table 3. Status Register Format for CY25C01/02/04

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| X     | Х     | Х     | Х     | BP1   | BP0   | WEN   | RDY   |

#### Table 4. Status Register Format for CY25C08/16

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPEN  | Х     | Х     | Х     | BP1   | BP0   | WEN   | RDY   |

#### Table 5. Status Register Bit Definition

| Bit                 | Definition                                                                                                                       |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit 0 (RDY)         | Bit $0 = 0^{\circ}$ (RDY) indicates the device is READY. Bit $0 = 1^{\circ}$ indicates the write cycle is in progress.           |  |  |  |

| Bit 1 (WEN)         | Bit 1= '0' indicates the device is not WRITE ENABLED. Bit 1 = '1' indicates the device is write enabled.                         |  |  |  |

| Bit 2 (BP0)         | See Table 6.                                                                                                                     |  |  |  |

| Bit 3 (BP1)         | See Table 6.                                                                                                                     |  |  |  |

| Bits 4–6 are '0's v | vhen device is not in an internal write cycle.                                                                                   |  |  |  |

| Bit 7 (X / WPEN)    | When the device is not in an internal write cycle, this bit is 0 in CY25C01/02/04 and WPEN (See Table 7 on page 5) in CY25C08/16 |  |  |  |

| Bits 0–7 are '1's o | Bits 0–7 are '1's during an internal write cycle.                                                                                |  |  |  |

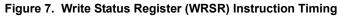

### Write Status Register (WRSR)

The WRSR instruction enables the user to select one of four levels of protection. The CY25C01/02/04/08/16 is divided into four array segments. One quarter, one half, or all of the memory segments can be protected. Any of the data within any selected segment is therefore read only. The block write protection levels and corresponding status register control bits are shown in Table 6.

The three bits BP0, BP1, and WPEN<sup>[1]</sup> are nonvolatile cells that have the same properties and functions as the regular memory cells (for example, WREN,  $t_{WC}$ , RDSR).

The WRSR instruction in CY25C08/16 also allows the user to enable or disable the write protect (WP) pin using the Write Protect Enable (WPEN) bit. Hardware write protection is enabled when the WP pin is low and the WPEN bit is '1'. Hardware write protection is disabled when the WP pin is high or when the WPEN bit is '0' (See Table 7).

When the device is hardware write protected, writes to the status register, including the block protect bits and the WPEN<sup>[1]</sup> bit, and the block protected sections in the memory array are disabled. Writes are only allowed to sections of the memory that are not block protected.

#### Table 6. Block Write Protect Bits

| Level   | Status Register Bits |     | Array Addresses Protected |         |           |             |             |  |

|---------|----------------------|-----|---------------------------|---------|-----------|-------------|-------------|--|

|         | BP1                  | BP0 | CY25C01                   | CY25C02 | CY25C04   | CY25C08     | CY25C16     |  |

| 0       | 0                    | 0   | None                      | None    | None      | None        | None        |  |

| 1 (1/4) | 0                    | 1   | 60 - 7F                   | C0 - FF | 180 - 1FF | 0300 - 03FF | 0600 - 07FF |  |

| 2 (1/2) | 1                    | 0   | 40 - 7F                   | 80 - FF | 100 - 1FF | 0200 - 03FF | 0400 - 07FF |  |

| 3 (All) | 1                    | 1   | 00 - 7F                   | 00 - FF | 000 - 1FF | 0000 - 03FF | 0000 - 07FF |  |

#### Table 7. WPEN Operation

| WPEN | WP   | WEN | Protected Blocks | Unprotected Blocks | Status Register |

|------|------|-----|------------------|--------------------|-----------------|

| 0    | Х    | 0   | Protected        | Protected          | Protected       |

| 0    | Х    | 1   | Protected        | Writable           | Writable        |

| 1    | Low  | 0   | Protected        | Protected          | Protected       |

| 1    | Low  | 1   | Protected        | Writable           | Protected       |

| Х    | High | 0   | Protected        | Protected          | Protected       |

| Х    | High | 1   | Protected        | Writable           | Writable        |

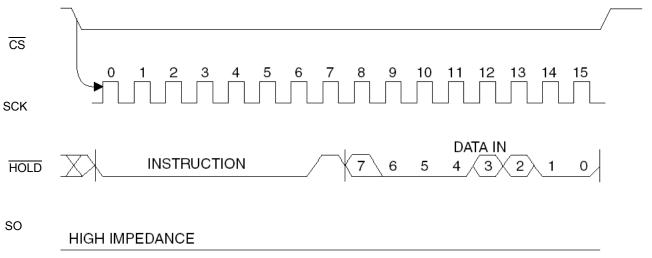

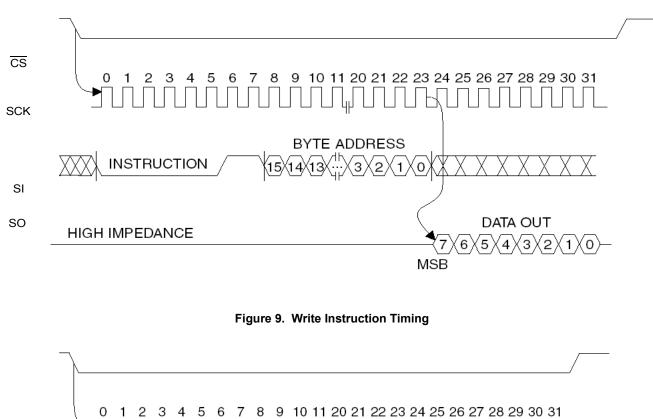

## Read Sequence (READ)

Reading the CY25C01/02/04/08/16 through the Serial Output (SO) pin requires the following sequence. After the CS line is pulled low to select a device, the read op-code (including A8) is transmitted through the SI line followed by the byte address to be read (A7–A0). When completed, any data on the SI line is ignored. The data (D7–D0) at the specified address is shifted out onto the SO line. If only one byte is to be read, the CS line must be driven high after the data comes out. The read sequence can be continued since the byte address is automatically incremented and data continues to be shifted out. When the highest address is reached, the address counter rolls over to the lowest address allowing the entire memory to be read in one continuous read cycle.

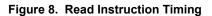

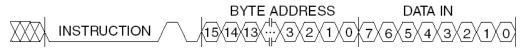

## Write Sequence (WRITE)<sup>[2]</sup>

To program the CY25C01/02/04/08/16, two separate instructions must be executed. First, the device must be write enabled through the WREN instruction. Then a write (WRITE) instruction can be executed. Also, the address of the memory locations to be programmed must be outside the protected address field location selected by the block write protection level. During an

internal write cycle, all commands are ignored except the RDSR instruction.

The sequence for a write instruction is as follows. After the CS line is pulled low to select the device, the WRITE op-code is transmitted throuh the SI line followed by the byte address (A7–A0) and the data (D7–D0) to be programmed. Programming starts after the CS pin is brought high. The low to high transition of the CS pin must occur during the SCK low time immediately after clocking in the D0 (LSB) data bit.

The READY/ $\overline{\text{BUSY}}$  status of the device is determined by initiating a read status register (RDSR) instruction. If Bit 0 = '1', the write cycle is still in progress. If Bit 0 = '0', the write cycle has ended. Only the RDSR instruction is enabled during the write programming cycle.

The CY25C01/02/04/08/16 is capable of a 32-byte page write operation. After each byte of data is received, the five low order address bits are internally incremented by one; the high order bits of the address remain constant. If more than 16 bytes of data are transmitted, the address counter rolls over and the previously written data is overwritten. The CY25C01/02/04/08/16 is automatically returned to the write disable state at the completion of a write cycle. WEN bit is reset after every write instruction regardless of it belonging to a protected array.

#### Figure 4. Write Enable (WREN) Instruction Timing

Note

2. If the device is not write enabled (WREN), the device ignores the write instruction and return to the standby state, when CS is brought HIGH. A new CS falling edge is required to re initiate the serial communication.

HIGH IMPEDANCE

## CY25C01/02/04/08/16

## **Maximum Ratings**

Exceeding maximum ratings may impair the useful life of the device. These user guidelines are not tested.

| Storage temperature65°C to +150°C                                                |

|----------------------------------------------------------------------------------|

| Ambient temperature with power applied40°C to +125°C                             |

| Supply voltage on $V_{CC}$ relative to GND–0.6V to +6.0V                         |

| DC voltage applied to outputs in high-Z state0.5V to V_{CC} + 1.0V               |

| Input voltage –0.5V to $V_{CC}$ + 0.5V                                           |

| Transient voltage (<20 ns) on any pin to ground potential1.0V to $V_{CC}$ + 2.0V |

## **DC Electrical Characteristics**

Over the Operating Range (V<sub>CC</sub> = 1.8V to 5.5V)

| Package power dissipation capability $(T_A = 25^{\circ}C)$ | 1.0W                  |

|------------------------------------------------------------|-----------------------|

| Surface mount lead soldering temperature (3 Seconds)       | +260°C for 10 seconds |

| Output short circuit current <sup>[3]</sup>                | 50 mA                 |

| Static discharge voltage<br>(per MIL-STD-883, Method 3015) | > 2001V               |

| Latch up current                                           | > 200 mA              |

|                                                            |                       |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>cc</sub> |

|------------|---------------------|-----------------|

| Industrial | –40°C to +85°C      | 1.8V to 5.5V    |

| Parameter        | Description            | Test Conditions                                                             | Min                   | Max                                  | Unit |

|------------------|------------------------|-----------------------------------------------------------------------------|-----------------------|--------------------------------------|------|

| V <sub>CC</sub>  | Supply Voltage         |                                                                             | 1.8                   | 5.5                                  | V    |

| I <sub>SB1</sub> | Standby Current        | $V_{CC}$ = 1.8V, $\overline{CS}$ = $V_{CC}$                                 |                       | 1                                    | μA   |

| I <sub>SB2</sub> | Standby Current        | $V_{CC} = 2.7V, \overline{CS} = V_{CC}$                                     |                       | 1.1                                  | μA   |

| I <sub>SB3</sub> | Standby Current        | $V_{CC} = 5.5V, \overline{CS} = V_{CC}$                                     |                       | 1.2                                  | μA   |

| I <sub>CC1</sub> | Supply Current (Read)  | V <sub>CC</sub> = 1.8V - 5.5V at 10 MHz                                     |                       | 5                                    | mA   |

|                  |                        | V <sub>CC</sub> = 4.5V - 5.5V at 20 MHz                                     |                       | 10                                   | mA   |

| I <sub>CC2</sub> | Supply Current (Write) | V <sub>CC</sub> = 5.5V                                                      |                       | 5                                    | mA   |

| ILI              | Input Leakage Current  | $V_{IN} = V_{CC} \text{ or } V_{SS}$                                        |                       | 1                                    | μA   |

| I <sub>LO</sub>  | Output Leakage Current | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>                        |                       | 1                                    | μA   |

| V <sub>IL</sub>  | Input LOW Voltage      | 1.8V <u>≤</u> V <sub>CC</sub> <u>≤</u> 2.7V                                 | -0.6 <sup>[4]</sup>   | 0.3 V <sub>CC</sub>                  | V    |

|                  |                        | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V                                               | -0.6 <sup>[4]</sup>   | 0.8                                  |      |

| V <sub>IH</sub>  | Input HIGH Voltage     | 1.8V <u>≤</u> V <sub>CC</sub> <u>≤</u> 5.5V                                 | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 0.5 <sup>[4]</sup> | V    |

| V <sub>OL</sub>  | Output LOW Voltage     | I <sub>OL</sub> = 3 mA, 3.6 <u>≤</u> V <sub>CC</sub> <u>≤</u> 5.5V          |                       | 0.4                                  | V    |

|                  |                        | I <sub>OL</sub> = 0.15 mA, 1.8 <u>≤</u> V <sub>CC</sub> <u>≤</u> 3.6V       |                       | 0.2                                  |      |

| V <sub>OH</sub>  | Output HIGH Voltage    | I <sub>OH</sub> = -0.1 mA, 1.8 <u>≤</u> V <sub>CC</sub> ≤ 3.6V              | V <sub>CC</sub> – 0.2 |                                      | V    |

|                  |                        | I <sub>OH</sub> = −1.6 mA, 3.6 <u>&lt;</u> V <sub>CC</sub> <u>&lt;</u> 5.5V | V <sub>CC</sub> – 0.8 |                                      |      |

#### Note

Outputs shorted for only one second. Only one output shorted at a time.

This parameter is characterized but not tested.

## Capacitance

In the following table, the capacitance parameters are listed. <sup>[5]</sup>

| Parameter        | Description            | Test Conditions                         | Max | Unit |

|------------------|------------------------|-----------------------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance      | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 6   | pF   |

| C <sub>OUT</sub> | Output Pin Capacitance | V <sub>CC</sub> = 5.5V                  | 8   | pF   |

## **Thermal Resistance**

In the following table, the thermal resistance parameters are listed.<sup>[5]</sup>

| Parameter     | Description                                 | Test Conditions                                                                                             | 8-SOIC | 8-TSSOP | Unit |

|---------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|---------|------|

| $\Theta_{JA}$ | Thermal Resistance<br>(Junction to Ambient) | Test conditions follow standard test methods and proce-<br>dures for measuring thermal impedance, per EIA / | 120.83 | 119.31  | °C/W |

| $\Theta_{JC}$ | Thermal Resistance<br>(Junction to Case)    | JESD51.                                                                                                     | 90.31  | 82.77   | °C/W |

## **Reliability Characteristics**

In the following table, the reliability characteristics parameters are listed.<sup>[5]</sup>

| Parameter        | Description     | Test Method         | Min                   | Unit   |

|------------------|-----------------|---------------------|-----------------------|--------|

| N <sub>END</sub> | Endurance       | JEDEC Standard A117 | 1 Million             | Cycles |

| T <sub>DR</sub>  | Data Rentention | JEDEC Standard A103 | 100                   | Years  |

| I <sub>LTH</sub> | Latch Up        | JEDEC Standard 78   | 100 + I <sub>CC</sub> | mA     |

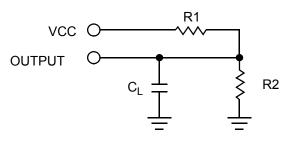

### Figure 10. AC Test Loads and Waveforms

| Parameters | Frequency | 1.8V - 2.7V | 2.7V - 5.5V | Unit |

|------------|-----------|-------------|-------------|------|

| R1         | 20/10 MHz | 1.8K        | 1.8K        | Ω    |

| R2         | 20/10 MHz | 1.3K        | 1.3K        | Ω    |

| CL         | 20 MHz    | -           | 30          | pF   |

|            | 10 MHz    | 30          |             |      |

AC test inputs are driven at  $V_{IHT}$  (0.9 $V_{CC}$ ) for a logic "1" and  $V_{ILT}$  (0.1 $V_{CC}$ ) for a logic "0". Measurement reference points for inputs and outputs are  $V_{LT}$  ( $V_{CC}/2 - 0.1V$ ) and  $V_{HT}$  ( $V_{CC}/2 + 0.1V$ ). Input rise and fall times (10%–90%) are <20 ns

#### Note

5. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

## **AC Switching Characteristics**

| Cypress<br>Parameter | Alt<br>Parameter  | Description            | 20 MHz<br>(4.5V to 5.5V) |     | 10 MHz<br>(1.8V to 5.5V) |     | Unit |

|----------------------|-------------------|------------------------|--------------------------|-----|--------------------------|-----|------|

|                      |                   |                        | Min                      | Max | Min                      | Max |      |

| f <sub>SCK</sub>     | f <sub>SCK</sub>  | Clock Frequency, SCL   |                          | 20  |                          | 10  | MHz  |

| t <sub>CL</sub>      | t <sub>LOWH</sub> | Clock Pulse Width Low  | 20                       |     | 40                       |     | ns   |

| t <sub>CH</sub>      | t <sub>WL</sub>   | Clock Pulse Width High | 20                       |     | 40                       |     | ns   |

| t <sub>CE</sub>      | t <sub>CS</sub>   | CS High Time           | 30                       |     | 50                       |     | ns   |

| t <sub>CES</sub>     | t <sub>CSS</sub>  | CS Setup Time          | 25                       |     | 50                       |     | ns   |

| t <sub>CEH</sub>     | t <sub>CSH</sub>  | CS Hold Time           | 25                       |     | 50                       |     | ns   |

| t <sub>SD</sub>      | t <sub>SU</sub>   | Data In Setup Time     | 5                        |     | 10                       |     | ns   |

| t <sub>HD</sub>      | t <sub>H</sub>    | Data In Hold Time      | 5                        |     | 10                       |     | ns   |

| t <sub>H.HLD</sub>   | t <sub>HD</sub>   | HOLD Hold Time         | 5                        |     | 10                       |     | ns   |

| t <sub>S.HLD</sub>   | t <sub>CD</sub>   | HOLD Setup Time        | 5                        |     | 10                       |     | ns   |

| t <sub>co</sub>      | t <sub>V</sub>    | Output Valid           |                          | 20  |                          | 40  | ns   |

| t <sub>HZ</sub>      | t <sub>HZ</sub>   | HOLD to Output High Z  |                          | 40  |                          | 80  | ns   |

| t <sub>LZ</sub>      | t <sub>LZ</sub>   | HOLD to Output Low Z   |                          | 25  |                          | 50  | ns   |

| t <sub>OH</sub>      | t <sub>HO</sub>   | Output Hold Time       | 0                        |     | 0                        |     | ns   |

| t <sub>HZCE</sub>    | t <sub>DIS</sub>  | Output Disable Time    |                          | 40  |                          | 80  | ns   |

| t <sub>WC</sub>      | t <sub>WC</sub>   | Write Cycle Time       |                          | 5   |                          | 5   | ms   |

| t <sub>r</sub>       | t <sub>r</sub>    | Rise Time              |                          | 4.8 |                          | 10  | ns   |

| t <sub>f</sub>       | t <sub>f</sub>    | Fall Time              |                          | 4.8 |                          | 10  | ns   |

Figure 12. Synchronous Data Timing (Mode 0)

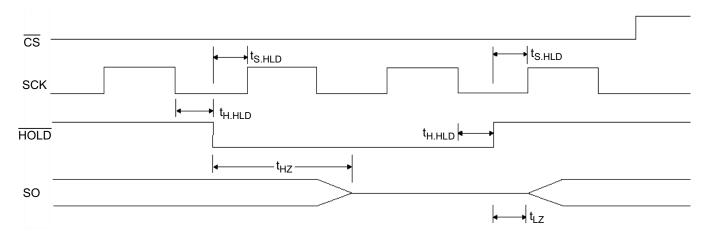

## Part Numbering Nomenclature

## **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Diagram | Package Type              | Operating<br>Range |

|---------------|---------------|--------------------|---------------------------|--------------------|

| 1 Kbit        | CY25C01-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|               | CY25C01-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|               | CY25C01-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|               | CY25C01-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 2 Kbit        | CY25C02-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|               | CY25C02-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|               | CY25C02-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|               | CY25C02-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 4 Kbit        | CY25C04-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|               | CY25C04-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|               | CY25C04-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|               | CY25C04-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 8 Kbit        | CY25C08-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|               | CY25C08-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|               | CY25C08-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|               | CY25C08-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 16 Kbit       | CY25C16-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|               | CY25C16-SXIT  | 7                  | 8-Pin SOIC (Tape & Reel)  |                    |

|               | CY25C16-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|               | CY25C16-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

This table contains Preliminary information. Please contact your local Cypress sales representative for availability of these parts.

## **Package Diagrams**

Figure 14. 8-Pin (150-Mil) SOIC, 51-85066

## Package Diagrams (continued)

Figure 15. 8-Pin (4.4 mm) TSSOP, 51-85093

DIMENSIONS IN MMEINCHES] MIN. MAX.

REFERENCE JEDEC MD-153

| PART #   |                |  |  |  |

|----------|----------------|--|--|--|

| Z08.173  | STANDARD PKG.  |  |  |  |

| ZZ08.173 | LEAD FREE PKG. |  |  |  |

51-85093-\*A

Page 15 of 17

## **Document History Page**

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 1069220 | UHA                | See ECN            | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *A   | 2522135 | GVCH/<br>PYRS      | 06/27/08           | 32 byte Page Mode in Features<br>Added Pb-Free and RoHS compliant information in "Features"<br>Removed PDIP package<br>Removed Automotive Temperature range<br>Updated Status Register Bit Definition Table 3.<br>Added description on write status Register(WRSR)<br>Added WPEN Operation Table 5.<br>Changed Supply voltage on V <sub>CC</sub> relative to GND max value from 5.0V to 6.0V<br>Corrected Typo of Vcc max value from 5.0V to 5.5V<br>Table 10: Added Thermal Resistance values for 8-TSSOP package<br>Table 12: Changed tr and tf values from 9.75 ns to 10 ns<br>Added AC test load values for different parameters<br>Updated Part Numbering Nomenclature and Ordering Information                                                           |

| *B   | 2611873 | VKN/<br>PYRS       | 11/24/08           | Changed Part # from CY25D01/02/04 to CY25C01/02/04<br>Added 8 Kbit and 16 Kbit parts and their related information<br>Added footnote 1 related to WPEN<br>Added 20 MHz clock rate specifications<br>Updated part numbering nomenclature<br>Updated ordering information table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *C   | 2656511 | VKN/PYRS           | 02/09/09           | Converted from preliminary to final<br>Added figures 2 and 3<br>Included V <sub>IL</sub> spec of 0.8V for the V <sub>CC</sub> range between 2.7V to 5.5V<br>Updated V <sub>IH</sub> test conditions<br>Added footnote #4<br>Updated V <sub>OL</sub> and V <sub>OH</sub> test conditions<br>On page 10, specified V <sub>CC</sub> range for AC test load conditions<br>Changed C <sub>L</sub> from 100pF to 30pF for 10MHz<br>On page 10, corrected AC measurement reference points from V <sub>IT</sub> and V <sub>OT</sub> to V <sub>LT</sub><br>and V <sub>HT</sub> respectively<br>Changed V <sub>LT</sub> level from 0.3V <sub>CC</sub> to V <sub>CC</sub> /2 - 0.1V<br>Changed V <sub>HT</sub> level from 0.7V <sub>CC</sub> to V <sub>CC</sub> /2 + 0.1V |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | <b>PSoC Solutions</b> |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2007-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-15633 Rev. \*C

Revised February 05, 2009

Page 17 of 17

All products and company names mentioned in this document may be the trademarks of their respective holders.