## CY27EE16ZE

# 1 PLL In-System Programmable Clock Generator with Individual 16K EEPROM

## Features

- 18 kbits of EEPROM

16 kbits independent scratch

2 kbits dedicated to clocking functions

- Integrated, phase-locked loop with programmable P and Q counters, output dividers, and optional analog VCXO, digital VCXO, spread spectrum for EMI reduction

- In system programmable through I<sup>2</sup>C Serial Programming Interface (SPI). Both the SRAM and non-volatile EEPROM memory bits are programmable with the 3.3V supply

- · Low-jitter, high-accuracy outputs

- VCXO with analog adjust

- 3.3V Operation (optional 2.5V outputs)

- 20-lead Exposed Pad, EP-TSSOP

## **Benefits**

Higher level of integration and reduced component count by combining EEPROM and PLL. Independent EEPROM may be used for scratch memory, or to store up to eight clock configurations.

High-performance PLL enables control of output frequencies that are customizable to support a wide range of applications.

Familiar industry standard eases programming effort and enables update of data stored in 16K EEPROM scratchpad and 2K EEPROM clock control block while CY27EE16ZE is installed in system.

Meets critical timing requirements in complex system designs.

Write Protect (WP pin) can be programmed to serve as an analog control voltage for a VCXO.The VCXO function is still available with a DCXO, or <u>digitally controlled</u> (through SPI) crystal <u>oscillator</u> if the pin is functioning as WP.

Meets industry-standard voltage platforms.

Industry standard packaging saves on board space.

| ſ | Part Number | Outputs | Input Frequency Range                                                                          | Output Frequency Range                                                                                                                                     |

|---|-------------|---------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | CY27EE16ZE  | 6       | 1 –150 MHz (Driven Clock Input) {Industrial}<br>8 – 30 MHz (Crystal Reference) {Comm. or Ind.} | 80 kHz – 200 MHz (3.3V) {Commercial}<br>80 kHz –167 MHz (3.3V) {Industrial}<br>80 kHz –167 MHz (2.5V) {Commercial}<br>80 kHz – 150 MHz (2.5V) {Industrial} |

**Cypress Semiconductor Corporation** Document #: 38-07440 Rev. \*C 3901 North First Street

San Jose, CA 95134 • 408-943-2600 Revised December 21, 2004

## **Pin Description**

| Name                | Pin Number | Description                                                        |

|---------------------|------------|--------------------------------------------------------------------|

| XIN                 | 1          | Reference crystal input                                            |

| VDD                 | 2, 19      | 3.3V voltage supply                                                |

| CLOCK6              | 3          | Clock output 6                                                     |

| AVDD                | 4          | 3.3V analog voltage supply                                         |

| SDAT                | 5          | Data input for serial programming                                  |

| AVSS                | 6          | Analog ground                                                      |

| VSSL                | 7          | Output ground                                                      |

| CLOCK1              | 8          | Clock output 1                                                     |

| CLOCK2              | 9          | Clock output 2                                                     |

| OE/PDM              | 10         | Output enable or power-down mode enable                            |

| VDDL                | 11,14      | Output voltage supply                                              |

| CLOCK3              | 12         | Clock output 3                                                     |

| SCL                 | 13         | Clock signal input for serial programming                          |

| CLOCK4              | 15         | Clock output 4                                                     |

| VSS                 | 16         | Ground                                                             |

| VCXO/WP             | 17         | Analog control input for VCXO or write protect (user-configurable) |

| CLOCK5              | 18         | Clock output 5                                                     |

| XOUT <sup>[1]</sup> | 20         | Reference crystal output                                           |

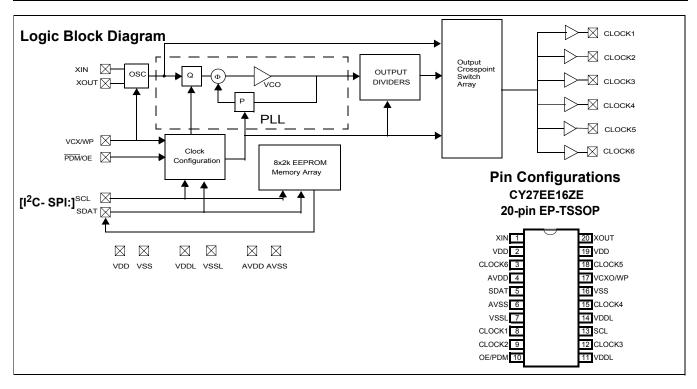

## **Functional Description**

The CY27EE16ZE integrates a 16-kbit EEPROM scratchpad and a clock generator that features Cypress's programmable clock core. An industry standard  $I^2C$  serial programming interface (SPI) is used to program the scratchpad and clock core.

## 16-kbit EEPROM

The 16-kbit EEPROM scratchpad is organized in eight blocks x 256 words x 8 bits. Each of the eight 2-kbit EEPROM scratchpad blocks, a 2-kbit clock configuration EEPROM block, and a 2-kbit volatile clock configuration SRAM block, have their own 7-bit device address. The device address is combined with a Read/Write bit as the LSB and is sent after each start bit.

## **Clock Features**

The programmable clock core is configured with the following features:

- **Crystal Oscillator**: Programmable drive and load, support for external references up to 166 MHz. See "Reference Frequency (REF)", page 5

- VCXO: Analog or digital control

- Inputs and I/Os: Programmable input muxes drive write protect (WP), analog VCXO control, output enable (OE), and power down mode (PDM) functions

- PLL: Programmable P, Q, offset, and loop filter parameters.

**Outputs**: Six outputs and two programmable linear dividers. The output swing of CLOCK1 through CLOCK4 is set by VDDL (2.5V or 3.3V). The output swing of CLOCK5 and CLOCK6 is set by VDD (3.3V).

Note:

1. Float XOUT if XIN is externally driven.

Document #: 38-07440 Rev. \*C

Clock configuration is stored in a dedicated 2-kbit block of nonvolatile EEPROM and a 2-kbit block of volatile SRAM. The SPI is used to write new configuration data to the on-chip programmable registers that are defined within the clock configuration memory blocks. Other, custom configurations, that include custom VCXO, Spread Spectrum for EMI reduction, Fractional N and frequency select pins (FS) are programmable; contact factory for details.

#### Write Protect (WP) - Active HIGH

The default clock configuration of the CY27EE16ZE has pin 17 configured as WP. When a logical HIGH level input is asserted on this pin, the write protect feature (WP) will inhibit writing to the EEPROM. This protects EEPROM bits from being changed, while allowing full read access to EEPROM. Writing to SRAM is allowed with WP enabled. When this pin is held at a logical LOW level, WP is disabled and data can be written to EEPROM.

# Analog Adjust for Voltage Controlled Crystal Oscillator (VCXO)

Pin 17 can be programmed, with the SPI, to function as the analog control for the VCXO. Then, pin 17 provides ±150 ppm adjustment of the crystal oscillator frequency (in order to use the VCXO, the crystal must have a minimum of ±150 ppm pull range and meet the pullable crystal specifications as shown in *Table 14* on page 12). The crystal oscillator frequency is pulled lower by at least 150 ppm when 0V is applied to VCXO, pulled higher by at least 150 ppm when V<sub>DD</sub> is applied to VCXO. The oscillator frequency will have a linear dependence on the voltage level applied to pin 17, VCXO, within a range from 0V to V<sub>DD</sub>. See section "Device Addressing", page 10 for more information.

#### Output Enable (OE) – Active HIGH

The default clock configuration has pin 10 programmed as an Output Enable (OE). This pin enables the divider bank clock outputs when HIGH, and disables divider bank clock outputs when LOW.

#### Power-down Mode (PDM) – Active LOW

The Power-down Mode (PDM) function <u>is available when pin</u> 10 of the CY27EE16ZE is configured as PDM. When the PDM signal pulled LOW, all clock components are shut down and the part enters a <u>low-power state</u>. To configure pin 10 of the CY27EE16ZE as PDM, see "Power-down Mode (PDM) and Output Enable (OE) Registers for Pin 10", page 7.

#### Serial Programming Interface (SPI)

The SPI uses industry-standard signaling in both standard and fast modes to program the 8 x 2 kbit EPPROM blocks of scratchpad, the 2-kbit EEPROM dedicated to clock configuration, and the 2-kbit SRAM block. See sections beginning with "Using the Serial Programming Interface (SPI)", page 3 for more information.

## Default Start-up Condition for CY27EE16ZE

The default (programmed) condition of the 8 x 256 bit EEPROM blocks (scratchpad) in the device as shipped from the factory, are blank and unprogrammed. In this condition, all bits are set to 0.

The default clock configuration is:

- the crystal oscillator circuit is active.

- CLOCK1 outputs REF frequency.

- All other outputs are three-stated.

- WP control on pin 17.

- OE control on pin 10.

This default clock configuration is typically customized to meet the needs of a specific application. It provides a clock signal upon power-on, to facilitate in-system programming. Alternatively, the CY27EE16ZE may be programmed with a different clock configuration prior to placement of the CY27EE16ZE in systems. While you can develop your own subroutine to program any or all of the individual registers described in the following pages, it may be easier to use CyClocksRT<sup>™</sup> to produce the required register setting file.

### Using the Serial Programming Interface (SPI)

The CY27EE16ZE provides an industry-standard serial programming interface for volatile and nonvolatile, in-system programming of unique frequencies and options. Serial programming and reprogramming allows for quick design changes and product enhancements, eliminates inventory of old design parts, and simplifies manufacturing.

The CY27EE16ZE is a group of ten slave devices with addresses as shown in *Figure 1*. The serial programming interface address of the CY27EE16ZE clock configuration 2-kbit EEPROM block is 69H. The serial programming interface address of the CY27EE16ZE clock configuration 2-kbit SRAM block is 68H. Should there be a conflict with any other devices in your system, all device addresses can also be changed using CyberClocks. Registers in the clock configuration 2-kbit SRAM memory block are written, when the user wants to update the clock configuration for on-the-fly changes. Registers in the clock configuration EEPROM block are written, if the user wants to update the clock configuration so that it is saved and used again after power-up or reset.

All programmable registers in the CY27EE16ZE are addressed with eight bits and contain eight bits of data. *Table 1* lists the specific register definitions and their allowable values. See section "Serial Programming Interface Timing", page 12, for a detailed description.

| 1st                                                              | 2nd                                                                        | 3rd          | 4th          | 5th          | 6th          | 7th          | 8th          |

|------------------------------------------------------------------|----------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| EE block                                                         | EE block                                                                   | EE block     | EE block     | EE block     | EE block     | EE block     | EE block     |

| 256 x 8 bits                                                     | 256 x 8 bits                                                               | 256 x 8 bits | 256 x 8 bits | 256 x 8 bits | 256 x 8 bits | 256 x 8 bits | 256 x 8 bits |

| Address:                                                         | Address:                                                                   | Address:     | Address:     | Address:     | Address:     | Address:     | Address:     |

| 1000000                                                          | 1000001                                                                    | 1000010      | 1000011      | 1000100      | 1000101      | 1000110      | 1000111      |

| clock config.<br>EE block<br>256 x 8 bits<br>Address:<br>1101000 | <b>clock config.</b><br><b>SRAM</b><br>256 x 8 bits<br>Address:<br>1101001 |              |              |              |              |              |              |

Figure 1. Device Addresses for EEPROM Scratchpad and Clock Configuration Blocks

| Register | Description                               | D7                              | D6                              | D5                       | D4                       | D3                       | D2                       | D1                       | D0                       |

|----------|-------------------------------------------|---------------------------------|---------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 09H      | CLKOE control                             | 0                               | CLOCK6                          | CLOCK5                   | 0                        | CLOCK4                   | CLOCK3                   | CLOCK2                   | CLOCK1                   |

| OCH      | DIV1SRC mux and<br>DIV1N divider          | DIV1SRC                         | DIV1N(6)                        | DIV1N(5)                 | DIV1N(4)                 | DIV1N(3)                 | DIV1N(2)                 | DIV1N(1)                 | DIV1N(0)                 |

| 10H      | Input Pin Control<br>Registers            | OESrc                           | OE0PadS<br>el[1]                | OE0PadS<br>el[0]         | OE1PadS<br>el[1]         | OE1PadS<br>el[0]         | PDMEna-<br>ble           | PDMPad-<br>Sel[1]        | PDMPad-<br>Sel[0]        |

| 11H      | Write Protect<br>Registers                |                                 |                                 |                          | MemWP                    | WPSrc                    | WPPad-<br>Sel[2]         | WPPad-<br>Sel[1]         | WPPad-<br>Sel[0]         |

| 12H      | Input crystal oscillator<br>drive control | FTAAd-<br>drSrc(1)<br>default=0 | FTAAd-<br>drSrc(0)<br>default=0 | XCapSrc<br>default=1     | XDRV(1)                  | XDRV(0)                  | 0                        | 0                        | 0                        |

| 13H      | Input load capacitor control              | Cap-<br>Load(7)                 | Cap-<br>Load(6)                 | Cap-<br>Load(5)          | Cap-<br>Load(4)          | Cap-<br>Load(3)          | Cap-<br>Load(2)          | Cap-<br>Load(1)          | Cap-<br>Load(0)          |

| 14H      | ADC Register                              | ADCEn-<br>able                  | AD-<br>CBypCnt                  | ADC-<br>Cnt[2]           | ADC-<br>Cnt[1]           | ADC-<br>Cnt[0]           | ADCFilt[1]               | ADCFilt[0]               | 0                        |

| 40H      | Charge Pump and PB                        | 1                               | 1                               | 0                        | Pump(2)                  | Pump(1)                  | Pump(0)                  | PB(9)                    | PB(8)                    |

| 41H      | counter                                   | PB(7)                           | PB(6)                           | PB(5)                    | PB(4)                    | PB(3)                    | PB(2)                    | PB(1)                    | PB(0)                    |

| 42H      | PO counter, Q<br>counter                  | PO                              | Q(6)                            | Q(5)                     | Q(4)                     | Q(3)                     | Q(2)                     | Q(1)                     | Q(0)                     |

| 44H      | Crosspoint switch matrix control          | CLKSRC2<br>for<br>CLOCK1        | CLKSRC1<br>for<br>CLOCK1        | CLKSRC0<br>for<br>CLOCK1 | CLKSRC2<br>for<br>CLOCK2 | CLKSRC1<br>for<br>CLOCK2 | CLKSRC0<br>for<br>CLOCK2 | CLKSRC2<br>for<br>CLOCK3 | CLKSRC1<br>for<br>CLOCK3 |

| 45H      |                                           | CLKSRC0<br>for<br>CLOCK3        | CLKSRC2<br>for<br>CLOCK4        | CLKSRC1<br>for<br>CLOCK4 | CLKSRC0<br>for<br>CLOCK4 | 1                        | 1                        | 1                        | CLKSRC2<br>for<br>CLOCK5 |

| 46H      |                                           | CLKSRC1<br>for<br>CLOCK5        | CLKSRC0<br>for<br>CLOCK5        | CLKSRC2<br>for<br>CLOCK6 | CLKSRC1<br>for<br>CLOCK6 | CLKSRC0<br>for<br>CLOCK6 | 1                        | 1                        | 1                        |

| 47H      | DIV2SRC mux and<br>DIV2N divider          | DIV2SRC                         | DIV2N(6)                        | DIV2N(5)                 | DIV2N(4)                 | DIV2N(3)                 | DIV2N(2)                 | DIV2N(1)                 | DIV2N(0)                 |

## Table 1. Summary Table – CY27EE16ZE Programmable Registers

## CY27EE16ZE Frequency Calculation and Register Definitions

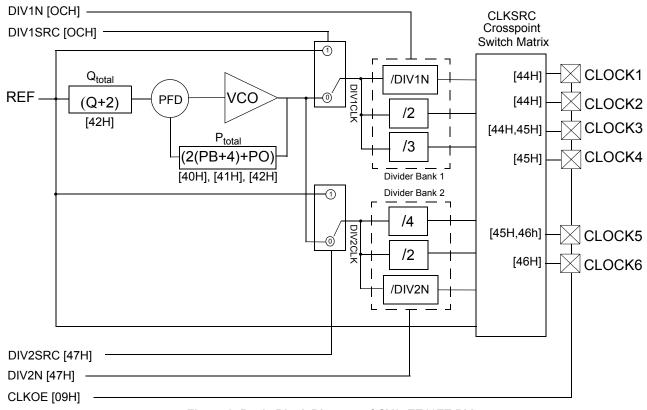

The CY27EE16ZE is an extremely flexible clock generator with four basic variables that can be used to determine the final output frequency. They are the input reference frequency (REF), the internally calculated P and Q dividers, and the post divider, which can be a fixed or calculated value. There are three basic formulas for determining the final output frequency of a CY27EE16ZE-based design. Any one of these three formulas may be used:

## CLK = ((REF \* P)/Q)/Post Divider

## CLK = REF/Post Divider

#### CLK = REF

The basic PLL block diagram is shown in *Figure 2*. Each of the six clock outputs on the CY27EE16ZE has a total of seven output options available to it. There are six post divider options available: /2 (two of these), /3, /4, /DIV1N and /DIV2N. DIV1N and DIV2N are independently calculated and are applied to individual output groups. The post divider options can be applied to the calculated VCO frequency ((REF\*P)/Q) or to the reference frequency directly.

In addition to the six post divider output options, the seventh option bypasses the PLL and passes the reference frequency directly to the crosspoint switch matrix.

Figure 2. Basic Block Diagram of CY27EE16ZE PLL

## **Reference Frequency (REF)**

The reference frequency can be a crystal or a driven frequency. For crystals, the frequency range must be between 8 MHz and 30 MHz. For a driven frequency, the frequency range must be between 1 MHz and 167 MHz (Commercial Temp.) or 150 MHz (Industrial Temp.).

## Using a Crystal as the Reference Input

The input crystal oscillator of the CY27EE16ZE is an important feature because of the flexibility it allows the user in selecting a crystal as a reference frequency source. The input oscillator has programmable gain, allowing for maximum compatibility with a reference crystal, regardless of manufacturer, process, performance and quality.

#### Programmable Crystal Input Oscillator Gain Settings

The Input crystal oscillator gain (XDRV) is controlled by two bits in register 12H, and are set according to *Table 2*. The parameters controlling the gain are the crystal frequency, the internal crystal parasitic resistance (ESR, available from the manufacturer), and the CapLoad setting during crystal start-up.

Bits 3 and 4 of register 12H control the input crystal oscillator gain setting. Bit 4 is the MSB of the setting, and bit 3 is the LSB. The setting is programmed according to *Table 2*.

All other bits in the register are reserved and should be programmed LOW. See *Table 3* for bit locations and values.

|               | Calculated CapLoad Value | 00H – 20H   |             | 20H ·       | - 30H       | 30H – 40H   |             |

|---------------|--------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

|               | Crystal ESR              | <b>30</b> Ω | <b>60</b> Ω | <b>30</b> Ω | <b>60</b> Ω | <b>30</b> Ω | <b>60</b> Ω |

| Crystal Input | 8–15 MHz                 | 00          | 01          | 01          | 10          | 01          | 10          |

| Frequency     | 15–20 MHz                | 01          | 10          | 01          | 10          | 10          | 10          |

|               | 20–25 MHz                | 01          | 10          | 10          | 10          | 10          | 11          |

|               | 25–30 MHz                | 10          | 10          | 10          | 11          | 11          | N/A         |

#### Table 3. Register Map for Input Crystal Oscillator Gain Setting

| Address | D7                           | D6                           | D5                     | D4      | D3      | D2 | D1 | D0 |

|---------|------------------------------|------------------------------|------------------------|---------|---------|----|----|----|

| 12H     | FTAAddrSrc(1)<br>default = 0 | FTAAddrSrc(0)<br>default = 0 | XCapSrc<br>default = 1 | XDRV(1) | XDRV(0) | 0  | 0  | 0  |

Document #: 38-07440 Rev. \*C

Page 5 of 17

#### Table 4. Programmable External Reference Input Oscillator Drive Settings

| Reference Frequency | 1 – 25 MHz | 25 – 50 MHz | 50 – 90 MHz | 90 – 167 MHz |

|---------------------|------------|-------------|-------------|--------------|

| Drive Setting       | 00         | 01          | 10          | 11           |

#### Using an External Clock as the Reference Input

The CY27EE16ZE can also accept an external clock as reference, with speeds up to 167 MHz (or 150 MHz at Industrial Temp.). With an external clock, the XDRV (register 12H) bits must be set according to *Table 4*.

#### Input Load Capacitors

Input load capacitors allow the user to set the load capacitance of the CY27EE16ZE to match the input load capacitance from a crystal. The value of the input load capacitors is determined by 8 bits in a programmable register [13H]. The proper CapLoad register setting is determined by the formula:

#### $CapLoad = (C_{L} - C_{BRD} - C_{CHIP})/0.09375 \text{ pF}$

where:

- C<sub>L</sub> = specified load capacitance of your crystal.

- C<sub>BRD</sub> = the total board capacitance, due to external capacitors and board trace capacitance. In CyClocksRT, this value defaults to 2 pF.

- C<sub>CHIP</sub> = 6 pF.

- 0.09375 pF = the step resolution available due to the 8-bit register.

In CyclocksRT, only the crystal capacitance ( $C_L$ ) is specified. C<sub>CHIP</sub> is set to 6 pF, and C<sub>BRD</sub> defaults to 2 pF. If your board capacitance is higher or lower than 2 pF, the formula above can be used to calculate a new CapLoad value and programmed into register 13H.

In CyClocksRT, enter the crystal capacitance (C<sub>L</sub>). The value of CapLoad will be determined automatically and programmed into the CY27EE16ZE. Through the SDAT and SCLK pins, the value can be adjusted up or down if your board capacitance is greater or less than 2 pF. For an external clock source, CapLoad defaults to 1. See *Table 5* for CapLoad bit locations and values.

The input load capacitors are placed on the CY27EE16ZE die to reduce external component cost. These capacitors are true parallel-plate capacitors, designed to reduce the frequency shift that occurs when non-linear load capacitance is affected by load, bias, supply and temperature changes.

## DCXO/VCXO

The default clock configuration of the CY27EE16ZE has 256 stored values that are used to adjust the frequency of the crystal oscillator, by changing the load capacitance. In order to use these stored values, the clock configuration must be reprogrammed to enable the DCXO or VCXO feature.

#### To Configure for DCXO Operation

- 1. FTAAddrScr[1:0], Register 12H[7:6] = 00 (default configuration = 00)

- 2. XCapSrc, Register 12H[5] = 0

- 3. XDRV[1:0], Register 12H[4:3] = (see Table 2)

- 4. ADCEnable, Register 14H[7] = 0

- 5. ADCBypCnt, Register 14H[6] = 0

- 6. ADCCnt[2:0], Register 14H[5:3] = 000

- 7. ADCFilt[1:0], Register 14H[2:1] = 00

Once the clock configuration block is programmed for DCXO operation, the SPI may be used to dynamically change the capacitor load value on the crystal. A change in crystal load capacitance corresponds with a change in the reference frequency. Thus, the crystal oscillator frequency can be adjusted from –150 ppm of the nominal frequency value to +150 ppm of the nominal frequency value. "Nominal frequency – 150 ppm" is achieved by writing 00000000 into the CapLoad register, and "nominal frequency + 150 ppm" is achieved by writing 1111111 into the CapLoad register

#### **Configure for VCXO Operation**

To configure the VCXO for analog control clock configuration registers must be written to as follows:

- 1. FTAAddrSrc[1:0], Register 12H[7:6] = 01

- 2. XCapSrc, Register 12H[5] = 0

- 3. XDRV[1:0], Register 12H[4:3] = (see Table 2)

- 4. ADCEnable, Register 14H[7] = 1

- 5. ADCBypCnt, Register 14H[6] = 0

- 6. ADCCnt[2:0], = 001

- 7. ADCFilt[1:0], Register 14H[2:1]= 10

- 8. WPSrc, Register 11H[3] = 1

#### Table 5. Input Load Capacitor Register Bit Setting

| Γ | Address | D7         | D6         | D5         | D4         | D3         | D2         | D1         | D0         |

|---|---------|------------|------------|------------|------------|------------|------------|------------|------------|

|   | 13H     | CapLoad(7) | CapLoad(6) | CapLoad(5) | CapLoad(4) | CapLoad(3) | CapLoad(2) | CapLoad(1) | CapLoad(0) |

# Power-down Mode (PDM) and Output Enable (OE) Registers for Pin 10

In the default clock configuration, pin 10 is configured as OE, and not configured as PDM. As such, the Power-down mode is not available unless the clock core is modified.

## To Configure for PDM

To configure pin 10 for PDM, use the SPI to write the following:

- 1. PDMEnable, Register 10H[2] = 1

- 2. PDMPadSel[1:0], Register 10H[1:0] =10

- 3. OESrc, Register 10H[7] = 1 (to redirect control of output enable to memory, register 40H[7:6], and thereby enable both divider banks).

Now, when the PDM signal (an active LOW signal) is asserted, all of the clock components are shut down and the part enters a low-power state.

The serial port and EE blocks will still be available. These circuits automatically go into a low-power state when not being used, but will draw power when active.

**Note:** For default factory programmed devices, Register 40H[7:6] may be programmed to 00. In this case Register 40H[7:6] must be programmed to 11 in order for clock outputs to be enabled.

#### To Configure for OE

To reconfigure pin 10 as OE again, so that pin 10 controls enable/disable of the output divider bank, use the SPI to write the following:

- 1. OESrc, Register 10H[7] = 0

- 2. OE0PadSel[1:0], Register 10H[6:5] =10

- 3. OE1PadSel[1:0], Register 10H[4:3] =10

- 4. PDMEnable, Register 10H[2] = 0

- 5. Mem WP, Register 11H[4] = 0

- 6. WPSrc, Register 11H[3] = 1

## Write Protect (WP) Registers

To reconfigure pin 17 as WP, to control enable/disable of write protection, use the SPI to write the following:

WPSrc, Register 11H[3] = 0

WPPadSel[2:0], Register 11H[2:0] = 100

Table 6. Q Counter Register Definition

When active (WP = 1), WP prevents the control logic for the EE from initiating a erase/program cycle for any of the EEPROM blocks (16-Kbit scratchpad and clock configuration block). All serial shifting works as normal.

## PLL Frequency, Q Counter

The first counter is known as the Q counter. The Q counter divides REF by its calculated value. Q is a 7 bit divider with a maximum value of 127 and minimum value of 0. The primary value of Q is determined by 7 bits in register 42H (6..0), but 2 is added to this register value to achieve the total Q, or  $Q_{total}$ .  $Q_{total}$  is defined by the formula:

#### $Q_{total} = Q + 2.$

The minimum value of  $Q_{total}$  is 2. The maximum value of  $Q_{total}$  is 129. Register 42H is defined in *Table 6*.

Stable operation of the CY27EE16ZE cannot be guaranteed if REF/Q<sub>total</sub> falls below 250 kHz. Q<sub>total</sub> bit locations and values are defined in *Table 6*.

## **PLL Frequency, P Counter**

The next counter definition is the P (product) counter. The P counter is multiplied with the (REF/Q<sub>total</sub>) value to achieve the VCO frequency. The product counter, defined as P<sub>total</sub>, is made up of two internal variables, PB and PO. The formula for calculating P<sub>total</sub> is:

## $\mathsf{P}_{\text{total}} = (2(\mathsf{PB} + 4) + \mathsf{PO})$

PB is a 10-bit variable, defined by registers 40H(1:0) and 41H(7:0). The 2 LSBs of register 40H are the two MSBs of variable PB. Bits 4..2 of register 40H are used to determine the charge pump settings (see section, "Charge Pump Settings [40H(2..0)]", page 8"). The 3 MSBs of register 40H are preset and reserved and cannot be changed.

PO is a single bit variable, defined in register 42H(7). This allows for odd numbers in  $P_{total}$ .

The remaining 7 bits of 42H are used to define the Q counter, as shown in *Table 6*.

The minimum value of P<sub>total</sub> is 8. The maximum value of P<sub>total</sub> is 2055. To achieve the minimum value of P<sub>total</sub>, PB and PO should both be programmed to 0. To achieve the maximum value of P<sub>total</sub>, PB should be programmed to 1023, and PO should be programmed to 1.

Stable operation of the CY27EE16ZE cannot be guaranteed if the value of ( $P_{total}^{*}(REF/Q_{total})$ ) is above 400 MHz or below 100 MHz. Registers 40H, 41H and 42H are defined in *Table 7*.

| Register | D7 | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|----------|----|------|------|------|------|------|------|------|

| 42H      | PO | Q(6) | Q(5) | Q(4) | Q(3) | Q(2) | Q(1) | Q(0) |

#### Table 7. P Counter Register Definition

| Address | D7    | D6    | D5    | D4      | D3      | D2      | D1    | D0    |

|---------|-------|-------|-------|---------|---------|---------|-------|-------|

| 40H     | 1     | 1     | 0     | Pump(2) | Pump(1) | Pump(0) | PB(9) | PB(8) |

| 41H     | PB(7) | PB(6) | PB(5) | PB(4)   | PB(3)   | PB(2)   | PB(1) | PB(0) |

| 42H     | PO    | Q(6)  | Q(5)  | Q(4)    | Q(3)    | Q(2)    | Q(1)  | Q(0)  |

#### Table 8. PLL Post Divider Options

| Address | D7      | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

|---------|---------|----------|----------|----------|----------|----------|----------|----------|

| OCH     | DIV1SRC | DIV1N(6) | DIV1N(5) | DIV1N(4) | DIV1N(3) | DIV1N(2) | DIV1N(1) | DIV1N(0) |

| 47H     | DIV2SRC | DIV2N(6) | DIV2N(5) | DIV2N(4) | DIV2N(3) | DIV2N(2) | DIV2N(1) | DIV2N(0) |

## **PLL Post Divider Options**

The output of the VCO is routed through two independent muxes, then to two divider banks to determine the final clock output frequency. The mux determines if the clock signal feeding into the divider banks is the calculated VCO frequency or REF. There are 2 select muxes (DIV1SRC and DIV2SRC) and 2 divider banks (Divider Bank 1 and Divider Bank 2) used to determine this clock signal. The clock signals passing through DIV1SRC and DIV2SRC are referred to as DIV1CLK and DIV2CLK, respectively.

The divider banks have 4 unique divider options available: /2, /3, /4, and /DIVxN. DIVxN is a variable that can be independently programmed (DIV1N and DIV2N) for each of the 2 divider banks. The minimum value of DIVxN is 4. The maximum value of DIVxN is 127. A value of DIVxN below 4 is not guaranteed to work properly.

DIV1SRC is a single bit variable, controlled by register OCH. The remaining 7 bits of register OCH determine the value of post divider DIV1N.

DIV2SRC is a single bit variable, controlled by register 47H. The remaining 7 bits of register 47H determine the value of post divider DIV2N.

Register OCH and 47H are defined in Table 8.

## Charge Pump Settings [40H(2..0)]

The correct pump setting is important for PLL stability. Charge pump settings are controlled by bits (4..2) of register 40H, and

#### Table 10.Register 40H Change Pump Bit Settings

are dependent on internal variable PB (see section "[00H to 08H] – Reserved [0AH to 08H] – Reserved [0DH to 0FH] –Reserved [15H to 3FH] –Reserved [43H] –Reserved [48H to FFH] –Reserved", page 9). *Table 9* summarizes the proper charge pump settings, based on P<sub>total</sub>. See *Table 10*, "Register 40H Change Pump Bit Settings", page 8, for register 40H bit locations.

Although using *Table 10* will guarantee stability, it is recommended to use the Print Preview function in CyberClocks<sup>™</sup> to determine the ideal charge pump settings for optimal jitter performance.

PLL stability cannot be guaranteed for  $P_{total}$  values below 16 and above 1023. If  $P_{total}$  values above 1023 are needed, use CyberClocks to determine the best charge pump setting.

**Table 9. Charge Pump Settings**

| Charge Pump Setting<br>– Pump(20) | Calculated P <sub>total</sub>        |

|-----------------------------------|--------------------------------------|

| 000                               | 16 – 44                              |

| 001                               | 45 – 479                             |

| 010                               | 480 – 639                            |

| 011                               | 640 – 799                            |

| 100                               | 800 – 1023                           |

| 101, 110, 111                     | Do Not Use – device will be unstable |

| Address | D7 | D6 | D5 | D4      | D3      | D2      | D1    | D0    |

|---------|----|----|----|---------|---------|---------|-------|-------|

| 40H     | 1  | 1  | 0  | Pump(2) | Pump(1) | Pump(0) | PB(9) | PB(8) |

## **Clock Output Settings**

#### CLKSRC - Clock Output Crosspoint Switch Matrix [44H(7..0)], [45H(7..0)], [46H(7..0)]

Every clock output can be defined to come from one of seven unique frequency sources. The CLKSRC(2..0) crosspoint switch matrix defines which source is attached to each individual clock output. CLKSRC(2..0) is set in Registers 44H, 45H, and 46H. The remainder of registers 45H(3:1) and 46H(2:0) must be written with the values stated in the register table when writing register values 45H(7:4), 45H(0), and 46H(7:3).

When DIV1N is divisible by 4, then CLKSRC(0,1,0) is guaranteed to be rising edge phase-aligned with CLKSRC(0,0,1). When DIV1N is 6, then CLKSRC(0,1,1) is guaranteed to be rising edge phase-aligned with CLKSRC(0,0,1). When DIV2N is divisible by 4, then CLKSRC(1,0,1) is guaranteed to be rising edge phase-aligned with CLKSRC(1,0,0). When DIV2N is divisible by 8, then CLKSRC(1,1,0) is guaranteed to be rising edge phase-aligned with CLKSRC(1,0,0).

#### CLKOE - Clock Output Enable Control [09H(7..0)]

Each clock output has its own output enable, CLKOE, controlled by register 09H(7..0). To enable an output, set the corresponding CLKOE bit to 1. CLKOE settings are in *Table 13*.

#### Test, Reserved, and Blank Registers

Writing to any of the following registers will cause the part to exhibit abnormal behavior:

[00H to 08H] – Reserved [0AH to 0BH] – Reserved [0DH to 0FH] –Reserved [15H to 3FH] –Reserved [43H] –Reserved [48H to FFH] –Reserved

#### Table 11.Clock Output Settings – Clock Source CLKSRC[2:0]

| CLKSRC2 | CLKSRC1 | CLKSRC0 | Definition and Notes                                                                                                                             |

|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | 0       | Reference Input                                                                                                                                  |

| 0       | 0       | 1       | DIV1CLK/DIV1N. DIV1N is defined by register [OCH]. Allowable values for DIV1N are 4 to 127. If Divider Bank 1 is not being used, set DIV1N to 8  |

| 0       | 1       | 0       | DIV1CLK/2. Fixed /2 divider option. If this option is used, DIV1N must be divisible by 4.                                                        |

| 0       | 1       | 1       | DIV1CLK/3. Fixed /3 divider option. If this option is used, set DIV1N to 6.                                                                      |

| 1       | 0       | 0       | DIV2CLK/DIV2N. DIV2N is defined by Register [47H]. Allowable values for DIV2N are 4 to 127. If Divider Bank 2 is not being used, set DIV2N to 8. |

| 1       | 0       | 1       | DIV2CLK/2. Fixed /2 divider option. If this option is used, DIV2N must be divisible by 4.                                                        |

| 1       | 1       | 0       | DIV2CLK/4. Fixed /4 divider option. If this option is used, DIV2N must be divisible by 8.                                                        |

| 1       | 1       | 1       | Reserved – Do not use                                                                                                                            |

#### Table 12.CLKSRC Registers

| Address | D7                    | D6                    | D5                    | D4                    | D3                    | D2                    | D1                    | D0                    |

|---------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 44H     | CLKSRC2<br>for CLOCK1 | CLKSRC1<br>for CLOCK1 | CLKSRC0<br>for CLOCK1 | CLKSRC2<br>for CLOCK2 | CLKSRC1<br>for CLOCK2 | CLKSRC0<br>for CLOCK2 | CLKSRC2<br>for CLOCK3 | CLKSRC1<br>for CLOCK3 |

| 45H     | CLKSRC0<br>for CLOCK3 | CLKSRC2<br>for CLOCK4 |                       | CLKSRC0<br>for CLOCK4 | 1                     | 1                     | 1                     | CLKSRC2<br>for CLOCK5 |

| 46H     | CLKSRC1<br>for CLOCK5 |                       | CLKSRC2<br>for CLOCK6 | CLKSRC1<br>for CLOCK6 | CLKSRC0<br>for CLOCK6 | 1                     | 1                     | 1                     |

#### Table 13.CLKOE Bit Setting

| Address | D7 | D6                  | D5                  | D4 | D3                  | D2                  | D1                  |                     |

|---------|----|---------------------|---------------------|----|---------------------|---------------------|---------------------|---------------------|

| 09H     | 0  | CLKOE for<br>CLOCK6 | CLKOE for<br>CLOCK5 | 0  | CLKOE for<br>CLOCK4 | CLKOE for<br>CLOCK3 | CLKOE for<br>CLOCK2 | CLKOE for<br>CLOCK1 |

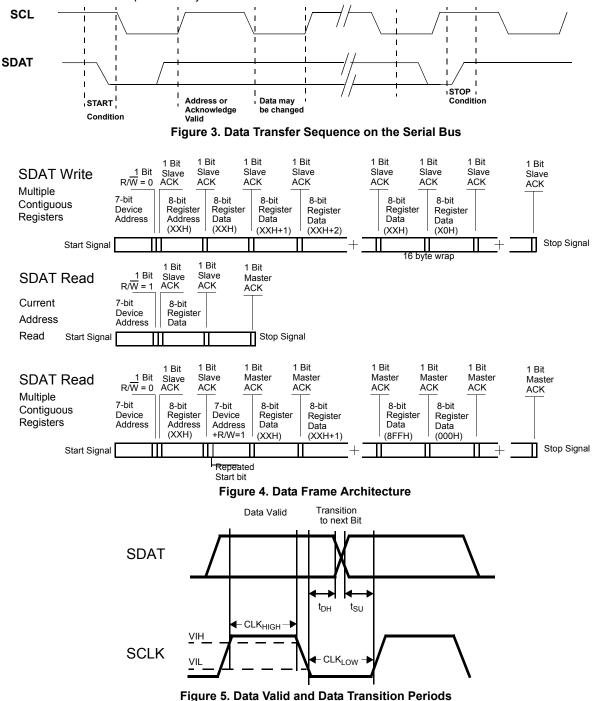

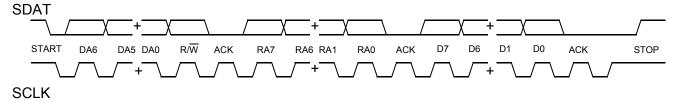

# Serial Programming Interface (SPI) Protocol and Timing

The CY27EE16ZE utilizes a 2-serial-wire interface SDAT and SCLK that operates up to 400 kbits/sec in Read or Write mode. The basic Write serial format is as follows:

Start Bit; 7-bit Device Address (DA); R/W Bit; Slave Clock Acknowledge (ACK); 8-bit Memory Address (MA); ACK; 8-bit Data; ACK; 8-bit Data in MA+1 if desired; ACK; 8-bit Data in MA+2; ACK; etc. until STOP Bit. The basic serial format is illustrated in *Figure 4*.

#### Data Valid

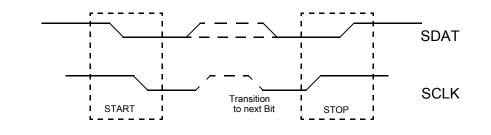

Data is valid when the clock is HIGH, and may only be transitioned when the clock is LOW as illustrated in *Figure 5*.

#### **Data Frame**

Every new data frame is indicated by a start and stop sequence, as illustrated in *Figure 6*.

Start Sequence – Start Frame is indicated by SDAT going LOW when SCLK is HIGH. Every time a start signal is given, the next 8-bit data must be the device address (7 bits) and a R/W bit, followed by register address (8 bits) and register data (8 bits).

Stop Sequence – Stop Frame is indicated by SDAT going HIGH when SCLK is HIGH. A Stop Frame frees the bus for writing to another part on the same bus or writing to another random register address.

#### Acknowledge Pulse

During Write Mode the CY27EE16ZE will respond with an Acknowledge pulse after every 8 bits. This is accomplished by pulling the SDAT line LOW during the N\*9<sup>th</sup> clock cycle as illustrated in *Figure 7*. (N = the number of bytes transmitted). During Read Mode the acknowledge pulse after the data packet is sent is generated by the master.

## **Device Addressing**

The first four bits of the device address word for the eight EEPROM scratchpad blocks are 1000. The 5th, 6th, and 7th bits are the address bits (A2, A1, A0 respectively) for the slices of 2K EEPROM. The first seven bits of the device address word for the clock configuration EEPROM block are 1101000. The first seven bits of the device address word for the clock configuration SRAM block are 1101001. The final bit of the address specifies the operation (HIGH/1 = Read, LOW/0 = Write)

## Write Operations

#### Writing Individual Bytes

A valid write operation must have a full 8-bit word address after the device address word, which is followed by an acknowledgment bit from the EEPROM (ack = 0/LOW). The next 8 bits must contain the data word intended for storage. After the data word is received, the EEPROM responds with another acknowledge bit (ack = 0/LOW), and the device that is addressing the EEPROM must end the write sequence with a stop condition. The EEPROM now enters an internal write process transferring the data received to nonvolatile memory. During, and until completion of, this internal write process, the EEPROM will not respond to other commands.

#### Writing Multiple Bytes

The CY27EE16ZE is capable of receiving up to 16 consecutive written bytes. In order to write more than one byte at a time, the device addressing the EEPROM does not end the write sequence with a stop condition. Instead, the device can send up to fifteen more bytes of data to be stored. After each byte, the EEPROM responds with an acknowledge bit, just like after the first byte. The EEPROM will accept data until the acknowledge bit is responded to by the stop condition, at which time it enters the internal write process as described in the section above. When receiving multiple bytes, the CY27EE16ZE internally increments the address of the last 4 bits in the address word. After 16 bytes are written, that incrementing brings it back to the first word that was written. If more than 16 bytes are written, the CY27EE16ZE will overwrite the first bytes written.

## **Read Operations**

Read operations are initiated the same way as Write operations except that the R/W bit of the slave address is set to '1' (HIGH). There are three basic read operations: current address read, random read, and sequential read.

#### Current Address Read

The CY27EE16ZE has an onboard address counter that retains 1 more than the address of the last word access. If the last word written or read was word 'n,' then a current address read operation would return the value stored in location 'n+1'. When the CY27EE16ZE receives the slave address with the R/W bit set to a '1,' the CY27EE16ZE issues an acknowledge and transmits the 8-bit word. The master device does not acknowledge the transfer, but does generate a STOP condition, which causes the CY27EE16ZE to stop transmission.

#### Random Read

Through random read operations, the master may access any memory location. To perform this type of read operation, first the word address must be set. This is accomplished by sending the address to the CY27EE16ZE as part of a write operation. After the word address is sent, the master generates a START condition following the acknowledge. This terminates the write operation before any data is stored in the address, but not before the internal address pointer is set. Next the master reissues the control byte with the R/W byte set to '1.' The CY27EE16ZE then issues an acknowledge and transmits the 8-bit word. The master device does not acknowledge the transfer, but does generate a STOP condition which causes the CY27EE16ZE to stop transmission.

#### **Sequential Read**

Sequential read operations follow the same process as random reads except that the master issues an acknowledge instead of a STOP condition after transmission of the first 8-bit data word. This action results in an incrementing of the internal address pointer, and subsequently output of the next 8-bit data word. By continuing to issue acknowledges instead of STOP conditions, the master may serially read the entire contents of the 16-kbit EEPROM scratchpad memory. When the internal address pointer points to the FFH word of a EEPROM block, after the next increment, the pointer will point to the 00H word of the next block. After incrementing to the FFH word of the eighth block, the next increment will point the pointer to the 00H word of the 1st EEPROM block. Similarly, sequential reads within either the EEPROM or SRAM clock configuration blocks will wrap within the block to the first word of the same block after reaching the end of either block.

## Serial Programming Interface Timing

Figure 6. Start and Stop Frame

Figure 7. Frame Format (Device Address, R/W, Register Address, Register Data)

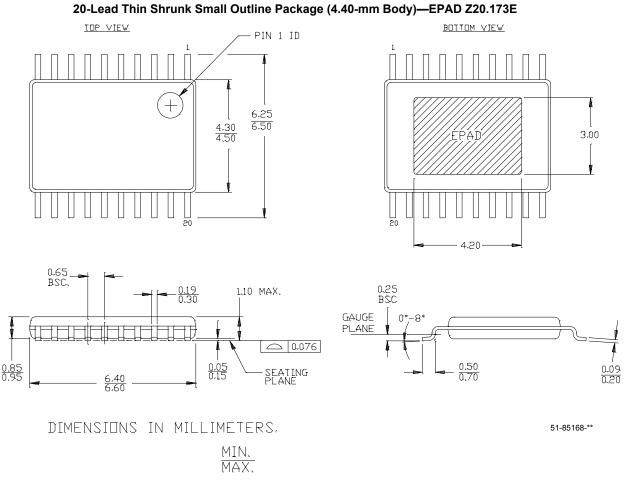

## Thermal Land Pad on PWB: Layout Requirement for 20-lead <u>Exposed Pad TSSOP</u>

In order to achieve power dissipation and maintain junction temperature within specified limits there must be an exposed landing pad placed under the package, and the exposed pad on the bottom of the package must be soldered to this landing pad. This is typically achieved by placing a dense array of thermal via that connects the landing pad to the ground plane. In order to meet the power dissipation specification of 40 °C/W, Amkor soldered the exposed pad to a thermal land pad, and placed thermal via on a 1.2-mm pitch (x and y) in the thermal land pad. For more information about this package, see, "Application Notes for Surface Mount Assembly of Amkor's Thermally/Electrically Enhanced Leadframe Based Packages." Amkor Technology, December 2001.

| Parameter           | Description                        | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------|------|------|------|------|

| CRYSTALLoad         | Load Capacitance                   |      | 14   |      | pF   |

| C0/C1               |                                    |      |      | 240  |      |

| ESR                 |                                    |      |      | 35   | W    |

| To                  | Operating Temperature (Commercial) | 0    |      | 70   | °C   |

| To                  | Operating Temperature (Industrial) | -40  |      | 85   | °C   |

| Acc <sub>init</sub> | Initial Accuracy                   |      | ±30  |      | ppm  |

| Stability           | Temperature plus Aging Stability   |      | ±80  |      | ppm  |

#### Table 14.Pullable Crystal Specifications

## **Absolute Maximum Conditions**

| Parameter       | Description                                 | Min.                  | Max.                  | Unit   |

|-----------------|---------------------------------------------|-----------------------|-----------------------|--------|

| V <sub>DD</sub> | Supply Voltage                              | -0.5                  | 7.0                   | V      |

| T <sub>S</sub>  | Storage Temperature                         | -65                   | 125                   | °C     |

| TJ              | Junction Temperature                        | -40                   | 100                   | °C     |

|                 | Logic Inputs                                | V <sub>SS</sub> – 0.5 | V <sub>DD</sub> + 0.5 | V      |

|                 | I <sup>2</sup> C interface (SDAT and SCL)   | -0.5                  | 5.5                   | V      |

|                 | Digital Outputs referred to V <sub>DD</sub> | $V_{SS} - 0.5$        | V <sub>DD</sub> + 0.5 | V      |

|                 | Electro-Static Discharge                    |                       | 2000                  | V      |

| VCXO            | Analog Input                                | -0.5                  | V <sub>DD</sub> + 0.5 | V      |

|                 | Endurance (@ 25°C)                          |                       | 1,000,000 (100k/page) | writes |

|                 | Data retention                              | 10                    |                       | yrs    |

## **Recommended Operating Conditions**

| Parameter         | Description                                                                                    | Min.  | Тур.     | Max.  | Unit |

|-------------------|------------------------------------------------------------------------------------------------|-------|----------|-------|------|

| V <sub>DD</sub>   | Operating Voltage                                                                              | 3.135 | 3.3      | 3.465 | V    |

| V <sub>DDL</sub>  | Operating Voltage                                                                              | 2.375 | 2.5, 3.3 | 3.465 | V    |

| T <sub>A</sub>    | Ambient Temperature, Industrial grade                                                          | -40   |          | 85    | °C   |

| T <sub>A</sub>    | Ambient Temperature, Commercial grade                                                          | 0     |          | 70    | °C   |

| C <sub>LOAD</sub> | Max. Load Capacitance                                                                          |       |          | 15    | pF   |

| t <sub>PU</sub>   | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05  |          | 500   | ms   |

## **DC Electrical Specifications**

| Parameter         | Name                                        | Description                                   | Min.                  | Тур. | Max.                  | Unit |

|-------------------|---------------------------------------------|-----------------------------------------------|-----------------------|------|-----------------------|------|

| I <sub>OH</sub>   | Output High Current <sup>[2]</sup>          | $V_{OH} = V_{DD} - 0.5, V_{DD} = 3.3V$        | 12                    |      | 24                    | mA   |

| I <sub>OL</sub>   | Output Low Current <sup>[2]</sup>           | V <sub>OL</sub> = 0.5, V <sub>DD</sub> = 3.3V | 12                    |      | 24                    | mA   |

| V <sub>IH</sub>   | Input High Voltage                          | CMOS levels                                   | 0.7 * V <sub>DD</sub> |      |                       | V    |

| V <sub>IL</sub>   | Input Low Voltage                           | CMOS levels                                   |                       |      | 0.3 * V <sub>DD</sub> | V    |

| C <sub>IN</sub>   | Input Capacitance <sup>[2, 3]</sup>         |                                               |                       |      | 7                     | pF   |

| I <sub>IZ</sub>   | Input Leakage Current                       | Except XTAL pins                              |                       |      | 10                    | μA   |

| $f_{\Delta XO}$   | VCXO Pullability Range <sup>[2]</sup>       |                                               | <u>+</u> 150          |      |                       | ppm  |

| V <sub>VCXO</sub> | VCXO Input Range <sup>[2]</sup>             |                                               | 0                     |      | V <sub>DD</sub>       | V    |

| f <sub>VBW</sub>  | VCXO Input Bandwidth <sup>[2]</sup>         |                                               | DC                    |      | 200                   | kHz  |

| I <sub>VDD</sub>  | Supply Current                              |                                               |                       | 45   |                       | mA   |

| I <sub>SB</sub>   | Supply Current - Power<br>Down Mode Enabled | Current drawn while part is in standby.       |                       | 5    | 40                    | μA   |

## DC Electrical Specifications – 2.5V Outputs

| Parameter          | Name                                  | Description                                                            | Min. | Тур. | Max. | Unit |

|--------------------|---------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| I <sub>OH2.5</sub> | Output High Current <sup>[2, 4]</sup> | $V_{OH} = V_{DD} - 0.5, V_{DD} = 3.3 V, V_{DDL} = 2.5V$                | 12   |      | 24   | mA   |

| I <sub>OL2.5</sub> | Output Low Current <sup>[2, 4]</sup>  | V <sub>OL</sub> = 0.5, V <sub>DD</sub> = 3.3 V, V <sub>DDL</sub> =2.5V | 12   |      | 24   | mA   |

Notes:

Guaranteed by design, not 100% tested.

Crystal must meet *Table 14* specifications.

V<sub>DD</sub> is only specified and characterized at 3.3V <u>+</u> 5%. V<sub>DDL</sub> may be powered at any value between 3.465 and 2.375.

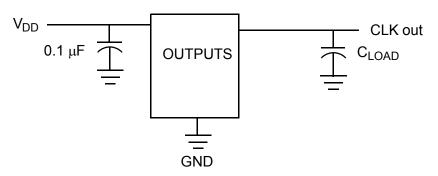

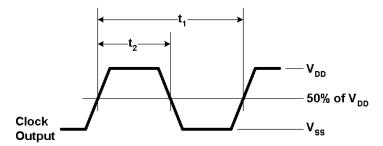

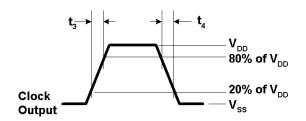

## AC Electrical Specifications ( $V_{DD}$ = 3.3V)

| Parameter <sup>[5]</sup>  | Name                                                                | Description                                                                                                             | Min.     | Тур.              | Max.     | Unit |

|---------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|-------------------|----------|------|

| DC                        | Clock Output Duty Cycle                                             | f <sub>OUT</sub> < 150 MHz<br>f <sub>OUT</sub> > 150 MHz, or f <sub>OUT</sub> = f <sub>REF</sub><br>See <i>Figure 8</i> | 45<br>40 | 50<br>50          | 55<br>60 | %    |

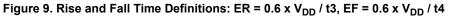

| ER <sub>O</sub>           | Rising Edge Rate                                                    | Output Clock Edge Rate, Measured from 20% to 80% of $V_{DD,} C_{LOAD}$ = 15 pF See <i>Figure 9</i> .                    | 0.8      | 1.4               |          | V/ns |

| EFO                       | Falling Edge Rate                                                   | Output Clock Edge Rate, Measured from 80% to 20% of $V_{DD,} C_{LOAD}$ = 15 pF See <i>Figure 9</i> .                    | 0.8      | 1.4               |          | V/ns |

| t <sub>5</sub>            | Output to Output Skew                                               | For related clock outputs                                                                                               |          |                   | 250      | ps   |

| t <sub>9</sub>            | Clock Jitter                                                        | Maximum absolute jitter (EEPROM quiet)<br>(during EEPROM reads)<br>(during EEPROM writes)                               |          | 250<br>300<br>350 |          | ps   |

| t <sub>10</sub>           | PLL Lock Time                                                       |                                                                                                                         |          |                   | 60       | ms   |

| t <sub>VDDramp</sub>      | Power Supply Ramp                                                   | Ramp time from 1.5V to 2.5V <sup>[6]</sup>                                                                              |          |                   | 15       | ms   |

| t <sub>VDDpowerdown</sub> | Power Supply Power Down after Write                                 | Wait time after a write to EEPROM is initiated by the stop bit until $V_{DD}$ fails below 2.5V                          | 20       |                   |          | ms   |

| Memory Section            | on Specifications                                                   |                                                                                                                         |          | •                 | •        |      |

| F <sub>SCL</sub>          | SCL input frequency                                                 |                                                                                                                         |          |                   | 400      | kHz  |

| tL                        | Clock Pulse Low                                                     | CLK <sub>LOW</sub> , 20–80% of V <sub>DD</sub>                                                                          |          |                   | 1.2      | μS   |

| t <sub>H</sub>            | Clock Pulse High                                                    | CLK <sub>HIGH</sub> , 80–20% of V <sub>DD</sub>                                                                         | 0.6      |                   |          | μS   |

| t <sub>SP</sub>           | Noise Suppression Time                                              | Square noise spike on input                                                                                             |          |                   | 50       | ns   |

| t <sub>AA</sub>           | Clock Low to Data Out Valid                                         |                                                                                                                         | 0.1      |                   | 0.9      | μS   |

| t <sub>BUFF</sub>         | Time the bus must be free<br>before a new transmission<br>may start |                                                                                                                         | 1.2      |                   |          | μs   |

| t <sub>HDSTART</sub>      | Start Hold Time                                                     |                                                                                                                         | 0.6      |                   |          | μS   |

| t <sub>SUSTART</sub>      | Start Set-up Time                                                   |                                                                                                                         | 0.6      |                   |          | μS   |

| t <sub>DH</sub>           | Data in Hold Time                                                   |                                                                                                                         | 0        |                   |          | ms   |

| t <sub>SU</sub>           | Data in Set-up time                                                 |                                                                                                                         | 100      |                   |          | ns   |

| t <sub>RI</sub>           | Inputs rise time                                                    |                                                                                                                         |          |                   | 300      | ns   |

| t <sub>FI</sub>           | Inputs fall time                                                    |                                                                                                                         |          |                   | 300      | ns   |

| t <sub>SUSTOP</sub>       | Stop Set-up Time                                                    |                                                                                                                         | 0.6      |                   |          | μS   |

| t <sub>DH</sub>           | Data Out Hold Time                                                  |                                                                                                                         | 50       |                   |          | ns   |

| t <sub>WR</sub>           | Write Cycle Time                                                    |                                                                                                                         |          |                   | 20       | ms   |

## **Test and Measurement Set-up**

Notes:

5. Not 100% tested.

6. The power supply voltage must increase monotonically from 0 to 2.5V; once V<sub>DD</sub> reaches 1.5V, it must ramp to 2.5V within 15 ms.

## **Voltage and Timing Definitions**

Figure 8. Duty Cycle Definition; DC = t2/t1

## **Ordering Information**

| Ordering Code                   | Programmed At         | Package Type                             | Operating<br>Range | Operating<br>Voltage |

|---------------------------------|-----------------------|------------------------------------------|--------------------|----------------------|

| CY27EE16ZEC-XXX <sup>[7]</sup>  | Factory<br>Programmed | 20-pin Exposed Pad TSSOP                 | Commercial         | 3.3V                 |

| CY27EE16ZEC-XXXT <sup>[7]</sup> | Factory<br>Programmed | 20-pin Exposed Pad TSSOP – Tape and Reel | Commercial         | 3.3V                 |

| CY27EE16ZEI-XXX <sup>[7]</sup>  | Factory<br>Programmed | 20-pin Exposed Pad TSSOP                 | Industrial         | 3.3V                 |

| CY27EE16ZEI-XXXT <sup>[7]</sup> | Factory<br>Programmed | 20-pin Exposed Pad TSSOP – Tape and Reel | Industrial         | 3.3V                 |

| CY27EE16FZEC                    | Field<br>Programmed   | 20-pin Exposed Pad TSSOP                 | Commercial         | 3.3V                 |

| CY27EE16FZECT                   | Field<br>Programmed   | 20-pin Exposed Pad TSSOP – Tape and Reel | Commercial         | 3.3V                 |

| CY27EE16FZEI                    | Field<br>Programmed   | 20-pin Exposed Pad TSSOP                 | Industrial         | 3.3V                 |

| CY27EE16FZEIT                   | Field<br>Programmed   | 20-pin Exposed Pad TSSOP –Tape and Reel  | Industrial         | 3.3V                 |

| Lead-Free                       | ·                     |                                          |                    |                      |

| CY27EE16FZXEC                   | Field<br>Programmed   | 20-pin Exposed Pad TSSOP                 | Commercial         | 3.3V                 |

| CY27EE16FZXECT                  | Field<br>Programmed   | 20-pin Exposed Pad TSSOP – Tape and Reel | Commercial         | 3.3V                 |

Note:

The CY27EE16ZEC-XXX, CY27EE16ZEC-XXXT, CY27EE16ZEI-XXX and CY27EE16ZEI-XXXT are factory-programmed configurations. Factory programming is available for high-volume design opportunities of 100Ku/year or more in production. For more details, contact your local Cypress field application engineer or Cypress sales representative.

## **Package Drawing and Dimensions**

Purchase of I<sup>2</sup>C components from Cypress, or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. All product and company names mentioned in this document may be the trademarks of their respective holders. CyberClocks and CyClocksRT are trademarks of Cypress Semiconductor Corporation.

#### Document #: 38-07440 Rev. \*C

© Cypress Semiconductor Corporation, 2004. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Downloaded from the component systems applications, index the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

## **Document History Page**

| Document Title: CY27EE16ZE 1 PLL In-System Programmable Clock Generator with Individual 16K EEPROM<br>Document Number: 38-07440 |         |            |                    |                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                                                            | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                  |

| **                                                                                                                              | 116411  | 10/01/02   | CKN                | New Data Sheet                                                                                                                                                                                                                                                                         |

| *A                                                                                                                              | 121903  | 12/14/02   | RBI                | Power-up requirements added to Operating Conditions information                                                                                                                                                                                                                        |

| *В                                                                                                                              | 127953  | 07/01/03   | IJATMP             | Removed PRELIMINARY from all pages<br>Changed 18 bits to 18 kbits on first page<br>Added Note after last paragraph titled "To configure for PDM"<br>Changed Registers under "Write Protect (WP) Registers"<br>Added note to Ordering Information table to clarify factory-programmable |

| *C                                                                                                                              | 305737  | See ECN    | RGL                | Added Lead-Free for Commercial Field programmable Devices                                                                                                                                                                                                                              |