# USB, Audio, and I/O Clock Generator for Intel 82440LX Chipset

#### Features

- USB, Audio, and I/O clock generator for most motherboards using 5<sup>th</sup> or 6<sup>th</sup> generation processors. Can also be used for peripheral systems.

- Two copies of 48 MHz USB clocks

- One copy of 24 MHz I/O clock

- Audio support for 33.8688 MHz, 24.576 MHz, 16.9344 MHz and 12.288 MHz, pin-selectable

- Three copies of Ref. clock @ 14.318 MHz

- 14.318 MHz reference input

- · Ability to three-state all outputs

- Test mode support

- Output duty cycle 45% min. to 55% max.

- Available in 20-pin SSOP packages

- 3.3V operation

- Internal pull-up resistors on S0, S1, and OE inputs

#### **Functional Description**

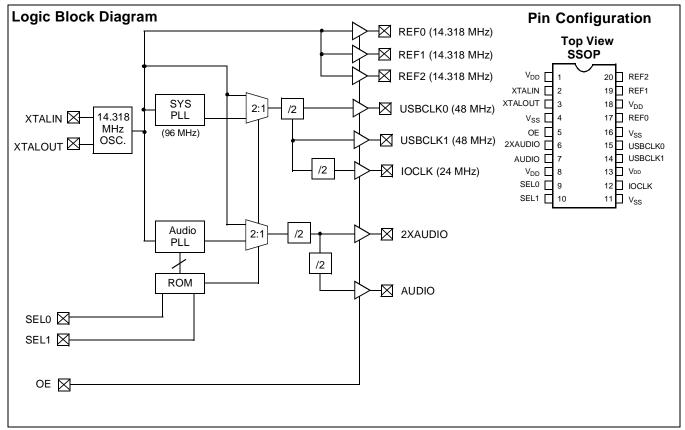

The CY2030 is a peripheral clock generator for most motherboards using fifth and sixth generation processors. The device outputs two copies of a 48 MHz USB clock, as well as one copy of a 24 MHz I/O clock, both of which meet Intel's accuracy, drive, and jitter requirements. Additionally, the part drives two audio clock outputs at 2X and 1X frequencies respectively. These audio clocks support all frequencies that are required by CODECs and FM synthesizers. Finally, the part outputs three reference clocks at 14.318 MHz, which can be used to drive ISA slots, graphics accelerators, and other devices requiring this frequency.

The CY2030 can be used with the CY2275-1 and CY2276-1 (which are CPU, AGP, PCI, and SDRAM clock generators) to provide a complete clock solution for PC motherboards.

The CY2030 accepts a 14.318 MHz reference signal as its input. The CY2030 has two PLLs, one of which generates the audio clocks, and the other generates the Universal Serial Bus (USB) and I/O clocks. The CY2030 runs off a 3.3V supply.

3901 North First Street •

#### **Pin Summary**

| Name                     | Pins | Description                                                                                                    |

|--------------------------|------|----------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>          | 1    | 3.3V voltage supply                                                                                            |

| XTALIN <sup>[1, 2]</sup> | 2    | Reference crystal input, typically 14.318 MHz                                                                  |

| XTALOUT <sup>[1]</sup>   | 3    | Reference crystal feedback                                                                                     |

| V <sub>SS</sub>          | 4    | Ground                                                                                                         |

| OE                       | 5    | Output Enable, active HIGH (internal pull-up resistor to $V_{DD}$ ). Three-states all outputs when driven LOW. |

| 2XAUDIO                  | 6    | 2XAudio clock output, at 33.8688 MHz or 24.576 MHz (See function table below)                                  |

| AUDIO                    | 7    | Audio clock output, at 16.9344 MHz or 12.288 MHz (See function table below)                                    |

| V <sub>DD</sub>          | 8    | 3.3V voltage supply                                                                                            |

| SEL0                     | 9    | Audio clock select input, bit 0 (internal pull-up resistor to $V_{DD}$ )                                       |

| SEL1                     | 10   | Audio clock select input, bit 1 (internal pull-up resistor to $V_{DD}$ )                                       |

| V <sub>SS</sub>          | 11   | Ground                                                                                                         |

| IOCLK                    | 12   | I/O clock output (24.0 MHz)                                                                                    |

| V <sub>DD</sub>          | 13   | 3.3V Voltage supply                                                                                            |

| USBCLK1                  | 14   | USB clock output (48.0 MHz)                                                                                    |

| USBCLK0                  | 15   | USB clock output (48.0 MHz)                                                                                    |

| V <sub>SS</sub>          | 16   | Ground                                                                                                         |

| REF0                     | 17   | REF clock output for ISA slots, drives 45 pF loads (14.318 MHz)                                                |

| V <sub>DD</sub>          | 18   | 3.3V voltage supply                                                                                            |

| REF1                     | 19   | Reference clock output (14.318 MHz)                                                                            |

| REF2                     | 20   | Reference clock output (14.318 MHz)                                                                            |

#### **Function Table**

| OE | SEL1 | SEL0 | XTALIN     | 2XAudio                 | Audio                   | REF [0:2]             | USBCLK [0:1]            | IOCLK                   |

|----|------|------|------------|-------------------------|-------------------------|-----------------------|-------------------------|-------------------------|

| 0  | Х    | Х    | 14.318 MHz | High-Z                  | High-Z                  | High-Z                | High-Z                  | High-Z                  |

| 1  | 0    | 0    | 14.318 MHz | XTALIN/2 <sup>[3]</sup> | XTALIN/4 <sup>[3]</sup> | XTALIN <sup>[3]</sup> | XTALIN/2 <sup>[3]</sup> | XTALIN/4 <sup>[3]</sup> |

| 1  | 0    | 1    | 14.318 MHz | 24.576 MHz              | 12.288 MHz              | 14.318 MHz            | 48 MHz                  | 24 MHz                  |

| 1  | 1    | 0    | 14.318 MHz | 33.8688 MHz             | 16.9344 MHz             | 14.318 MHz            | 48 MHz                  | 24 MHz                  |

| 1  | 1    | 1    | 14.318 MHz | Low                     | Low                     | 14.318 MHz            | 48 MHz                  | 24 MHz                  |

## **Actual Frequency Values**

| Clock   | Target Frequency (MHz) | Actual Frequency (MHz) | PPM |

|---------|------------------------|------------------------|-----|

| USBCLK  | 48.0                   | 48.008                 | 167 |

| IOCLK   | 24.0                   | 24.004                 | 167 |

| 2XAUDIO | 33.8688                | 33.8680                | -24 |

| 2XAUDIO | 24.576                 | 24.5795                | 144 |

| AUDIO   | 16.9344                | 16.9340                | -24 |

| AUDIO   | 12.288                 | 12.2898                | 144 |

| REF     | 14.318                 | 14.318                 | 0   |

Notes:

XTALIN and XTALOUT do not have internal compensation capacitors. Therefore, if an external crystal is used with the device, external compensation capacitors are required to match the load capacitance of the crystal.

If the reference is an external clock, it should be driven on the XTALIN input, and XTALOUT must be left floating.

Intel Test Mode

## CY2030

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Supply Voltage.....-0.5 to +4.6V Input Voltage.....-0.5V to V\_DD+0.5

#### **Operating Conditions**<sup>[4]</sup>

| Storage Temperature (Non-Condensing)65°C to +15                | 0°C |

|----------------------------------------------------------------|-----|

| Max. Soldering Temperature (10 sec) +26                        | 0°C |

| Junction Temperature +15                                       | 0°C |

| Static Discharge Voltage>200<br>(per MIL-STD-883, Method 3015) | 00V |

| Parameter          | Description                                                 | Min.     | Max.     | Unit |

|--------------------|-------------------------------------------------------------|----------|----------|------|

| V <sub>DD</sub>    | Supply Voltage, 3.3V                                        | 3.135    | 3.465    | V    |

| T <sub>A</sub>     | Operating Temperature, Ambient                              | 0        | 70       | °C   |

| CL                 | Capacitive Load on<br>All Clock Outputs except REF0<br>REF0 | 10<br>20 | 20<br>45 | pF   |

| f <sub>(REF)</sub> | Reference Clock Input Frequency                             | 14.318   | 14.318   | MHz  |

#### **Electrical Characteristics** $V_{DD}$ = 3.135V to 3.465V, $T_A$ = 0°C to +70°C

| Parameter                      | Description               | Test Conditions                                  |                          |                            | Min. | Max. | Unit |

|--------------------------------|---------------------------|--------------------------------------------------|--------------------------|----------------------------|------|------|------|

| V <sub>IH</sub>                | High-level Input Voltage  | Except Crystal Inputs                            |                          |                            | 2.0  |      | V    |

| V <sub>IL</sub>                | Low-level Input Voltage   | Except Crystal In                                | puts                     |                            |      | 0.8  | V    |

| V <sub>OH</sub> <sup>[5]</sup> | High-level Output Voltage | $V_{DD} = V_{DD}$ Min.                           | I <sub>OH</sub> = -15 mA | All outputs<br>except REF0 | 2.4  |      | V    |

| V <sub>OH</sub> <sup>[5]</sup> | High-level Output Voltage | $V_{DD} = V_{DD}$ Min.                           | I <sub>OH</sub> = -38 mA | REF0                       |      |      |      |

| V <sub>OL</sub> <sup>[5]</sup> | Low-level Output Voltage  | $V_{DD} = V_{DD}$ Min.                           | I <sub>OL</sub> = 8 mA   | All outputs<br>except REF0 |      | 0.4  | V    |

| V <sub>OL</sub> <sup>[5]</sup> | Low-level Output Voltage  | $V_{DD} = V_{DD}$ Min.                           | I <sub>OL</sub> = 22 mA  | REF0                       |      |      |      |

| I <sub>IH</sub>                | Input High Current        | $V_{IH} = V_{DD}$                                |                          |                            |      | 5    | μA   |

| IIL                            | Input Low Current         | $V_{IL} = 0V$                                    |                          |                            |      | 100  | μA   |

| I <sub>OZ</sub>                | Output Leakage Current    | Three-state                                      |                          |                            | -10  | +10  | μA   |

| I <sub>DD</sub>                | Power Supply Current      | $V_{DD} = 3.465V, V_{IN} = 0 \text{ or } V_{DD}$ |                          |                            |      | 50   | mA   |

## Switching Characteristics<sup>[5, 6]</sup>

| Parameter      | Output                           | Description                      | Test Conditions                | Min. | Max. | Unit |

|----------------|----------------------------------|----------------------------------|--------------------------------|------|------|------|

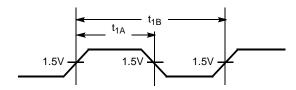

| t <sub>1</sub> | All                              | Output Duty Cycle <sup>[7]</sup> | $t_1 = t_{1A} \div t_{1B}$     | 45%  | 55%  |      |

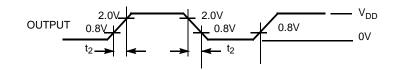

| t <sub>2</sub> | REF0                             | REF0 Clock Rise Time             | Measured between 0.8V and 2.0V |      | 2.0  | ns   |

| t <sub>3</sub> | REF0                             | REF0 Clock Fall Time             | Measured between 2.0V and 0.8V |      | 2.0  | ns   |

| t <sub>2</sub> | All Clock outputs<br>except REF0 | Clock Rise Time                  | Measured between 0.8V and 2.0V |      | 4    | ns   |

| t <sub>3</sub> | All Clock outputs<br>except REF0 | Clock Fall Time                  | Measured between 2.0V and 0.8V |      | 4    | ns   |

| t <sub>4</sub> | USBCLK, IOCLK                    | Cycle-Cycle Clock Jitter         | Measured at 1.5V               |      | 500  | ps   |

Notes:

Electrical parameters are guaranteed with these operating conditions.

Guaranteed by design and characterization, not 100% tested in production.

All parameters specified with outputs fully loaded.

Duty cycle is measured at 1.5V.

## Switching Waveforms

#### **Duty Cycle Timing**

#### All Outputs Rise/Fall Time

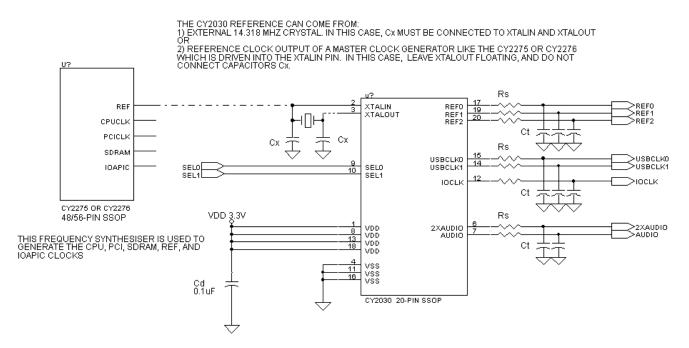

#### **Applications Information**

Clock traces must be terminated with either series or parallel termination, as they are normally done. Additionally, the CY2030 does not have crystal load matching capacitors internal to the device, and therefore, external capacitors will be needed when using the device with an external crystal.

CX = LOAD MATCHING CAPACITORS, REQUIRED WITH EXTERNAL CRYSTALS = 2 \* CRYSTAL LOAD CAPACITANCE

- Cd = DECOUPLING CAPACITOR

- Ct = OPTIONAL EMI-REDUCING CAPACITORS

- Rs = SERIES TERMINATING RESISTORS

#### Summary

- A parallel-resonant crystal should be used as the reference to the clock generator. The operating frequency and C<sub>LOAD</sub> of this crystal should be as specified in the data sheet. Optional trimming capacitors may be needed if a crystal with a different C<sub>LOAD</sub> is used. Footprints must be laid out for flexibility.

- Surface mount, low-ESR, ceramic capacitors should be used for filtering. Typically, these capacitors have a value of 0.1 μF. In some cases, smaller value capacitors may be required.

- The value of the series terminating resistor satisfies the following equation, where R<sub>trace</sub> is the loaded characteristic impedance of the trace, R<sub>out</sub> is the output impedance of the clock generator (specified in the data sheet), and R<sub>series</sub> is the series terminating resistor.

$R_{series} \ge R_{trace} - R_{out}$

- Footprints must be laid out for optional EMI-reducing capacitors, which should be placed as close to the terminating resistor as is physically possible. Typical values of these capacitors range from 4.7 pF to 22 pF.

- A Ferrite Bead **may** be used to isolate the Board  $V_{DD}$  from the clock generator  $V_{DD}$  island. Ensure that the Ferrite Bead offers greater than 50 $\Omega$  impedance at the clock frequency, under loaded DC conditions. Please refer to the application note "Layout and Termination Techniques for Cypress Clock Generators" for more details.

- If a Ferrite Bead is used, a 10 μF-22 μF tantalum bypass capacitor should be placed close to the Ferrite Bead. This capacitor prevents power supply droop during current surges.

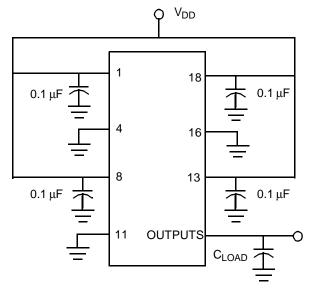

## **Test Circuit**

Note: All capacitors should be placed as close to each pin as possible.

## **Ordering Information**

| Ordering Code | Package<br>Name | Package Type | Operating<br>Range |  |

|---------------|-----------------|--------------|--------------------|--|

| CY2030PVC-1   | O20             | 20-Pin SSOP  | Commercial         |  |

Document #: 38-00560-B

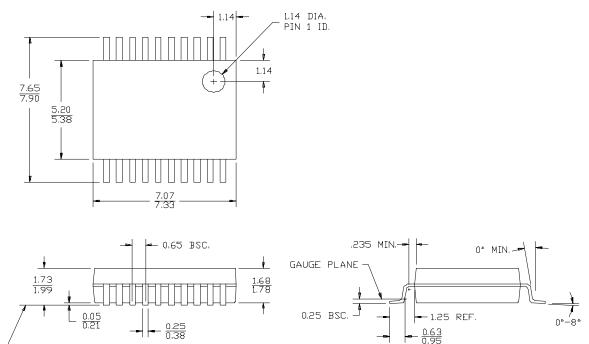

## Package Diagram

All Dimensions in mm.

20-Pin Shrunk Small Outline Package O20

L SEATING PLANE

© Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor against all charges.