### FUDAN MICROELECTRONICS

# STF1001 Telephone IC Card Chip

Specification

May. 2008

INFORMATION IN THIS DOCUMENT IS INTENDED AS A REFERENCE TO ASSIST OUR CUSTOMERS IN THE SELECTION OF SHANGHAI FUDAN MICROELECTRONICS CO., LTD PRODUCT BEST SUITED TO THE CUSTOMER'S APPLICATION; THEY DO NOT CONVEY ANY LICENSE UNDER ANY INTELLECTUAL PROPERTY RIGHTS, OR ANY OTHER RIGHTS, BELONGING TO SHANGHAI FUDAN MICROELECTRONICS CO., LTD OR A THIRD PARTY. WHEN USING THE INFORMATION CONTAINED IN THIS DOCUMENTS, PLEASE BE SURE TO EVALUATE ALL INFORMATION AS A TOTAL SYSTEM BEFORE MAKING A FINAL DECISION ON THE APPLICABILITY OF THE INFORMATION AND PRODUCTS. SHANGHAI FUDAN MICROELECTRONICS CO., LTD ASSUMES NO RESPONSIBILITY FOR ANY DAMAGE, LIABILITY OR OTHER LOSS RESULTING FROM THE INFORMATION CONTAINED HEREIN. SHANGHAI FUDAN MICROELECTRONICS CO., LTD PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS. THE PRIOR WRITTEN APPROVAL OF SHANGHAI FUDAN MICROELECTRONICS CO., LTD IS NECESSARY TO REPRINT OR REPRODUCE IN WHOLE OR IN PART THESE DOCUMENTS. Future routine revisions will occur when appropriate, without notice. Contact Shanghai Fudan Microelectronics Co., Ltd sales office to obtain the latest specifications and before placing your product order. Please also pay attention to information published by Shanghai Fudan Microelectronics Co., Ltd home page (http://www.fmsh.com/).

Please contact Shanghai Fudan Microelectronics Co., Ltd local sales office for the specification regarding the information in this documents or Shanghai Fudan Microelectronics Co., Ltd products.

#### **Trademarks**

Shanghai Fudan Microelectronics Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Co., Ltd, Printed in the China, All Rights Reserved.

上海复旦微电子股份有限公司

Specification

STF1001 Telephone IC Card Chip

Ver 1.1

2

## 1. Product Overview

### 1.1. Description

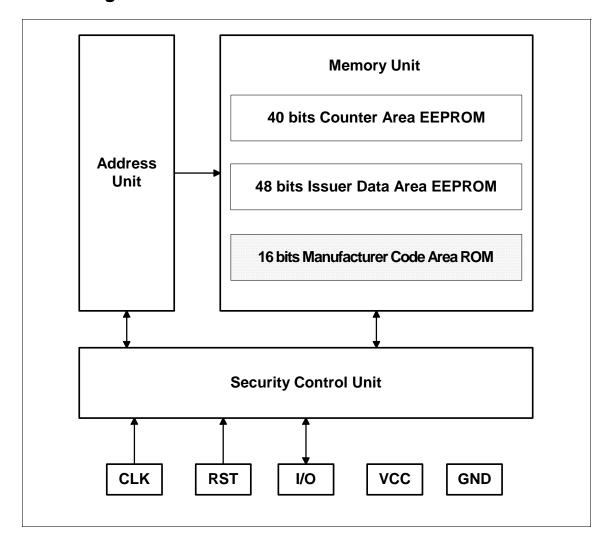

STF1001 is designed for applications in prepaid cards. The chip is special for China Telecom with a specific Manufacturer Code. STF1001 consists of 104 bit memory and adopts 0.6µm CMOS EEPROM technology. The STF1001 is security ICs for telecom providing 88 bits of serial electrically erasable and programmable read-only memory (EEPROM) for counter with security.

### 1.2. Features

- 100% functional compatibility to SLE4406

- 88 bits EEPROM and 16 bits ROM

- 16 bits Manufacturer code (ROM)

- 48 bits for personalization data of card issuer (EEPROM)

- 40 bits Counter Area including 1 bit for personalization (EEPROM)

- Counter with up to 37448 count units

- Five stage counter

- Due to the personalization bit a maximum of 33352 count units is guaranteed

- Transport Code protection for delivery

- Supply voltage: 4.5V~5.5V

- Supply current < 3mA</li>

- EEPROM programming time 5 ms

- ESD protection minimum 2,000V; typical 4,000V

- Endurance minimum 100,000 write/erase cycles / bit

- Data retention for minimum of 30 years

- Contact configuration and Answer-to-Reset (synchronous transmission) in accordance to standard ISO/IEC 7816

## 1.3. Pin Configurations

| vcc | C1 |  | C5    | GND       |    |    |

|-----|----|--|-------|-----------|----|----|

| RST | C2 |  | C2 C6 |           | C6 | NC |

| CLK | C3 |  | C7    | <b>VO</b> |    |    |

### 1.4. Pin Description

| Card Contact | Symbol | Description                          |  |

|--------------|--------|--------------------------------------|--|

| C1           | VCC    | Supply voltage                       |  |

| C2           | RST    | Control input (Reset Signal)         |  |

| C3           | CLK    | Clock input                          |  |

| C5           | GND    | Ground                               |  |

| C6           | N.C.   | Not connected                        |  |

| C7           | I/O    | Bidirectional data line (open drain) |  |

上海复旦微电子股份有限公司

## 1.5. Block Diagram

## 2. Memory Organization

The memory is organized in  $104 \times 1$  bit. Dependent on the status of the flag for personalization (address 64) the memory operates in two different modes.

### 2.1. Issuer Mode

The flag for personalization (address 64) is "1". During delivery the chip is protected by a secret Transport Code with an Error counter. The Identification Area (address 0~63) and the Error counter (address 72~79) are readable, and only the Error counter is programmed. Only after correct verification of the Transport Code the whole memory is readable and programmed. The Counter Area (address 64~103) changes to a five stage counter.

### 2.2. User Mode

The flag for personalization (address 64) is "0". The Identification Area (address 0~63) is protect against further programming.

# 3. Memory Map

|         | Issuer Mode |     |                 |                     |         |             | User Mode   |                      |        |    |                                       |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

|---------|-------------|-----|-----------------|---------------------|---------|-------------|-------------|----------------------|--------|----|---------------------------------------|----|-----|---------------------------------------|----|-------|-------------------|----|---|---|-----|---|------------------------|

| Address | TC r        |     | TC not verified |                     |         | TC verified |             | TC verified          |        |    |                                       |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

|         | W           | Е   | R               | Definition          | ion W E |             | R           | W                    | Е      | R  | Definition                            |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 96-103  | N           | N   | 1               | TC Byte3            | Υ       | In          | Υ           | Υ                    | In     | Υ  | Counter Stage 1 (8 <sup>0</sup> unit) |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 88-95   | Ν           | N   | 1               | TC Byte2            | Υ       | In          | Υ           | Υ                    | In     | Υ  | Counter Stage 2 (8 <sup>1</sup> unit) |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 80-87   | N           | N   | 1               | TC Byte1            | Υ       | In          | Υ           | Υ                    | In     | Υ  | Counter Stage 3 (8 <sup>2</sup> unit) |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 72-79   | V           | V   | V               | Υ                   | \ \     | V           | V           | \<br>\               | \<br>\ | V  | V                                     | V  | V   | NI.                                   | Y  | Error | Υ                 | In | Υ | Υ | l n | Υ | Country Store 1 (03it) |

| (77-79) | Y           | N   | Y               | Counter             | Y       | In          | Y           | Y                    | In     | ſ  | Counter Stage 1 (8 <sup>3</sup> unit) |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 65-71   | N.          | N   | NI              | N                   | N       | NY          | (Boson (od) | Υ                    | N      | Υ  | Υ                                     | NI | Υ   | Counter Stage 5 (8 <sup>4</sup> unit) |    |       |                   |    |   |   |     |   |                        |

| (69-71) | IN          | IN  | Ť               | (Reserved)          | Ť       | IN          | Ť           | YNN                  |        | Ť  | Counter Stage 5 (6 unit)              |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 64      | N           | N N | 1               | Personalizati Y N 1 | Υ       | N           | 0           | Personalization flag |        |    |                                       |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 04      | 1.4         | 1.4 | •               | on flag             | •       | 1.4         | '           |                      | 14   0 |    | 1 Cr30HallZation Hag                  |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 16-63   | Ν           | Ν   | Υ               | С                   | Υ       | Ν           | Υ           | Ν                    | Ν      | Υ  | Personalization flag                  |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 0-15    | N           | N   | Υ               | Manufacturer        | N       | N           | Υ           | NI                   | N      | Υ  | Manufacturer code                     |    |     |                                       |    |       |                   |    |   |   |     |   |                        |

| 0-15    | IN          | IN  | Ť               | code                | IN      | IN          | r           | N                    | IN     | IN | IN                                    | IN | IN_ | IN                                    | IN | Ť     | Manufacturer code |    |   |   |     |   |                        |

### **Access Conditions**

| <b>W</b> : Write ("1"→ "0") | E: Erase ("0"→ "1") | R: Read ("1" or "0") |

|-----------------------------|---------------------|----------------------|

| Y: Yes                      | N: No               | Y: Yes               |

| N: No                       | In: Indirectly      | 1: read "1"          |

## 4. Count Unit

The Counter Area consists of a preloaded five stage counter as 5-digit octal counter. The highest counter stage 5 representing a value of 8<sup>4</sup> units; The lowest counter stage 1 representing a value of 8<sup>0</sup> unit.

Therefore a maximum number of units is

$$8*8^4+8*8^3+8*8^2+8*8^1+8*8^0=37448$$

In practice the range is reduced to 33352 units due to the personalization bit (address 64).

Counting is done by writing bits from "1" to "0". If there are not enough bits in stage the erasing with carry has to be applied.

The erasing with carry consists of two consecutive write operations. The first pulse writes a carry bit in higher stage m to "0", the second pulse at same address erase all 8 bits of the lower stage m-1 to "1".

The counter stage 1 to 4 may completely be erased to "1". The highest counter stage 5 is not erasable, thus counter can be limited to certain number of units.

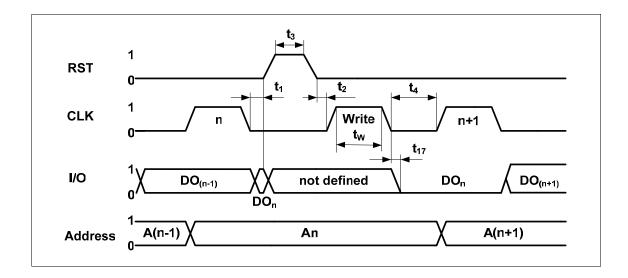

## 5. Transport Code Protection

The chip is protected with a 3bytes Transport Code (Issuer Mode). The Transport Code is programmed in counter stage 1 (address 96~103), 2 (address 88~95) and 3 (address 80~87) and the counter stage 4 (address 72~79) has the functionality of the Error Counter. It limits the Transport Code verification to 8 trials.

In the state the Identification Area (address 0~63) and the Error counter (address 72~79) are readable, and only the Error counter is programmed. Only after correct verification of the Transport Code the whole memory is readable and programmed.

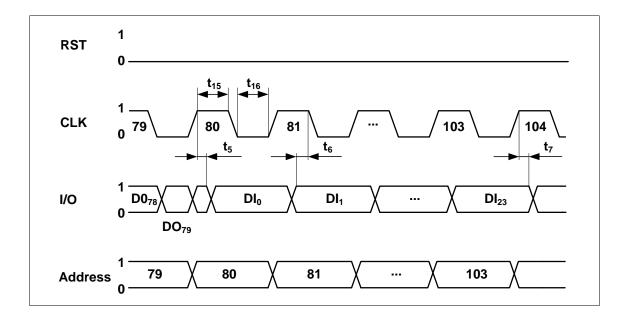

The following procedure has to be applied to verify the Transport Code:

- 1. Address Reset.

- 2. Increment Error Counter by 1. Increment address counter to free Error Counter bit (="1") in the address from 72 to 79. Apply write operation on the addressed bit

- Starting at address 80 the 24bit Transport Code has to be presented at I/O. Increment address

counter from 80 to 103 and present data during CLK high. The internal comparison occurs

during every CLK low. Add one clock pulse to finish the comparison.

The Transport Code mechanism is active until the personalization bit (address 64) is written (="0"). The chip is irreversibly blocked for further use if all Error Counter bits are written without correct verification of the Transport Code.

Figure 1. Entry of Transport Code

## 6. Electrical Characteristics

## 6.1. Absolute Maximum Ratings

| Operating Temperature              | -40°C ~ +85°C  |

|------------------------------------|----------------|

| Storage Temperature                | -55°C ~ +125°C |

| Input voltage on Any Pin to Ground | -0.3V ~ +6.0V  |

| Maximum Operating Voltage          | 6. 0V          |

### 6.2. DC Characteristics

| Symbol          | Parameter                        | Test Condition                              | Min | Тур | Max      | Units |

|-----------------|----------------------------------|---------------------------------------------|-----|-----|----------|-------|

| $V_{CC}$        | Supply Voltage                   |                                             | 4.5 |     | 5.5      | V     |

| I <sub>CC</sub> | Supply Current                   | V <sub>CC</sub> = 5V                        |     | 1.0 | 3.0      | mA    |

| $V_{IH}$        | Input High Level (I/O, CLK, RST) |                                             | 3.5 |     | $V_{CC}$ | V     |

| $V_{IL}$        | Input Low Level (I/O, CLK, RST)  |                                             | 0   |     | 8.0      | V     |

| I <sub>IH</sub> | High Level Input Current (CLK)   | V <sub>IH</sub> = 5V,<br>internal pull-down |     |     | 100      | μA    |

| I <sub>IO</sub> | Low Level Input Current (RST)    | V <sub>IH</sub> = 0V,<br>internal pull-up   |     | -   | -100     | μA    |

| I <sub>OH</sub> | High Level Output Current (I/O)  | V <sub>OH</sub> = 5V, open drain            |     |     | 10       | μA    |

| I <sub>OL</sub> | Low Level Output Current (I/O)   | $V_{OL}$ = 0.5V, open drain                 | 0.5 |     |          | mA    |

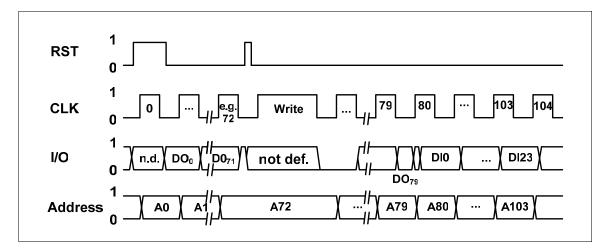

## 6.3. AC Characteristics

| Symbol          | Parameter                                 | Min | Тур | Max | Units |

|-----------------|-------------------------------------------|-----|-----|-----|-------|

| t <sub>10</sub> | RST High to CLK Setup time                | 5   |     |     | μs    |

| t <sub>11</sub> | CLK Low to RST Hold time                  | 5   |     |     | μs    |

| t <sub>12</sub> | RST High time (address reset)             | 50  |     |     | μs    |

| t <sub>13</sub> | RST Low to I/O Valid time                 |     |     | 5   | μs    |

| t <sub>14</sub> | RST Low to CLK Setup time (set address)   | 5   |     |     | μs    |

| t <sub>15</sub> | CLK High time (set address)               | 10  |     |     | μs    |

| t <sub>16</sub> | CLK Low time (set address)                | 10  |     |     | μs    |

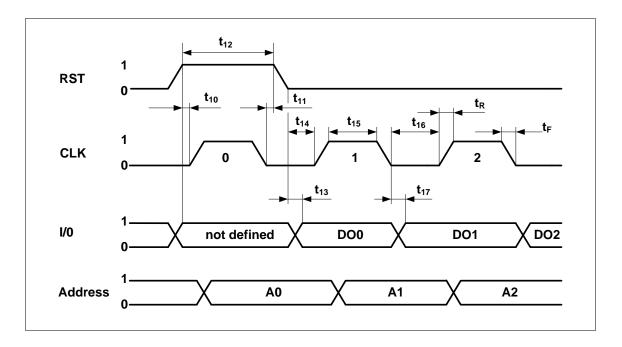

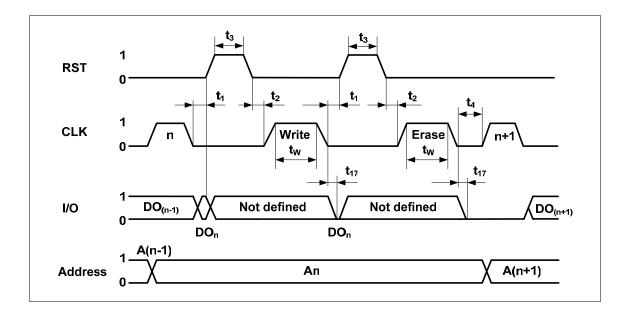

| t <sub>17</sub> | CLK Low to I/O Valid time                 |     |     | 3.5 | μs    |

| $t_R$           | CLK Rise time                             |     |     | 1   | μs    |

| $t_{F}$         | CLK Fall time                             |     |     | 1   | μs    |

| $t_1$           | CLK Low to RST Setup time                 | 5   |     |     | μs    |

| $t_2$           | RST Low to CLK Setup time (write address) | 5   |     |     | μs    |

| $t_3$           | RST High time (set write flag)            | 10  |     |     | μs    |

| t <sub>4</sub>  | CLK Low to CLK Setup time After Write     | 10  |     |     | μs    |

| t <sub>W</sub>  | CLK High time (write)                     | 5   |     |     | ms    |

| $t_5$           | CLK High to I/O Clear time                |     |     | 3.5 | μs    |

| t <sub>6</sub>  | I/O Setup to CLK Low time                 | 3.5 |     |     | μs    |

| t <sub>7</sub>  | CLK High to I/O Hold time                 | 3.5 |     |     | μs    |

上海复旦微电子股份有限公司 SHANGHAI FUDAN MICROFLECTROMOR CO.

SHANGHAI FUDAN MICROBLECTRONICS CO., LTD.

STF1001 Telephone IC Card Chip

Specification

# 7. Timing Diagrams

Figure 2. Answer to Reset, Address setting and Read Operation

Figure 3. Write Operation

Figure 4. Erase 8 Bits with Carry Operation

Figure 5. Entry of Transport Code

11

# 8. Ordering Information

| Ordering Code | Package               | Operating Range                           |

|---------------|-----------------------|-------------------------------------------|

| STF1001-M3    | Module Package (6Pin) | Industrial Temperature<br>(-40°C ~ +85°C) |

# **Revision History**

| Version | Publication date | Pages | Paragraph or<br>Illustration | Revise Description                |

|---------|------------------|-------|------------------------------|-----------------------------------|

| 1.0     | Oct. 2007        | 14    |                              | Initial Release.                  |

| 1.1     | May. 2008        | 14    | Sales and service            | Updated the address of HK office. |

|         |                  |       |                              |                                   |

## Sales and Service

### Shanghai Fudan Microelectronics Co., Ltd.

Address: Bldg No. 4, 127 Guotai Rd,

Shanghai City China. Postcode: 200433 Tel: (86-21) 6565 5050 Fax: (86-21) 6565 9115

#### Shanghai Fudan Microelectronics (HK) Co., Ltd.

Address: Unit 506, 5/F., East Ocean Centre, 98 Granville Road,

Tsimshatsui East, Kowloon, Hong Kong Tel: (852) 2116 3288 2116 3338

Fax: (852) 2116 0882

#### **Beijing Office**

Address: Room.1208, Bldg C,

Zhongguancun Science and Technology Development Edifice, 34 zhongguancun Street (South),

Hai Dian District, Beijing City, China.

Postcode: 100081

Tel: (86-10) 6212 0682 6213 9558

Fax: (86-10) 6212 0681

#### **Shenzhen Office**

Address: Room.1301, Century Bldg, Shengtingyuan Hotel, Huagiang Rd (North),

Shenzhen City, China. Postcode: 518028

Tel: (86-755) 8335 3211 8335 6511

Fax: (86-755) 8335 9011

Web Site: http://www.fmsh.com/

14