2.7GHz, 5V, Low Noise, Rail-to-Rail Input Differential Amplifier/Driver

## FEATURES

- Low Noise: 1.6nV/√Hz RTI

- Low Power: 18mA at 5V

- Low Distortion (HD2/HD3):

- -82dBc/-65dBc at 50MHz, 2V<sub>P-P</sub> -97dBc/-91dBc at 25MHz, 2V<sub>P-P</sub>

- Rail-to-Rail Differential Input

- 4.5V to 5.5V Supply Voltage Range

- Fully Differential Input and Output

- Adjustable Output Common Mode Voltage

- 800MHz 3dB Bandwidth with A<sub>V</sub> = 1

- Gain-Bandwidth Product: 2.7GHz

- Low Power Shutdown

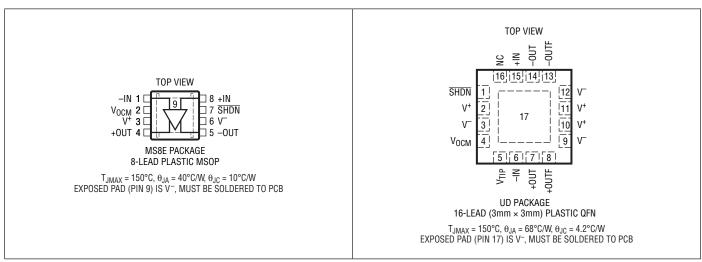

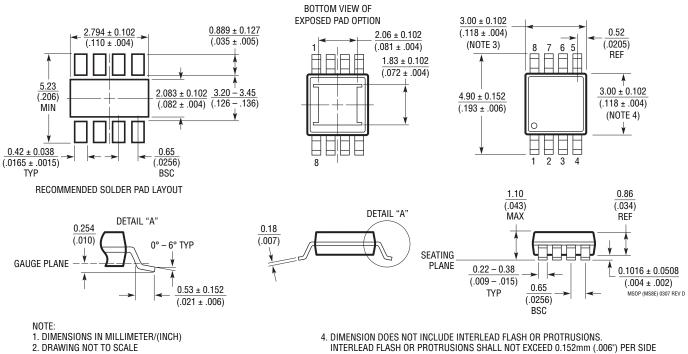

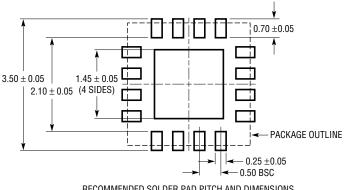

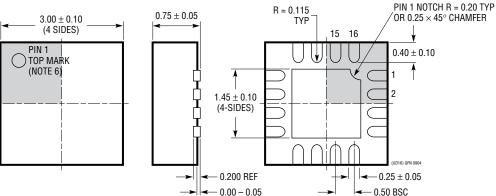

- Available in 8-Lead MSOP and 16-Lead 3mm × 3mm × 0.75mm QFN Packages

# **APPLICATIONS**

- Differential Input ADC Driver

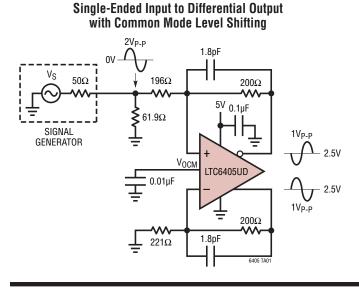

- Single-Ended to Differential Conversion

- Level-Shifting Ground-Referenced Signals

- Level-Shifting V<sub>CC</sub>-Referenced Signals

- High-Linearity Direct Conversion Receivers

# DESCRIPTION

The LTC<sup>®</sup>6405 is a very low noise, low distortion, fully differential input/output amplifier optimized for 5V, single supply operation. The LTC6405 input common mode range is rail-to-rail, while the output common mode voltage is independently adjustable by applying a voltage on the  $V_{OCM}$  pin. This makes the LTC6405 ideal for level shifting signals with a wide common mode range for driving 12-bit to 16-bit single supply, differential input ADCs.

A 2.7GHz gain-bandwidth product results in 65dB linearity for 50MHz input signals. The LTC6405 is unity gain stable and the closed-loop bandwidth extends from DC to 800MHz. The output voltage swing extends from near-ground to 4V, to be compatible with a wide range of ADC converter input requirements. The LTC6405 draws only 18mA, and has a hardware shutdown feature which reduces current consumption to  $400\mu$ A.

The LTC6405 is available in a compact  $3mm \times 3mm 16$ -pin leadless QFN package, as well as an 8-lead MSOP package, and operates over a -40°C to 85°C temperature range.

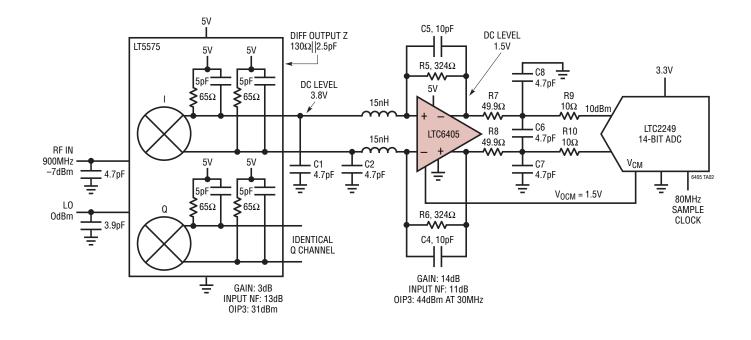

# TYPICAL APPLICATION

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )5.5V                     |

|----------------------------------------------------------------------------------|

| Input Current                                                                    |

| (+IN, -IN, V <sub>OCM</sub> , <del>SHDN</del> , V <sub>TIP</sub> ) (Note 2)±10mA |

| Output Short-Circuit Duration (Note 3) Indefinite                                |

| Operating Temperature Range                                                      |

| (Note 4)–40°C to 85°C                                                            |

| Specified Temperature Range (Note 5) |               |  |  |  |

|--------------------------------------|---------------|--|--|--|

| LTC64051                             | –40°C to 85°C |  |  |  |

| LTC6405C                             | 0°C to 70°C   |  |  |  |

| Junction Temperature                 | 150°C         |  |  |  |

| Storage Temperature Range            | 65°C to 150°C |  |  |  |

## PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION                   | SPECIFIED TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------------|-----------------------------|

| LTC6405CMS8E#PBF | LTC6405CMS8E#TRPBF | LTDKN         | 8-Lead Plastic MSOP                   | 0°C to 70°C                 |

| LTC6405IMS8E#PBF | LTC6405IMS8E#TRPBF | LTDKN         | 8-Lead Plastic MSOP                   | -40°C to 85°C               |

| LTC6405CUD#PBF   | LTC6405CUD#TRPBF   | LDKP          | 16-Lead (3mm $	imes$ 3mm) Plastic QFN | 0°C to 70°C                 |

| LTC6405IUD#PBF   | LTC6405IUD#TRPBF   | LDKP          | 16-Lead (3mm $	imes$ 3mm) Plastic QFN | -40°C to 85°C               |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

**DC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{0CM} = V_{1CM} = 2.5V$ ,  $V_{SHDN} = open$ , circuit component values in Figure 1 used, unless otherwise noted.  $V_S$  is defined as  $(V^+ - V^-)$ .  $V_{OUTCM}$  is defined as  $(V_{+OUT} + V_{-OUT})/2$ .  $V_{ICM}$  is defined as  $(V_{+IN} + V_{-IN})/2$ .  $V_{OUTDIFF}$  is defined as  $(V_{+OUT} - V_{-OUT})$ .

| SYMBOL                          | PARAMETER                                                                                     | CONDITIONS                                                               |     | MIN         | ТҮР                  | MAX              | UNITS                   |

|---------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-------------|----------------------|------------------|-------------------------|

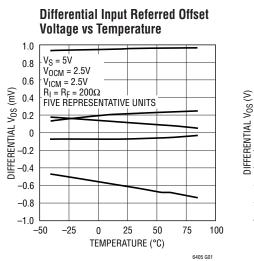

| V <sub>OSDIFF</sub>             | Differential Offset Voltage (Input Referred)                                                  | $V_{ICM} = 5V$ (Note 12)<br>$V_{ICM} = 2.5V$<br>$V_{ICM} = 0V$ (Note 12) | •   |             | ±1<br>±0.5<br>±1     | ±7<br>±3.5<br>±7 | mV<br>mV<br>mV          |

| $\Delta V_{OSDIFF} / \Delta T$  | Differential Offset Voltage Drift (Input Referred)                                            |                                                                          | ••• |             | 1.5<br>1<br>3        |                  | μV/°C<br>μV/°C<br>μV/°C |

| I <sub>B</sub>                  | Input Bias Current (Note 6)                                                                   |                                                                          | •   | -24         | 8<br>7<br>14         |                  | μΑ<br>μΑ<br>μΑ          |

| I <sub>OS</sub>                 | Input Offset Current (Note 6)                                                                 |                                                                          | •   |             | ±0.5<br>±0.5<br>±0.5 | ±4               | μΑ<br>μΑ<br>μΑ          |

| R <sub>IN</sub>                 | Input Resistance                                                                              | Common Mode<br>Differential Mode                                         |     |             | 230<br>3.5           |                  | kΩ<br>kΩ                |

| CIN                             | Input Capacitance                                                                             | Differential                                                             |     |             | 1                    |                  | pF                      |

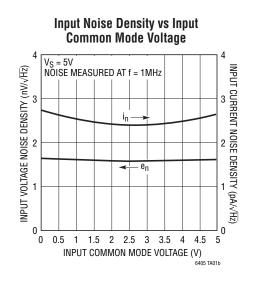

| e <sub>n</sub>                  | Differential Input Referred Noise Voltage Density                                             | $f = 1MHz$ , Not Including $R_I/R_F$<br>Noise                            |     |             | 1.6                  |                  | nV/√Hz                  |

| i <sub>n</sub>                  | Input Noise Current Density                                                                   | $f = 1MHz$ , Not Including $R_I/R_F$<br>Noise                            |     |             | 2.4                  |                  | pA/√Hz                  |

| envocm                          | Input Referred Common Mode Output Noise Voltage<br>Density                                    | f = 1MHz                                                                 |     |             | 9.5                  |                  | nV/√Hz                  |

| V <sub>ICMR</sub> (Note 7)      | Input Signal Common Mode Range                                                                | Op-Amp Inputs                                                            | •   | V-          |                      | V+               | V                       |

| CMRRI<br>(Note 8)               | Input Common Mode Rejection Ratio<br>(Input Referred) ΔV <sub>ICM</sub> /ΔV <sub>OSDIFF</sub> | V <sub>ICM</sub> from 0V to 5V                                           | •   | 50          | 75                   |                  | dB                      |

| CMRRIO<br>(Note 8)              | Output Common Mode Rejection Ratio<br>(Input Referred) $\Delta V_{OCM} / \Delta V_{OSDIFF}$   | V <sub>OCM</sub> from 0.5V to 3.9V                                       | •   | 50          | 75                   |                  | dB                      |

| PSRR<br>(Note 9)                | Differential Power Supply Rejection $(\Delta V_S/\Delta V_{OSDIFF})$                          | V <sub>S</sub> = 4.5V to 5.5V                                            |     | 50          | 75                   |                  | dB                      |

| PSRRCM<br>(Note 9)              | Output Common Mode Power Supply Rejection $(\Delta V_S/\Delta V_{OSCM})$                      | V <sub>S</sub> = 4.5V to 5.5V                                            | •   | 55          | 70                   |                  | dB                      |

| G <sub>CM</sub>                 | Common Mode Gain ( $\Delta V_{OUTCM}/\Delta V_{OCM}$ )                                        | V <sub>OCM</sub> from 0.5V to 3.9V                                       | •   |             | 1                    |                  | V/V                     |

| $\Delta G_{CM}$                 | Common Mode Gain Error 100 • (G <sub>CM</sub> – 1)                                            | V <sub>OCM</sub> from 0.5V to 3.9V                                       | •   |             | ±0.25                | ±0.8             | %                       |

| BAL                             | Output Balance ( $\Delta V_{OUTCM} / \Delta V_{OUTDIFF}$ )                                    | ΔV <sub>OUTDIFF</sub> = 2V<br>Single-Ended Input<br>Differential Input   | •   |             | 60<br>65             | -40<br>-40       | dB<br>dB                |

| V <sub>OSCM</sub>               | Common Mode Offset Voltage (V <sub>OUTCM</sub> – V <sub>OCM</sub> )                           |                                                                          | •   |             | ±6                   | ±15              | mV                      |

| ΔV <sub>OSCM</sub> /ΔT          | Common Mode Offset Voltage Drift                                                              |                                                                          | •   |             | 20                   |                  | μV/°C                   |

| V <sub>OUTCMR</sub><br>(Note 7) | Output Signal Common Mode Range<br>(Voltage Range for the V <sub>OCM</sub> Pin)               |                                                                          | •   | 0.5         |                      | 3.9              | V                       |

| RINVOCM                         | Input Resistance, V <sub>OCM</sub> Pin                                                        |                                                                          | •   | 13          | 19                   | 25               | kΩ                      |

| V <sub>OCM</sub>                | Self-Biased Voltage at the $V_{\rm 0CM}$ Pin                                                  | V <sub>OCM</sub> = Open                                                  | •   | 2.35        | 2.5                  | 2.65             | V                       |

| V <sub>OUT</sub>                | Output Voltage, High, +OUT/-OUT Pins                                                          | $ I_L = 0  I_L = -5mA $                                                  | •   | 3.9<br>3.85 | 4<br>3.95            |                  | V<br>V                  |

|                                 | Output Voltage, Low, +OUT/-OUT Pins                                                           | $ I_L = 0  I_L = 5 mA $                                                  | •   |             | 0.3<br>0.42          | 0.4<br>0.54      | V<br>V                  |

| I <sub>SC</sub>                 | Output Short-Circuit Current, +OUT/-OUT Pins<br>(Note 10)                                     |                                                                          | •   | ±40         | ±60                  |                  | mA                      |

**DC ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{0CM} = V_{1CM} = 2.5V$ ,  $V_{SHDN} = open$ , circuit component values in Figure 1 used, unless otherwise noted.  $V_S$  is defined as  $(V^+ - V^-)$ .  $V_{0UTCM}$  is defined as  $(V_{+0UT} + V_{-0UT})/2$ .  $V_{ICM}$  is defined as  $(V_{+1N} + V_{-1N})/2$ .  $V_{0UTDIFF}$  is defined as  $(V_{+0UT} - V_{-0UT})$ .

| SYMBOL            | PARAMETER                           | CONDITIONS                     |   | MIN  | ТҮР | MAX  | UNITS |

|-------------------|-------------------------------------|--------------------------------|---|------|-----|------|-------|

| A <sub>VOL</sub>  | Large-Signal Open Loop Voltage Gain |                                |   |      | 90  |      | dB    |

| V <sub>S</sub>    | Supply Voltage Range                |                                | • | 4.5  |     | 5.5  | V     |

| Is                | Supply Current                      |                                | • |      | 18  | 23   | mA    |

| ISHDN             | Supply Current in Shutdown          | V <sub>SHDN</sub> = 0V         | • |      | 0.4 | 1    | mA    |

| R <sub>SHDN</sub> | SHDN Pull-Up Resistor               | V <sub>SHDN</sub> = 0V to 0.5V | • | 30   | 50  | 70   | kΩ    |

| V <sub>IL</sub>   | SHDN Input Logic Low                |                                | • | 1.25 | 1.8 |      | V     |

| V <sub>IH</sub>   | SHDN Input Logic High               |                                | • |      | 2   | 2.55 | V     |

| t <sub>ON</sub>   | Turn-On Time                        |                                |   |      | 200 |      | ns    |

| t <sub>OFF</sub>  | Turn-Off Time                       |                                |   |      | 50  |      | ns    |

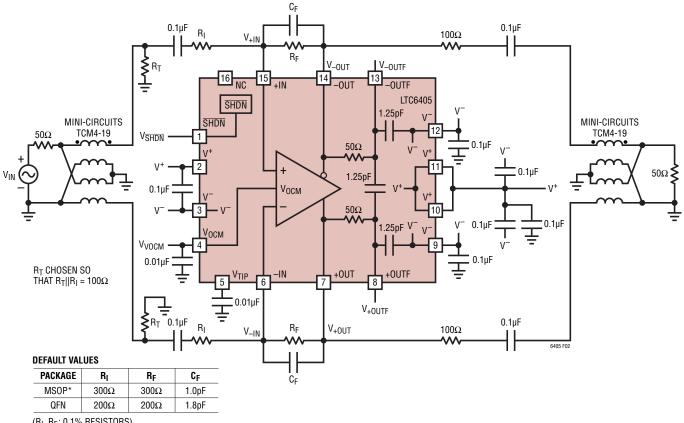

### AC ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full

operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_{OCM} = V_{ICM} = 2.5V$ ,  $V_{SHDN} = open$ ,  $R_{LOAD} = 400\Omega$ , circuit component values in Figure 2 used, unless otherwise noted.  $V_S$  is defined as  $(V^+ - V^-)$ .  $V_{ICM}$  is defined as  $(V_{+IN} + V_{-IN})/2$ .  $V_{OUTDIFF}$  is defined as  $(V_{+OUT} - V_{-OUT})$ .

| SYMBOL            | PARAMETER                                                                                     | CONDITIONS                                                                                                                                                                                                                       |   | MIN        | ТҮР         | MAX | UNITS      |

|-------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------|-----|------------|

| SR                | Slew Rate                                                                                     | Differential Output                                                                                                                                                                                                              |   |            | 690         |     | V/µS       |

| GBW               | Gain-Bandwidth Product                                                                        | f <sub>TEST</sub> = 27MHz                                                                                                                                                                                                        |   |            | 2.7         |     | GHz        |

| f <sub>-3dB</sub> | -3dB Frequency (See Figure 2)                                                                 | QFN Package<br>MSOP Package                                                                                                                                                                                                      |   | 500<br>400 | 800<br>750  |     | MHz<br>MHz |

|                   | 50MHz Distortion<br>Differential Input, V <sub>OUTDIFF</sub> = 2V <sub>P-P</sub><br>(Note 13) | V <sub>OCM</sub> = 2.5V, V <sub>S</sub> = 5V<br>2nd Harmonic<br>3rd Harmonic                                                                                                                                                     | • |            | 80<br>64    | -53 | dBc<br>dBc |

|                   |                                                                                               | V <sub>OCM</sub> = 2.5V, V <sub>S</sub> = 5V, R <sub>LOAD</sub> = 800Ω<br>2nd Harmonic<br>3rd Harmonic                                                                                                                           |   |            | 82<br>66    |     | dBc<br>dBc |

|                   |                                                                                               | $\label{eq:VOCM} \begin{array}{l} V_{0CM} = 2.5 \text{V}, \ V_S = 5 \text{V}, \ R_{\text{LOAD}} = 800 \Omega, \\ R_I = R_F = 499 \Omega \\ 2 \text{nd Harmonic} \\ 3 \text{rd Harmonic} \end{array}$                             |   |            | 82<br>64    |     | dBc<br>dBc |

|                   | 50MHz Distortion<br>Single-Ended Input, V <sub>OUTDIFF</sub> = 2V <sub>P-P</sub><br>(Note 13) | $\begin{array}{l} V_{0CM} = 2.5 \text{V}, \text{V}_{S} = 5 \text{V}, \text{R}_{\text{LOAD}} = 800 \Omega, \\ \text{R}_{\text{I}} = \text{R}_{\text{F}} = 499 \Omega \\ 2 \text{nd Harmonic} \\ 3 \text{rd Harmonic} \end{array}$ |   |            | -72<br>-77  |     | dBc<br>dBc |

|                   | 3rd-Order IMD at 49.5MHz, 50.5MHz                                                             | $V_{OUTDIFF} = 2V_{P-P}$ Envelope,<br>R <sub>LOAD</sub> = 800 $\Omega$                                                                                                                                                           |   |            | -63         |     | dBc        |

|                   | Equivalent OIP3 at 50MHz (Note 11)                                                            | $R_{LOAD} = 800\Omega$                                                                                                                                                                                                           |   |            | 35.5        |     | dBm        |

| t <sub>S</sub>    | Settling Time                                                                                 | V <sub>OUTDIFF</sub> = 2V Step<br>1% Settling<br>0.1% Settling                                                                                                                                                                   |   |            | 6<br>11     |     | ns<br>ns   |

| NF                | Noise Figure at 50MHz                                                                         | $ \begin{array}{l} Shunt\mbox{-Terminated to } 50\Omega,  R_S = 50\Omega \\ Z_{IN} = 200\Omega \ (R_I = 100\Omega,  R_F = 300\Omega) \end{array} $                                                                               |   |            | 14.4<br>7.5 |     | dB<br>dB   |

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Input pins (+IN, -IN,  $V_{OCM}$ , SHDN and  $V_{TIP}$ ) are protected by steering diodes to either supply. If the inputs should exceed either supply voltage, the input current should be limited to less than 10mA. In addition, the inputs +IN, -IN are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1.4V, the input current should be limited to less than 10mA.

**Note 3:** A heat sink may be required to keep the junction temperature below the Absolute Maximum Rating when the output is shorted indefinitely.

**Note 4:** The LTC6405C/LTC6405I are guaranteed functional over the operating temperature range –40°C to 85°C.

**Note 5:** The LTC6405C is guaranteed to meet specified performance from 0°C to 70°C. The LTC6405C is designed, characterized, and expected to meet specified performance from -40°C to 85°C but is not tested or QA sampled at these temperatures. The LTC6405I is guaranteed to meet specified performance from -40°C to 85°C.

**Note 6:** Input bias current is defined as the average of the input currents flowing into the inputs (–IN, and +IN). Input Offset current is defined as the difference between the input currents ( $I_{OS} = I_B^+ - I_B^-$ ).

**Note 7:** Input common mode range is tested using the test circuit of Figure 1 by taking 3 measurements of differential gain with a ±1VDC differential output with  $V_{ICM} = 0V$ ;  $V_{ICM} = 2.5V$ ;  $V_{ICM} = 5V$ , verifying that the differential gain has not deviated from the  $V_{ICM} = 2.5V$  case by more than 0.5%, and that the common mode offset ( $V_{OSCM}$ ) has not deviated from the common mode offset at  $V_{ICM} = 2.5V$  by more than ±35mV.

The voltage range for the output common mode range is tested using the test circuit of Figure 1 by applying a voltage on the V<sub>OCM</sub> pin and testing at both V<sub>OCM</sub> = 2.5V and at the Electrical Characteristics table limits to verify that the common mode offset (V<sub>OSCM</sub>) has not deviated by more than  $\pm$ 20mV from the V<sub>OCM</sub> = 2.5V case.

**Note 8:** Input CMRR is defined as the ratio of the change in the input common mode voltage at the pins +IN or -IN to the change in differential input referred voltage offset. Output CMRR is defined as the ratio of the change in the voltage at the V<sub>OCM</sub> pin to the change in differential input referred voltage offset. This specification is strongly dependent on feedback ratio matching between the two outputs and their respective inputs, and it is difficult to measure actual amplifier performance. (See the "Effects of Resistor Pair Mismatch" in the Applications Information section of this data sheet.) For a better indicator of actual amplifier performance independent of feedback component matching, refer to the PSRR specification.

**Note 9:** Differential Power Supply Rejection (PSRR) is defined as the ratio of the change in supply voltage to the change in differential input referred voltage offset. Common mode power supply rejection (PSRRCM) is defined as the ratio of the change in supply voltage to the change in the common mode offset,  $V_{OUTCM} - V_{OCM}$ .

**Note 10:** Extended operation with the output shorted may cause the junction temperature to exceed the 150°C limit.

**Note 11:** Because the LTC6405 is a feedback amplifier with low output impedance, a resistive load is not required when driving an ADC. Therefore, typical output power can be very small in many applications. In order to compare the LTC6405 with "RF style" amplifiers that require  $50\Omega$  load, the output voltage swing is converted to dBm as if the outputs were driving a  $50\Omega$  load. For example,  $2V_{P-P}$  output swing is equal to 10dBm using this convention.

**Note 12:** Includes offset/drift induced by feedback resistors mismatch. See the Applications Information section for more details.

**Note 13:** QFN package only—refer to datasheet curves for MSOP package numbers.

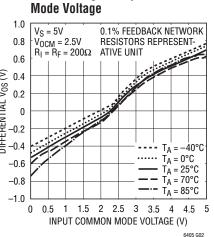

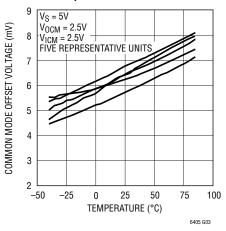

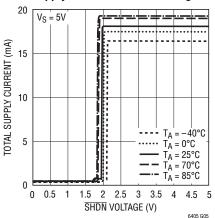

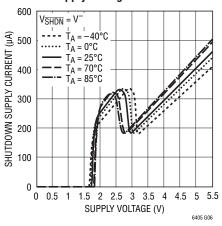

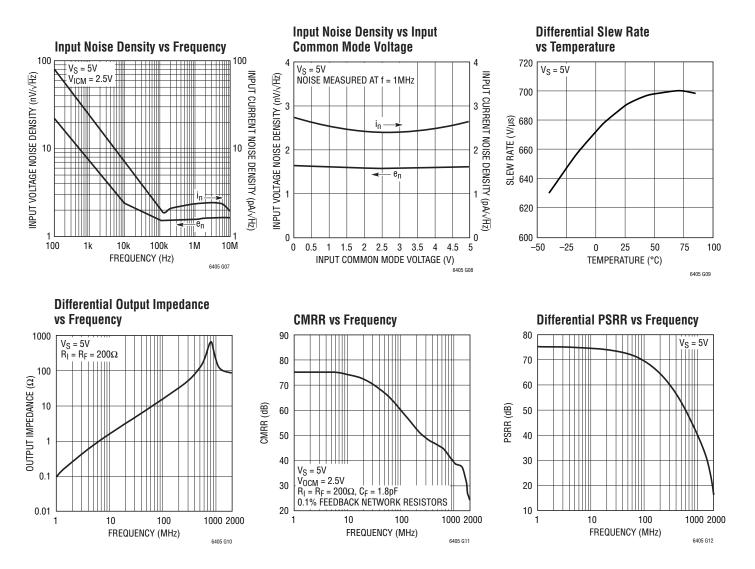

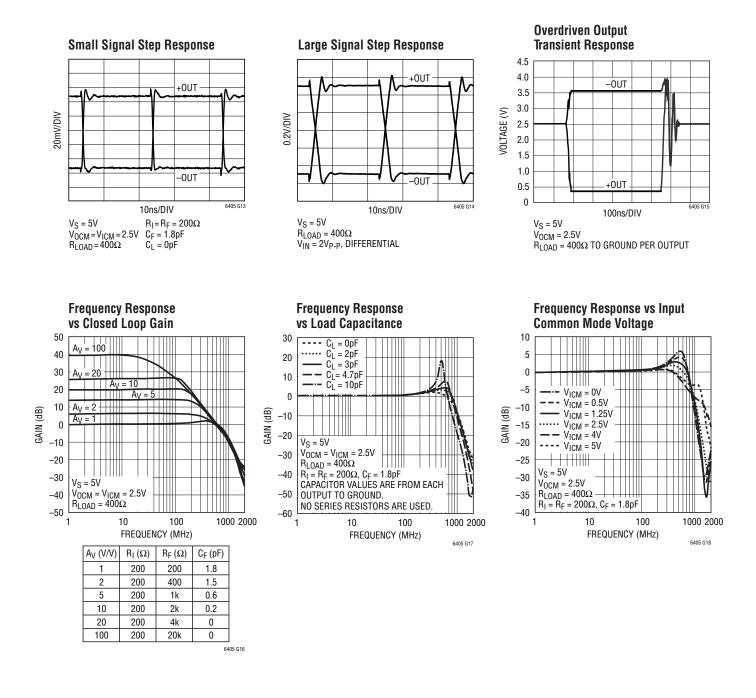

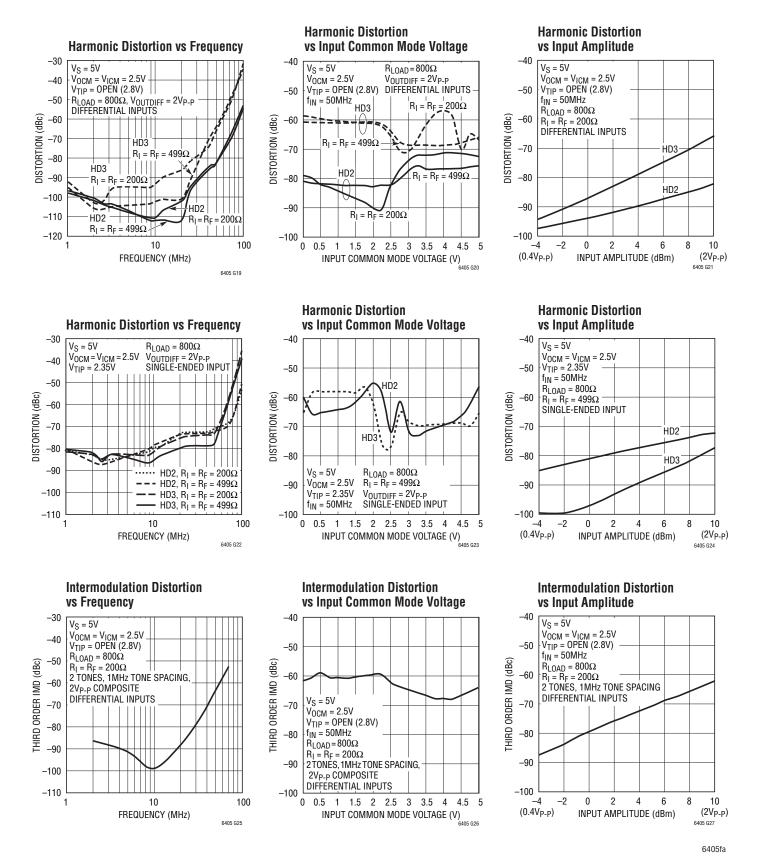

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Differential Input Referred Offset Voltage vs Input Common

#### Common Mode Offset Voltage vs Temperature

**Supply Current vs Supply Voltage** 20  $V_{\overline{SHDN}} = OPEN$  $--40^{\circ}C$  $T_A = 0^{\circ}C$ TOTAL SUPPLY CURRENT (mA) 15  $T_A = 25^{\circ}C$  $T_A = 70^{\circ}C$  $T_A = 85^{\circ}C$ 10 5 İ 0 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 SUPPLY VOLTAGE (V) 6405 G04

Supply Current vs SHDN Voltage

Shutdown Supply Current vs Supply Voltage

# **TYPICAL PERFORMANCE CHARACTERISTICS**

www.DataSheet4<del>Uz</del>om

# TYPICAL PERFORMANCE CHARACTERISTICS (QFN Package)

8

### TYPICAL PERFORMANCE CHARACTERISTICS (QFN Package)

www.DataSheet40.com

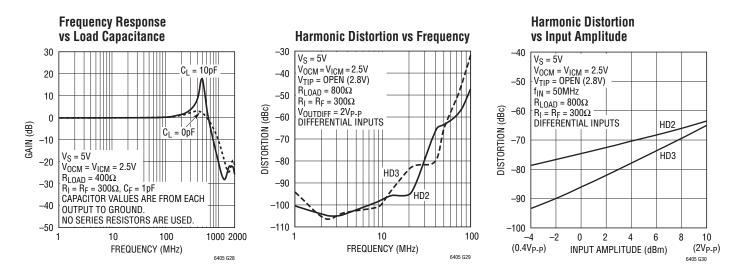

# TYPICAL PERFORMANCE CHARACTERISTICS (MSOP Package)

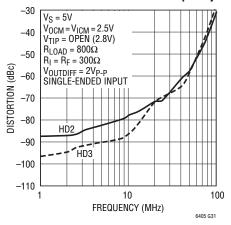

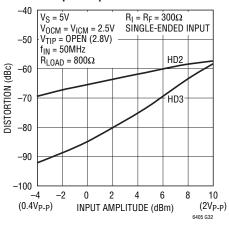

Harmonic Distortion vs Frequency

Harmonic Distortion vs Input Amplitude

### PIN FUNCTIONS (MSOP/QFN)

**V<sub>OCM</sub>** (Pin 2/Pin 4): Output Common Mode Reference Voltage. The voltage on V<sub>OCM</sub> sets the output common mode voltage level (which is defined as the average of the voltages on the +OUT and –OUT pins). The V<sub>OCM</sub> voltage is internally set by a resistive divider between the supplies, developing a default voltage potential of 2.5V with a 5V supply. The V<sub>OCM</sub> pin can be over-driven by an external voltage capable of driving the 19k $\Omega$  Thevenin equivalent impedance presented by the pin. The V<sub>OCM</sub> pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.01µF, to minimize common mode noise from being converted to differential noise by impedance mismatches both externally and internally to the IC.

#### V<sup>+</sup> (Pin 3/Pins 2, 10, 11):

#### V<sup>-</sup> (Pin 6/Pins 3, 9, 12):

Power Supply Pins. It is critical that close attention be paid to supply bypassing. For single supply applications, it is recommended that a high quality  $0.1\mu$ F surface mount ceramic bypass capacitor be placed between V<sup>+</sup> and V<sup>-</sup> with direct short connections. In addition, V<sup>-</sup> should be tied directly to a low impedance ground plane with minimal routing. For dual (split) power supplies, it is recommended that additional high quality,  $0.1\mu$ F ceramic capacitors are used to bypass V<sup>+</sup> to ground and V<sup>-</sup> to ground, again with minimal routing. For driving large loads (<200 $\Omega$ ), additional bypass capacitance may be needed for optimal performance. Keep in mind that small geometry (e.g., 0603 or smaller) surface mount ceramic capacitors have a much higher self resonant frequency than do leaded capacitors, and perform best in high speed applications.

+OUT, -OUT (Pins 4, 5/Pins 7, 14): Unfiltered Output Pins. Besides driving the feedback network, each pin can drive an additional  $50\Omega$  to ground with typical short circuit current limiting of ±60mA. Each amplifier output is designed to drive a load capacitance of 5pF. Larger capacitive loads should be decoupled with at least  $15\Omega$  resistors from each output.

$V_{TIP}$  (Pin 5) QFN Only: This pin can normally be left floating. It determines which pair of input transistors (NPN or PNP or both) is sensing the input signal. The V<sub>TIP</sub> pin is set by an internal resistive divider between the supplies, developing a default 2.8V voltage with a 5V supply. V<sub>TIP</sub> has a Thevenin equivalent resistance of approximately 17k and can be over-driven by an external voltage. The V<sub>TIP</sub> pin should be bypassed with a high quality ceramic bypass capacitor of at least 0.01µF. See the Applications Information section for more details.

**SHDN** (Pin 7/Pin 1): When SHDN is floating or directly tied to V<sup>+</sup>, the LTC6405 is in the normal (active) operating mode. When the SHDN pin is connected to V<sup>-</sup>, the LTC6405 enters into a low power shutdown state with Hi-Z outputs.

**+IN**, **–IN** (**Pins 8**, **1**/**Pins 15**, **6**): Noninverting and Inverting Input Pins of the Amplifier, Respectively. For best performance, it is highly recommended that stray capacitance be kept to an absolute minimum by keeping printed circuit connections as short as possible.

+OUTF, -OUTF (Pins 8, 13) QFN Only: Filtered Output Pins. These pins have a series RC network (R =  $50\Omega$ , C = 3.75pF) connected between the filtered and unfiltered outputs. See the Applications Information section for more details.

**NC (Pin 16) QFN Only:** No Connection. This pin is not connected internally.

**Exposed Pad (Pin 9/Pin 17):** Tie the bottom pad to V<sup>-</sup>. If split supplies are used, DO NOT tie the pad to ground.

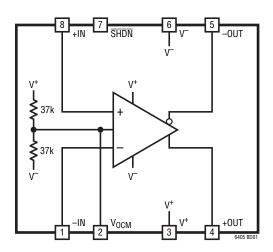

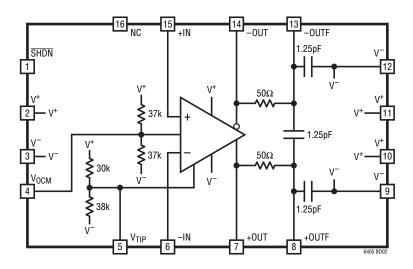

# **BLOCK DIAGRAMS**

LTC6405 Block Diagram/Pinout in MSOP Package

LTC6405 Block Diagram/Pinout in QFN Package

12

#### **Functional Description**

The LTC6405 is a small outline, wideband, low noise, and low distortion fully-differential amplifier with accurate output phase balancing. The LTC6405 is optimized to drive low voltage, single-supply, differential input analogto-digital converters (ADCs). The LTC6405 input common mode range is rail-to-rail, while the output common mode voltage is independently adjustable by applying a voltage on the V<sub>OCM</sub> pin. The output voltage swing extends from near-ground to 4V, to be compatible with a wide range of ADC converter input requirements. This makes the LTC6405 ideal for level shifting signals with a wide common mode range for driving 12-bit to 16-bit single supply, differential input ADCs. The differential output allows for twice the signal swing in low voltage systems when compared to single-ended output amplifiers. The balanced differential nature of the amplifier also provides even-order harmonic distortion cancellation, and less susceptibility to common

mode noise (like power supply noise). The LTC6405 can be used as a single ended input to differential output amplifier, or as a differential input to differential output amplifier.

The LTC6405 output common mode voltage, defined as the average of the two output voltages, is independent of the input common mode voltage, and is adjusted by applying a voltage on the  $V_{OCM}$  pin. If the pin is left open, there is an internal resistive voltage divider, which develops a potential of 2.5V (if the supply is 5V). It is recommended that a high quality ceramic cap is used to bypass the  $V_{OCM}$  pin to a low impedance ground plane. The LTC6405's internal common mode feedback path forces accurate output phase balancing to reduce even order harmonics, and centers each individual output about the potential set by the  $V_{OCM}$  pin.

$$V_{\text{OUTCM}} = V_{\text{OCM}} = \frac{V_{+\text{OUT}} + V_{-\text{OUT}}}{2}$$

\*TO OPTIMIZE THE HIGH FREQUENCY PERFORMANCE FOR THE PIN CONFIGURATION OF THE LTC6405 IN THE SMALL MSOP PACKAGE, A FEEDBACK RESISTANCE OF AT LEAST  $300\Omega$  IS RECOMMENDED.

Figure 1. DC Test Circuit

The outputs (+OUT and -OUT) of the LTC6405 are capable of swinging from close-to-ground to typically 1V below V<sup>+</sup>. They can source or sink up to approximately 60mA of current. Each output is designed to directly drive up to 5pF to ground. Higher load capacitances should be decoupled with at least  $15\Omega$  of series resistance from each output.

#### Input Pin Protection

The LTC6405 input stage is protected against differential input voltages which exceed 1.4V by two pairs of series diodes connected back to back between +IN and -IN. In addition, the input pins have clamping diodes to either power supply. If the input pins are over-driven, the current should be limited to under 10mA to prevent damage to the

IC. The LTC6405 also has clamping diodes to either power supply on the V<sub>OCM</sub>, V<sub>TIP</sub> and SHDN pins and if driven to voltages which exceed either supply, they too, should be current limited to under 10mA.

### **SHDN** Pin

The SHDN pin is a CMOS logic input with a 50k internal pull-up resistor. If the pin is driven low, the LTC6405 powers down with Hi-Z outputs. If the pin is left unconnected or driven high, the part is in normal active operation. Some care should be taken to control leakage currents at this pin to prevent inadvertently putting the LTC6405 into shutdown. The turn-on and turn-off time between the shutdown and active states are typically less than 1µs.

(RI, RF: 0.1% RESISTORS)

\*TO OPTIMIZE THE HIGH FREQUENCY PERFORMANCE FOR THE PIN CONFIGURATION OF THE LTC6405 IN THE SMALL MSOP PACKAGE, A FEEDBACK RESISTANCE OF AT LEAST  $300\Omega$  is recommended.

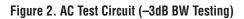

#### **General Amplifier Applications**

As levels of integration have increased and correspondingly, system supply voltages decreased, there has been a need for ADCs to process signals differentially in order to maintain good signal to noise ratios. These ADCs are typically supplied from a single supply voltage which can be as low as 3V, and will have an optimal common mode input range of 1.25V or 1.5V. The LTC6405 makes interfacing to these ADCs easy, by providing both single-ended to differential conversion as well as common mode level shifting. The gain to V<sub>OUTDIFF</sub> from V<sub>INM</sub> and V<sub>INP</sub> is:

$$V_{\text{OUTDIFF}} = V_{+\text{OUT}} - V_{-\text{OUT}} \approx \frac{R_F}{R_I} \bullet \left( V_{\text{INP}} - V_{\text{INM}} \right)$$

Note from the above equation, the differential output voltage  $(V_{+OUT} - V_{-OUT})$  is completely independent of input and output common mode voltages, or the voltage at the common mode pin. This makes the LTC6405 ideally suited for pre-amplification, level shifting and conversion of single ended signals to differential output signals in preparation for driving differential input ADCs.

#### **Effects of Resistor Pair Mismatch**

Figure 3 shows a circuit diagram which takes into consideration that real world resistors will not match perfectly. Assuming infinite open loop gain, the differential output relationship is given by the equation:

$$\begin{split} V_{\text{OUTDIFF}} &= V_{+\text{OUT}} - V_{-\text{OUT}} \cong \frac{R_{\text{F}}}{R_{\text{I}}} \bullet V_{\text{INDIFF}} + \\ &\frac{\Delta\beta}{\beta_{\text{AVG}}} \bullet V_{\text{ICM}} - \frac{\Delta\beta}{\beta_{\text{AVG}}} \bullet V_{\text{OCM}} \end{split}$$

where:

$R_F$  is the average of  $R_{F1},$  and  $R_{F2},$  and  $R_I$  is the average of  $R_{I1},$  and  $R_{I2}.$

$\beta_{AVG}$  is defined as the average feedback factor from the outputs to their respective inputs:

$$\beta_{AVG} = \frac{1}{2} \bullet \left( \frac{R_{l1}}{R_{l1} + R_{F1}} + \frac{R_{l2}}{R_{l2} + R_{F2}} \right)$$

$\Delta\beta$  is defined as the difference in feedback factors:

$$\Delta\beta = \frac{R_{l2}}{R_{l2} + R_{F2}} - \frac{R_{l1}}{R_{l1} + R_{F1}}$$

$V_{ICM}$  is defined as the average of the two input voltages  $V_{INP}$  and  $V_{INM}$  (also called the input common mode voltage):

$$V_{ICM} = \frac{1}{2} \bullet \left( V_{INP} + V_{INM} \right)$$

and V<sub>INDIFF</sub> is defined as the difference of the input voltages:

$$V_{INDIFF} = V_{INP} - V_{INM}$$

$V_{0CM}$  is defined as the average of the two output voltages  $V_{+0UT}$  and  $V_{-0UT}$ :

$$V_{\text{OCM}} = \frac{V_{+\text{OUT}} + V_{-\text{OUT}}}{2}$$

When the feedback ratios mismatch ( $\Delta\beta$ ), common mode to differential conversion occurs.

Setting the differential input to zero ( $V_{INDIFF} = 0$ ), the degree of common mode to differential conversion is given by the equation:

$$V_{\text{OUTDIFF}} = V_{+\text{OUT}} - V_{-\text{OUT}} \approx (V_{\text{ICM}} - V_{\text{OCM}}) \bullet \frac{\Delta\beta}{\beta_{\text{AVG}}}$$

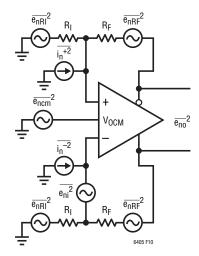

Figure 3. Real-World Application with Feedback Resistor Pair Mismatch

www.DataSheet40.com

In general, the degree of feedback pair mismatch is a source of common mode to differential conversion of both signals and noise. Using 1% resistors or better will mitigate most problems, and will provide about 34dB worst case of common mode rejection. Using 0.1% resistors will provide about 54dB of common mode rejection. A low impedance ground plane should be used as a reference for both the input signal source and the V<sub>OCM</sub> pin. Bypassing the V<sub>OCM</sub> with a high quality 0.1µF ceramic capacitor to this ground plane will further help prevent common mode signals from being converted to differential signals.

There may be concern on how feedback factor mismatch affects distortion. Feedback factor mismatch from using 1% resistors or better, has a negligible effect on distortion. However, in single supply level shifting applications where there is a voltage difference between the input common mode voltage and the output common mode voltage, resistor mismatch can make the apparent voltage offset of the amplifier appear worse than specified.

The apparent input referred offset induced by feedback factor mismatch is derived from the above equation:

$V_{OSDIFF(APPARENT)} \approx (V_{ICM} - V_{OCM}) \bullet \Delta\beta$

Using the LTC6405 in a single supply application on a single 5V supply with 1% resistors, and the input common mode grounded, with the  $V_{OCM}$  pin biased at 2.5V, the worst case DC offset can induce 25mV of apparent offset voltage. With 0.1% resistors, the worst case apparent offset reduces to 2.5mV.

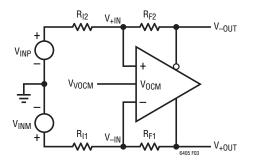

### Input Impedance and Loading Effects

The input impedance looking into the V<sub>INP</sub> or V<sub>INM</sub> input of Figure 1 depends on whether or not the sources V<sub>INP</sub> and V<sub>INM</sub> are fully differential or not. For balanced input sources (V<sub>INP</sub> =  $-V_{INM}$ ), the input impedance seen at either input is simply:

$R_{INP} = R_{INM} = R_{I}$

For single ended inputs, because of the signal imbalance at the input, the input impedance actually increases over

the balanced differential case. The input impedance looking into either input is:

$$R_{INP} = R_{INM} = \frac{R_I}{\left(1 - \frac{1}{2} \cdot \left(\frac{R_F}{R_I + R_F}\right)\right)}$$

Input signal sources with non-zero output impedances can also cause feedback imbalance between the pair of feedback networks. For the best performance, it is recommended that the input source output impedance be compensated for. If input impedance matching is required by the source, a termination resistor R1 should be chosen (see Figure 4):

Figure 4. Optimal Compensation for Signal Source Impedance

According to Figure 4, the input impedance looking into the differential amp  $(R_{\rm INM})$  reflects the single ended source case, thus:

$$R_{INM} = \frac{R_{I}}{\left(1 - \frac{1}{2} \cdot \left(\frac{R_{F}}{R_{I} + R_{F}}\right)\right)}$$

R2 is chosen to equal R1 || R<sub>S</sub>:

$$R2 = \frac{R1 \cdot R_{S}}{R1 + R_{S}}$$

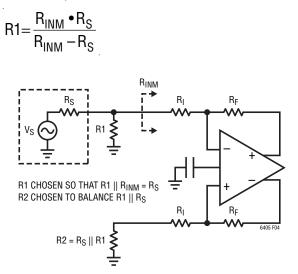

#### Input Common Mode Voltage Range

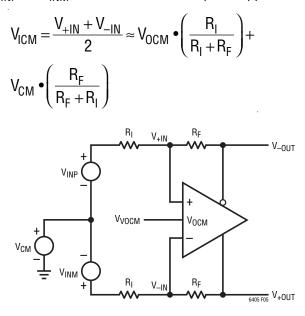

The LTC6405's input common mode voltage (V<sub>ICM</sub>) is defined as the average of the two input voltages, V<sub>+IN</sub>, and V<sub>-IN</sub>. At the inputs to the actual op amp, the range extends from V<sup>-</sup> to V<sup>+</sup>. This makes it easy to interface to a wide range of common mode signals, from ground referenced to V<sub>CC</sub> referenced signals. Moreover, due to external resistive divider action of the gain and feedback resistors, the effective range of signals that can be processed is even wider. The input common mode range at the op amp inputs depends on the circuit configuration (gain), V<sub>OCM</sub> and V<sub>CM</sub> (refer to Figure 5). For fully differential input applications, where V<sub>INP</sub> =  $-V_{INM}$ , the common mode input is approximately:

Figure 5. Circuit for Common Mode Range

With single ended inputs, there is an input signal component to the input common mode voltage. Applying only  $V_{\rm INP}$  (setting  $V_{\rm INM}$  to zero), the input common voltage is approximately:

$$V_{ICM} = \frac{V_{+IN} + V_{-IN}}{2} \approx V_{0CM} \cdot \left(\frac{R_I}{R_I + R_F}\right) + V_{CM} \cdot \left(\frac{R_F}{R_F + R_I}\right) + \frac{V_{INP}}{2} \cdot \left(\frac{R_F}{R_F + R_I}\right)$$

Use the equations above to check that the  $V_{\rm ICM}$  at the op amp inputs is within range (V^- to V^+).

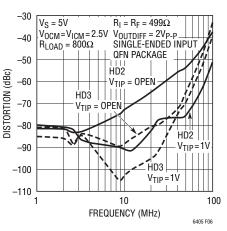

### Manipulating the Rail-to-Rail Input Stage with $\ensuremath{V_{\text{TIP}}}$

To achieve rail-to-rail input operation, the LTC6405 features an NPN input stage in parallel with a PNP input stage. When the input common mode voltage is near V<sup>+</sup>, the NPNs are active while the PNPs are off. When the input common mode is near V<sup>-</sup>, the PNPs are active while the NPNs are off. At some range in the middle, both input stages are active. This 'hand-off' operation happens automatically.

In the QFN package, a special pin,  $V_{TIP}$ , is made available that can be used to manipulate the 'hand-off' operation between the NPN and PNP input stages. By default, the  $V_{TIP}$  pin is internally biased by an internal resistive divider between the supplies, developing a default 2.8V voltage with a 5V supply. If desired,  $V_{TIP}$  can be over-driven by an external voltage (the Thevenin equivalent resistance is approximately 17k).

If  $V_{TIP}$  is pulled closer to V<sup>-</sup>, the range over which the NPN input pair remains active is increased, while the range over which the PNP input pair is active is reduced. In applications where the input common mode does not come close to V<sup>-</sup>, this mode can be used to further improve linearity beyond the specified performance (see Figure 6).

If  $V_{TIP}$  is pulled closer to V<sup>+</sup>, the range over which the PNP input pair remains active is increased, while the range over which the NPN input pair is active is reduced. In applications where the input common mode does not come close to V<sup>+</sup>, this mode can be used to further improve linearity beyond the specified performance.

Figure 6. Manipulating  $V_{\text{TIP}}$  to Improve Harmonic Distortion

#### **Output Common Mode Voltage Range**

The output common mode voltage is defined as the average of the two outputs:

$$V_{OUTCM} = V_{OCM} = \frac{V_{+OUT} + V_{-OUT}}{2}$$

The V<sub>OCM</sub> pin sets this average by an internal common mode feedback loop which internally forces  $V_{OUTCM} = V_{OCM}$ . The output common mode range extends from 0.5V above V<sup>-</sup> to typically 1V below V<sup>+</sup>. The V<sub>OCM</sub> voltage is internally set by a resistive divider between the supplies, developing a default voltage potential of 2.5V with a 5V supply.

In single supply applications, where the LTC6405 is used to interface to an ADC, the optimal common mode input range to the ADC is often determined by the ADC's reference. If the ADC makes a reference available for setting the input common mode voltage, it can be directly tied to the  $V_{OCM}$  pin (as long as it is able to drive the 19k $\Omega$  Thevenin equivalent input impedance presented by the  $V_{OCM}$  pin).

The  $V_{OCM}$  pin should be bypassed with a high quality ceramic bypass capacitor of at least  $0.01\mu$ F to filter any common mode noise rather than being converted to differential noise and to prevent common mode signals on this pin from being inadvertently converted to differential signals by impedance mismatches both externally and internally to the IC.

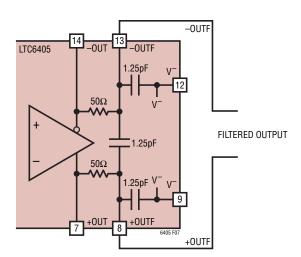

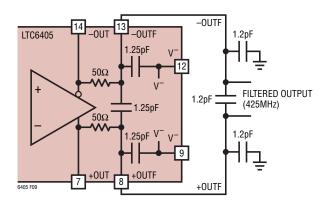

Figure 7. LTC6405 Internal Filter Topology

### **Output Filter Considerations and Use**

Filtering at the output of the LTC6405 is often desired to provide anti-aliasing or to improve signal to noise ratio. To simplify this filtering, the LTC6405 in the QFN package includes an additional pair of differential outputs (+OUTF and -OUTF) which incorporate an internal lowpass RC network with a -3dB bandwidth of 850MHz (Figure 7).

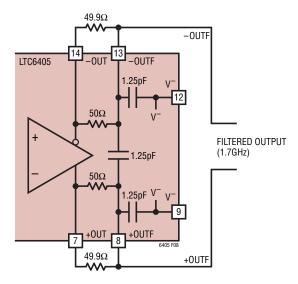

These pins each have an output resistance of  $50\Omega$  (tolerance ±12%). Internal capacitances are 1.25pF (tolerance  $\pm 15\%$ ) to V<sup>-</sup> on each filtered output, plus an additional 1.25 pF (tolerance  $\pm 15\%$ ) capacitor connected between the two filtered outputs. This resistor/capacitor combination creates filtered outputs that look like a series  $50\Omega$  resistor with a 3.75pF capacitor shunting each filtered output to AC ground, providing a –3dB bandwidth of 850MHz, and a noise bandwidth of 1335MHz. The filter cutoff frequency is easily modified with just a few external components. To increase the cutoff frequency, simply add two equal value resistors, one between +OUT and +OUTF and the other between -OUT and -OUTF (Figure 8). These resistors, in parallel with the internal  $50\Omega$  resistors, lower the overall resistance and therefore increase filter bandwidth. For example, to double the filter bandwidth, add two external  $50\Omega$  resistors to lower the series filter resistance to  $25\Omega$ . The 3.75pF of capacitance remains unchanged, so filter bandwidth doubles. Keep in mind, the series resistance also serves to decouple the outputs from load capacitance.

Figure 8. LTC6405 Filter Topology Modified for 2x Filter Bandwidth (Two External Resistors)

The outputs of the LTC6405 are designed to drive 5pF to ground, so care should be taken to not lower the effective impedance between +OUT and +OUTF or –OUT and –OUTF below  $15\Omega$ .

To decrease filter bandwidth, add two external capacitors, one from +OUTF to ground, and the other from –OUTF to ground. A single differential capacitor connected between +OUTF and –OUTF can also be used, but since it is being driven differentially it will appear at each filtered output as a single-ended capacitance of twice the value. To halve the filter bandwidth, for example, two 3.9pF capacitors could be added (one from each filtered output to ground). Alternatively, one 1.8pF capacitor could be added between the filtered outputs, which also halves the filter bandwidth. Combinations of capacitors could be used as well; a three capacitor solution of 1.2pF from each filtered output to ground plus a 1.2pF capacitor between the filtered outputs would also halve the filter bandwidth (Figure 9).

#### **Noise Considerations**

The LTC6405's input referred voltage noise is 1.6nV/ $\sqrt{Hz}$ . Its input referred current noise is 2.4pA/ $\sqrt{Hz}$ . In addition to the noise generated by the amplifier, the surrounding feedback resistors also contribute noise. A noise model is shown in Figure 10. The output noise generated by both

Figure 9. LTC6405 Filter Topology Modified for 1/2x Filter Bandwidth (Three External Capacitors)

the amplifier and the feedback components is governed by the equation:

$$e_{no} = \sqrt{\left(e_{ni} \cdot \left(1 + \frac{R_F}{R_I}\right)\right)^2 + 2 \cdot \left(I_n \cdot R_F\right)^2 + 2 \cdot \left(e_{nRI} \cdot \left(\frac{R_F}{R_I}\right)\right)^2 + 2 \cdot e_{nRF}^2\right)^2}$$

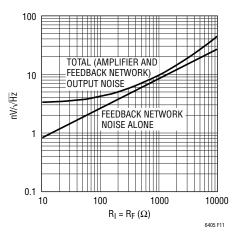

A plot of this equation, and a plot of the noise generated by the feedback components for the LTC6405 is shown in Figure 11.

Figure 10. Noise Model of the LTC6405

Figure 11. LTC6405 Output Spot Noise vs Spot Noise Contributed by Feedback Network Alone

The LTC6405's input referred voltage noise contributes the equivalent noise of a  $155\Omega$  resistor. When the feedback network is comprised of resistors whose values are less than this, the LTC6405's output noise is voltage noise dominant (see Figure 11):

$$e_{no} \approx e_{ni} \bullet \left( 1 + \frac{R_F}{R_I} \right)$$

Feedback networks consisting of resistors with values greater than about  $200\Omega$  will result in output noise which is resistor noise and amplifier current noise dominant.

$$e_{no} \approx \sqrt{2} \bullet \sqrt{\left(I_n \bullet R_F\right)^2 + \left(1 + \frac{R_F}{R_I}\right) \bullet 4 \bullet k \bullet T \bullet R_F}$$

Lower resistor values (<100 $\Omega$ ) always result in lower noise at the penalty of increased distortion due to increased loading of the feedback network on the output. Higher resistor values (but still less than <500 $\Omega$ ) will result in higher output noise, but typically improved distortion due to less loading on the output. The optimal feedback resistance for the LTC6405 runs in between 100 $\Omega$  to 500 $\Omega$ .

The differential filtered outputs +OUTF and –OUTF will have a little higher noise than the unfiltered outputs (due to the two  $50\Omega$  resistors which contribute  $0.9nV/\sqrt{Hz}$  each), but can provide superior signal-to-noise due to the output noise filtering.

### Layout Considerations

Because the LTC6405 is a very high speed amplifier, it is sensitive to both stray capacitance and stray inductance. In the QFN package, three pairs of power supply pins are provided to keep the power supply inductance as low as possible to prevent any degradation of amplifier 2nd harmonic performance. It is critical that close attention be paid to supply bypassing. For single supply applications it is recommended that high quality  $0.1\mu$ F surface mount ceramic bypass capacitor be placed directly between each V<sup>+</sup> and V<sup>-</sup> pin with direct short connections. The V<sup>-</sup> pins should be tied directly to a low impedance ground plane with minimal routing. For dual (split) power supplies, it is recommended that additional high quality,  $0.1\mu$ F ceramic capacitors are used to bypass V<sup>+</sup> to ground and V<sup>-</sup> to ground, again with minimal routing. For driving large loads (<200 $\Omega$ ), additional bypass capacitance may be needed for optimal performance. Keep in mind that small geometry (e.g., 0603) surface mount ceramic capacitors have a much higher self resonant frequency than do leaded capacitors, and perform best in high speed applications.

Any stray parasitic capacitances to ground at the summing junctions, +IN and –IN, should be minimized. This becomes especially true when the feedback resistor network uses resistor values >500 $\Omega$  in circuits with  $R_F = R_I$ . Always keep in mind the differential nature of the LTC6405, and that it is critical that the load impedances seen by both outputs (stray or intended), should be as balanced and symmetric as possible. This will help preserve the natural balance of the LTC6405, which minimizes the generation of even order harmonics, and improves the rejection of common mode signals and noise.

It is highly recommended that the  $V_{OCM}$  pin be bypassed to ground with a high quality ceramic capacitor whose value exceeds 0.01µE This will help stabilize the common mode feedback loop as well as prevent thermal noise from the internal voltage divider and other external sources of noise from being converted to differential noise due to divider mismatches in the feedback networks. It is also recommended that the resistive feedback networks be comprised of 1% resistors (or better) to enhance the output common mode rejection. This will also prevent  $V_{OCM}$  input referred common mode noise of the common mode amplifier path (which cannot be filtered) from being converted to differential noise, degrading the differential noise performance.

Feedback factor mismatch has a weak effect on distortion. Using 1% or better resistors will limit any mismatch from impacting amplifier linearity. However, in single supply level shifting applications where there is a voltage difference between the input common mode voltage and the output common mode voltage, resistor mismatch can make the apparent voltage offset of the amplifier appear worse than specified.

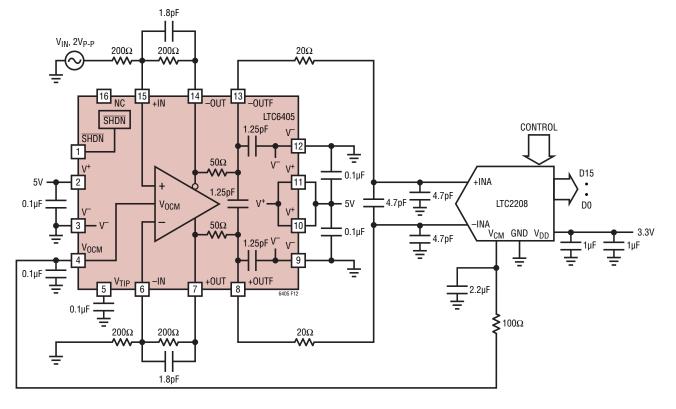

### Interfacing the LTC6405 to A/D Converters

Rail-to-rail input and fast settling time make the LTC6405 ideal for interfacing to low voltage, single supply, differential input ADCs. The sampling process of ADCs create a sampling glitch caused by switching in the sampling capacitor on the ADC front end which momentarily "shorts" the output of the amplifier as charge is transferred between the amplifier and the sampling capacitor. The amplifier must recover and settle from this load transient before this acquisition period ends for a valid representation of the input signal. In general, the LTC6405 will settle much more quickly from these periodic load impulses than from a 2V input step, but it is a good idea to place an R-C filter network between the differential outputs of the LTC6405 and the input of the ADC to help absorb the charge injection that comes out of the ADC from the sampling process. The capacitance of the filter network serves as a charge reservoir to provide high frequency charging during the sampling process, while the resistors of the filter network are used to dampen and attenuate any charge kickback from the ADC. The selection of the R-C time constant is trial and error for a given ADC, but the following guidelines are recommended: Choosing too large of a resistor in the decoupling network leaving insufficient settling time will create a voltage divider between the dynamic input impedance of the ADC and the decoupling resistors. Choosing too small of a resistor will possibly prevent the resistor from properly dampening the load transient caused by the sampling process, prolonging the time required for settling. In 16-bit applications, this will typically require a minimum of 11 R-C time constants. It is recommended that the capacitor chosen have a high quality dielectric (such as COG multilaver ceramic).

Figure 12. Interfacing the LTC6405 to an ADC

# TYPICAL APPLICATION

2VP-P DIFF OUTPUT C1, 2.7pF LEVEL-SHIFTED TO 1.25V R3. 100Ω 3.3V **AA** 5V R5 R1 511Ω 51.1Ω  $\sim$ Ś ±5V SINE WAVE R6 R2 LTC6405 LTC2207 (10V<sub>P-P</sub>) CENTERED AT 0V 511Ω 51.1Ω 6405 TA0  $V_{CM} = 1.25V$ R4, 100Ω 2.2µF Ŧ C2, 2.7pF

Attenuating and Level Shifting a Single-Ended ±5V Signal to a Differential 2V<sub>P-P</sub> Signal at a 1.25V Common Mode

PACKAGE DESCRIPTION

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

### PACKAGE DESCRIPTION

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

BOTTOM VIEW-EXPOSED PAD

NOTE:

1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WEED-2)

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

- ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

#### DC-Coupled Level Shifting of Demodulator Output

### **RELATED PARTS**

| PART NUMBER                                    | DESCRIPTION                                                                      | COMMENTS                                                                                                                                 |

|------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| LT1993-2/LT1993-4/<br>LT1993-10                | 800MHz/900MHz/700MHz Low Distortion, Low Noise Differential Amplifier/ADC Driver | A <sub>V</sub> = 2V/V / A <sub>V</sub> = 4V/V / A <sub>V</sub> = 10V/V, NF = 12.3dB/14.5dB/<br>12.7dB, 0IP3 = 38dBm/40dBm/40dBm at 70MHz |

| LT1994                                         | Low Noise, Low Distortion Fully differential Input/Output<br>Amplifier/Driver    | Low Distortion, 2V <sub>P-P</sub> , 1MHz: –94dBc, 13mA,<br>Low Noise: 3nV/√Hz                                                            |

| LTC6400-8/LTC6400-14/<br>LTC6400-20/LTC6400-26 | 1.8GHz Low Noise, Low Distortion, Differential ADC Driver                        | 300MHz IF Amplifier, A <sub>V</sub> = 20dB/26dB                                                                                          |

| LTC6401-8/LTC6401-14/<br>LTC6401-20/LTC6401-26 | 1.3GHz Low Noise, Low Distortion, Differential ADC Driver                        | 140MHz IF Amplifier, A <sub>V</sub> = 20dB/26dB                                                                                          |

| LT6402-6/LT6402-12/<br>LT6402-20               | 300MHz/300MHz/300MHz Low Distortion, Low Noise Differential Amplifier/ADC Driver | $A_V = 6dB/A_V = 12dB/A_V = 20dB$ , NF = 18.6dB/15dB/12.4dB, OIP3 = 49dBm/43dBm/51dBm at 20MHz                                           |

| LTC6404-1/ LTC6404-2/<br>LTC6404-4             | 600MHz Low Noise, Low Distortion, Differential ADC Driver                        | 1.5nV/ $\sqrt{\text{Hz}}$ Noise, –90dBc Distortion at 10MHz                                                                              |

| LTC6406                                        | 3GHz Low Noise, 3V, Rail-to-Rail Input Differential Amplifier/Driver             | 1.6nV/ <del>√Hz</del> Noise, –70dBc Distortion at 50MHz, 18mA, 3V Supply                                                                 |

| LTC6411                                        | Low Power Differential ADC Driver/Dual Selectable Gain Amplifier                 | 16mA Supply Current, IMD3 = $-83$ dBC at 70MHz, A <sub>V</sub> = 1, $-1$ , or 2                                                          |

| LT6600-2.5/LT6600-5/<br>LT6600-10/LT6600-20    | Very Low Noise, Fully Differential Amplifier and 4th<br>Order Filter             | 2.5MHz/5MHz/10MHz/20MHz Integrated Filter, 3V Supply, SO-8 Package                                                                       |

| LTC6403-1                                      | 200MHz Low Noise, Low Power Differential ADC Driver                              | –95dBc Distortion at 3MHz, 10.8mA Supply Current                                                                                         |