**REV. 1.0** FS3332-DS-10\_EN JAN. 2007

**Datasheet**

FS3332

Two Cell Lithium-ion/Polymer Battery Protection IC

Fortune Semiconductor Corporation

富晶電子股份有限公司

28F., No.27, Sec. 2, Zhongzheng E. Rd., Danshui Town, Taipei County 251, Taiwan

Tel.: 886-2-28094742 Fax: 886-2-28094874 www.ic-fortune.com

This manual contains new product information. Fortune Semiconductor Corporation reserves the rights to modify the product specification without further notice. No liability is assumed by Fortune Semiconductor Corporation as a result of the use of this product. No rights under any patent accompany the sale of the product.

**Rev. 1.0** 2/23

#### General Description

The FS3332 Series are protection ICs for 2-serial-cell lithium-ion/lithium-polymer rechargeable batteries and include high-accuracy voltage detectors and delay circuits.

These ICs are suitable for protecting 2-cell rechargeable lithium-ion/lithium-polymer battery packs from overcharge, overdischarge, and over-current

#### 2. Features

- Low supply current

- Normal Operation: 7.5 μ A typ. 14.2 μ A max.

Power-down mode: 0.3 μ A typ.

- Overcharge detection voltage

3.90V~4.60V. Accuracy of ±25mV

- Overcharge release voltage

3.60V~4.60V, Accuracy of ±50mV

- Over-discharge detection voltage 1.70V~2.60V, Accuracy of ±80mV

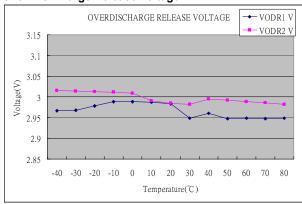

- Over-discharge release voltage (VODR) 1.70V~3.80V, Accuracy of ±100mV

- Over current detection voltage

0.07V~0.30V, Accuracy of ±20mV

- Short circuit detection voltage (VOI2)

Fixed at 1.0V

- Delay times are set by an external capacitor. Each delay time for Overcharge detection,

Over-discharge detection, Over-current detection are "Proportion of hundred of ten to one"

- Two over-current detection levels (protection for short-circuit)

- Internal auxiliary over voltage detection circuit (Fail safe for over voltage)

- Internal charge circuit for 0 V battery (Unavailable is option)

- High-withstanding-voltage devices Absolute maximum rating: 18 V

- Wide operating temperature range -40 to +85°C

- Wide supply voltage range 2.0 ~ 16V

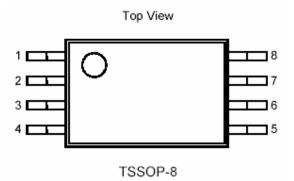

- 8-pin TSSOP Pb-free package

#### 3. Ordering Information

FS3332 <u>x</u>-P (P stands for Pb free)

Serial code \*

\*: Refer to the product name list on next page.

### 4. Applications

- Protection IC for 2-Cell Lithium-lon / Lithium-Polymer Battery Pack

- Portable DVD, DSC, PDA, etc.

Rev. 1.0 3/23

# 5. Product Name List

| Model   | Overcharge<br>detection<br>voltage<br>[VOCU] (V) | release<br>voltage   | Over-discharge<br>detection<br>voltage<br>[VODL] (V) | release<br>voltage | Over-current<br>detection<br>voltage<br>[VOI1] (mV) | 0 V Battery<br>Charging<br>Function |

|---------|--------------------------------------------------|----------------------|------------------------------------------------------|--------------------|-----------------------------------------------------|-------------------------------------|

| FS3332A | 4.250 <u>±</u> 0.025                             | 4.050±0.050          | 2.40±0.080                                           | 3.00±0.100         | 200±20                                              | No                                  |

| FS3332B | 4.350 <u>±</u> 0.025                             | 4.150 <u>±</u> 0.050 | 2.30±0.080                                           | 3.00±0.100         | 300±20                                              | No                                  |

| FS3332C | 4.350±0.025                                      | 4.150±0.050          | 2.30±0.080                                           | 3.00±0.100         | 300±20                                              | Yes<br>(Not Available)              |

| FS3332L | 4.300±0.025                                      | 4.050±0.050          | 2.00±0.080                                           | 3.00±0.100         | 200±20                                              | No                                  |

# 6. Pin Configuration

| Pin No. | Symbol | Description                                                                                 |

|---------|--------|---------------------------------------------------------------------------------------------|

| 1       | SENS   | Detection pin for voltage between SENS and VC (Detection for overcharge and over-discharge) |

| 2       | DO     | FET gate connection pin for discharge control                                               |

| 3       | СО     | FET gate connection pin for charge control                                                  |

| 4       | VM     | Input pin for current sense (Over-current detection pin)                                    |

| 5       | VSS    | Negative power input pin                                                                    |

| 6       | ICT    | Capacitor connection pin for detection delay                                                |

| 7       | VC     | Connection for negative voltage of battery 1 and                                            |

|         |        | positive voltage of battery 2                                                               |

| 8       | VDD    | Positive power input pin                                                                    |

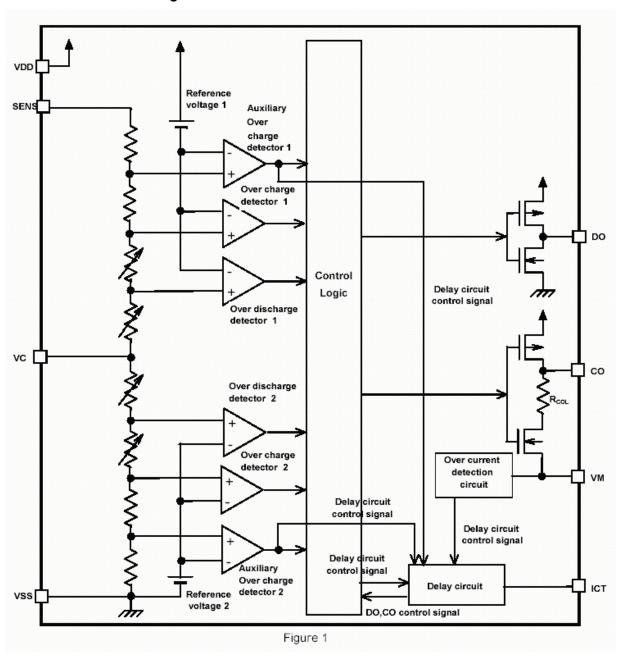

# 7. Functional Block Diagram

**Rev. 1.0** 5/23

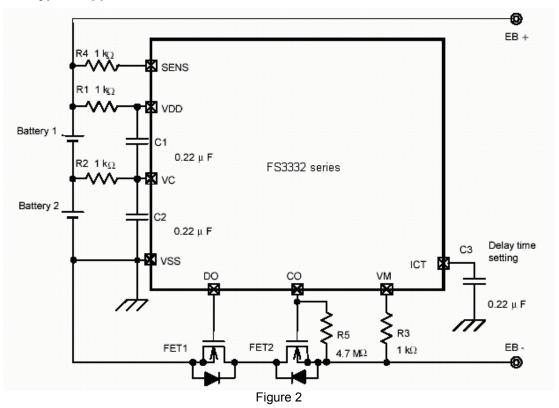

# 8. Typical Application Circuit

# 9. Absolute Maximum Ratings

(VSS=0V, Ta=25°C unless otherwise specified)

| Item                                | Symbol | Rating               | Unit |

|-------------------------------------|--------|----------------------|------|

| Input voltage between VDD and VSS * | VDD    | VSS-0.3 to VSS +18   | V    |

| SENS input pin voltage              | VSENS  | VSS -0.3 to VDD +0.3 | V    |

| ICT input pin voltage               | VICT   | VSS -0.3 to VDD +0.3 | V    |

| CO output pin voltage               | VCO    | VVM -0.3 to VDD +0.3 | V    |

| DO output pin voltage               | VDO    | VSS -0.3 to VDD +0.3 | V    |

| VM input pin voltage                | VVM    | VDD -18 to VDD +0.3  | V    |

| VC input pin voltage                | VVC    | VSS -0.3 to VDD +0.3 | V    |

| Power dissipation                   | PD     | 300                  | mW   |

| Operating Temperature Range         | TOP    | -40 to +85           | °C   |

| Storage Temperature Range           | TST    | -40 to +125          | °C   |

Note: FS3332 contains a circuit that will protect it from static discharge; but please take special care that no excessive static electricity or voltage which exceeds the limit of the protection circuit will be applied to it.

**Rev. 1.0** 7/23

$<sup>^{\</sup>star}$  Pulse (µsec) noise exceeding the above input voltage (VSS +12V) may cause damage to the IC.

# 10. Electrical Characteristics

(Vss=0V, Ta=25°C unless otherwise specified)

| PARAMETER                                  | CONDITIONS     | SYMBOL    | Min            | Тур           | Max            | UNIT |

|--------------------------------------------|----------------|-----------|----------------|---------------|----------------|------|

| CURRENT CONSUMPTION                        |                |           |                |               |                |      |

| Supply Current                             | VDD=7V(2*3.5V) | IDD       |                | 7.5           | 12.7           | μA   |

| Power-Down Current                         | VDD=4.0V(2*2V) | IPD       |                | 0.3           | 0.6            | μA   |

| OPERATING VOLTAGE                          |                |           |                |               |                |      |

| Operating input voltage                    | VDD-VSS        | VDS1      | 2.0            |               | 16             | V    |

| DETECTION VOLTAGE                          |                |           |                |               |                |      |

| Overcharge detection voltage               |                | VOCU      | VOCU<br>-0.025 | VOCU          | VOCU<br>+0.025 | V    |

| Auxiliary overcharge detection Voltage 1,2 |                | VCUAUX1,2 | VOCU*<br>1.21  | VOCU*<br>1.25 | VOCU*<br>1.29  |      |

| Overcharge release voltage                 |                | VOCR      | VOCR<br>-0.050 | VOCR          | VOCR<br>+0.050 | V    |

| Over-discharge detection voltage           |                | VODL      | VODL<br>-0.080 | VODL          | VODL<br>+0.080 | V    |

| Over-discharge release voltage             |                | VODR      | VODR<br>-0.100 | VODR          | VODR<br>+0.100 | V    |

| Over current detection voltage 1           |                | VOI1      | VOI1<br>-0.020 | VOI1          | VOI1<br>+0.020 | V    |

| Over current detection voltage 2           | VSS reference  | VOI2      | 0.5            | 1.0           | 1.5            | V    |

| DELAY TIME(C3=0.22µF)                      |                |           |                |               |                |      |

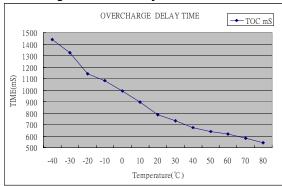

| Overcharge detection delay time            |                | TOC       |                | 1.00          |                | S    |

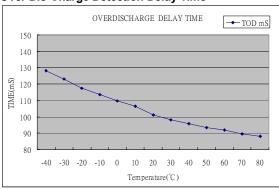

| Over-discharge detection delay time        |                | TOD       |                | 100           | 138            | ms   |

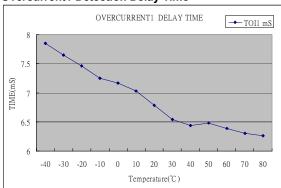

| Over current detection delay time          |                | TOI1      |                | 10            | 13.9           | ms   |

| OTHER                                      |                |           |                |               |                |      |

| CO pin output "H" voltage                  |                | Voh1      |                | VDD-0.019     | VDD            | V    |

| DO pin output "H" voltage                  |                | Voh2      |                | VDD-0.003     | VDD            | V    |

| DO pin output "L" voltage                  |                | Vol2      | VSS            | VSS+0.003     | VSS+0.05       | V    |

| Resistance between VSS and CO              |                | RCOL      | 0.29           | 0.6           | 1.44           | МΩ   |

| Resistance between VDD and VM              |                | RVMD      | 105            | 240           | 575            | kΩ   |

| Resistance between VSS and VM              |                | RVSM      | 511            | 597           | 977            | kΩ   |

| 0 V battery charge starting voltage        |                | V0CHA     |                | No            |                | V    |

(Vss=0V, Ta=-40°C ~ +85°C unless otherwise specified)

| (Vss=0V, Ta=-40°C ~ +85°C unio             | CONDITIONS     | SYMBOL    | Min            | Тур           | Max            | UNIT |

|--------------------------------------------|----------------|-----------|----------------|---------------|----------------|------|

| CURRENT CONSUMPTION                        |                |           |                |               |                |      |

| Supply Current                             | VDD=7V(2*3.5V) | IDD       |                | 7.5           | 14.2           | μA   |

| Power-Down Current                         | VDD=4.0V(2*2V) | IPD       |                | 0.3           | 1.0            | μA   |

| OPERATING VOLTAGE                          |                |           |                |               |                |      |

| Operating input voltage                    | VDD-VSS        | VDS1      | 2.0            |               | 16             | V    |

| DETECTION VOLTAGE                          |                |           |                |               |                |      |

| Overcharge detection voltage               |                | VOCU      | VOCU<br>-0.055 | VOCU          | VOCU<br>+0.045 | ٧    |

| Auxiliary overcharge detection Voltage 1,2 |                | VCUAUX1,2 | VOCU*<br>1.19  | VOCU*<br>1.25 | VOCU*<br>1.31  |      |

| Overcharge release voltage                 |                | VOCR      | VOCR<br>-0.080 | VOCR          | VOCR<br>+0.070 | ٧    |

| Over-discharge detection voltage           |                | VODL      | VODL<br>-0.110 | VODL          | VODL<br>+0.100 | ٧    |

| Over-discharge release voltage             |                | VODR      | VODR<br>-0.130 | VODR          | VODR<br>+0.120 | ٧    |

| Over current detection voltage 1           |                | VOI1      | VOI1<br>-0.033 | VOI1          | VOI1<br>+0.033 | ٧    |

| Over current detection voltage 2           | VSS reference  | VOI2      | 0.4            | 1.0           | 1.6            | ٧    |

| DELAY TIME(C3=0.22μF)                      |                |           |                |               |                |      |

| Overcharge detection delay time            |                | TOC       |                | 1.00          |                | S    |

| Over-discharge detection delay time        |                | TOD       | 67             | 100           | 141            | ms   |

| Over current detection delay time          |                | TOI1      | 6.3            | 10            | 14.7           | ms   |

| OTHER                                      |                |           |                |               |                |      |

| CO pin output "H" voltage                  |                | Voh1      |                | VDD-0.019     | VDD            | V    |

| DO pin output "H" voltage                  |                | Voh2      |                | VDD-0.003     | VDD            | V    |

| DO pin output "L" voltage                  |                | Vol2      | VSS            | VSS+0.003     |                | V    |

| Resistance between VSS and CO              |                | RCOL      | 0.22           | 0.6           | 2.20           | ΜΩ   |

| Resistance between VDD and VM              |                | RVMD      | 79             | 240           | 878            | kΩ   |

| Resistance between VSS and VM              |                | RVSM      | 387            | 597           | 1491           | kΩ   |

| 0 V battery charge starting voltage        |                | V0CHA     |                | No            |                | V    |

**Rev. 1.0** 9/23

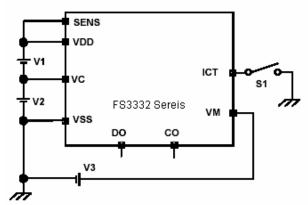

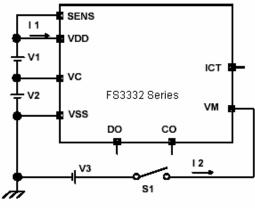

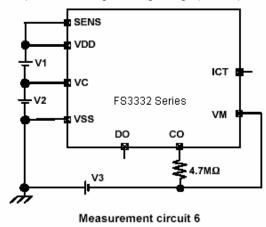

#### 11. Measurement Circuits

#### 11.1 Measurement 1 Measurement Circuit 1

Set S1=OFF, V1=V2=3.6V, and V3=0V under normal condition. Increase V1 from 3.6V gradually. The V1 voltage when CO = 'L' is overcharge detection voltage 1 (VCU1). Decrease V1 gradually. The V1 voltage when CO = 'H' is overcharge release voltage 1 (VCR1). Further decrease V1. The V1 voltage when DO = 'L' is overdischarge detection voltage 1 (VDL1). Increase V1 gradually. The V1 voltage when DO = 'H' is overdischarge release voltage 1 (VDR1). Set S1=ON, and V1=V2=3.6V and V3=0V under normal condition. Increase V1 from 3.6V gradually. The V1 voltage when CO = 'L' is auxiliary overcharge detection voltage 1 (VCUaux1).

Measurement circuit 1

#### 11.2 Measurement 2 Measurement Circuit 1

Set S1=OFF, V1=V2=3.6V, and V3=0V under normal condition. Increase V2 from 3.6V gradually. The V2 voltage when CO = 'L' is overcharge detection voltage 2 (VCU2). Decrease V2 gradually. The V2 voltage when CO = 'H' is overcharge release voltage 2 (VCR2). Further decrease V2. The V2 voltage when DO = 'L' is overdischarge voltage 2 (VDL2). Increase V2 gradually. The V2 voltage when DO = 'H' is overdischarge release voltage 2 (VDR2). Set S1=ON, and V1=V2=3.6V and V3=0V under normal condition. Increase V2 from 3.6V gradually. The V2 voltage when CO = 'L' is auxiliary overcharge detection voltage 2 (VCUaux2).

#### 11.3 Measurement 3 Measurement Circuit 1

Set S1=OFF, V1=V2=3.6V, and V3=0V under normal condition. Increase V3 from 0V gradually. The V3 voltage when DO = 'L' is overcurrent detection voltage 1 (VIOV1). Set S1=ON, V1=V2=3.6V, V3=0 under normal condition. Increase V3 from 0 V gradually. (The voltage change rate < 1.0V/ms) (V1+V2-V3) voltage when DO = 'L' is overcurrent detection voltage 2 (VIOV2).

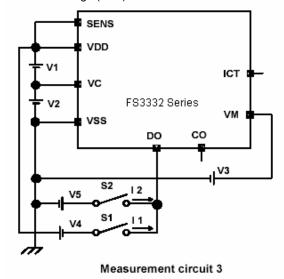

#### 11.4 Measurement 4 Measurement Circuit 2

Set S1=ON, V1=V2=3.6V, and V3=0V under normal condition and measure current consumption. Current consumption I1 is the normal condition current consumption (IDD). Set S1=OFF, V1=V2=1.5V under overdischarge condition and measure current consumption. Current consumption I1 is the power-down current consumption (IPD).

Measurement circuit 2

#### 11.5 Measurement 5 Measurement Circuit 2

Set S1=ON, V1=V2=V3=1.5V, and V3=2.5V under overdischarge condition. (V1+V2-V3)/I2 is the internal resistance between VCC and VM (RVMD). Set S1=ON, V1=V2=3.5V, and V3=1.1V under overcurrent condition. V3/I2 is the internal resistance between VSS and VM (RVSM).

#### 11.6 Measurement 6 Measurement Circuit 3

Set S1=ON, S2=OFF, V1=V2=3.6V, and V3=0V under normal condition. Increase V4 from 0V gradually. The V4 voltage when I1 =  $10\mu$ A is DO 'H' voltage (Voh2). Set S1=OFF, S2=ON, V1=V2=3.6V, and V3=0.5V under overcurrent condition. Increase V5 from 0V gradually. The V5 voltage when I2 =  $10 \mu$ A is the DO 'L' voltage (Vol2).

**Rev. 1.0** 11/23

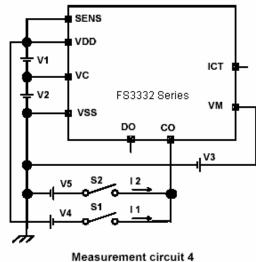

#### 11.7 Measurement 7 Measurement Circuit 4

Set S1=ON, S2=OFF, V1=V2=3.6V and V3=0V under normal condition. Increase V4 from 0V gradually. The V4 voltage when I1 = 10µA is the CO 'H' voltage (Voh1). Set S1=OFF S2=ON, V1=V2=4.7V, V3=0V, and V4=9.4V under over voltage condition. (V5)/I2 is the CO pin internal resistance (RCOL).

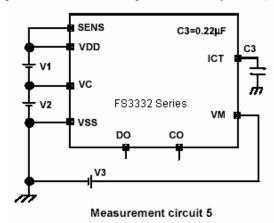

#### 11.8 Measurement 8 Measurement Circuit 5

Set V1=V2=3.6V, and V3=0V under normal condition. Increase V1 from (VCU1-0.2V) to (VCU1+0.2V) immediately (within 10µs). The time after V1 becomes (VCU1+0.2V) until CO goes 'L' is the overcharge detection delay time 1 (tCU1). Set V1=V2=3.5V, and V3=0V under normal condition. Decrease V1 from (VDL1+0.2V) to (VDL1-0.2V) immediately (within 10µs). The time after V1 becomes (VDL1-0.2V) until DO goes 'L' is the overdischarge detection delay time 1 (tDL1).

#### 11.9 Measurement 9 Measurement Circuit 5

Set V1=V2=3.6V, and V3=0V under normal condition. Increase V2 from (VCU2-0.2V) to (VCU2+0.2V) immediately (within 10µs). The time after V2 becomes (VCU2+0.2V) until CO goes 'L' is the overcharge detection delay time 2 (tCU2). Set V1=V2=3.6V, and V3=0V under normal condition. Decrease V2 from (VDL2+0.2V) to (VDL2-0.2V) immediately (within 10µs). The time after V2 becomes (VDL2-0.2V) until DO goes 'L' is the overdischarge detection delay time 2 (tDL2).

Rev. 1.0 12/23

#### 11.10 Measurement 10 Measurement Circuit 5

Set V1=V2=3.6V, and V3=0V under normal condition. Increase V3 from 0V to 0.5V immediately (within  $10\mu s$ ). The time after V3 becomes 0.5V until DO goes 'L' is the overcurrent detection delay time 1 (tIOV1).

# 11.11 Measurement 11 Measurement Circuit 6

Set V1=V2=0V, and V3=2V, and decrease V3 gradually. The V3 voltage when CO = 'L' (VDD-0.3V or lower) is the 0V charge starting voltage (V0CHA).

## 12. Description of Operation

## 12.1 Normal Condition

This IC monitors the voltage of the battery connected between the VDD and VSS pins and the voltage difference between the VM and VSS pins to control charging and discharging. When the voltages of two batteries are in the range from over-discharge detection voltage (VDL1,2) to overcharge detection voltage (VCU1,2), and the VM pin voltage is in the range from the charger detection voltage (VCHA) to over-current detection voltage 1 (VIOV1), the IC turns both the charging and discharging control FETs on. This condition is called the normal status, and in this condition charging and discharging can be carried out freely. The VM and VSS pins are shorted by the RVSM resistor in this condition.

Caution: When the battery is connected for the first time, discharging may not be enabled. In this case, short the VM and VSS pins or connect the charger to restore the normal status.

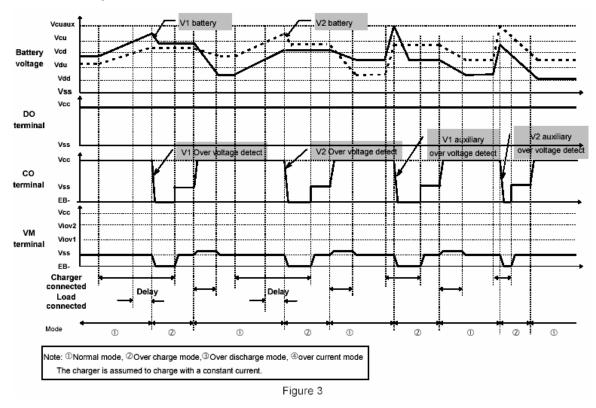

#### 12.2 Overcharge Condition

When one of the battery voltages becomes higher than overcharge detection voltage (VCU1,2) during charging in the normal status and detection continues for the overcharge detection delay time (tCU1,2) or longer, the charging control FET turns off to stop charging. When one of the battery voltages becomes higher than auxiliary overcharge detection voltage (VCUAUX1,2), the charging control FET turns off to stop charging, too. Both conditions are called the overcharge status. The VM and VSS pins are shorted by the RVSM resistor in this condition.

The overcharge status is released in the following two cases (a and b).

- a) The battery voltage which exceeded overcharge detection voltage (VCU1,2) falls below the overcharge release voltage (VCR1,2), the charging control FET turns on and returns to the normal status.

- b) The battery voltage which exceeded overcharge detection voltage (VCU1,2) is equal to or higher than the overcharge release voltage (VCR1,2), the charger is removed, a load is connected and discharging starts, the charging control FET turns on and returns to the normal status. Just after the load is connected and discharging starts, the discharging current flows through the parasitic diode in the charging control FET. At this moment the VM pin potential becomes Vf, the voltage for the parasitic diode, higher than the VSS level. When the battery voltage goes under overcharge detection voltage (VCU1,2) and provided that the VM pin voltage is higher than over-current detection voltage 1, the IC releases the overcharge status and returns to the normal status.

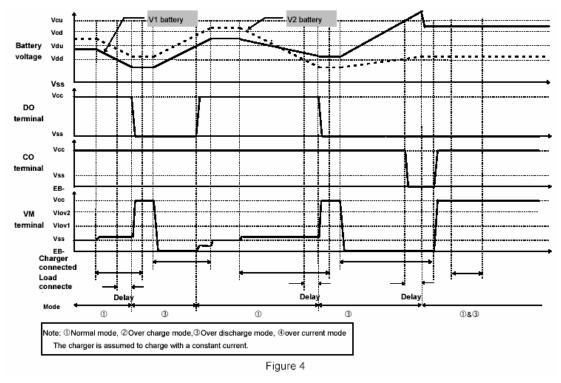

## 12.3 Over-discharge Condition

When one of the battery voltages falls below over-discharge detection voltage (VDL1,2) during discharging in the normal status and detection continues for the over-discharge detection delay time (tDL1,2) or longer, the discharging control FET turns off to stop discharging. This condition is called the over-discharge status. When the discharging control FET is turned off, the VM pin voltage is pulled up by the resistor between the VM and VDD pins in the IC (RVMD). When the voltage difference between the VM and VDD pins then is over-current detection voltage 2 or lower, the current consumption is reduced to the power-down current consumption (IPDN). This condition is called the power-down status. The power-down status is released when a charger is connected and the voltage difference between the VM and VDD pins is over-current detection voltage 2 or higher. Moreover, when all the battery voltages become over-discharge detection voltage (VDL1,2) or higher, the discharging FET turns on and returns to the normal status.

**Rev. 1.0** 14/23

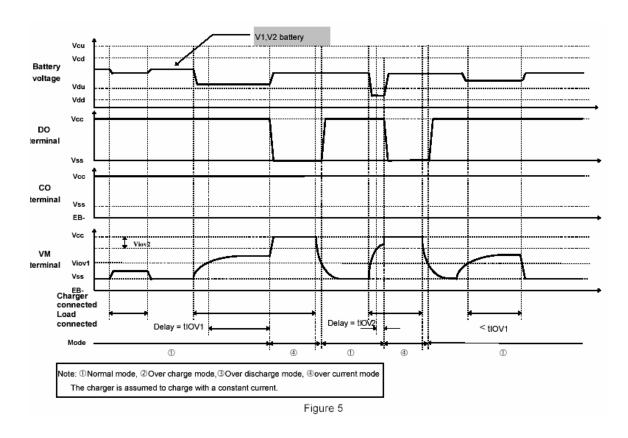

#### 12.4 Over Current Condition

When a battery in the normal status is in the status where the voltage of the VM pin is equal to or higher than the over-current detection voltage because the discharge current is higher than the specified value and the status lasts for the over-current detection delay time, the discharge control FET is turned off and discharging is stopped. This status is called the over-current status. In the over-current status, the VM and VSS pins are shorted by the resistor between VM and VSS (RVSM) in the IC. The charging FET is also turned off. The voltage of the VM pin is at the VDD potential as long as the load is connected. When the load is disconnected, the VM pin returns to the VSS potential. This IC detects the status when the impedance between the EB-pin and EB-pin (see typical application circuit) increases and is equal to the impedance that enables automatic restoration and the voltage at the VM pin returns to over-current detection voltage 1 (VIOV1) or lower and the over-current status is restored to the normal status.

Caution: The impedance that enables automatic restoration varies depending on the battery voltage and the set value of over-current detection voltage 1.

#### 12.5 Delay Circuits

The overcharge detection delay time (tCU1,2), the over-discharge detection delay time (tDL1,2), and the over-current detection delay time 1 (tOl1) are set via an external capacitor (C3). One capacitor determines each delay time, and the delay times are correlated by following ratio:

Overcharge delay time: Over-discharge delay time: Over-current delay time = 100: 10: 1

The delay times are calculated as follows:

Overcharge detection delay time

tCU [s] = delay factor 1 x C3  $[\mu F]$

Delay factor 1 = (2.500 min, 4.545 typ, 9.364 max)

Over-discharge detection delay time

tDL [s] = delay factor 2 x C3 [ $\mu$ F]

Delay factor 2 = (0.3045 min, 0.4545 typ, 0.6409 max)

Over-current detection delay time 1

tIOV1 [s] = delay factor 3 x C3 [ $\mu$ F]

Delay factor 3 = (0.02864 min, 0.04545 typ, 0.06682 max)

Note: The over-current detection delay time 2 is fixed by internal circuit

**Rev. 1.0** 15/23

# 13. Timing Diagram

# 13.1 Overcharge detection

# **Fortune**

# 13.2 Over-discharge detection

**Rev. 1.0** 17/23

## 13.3 Over-current detection

# 14. Typical Characteristics

# 14.1 Detection Voltage Temperature Characteristics

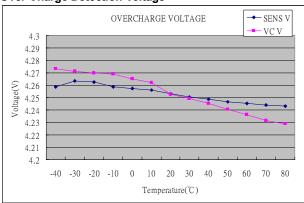

## **Over Charge Detection Voltage**

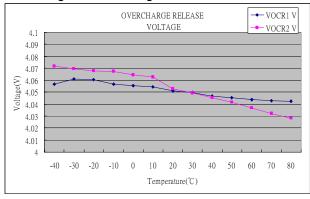

# Over Charge Release Voltage

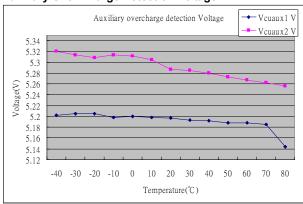

#### **Auxiliary Over Charge Detection Voltage**

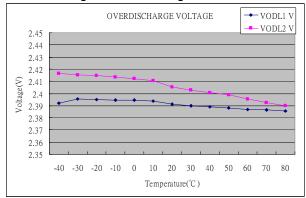

# **Over Dis-Charge Detection Voltage**

# Over Dis-Charge Release Voltage

**Rev. 1.0** 20/23

# 14.2 Delay Time Temperature Characteristics

# **Over Charge Detection Delay Time**

# **Over Dis-Charge Detection Delay Time**

#### **Overcurrent1 Detection Delay Time**

**Rev. 1.0** 21/23

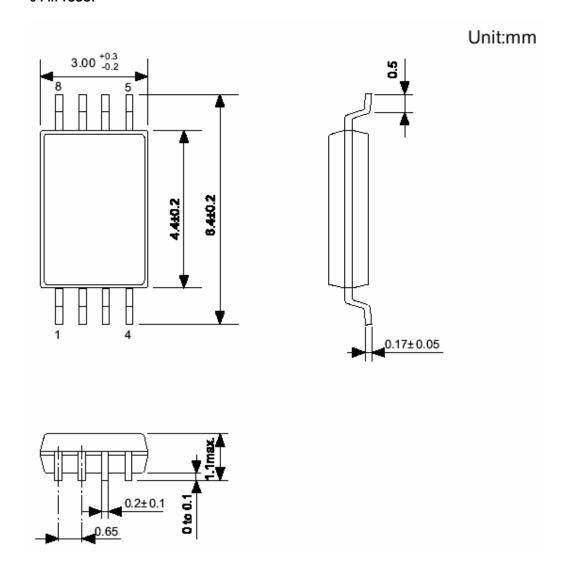

# 15. Package Outline

# 8-Pin TSSOP

Rev. 1.0 22/23

# 16. Revision History

| Version | Date      | Page | Description |

|---------|-----------|------|-------------|

| 1.0     | 2007/1/08 | -    | New Release |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

|         |           |      |             |

**Rev. 1.0** 23/23