## Linear Integrated Systems

| FEATURES                                  |                |  |  |  |  |

|-------------------------------------------|----------------|--|--|--|--|

| SECOND SOURCE FOR SILICONIX VCR11N        |                |  |  |  |  |

| VOLTAGE CONTROLLED RESISTANCE 100 to 200Ω |                |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>     |                |  |  |  |  |

| @ 25 °C (unless otherwise stated)         |                |  |  |  |  |

| Maximum Temperatures                      |                |  |  |  |  |

| Storage Temperature                       | -65 to +150 °C |  |  |  |  |

| Operating Junction Temperature            | -55 to +135 °C |  |  |  |  |

| Maximum Power Dissipation                 |                |  |  |  |  |

| Continuous Power Dissipation              | 300mW          |  |  |  |  |

| Maximum Current                           |                |  |  |  |  |

| Forward Gate Current                      | 10mA           |  |  |  |  |

| Maximum Voltages                          |                |  |  |  |  |

| Gate to Drain Voltage                     | 25V            |  |  |  |  |

| Gate to Source Voltage                    | 25V            |  |  |  |  |

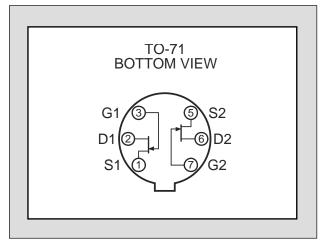

## VCR11N

## N-CHANNEL JFET VOLTAGE CONTROLLED RESISTOR

\*Contact the factory for surface mount package options and pin outs.

## ELECTRICAL CHARACTERISTICS @ 25 °C (unless otherwise stated)

| SYMBOL               | CHARACTERISTIC                                | MIN  | TYP | MAX  | UNITS | CONDITIONS                                      |

|----------------------|-----------------------------------------------|------|-----|------|-------|-------------------------------------------------|

| $BV_{GSS}$           | Gate to Source Breakdown Voltage              | -25  |     |      | V     | $I_G = -1\mu A$ , $V_{DS} = 0V$                 |

| $V_{GS(off)}$        | Gate to Source Cutoff Voltage                 | -8   |     | -12  | V     | $I_D = 1\mu A, V_{DS} = 10V$                    |

| I <sub>GSS</sub>     | Gate Reverse Current                          |      |     | -0.2 | nA    | $V_{GS} = -15V, V_{DS} = 0V$                    |

| r <sub>ds(on)</sub>  | Dynamic Drain to Source<br>On Resistance      | 100  |     | 200  | Ω     | $V_{GS} = 0V, I_D = 0A, f = 1kHz$               |

| r <sub>DS(min)</sub> | Static Drain to Source<br>On Resistance Ratio | 0.95 |     | 1    |       | $V_{DS} = 100 \text{mV}, r_{DS} = 200 \Omega^2$ |

| r <sub>DS(max)</sub> |                                               | 0.95 |     | 1    |       | $V_{GS1} = V_{GS2}, r_{DS} = 2k\Omega^2$        |

| $C_{\sf dgo}$        | Drain to Gate Capacitance                     |      |     | 8    | pF    | $V_{GD} = -10V$ , $I_{S} = 0A$ , $f = 1MHz$     |

| $C_{sgo}$            | Source to Gate Capacitance                    |      |     | 8    | pF    | $V_{GS} = -10V$ , $I_{D} = 0A$ , $f = 1MHz$     |

- 1. Absolute maximum ratings are limiting values above which serviceability may be impaired.

- 2.  $V_{GS1}$  + Control Voltage necessary to force  $r_{DS}$  to  $200\Omega$  or  $2k\Omega$ .

Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.