www.DataSheet4U.com

LTC3589

## 8-Output Regulator with Sequencing and I<sup>2</sup>C

## **FEATURES**

- Triple I<sup>2</sup>C Adjustable High Efficiency Step-Down Switching Regulators: 1.6A, 1A, 1A

- High Efficiency 1.2A Buck-Boost Switching Regulator

- Triple 250mA LDO Regulators

- Always Alive 25mA LDO Regulator

- Flexible Pin-Strap Sequencing Operation

- I<sup>2</sup>C and Independent Enable Control Pins

- Power Good and Reset Outputs

- Dynamic Voltage Scaling and Slew Rate Control

- Selectable 2.25MHz or 1.12MHz Switching Frequency

- Pushbutton ON/OFF Control with System Reset

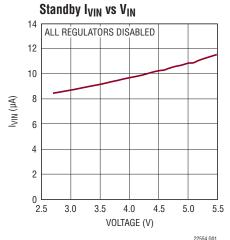

- 10µA Standby Current

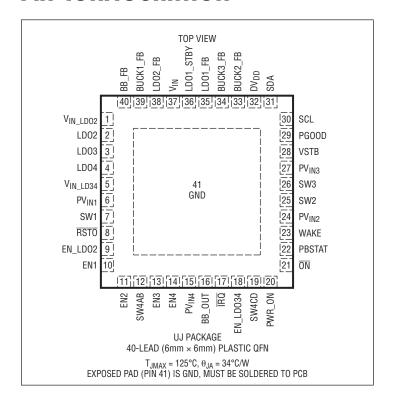

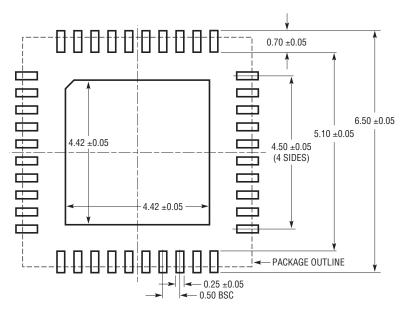

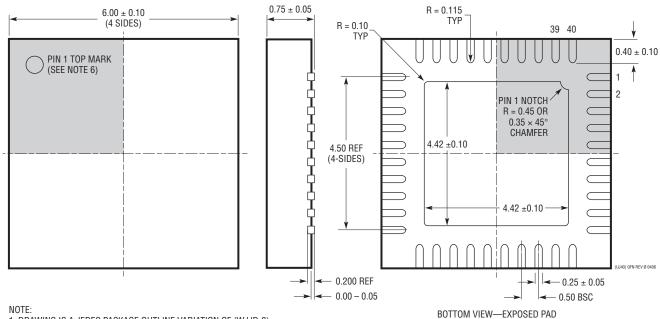

- 40-Pin 6mm × 6mm × 0.75mm QFN

## **APPLICATIONS**

- Handheld Instruments and Scanners

- Portable Industrial Devices

- Automotive Infotainment

- Portable Medical Devices

- High End Consumer Devices

- Multirail Systems

- Supports Freescale i.MX, Marvell PXA and Other Application Processors

### DESCRIPTION

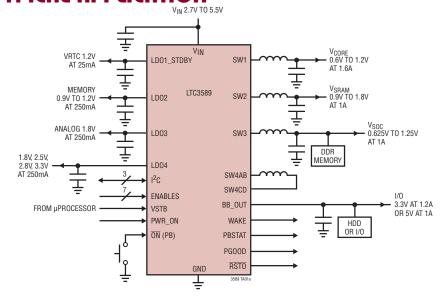

The LTC®3589 is a complete power management solution for ARM and ARM-based processors and advanced portable microprocessor systems. The device contains three synchronous step-down DC/DC converters for core, memory and SoC rails, a synchronous buck-boost regulator for I/O at 3.3V to 5V, and three 250mA LDO regulators for low noise analog supplies. An I<sup>2</sup>C serial port is used to control regulator enables, output voltage levels. dynamic voltage scaling and slew rate, operating modes and status reporting. Regulator start-up is sequenced by connecting regulator outputs to enable pins in the desired order or via the I<sup>2</sup>C port. System power-on, power-off and reset functions are controlled by pushbutton interface, pin inputs, or I<sup>2</sup>C interface. The LTC3589 supports i.MX, PXA and OMAP processors with eight independent rails at appropriate power levels, dynamic control and sequencing. Other features include interface signals such as the VSTB pin that toggles between programmed run and standby output voltages on up to four rails simultaneously. The device is available in a low profile 40-pin 6mm × 6mm exposed pad QFN package.

7, LT, LTC, LTM, Burst Mode, Linear Technology and the Linear logo are registered trademarks, Hot Swap and Bat-track are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

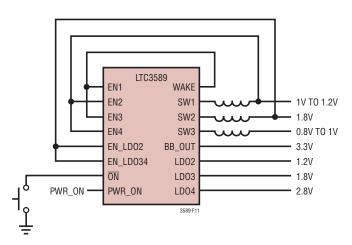

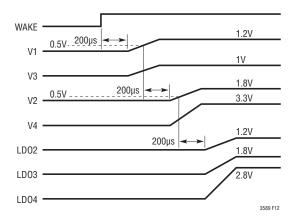

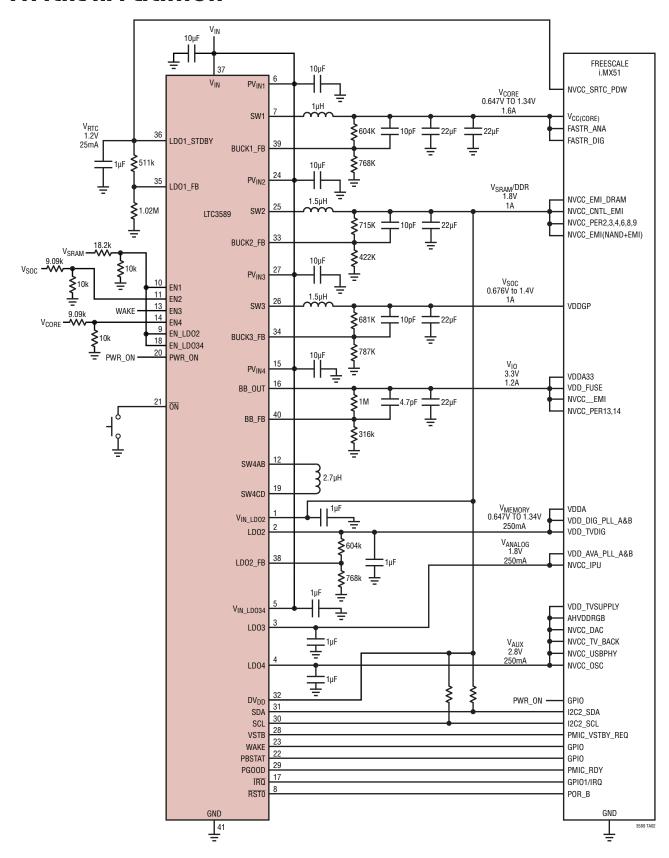

## TYPICAL APPLICATION

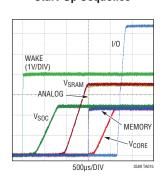

#### Start-Up Sequence

# LTC3589

## TABLE OF CONTENTS

| Features                                 |    |

|------------------------------------------|----|

| Applications                             |    |

| Typical Application                      |    |

| Description                              |    |

| Absolute Maximum Ratings                 |    |

| Pin Configuration                        |    |

| Order Information                        |    |

| Electrical Characteristics               |    |

| Typical Performance Characteristics      |    |

| Pin Functions                            | 12 |

| Block Diagram                            | 14 |

| Operation                                | 15 |

| Introduction                             | 15 |

| Always-On LDO                            | 16 |

| 250mA LDO Regulators                     | 16 |

| Step-Down Switching Regulators           | 18 |

| Buck-Boost Switching Regulator           | 22 |

| Slewing DAC Reference Operation          | 26 |

| Pushbutton Operation                     |    |

| Enable and Power-On Sequencing           | 29 |

| Fault Detection, Shutdown, and Reporting |    |

| I <sup>2</sup> C Operation               | 32 |

| Thermal Considerations and Board Layout  | 38 |

| Applications Information                 |    |

| Typical Application                      |    |

| Package Description                      | 43 |

| Typical Application                      | 44 |

| Related Parts                            | 44 |

## **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 3)

SW1, SW2, SW3, SW4AB, SW4CD (Transients < 1ms, Duty Cycle < 1%) .......-0.3V to 7V  $PV_{IN1}$ ,  $PV_{IN2}$ ,  $PV_{IN3}$ ,  $PV_{IN4}$ ......-0.3V to  $V_{IN}$  + 0.3V  $V_{IN\_LD02}$ ,  $V_{IN\_LD034}$ ......-0.3V to  $V_{IN}$  + 0.3V  $V_{IN}$ ,  $DV_{DD}$ .....-0.3V to 6V LD01\_STBY,LD01\_FB,BUCK1\_FB,BUCK2\_FB,BUCK3\_FB, BB\_FB, BB\_OUT, LD02, LD02\_FB,LD03, LD04, PG00D,

VSTB, EN1, EN2, EN3, EN4, EN\_LD02, EN\_LD034,  $\overline{\text{ON}}$ , PBSTAT, WAKE, RSTO, PWR\_ON, IRQ, ......-0.3V to 6V SDA, SCL .....-0.3V to DV<sub>DD</sub> to 0.3V Operating Junction Temperature Range (Note 2).....-40°C to 150°C Storage Temperature Range .....-65°C to 150°C

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC3589EUJ#PBF   | LTC3589EUJ#TRPBF | 3589          | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589IUJ#PBF   | LTC3589IUJ#TRPBF | 3589          | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3589HUJ#PBF   | LTC3589HUJ#TRPBF | 3589          | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

## LTC3589

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                                                   | CONDITIONS                                                 |   | MIN   | TYP       | MAX       | UNITS    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---|-------|-----------|-----------|----------|

| $\overline{V_{IN}}$  | Operating Input Supply Voltage, V <sub>IN</sub>                                                                             |                                                            | • | 2.7   |           | 5.5       | V        |

| I <sub>VINLD01</sub> | V <sub>IN</sub> Quiescent Current                                                                                           | All Enables = 0V                                           | • |       | 10        | 17        | μА       |

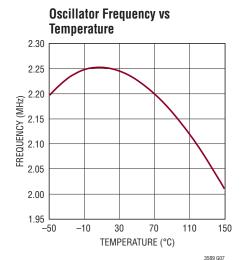

| f <sub>OSC</sub>     | Oscillator Frequency                                                                                                        |                                                            | • | 1.9   | 2.25      | 2.6       | MHz      |

| Step Down            | Switching Regulators 1, 2, and 3                                                                                            |                                                            |   |       |           |           |          |

| I <sub>VIN</sub>     | Pulse-Skipping Mode V <sub>IN</sub> Quiescent Current<br>Per Buck<br>Burst Mode® V <sub>IN</sub> Quiescent Current Per Buck | V <sub>FB</sub> = 0.85V (Note 5)                           | • |       | 135<br>27 | TBD<br>40 | μA<br>μA |

| I <sub>FB</sub>      | Feedback Pin Input Current                                                                                                  | V <sub>FB</sub> = 0.8V                                     |   | -0.1  | LI        | 0.1       | μΑ       |

| DX                   | Maximum Duty Cycle                                                                                                          | V <sub>FB</sub> = 0V                                       |   | 100   |           |           | %        |

| R <sub>SW</sub>      | SW Pull-Down Resistance                                                                                                     | Regulators Disabled                                        |   |       | 2000      |           | Ω        |

| t <sub>SS</sub>      | Soft-Start Rate                                                                                                             | (Note 6)                                                   |   |       | 2         |           | V/ms     |

| $V_{FB(MAX)}$        | Maximum Feedback Voltage                                                                                                    | BxDTV1 = BxDTV2 = 11111,<br>V <sub>IN</sub> = 2.7V to 5.5V | • | 0.735 | 0.75      | 0.765     | V        |

| V <sub>FB(LSB)</sub> | Feedback LSB Step Size                                                                                                      |                                                            |   |       | 12.5      |           | mV       |

| V <sub>FB(MIN)</sub> | Minimum Feedback Voltage                                                                                                    | BxDTV1 = BxDTV2 = 00000,<br>V <sub>IN</sub> = 2.7V to 5.5V | • | 0.351 | 0.3625    | 0.374     | V        |

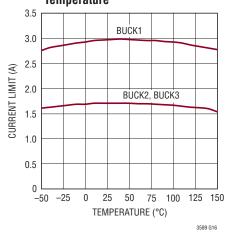

| 1.6A Step D          | own Switching Regulator 1 (Buck 1)                                                                                          |                                                            |   |       |           |           |          |

| I <sub>LIM1</sub>    | Peak PMOS Current Limit SW1                                                                                                 |                                                            | • | 2.2   | 2.7       |           | A        |

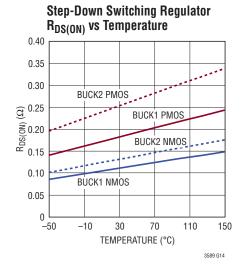

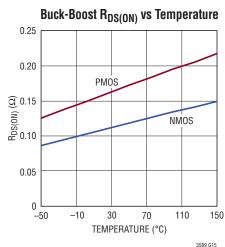

| RP1                  | R <sub>DS(ON)</sub> of PMOS1                                                                                                | I <sub>SW1</sub> = 100mA                                   |   |       | 180       |           | mΩ       |

| RN1                  | R <sub>DS(ON)</sub> of NMOS1                                                                                                | I <sub>SW1</sub> = 100mA                                   |   |       | 110       |           | mΩ       |

| 1.0A Step D          | own Switching Regulators 2 and 3                                                                                            |                                                            |   |       |           |           |          |

| I <sub>LIM2, 3</sub> | Peak PMOS Current Limit SW2                                                                                                 |                                                            | • | 1.5   | 1.9       |           | A        |

| RP2, 3               | R <sub>DS(ON)</sub> of PMOS3                                                                                                |                                                            |   |       | 250       |           | mΩ       |

| RN2, 3               | R <sub>DS(ON)</sub> of NMOS3                                                                                                |                                                            |   |       | 130       |           | mΩ       |

| 1.2A Buck-E          | Boost Switching Regulator 4 (Buck-Boost)                                                                                    |                                                            |   |       |           |           |          |

| I <sub>VIN</sub>     | PWM Mode V <sub>IN</sub> Quiescent Current<br>Burst Mode V <sub>IN</sub> Quiescent Current                                  | V <sub>BB_FB</sub> = 0.85V                                 | • |       |           | 130<br>19 | μA<br>μA |

| $V_{BB\_FB}$         | Feedback Voltage                                                                                                            | $V_{IN} = 2.7V$ to 5.5V, $V_{OUT} = 5.5V$                  | • | 0.776 | 0.8       | 0.824     | V        |

| $V_{OUTBB}$          | Output Voltage Range                                                                                                        |                                                            |   | 1.8   |           | 5.0       | V        |

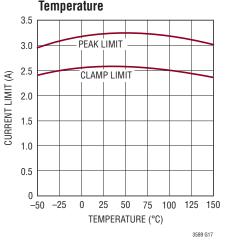

| I <sub>LIM4</sub>    | Peak PMOS Current Limit SW4AB                                                                                               |                                                            | • | 2.5   | 2.7       |           | A        |

| I <sub>PEAK4</sub>   | Forward Burst Current Limit (Switch A)                                                                                      | Burst Mode Operation                                       |   |       | 500       |           | mA       |

| I <sub>LIMR4</sub>   | Reverse Current Limit (Switch D)                                                                                            |                                                            |   |       | 800       |           | mA       |

| I <sub>ZER04</sub>   | Reverse Burst Current Limit (Switch D)                                                                                      | Burst Mode Operation                                       |   |       | 0         |           | mA       |

| RP4                  | R <sub>DS(ON)</sub> of Switch A and Switch D                                                                                | $I_{SW4AB} = I_{SW4CD} = 100$ mA                           |   |       | 160       |           | mΩ       |

| RN4                  | R <sub>DS(ON)</sub> of Switch B and Switch C                                                                                | $I_{SW4AB} = I_{SW4CD} = -100$ mA                          |   |       | 110       |           | mΩ       |

| R <sub>OUT4</sub>    | BB_OUT Pull-Down Resistance                                                                                                 | Regulator Disabled                                         |   |       | 2000      |           | Ω        |

| t <sub>SS</sub>      | Soft-Start Rate                                                                                                             | (Note 6)                                                   |   |       | 2         |           | V/ms     |

| I <sub>FB</sub>      | Feedback Pin Input Current                                                                                                  | V <sub>FB</sub> = 0.85V                                    |   | -0.1  |           | 0.1       | μA       |

|                      |                                                                                                                             |                                                            |   |       |           |           |          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                         | CONDITIONS                                                                                                                              |   | MIN   | TYP     | MAX             | UNITS    |

|------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|-------|---------|-----------------|----------|

| LDO Regulat            | tors                                                                              |                                                                                                                                         |   |       |         |                 |          |

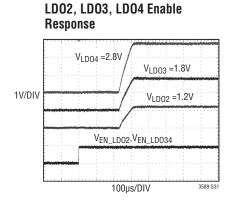

| t <sub>LDO_SS</sub>    | Soft-Start Time LD02, LD03, LD04                                                  |                                                                                                                                         |   |       | 100     |                 | μs       |

| R <sub>LDO_PD</sub>    | Output Pull-Down Resistance LD02, LD03, LD04                                      | LDO Disabled                                                                                                                            |   |       | 2000    |                 | Ω        |

| Always-On F            | Regulator (LDO1_STDBY)                                                            |                                                                                                                                         |   |       |         |                 |          |

| V <sub>LD01_FB</sub>   | LDO1 Feedback Voltage                                                             |                                                                                                                                         | • | 0.76  | 0.8     | 0.84            | V        |

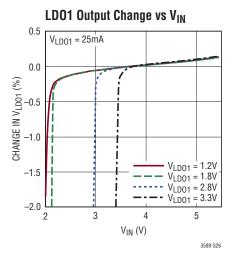

| V <sub>LD01</sub>      | LD01 Line Regulation                                                              | $\begin{split} &I_{LD01\_STBY} = 1 \text{mA, LD01\_STBY} = 3.3 \text{V,} \\ &V_{\text{IN}} = 2.7 \text{V to } 5.5 \text{V} \end{split}$ |   |       | 0.2     |                 | %/V      |

|                        | LDO1 Load Regulation                                                              | I <sub>LD01</sub> = 0.1mA to 25mA,<br>LD01_STBY = 3.3V                                                                                  |   |       | 0.2     |                 | %        |

| I <sub>LD01</sub>      | Available Output Current                                                          |                                                                                                                                         | • | 25    |         |                 | mA       |

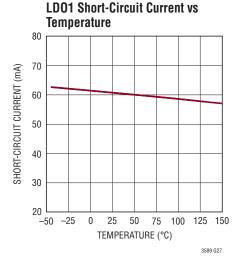

| I <sub>LD01_SC</sub>   | Short Circuit Output Current Limit                                                |                                                                                                                                         |   |       | 65      | 100             | mA       |

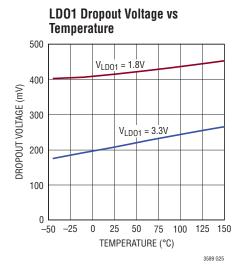

| V <sub>DROP1</sub>     | Dropout Voltage (Note 4)                                                          | $I_{LDO1} = 25 \text{mA}, LDO1\_STBY = 3.3V$                                                                                            |   |       | 180     | 280             | mV       |

| I <sub>LD01_FB</sub>   | LDO1_FB Input Current                                                             | $V_{LD01\_FB} = 0.85V$                                                                                                                  |   | -0.1  |         | 0.1             | μA       |

| LDO Regulat            | tor 2 (LDO2)                                                                      |                                                                                                                                         |   |       |         |                 |          |

| $V_{IN\_LD02}$         | V <sub>IN_LDO2</sub> Input Voltage Range                                          |                                                                                                                                         | • | 1.7   |         | $V_{IN}$        | V        |

| I <sub>VIN_LD02</sub>  | V <sub>IN_LDO2</sub> Quiescent Current<br>V <sub>IN_LDO2</sub> Shutdown Current   | EN_LD02 = High, LD02_FB = 0.85V<br>EN_LD02 = Low                                                                                        | • |       | 14<br>0 | 19<br>1         | μA<br>μA |

| I <sub>VIN</sub>       | V <sub>IN</sub> Quiescent Current                                                 | EN_LD02 = High                                                                                                                          | • |       | 50      | 80              | μA       |

| V <sub>FB2(MAX)</sub>  | LDO2 Maximum Feedback Voltage                                                     | L2DTV1 = L2DTV2 = 11111                                                                                                                 | • | 0.735 | 0.75    | 0.765           | V        |

| V <sub>FB2(LSB)</sub>  | LDO2 Feedback LSB Step Size                                                       |                                                                                                                                         |   |       | 12.5    |                 | mV       |

| V <sub>FB2(MIN)</sub>  | LDO2 Minimum Feedback Voltage                                                     | L2DTV1 = L2DTV2 = 00000<br>$V_{IN\_LD02} = V_{IN} = 2.7V$ to 5.5V,<br>$I_{LD02} = 1mA$                                                  | • | 0.351 | 0.3625  | 0.373           | V        |

|                        | LDO2 Line Regulation                                                              | I <sub>LDO2</sub> =1mA, V <sub>INLDO2</sub> = 2.7V to 5.5V                                                                              |   |       | 0.1     |                 | %/V      |

|                        | LDO2 Load Regulation                                                              | I <sub>LD02</sub> = 1mA to 250mA                                                                                                        |   |       | 0.1     |                 | %        |

| I <sub>OUT2</sub>      | LDO2 Available Output Current                                                     |                                                                                                                                         | • | 250   |         |                 | mA       |

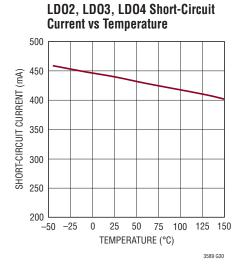

| I <sub>SC2</sub>       | LDO2 Short-Circuit Current Limit                                                  |                                                                                                                                         |   | 300   | 420     | 600             | mA       |

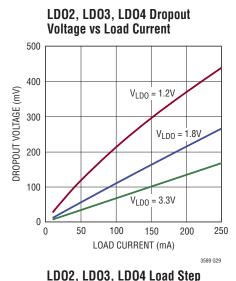

| $V_{DROP2}$            | Dropout Voltage (Note 4)                                                          | I <sub>LD02</sub> = 200mA, V <sub>LD02</sub> = 2.5V                                                                                     |   |       | 130     | 180             | mV       |

|                        |                                                                                   | $I_{LD02} = 200 \text{mA}, V_{LD02} = 1.2 \text{V}$                                                                                     |   |       | 330     | 500             | mV       |

| I <sub>LD02_FB</sub>   | LDO2_FB Input Current                                                             | $V_{LD02\_FB} = 0.8V$                                                                                                                   |   | -0.1  |         | 0.1             | μA       |

| LDO Regulat            | tor 3 (LDO3)                                                                      |                                                                                                                                         |   |       |         |                 |          |

| V <sub>IN_LD034</sub>  | V <sub>IN_LD034</sub> Input Range                                                 |                                                                                                                                         | • | 2.35  |         | V <sub>IN</sub> | V        |

| I <sub>VIN_LD034</sub> | V <sub>IN_LD034</sub> Quiescent Current<br>V <sub>IN_LD034</sub> Shutdown Current | EN_LD03 = High, LD03_FB = 0.85V<br>Regulator Disabled                                                                                   | • |       | 14<br>0 | 24<br>1         | μA<br>μA |

| I <sub>VIN</sub>       | V <sub>IN</sub> Quiescent Current                                                 |                                                                                                                                         | • |       | 50      | 80              | μA       |

| V <sub>LD03</sub>      | LD03 Output Voltage                                                               | $V_{IN\_LD034} = V_{IN} = 2.7V \text{ to 5V},$<br>$I_{LD03} = 1\text{mA}$                                                               | • | 1.746 | 1.8     | 1.854           | V        |

|                        | LD03 Line Regulation                                                              | $I_{LDO3} = 1 \text{mA}, V_{INLDO34} = 2.7 \text{V to } 5.5 \text{V}$                                                                   |   |       | 0.1     |                 | %/V      |

|                        | LD03 Load Regulation                                                              | I <sub>LD03</sub> = 1mA to 250mA                                                                                                        |   |       | 0.1     |                 | %        |

| I <sub>LD03</sub>      | LDO3 Available Output Current                                                     |                                                                                                                                         | • | 250   |         |                 | mA       |

| I <sub>LD03_SC</sub>   | LDO3 Short-Circuit Current Limit                                                  |                                                                                                                                         |   | 300   | 420     | 600             | mA       |

| V <sub>DROP3</sub>     | LDO3 Dropout Voltage (Note 4)                                                     | I <sub>LD03</sub> = 200mA, V <sub>LD03</sub> = 1.8V                                                                                     |   |       | 180     | 250             | mV       |

## LTC3589

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                                               | PARAMETER                                                                         | CONDITIONS                                                                                                 |   | MIN                              | TYP                      | MAX                              | UNITS                                  |

|------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---|----------------------------------|--------------------------|----------------------------------|----------------------------------------|

| LDO Regulato                                         | r 4 (LDO4)                                                                        |                                                                                                            |   |                                  |                          |                                  |                                        |

| V <sub>IN_LD034</sub>                                | V <sub>IN_LDO34</sub> Input Range                                                 |                                                                                                            | • | 2.35                             |                          | V <sub>IN</sub>                  | V                                      |

| I <sub>VIN_LD034</sub>                               | V <sub>IN_LD034</sub> Quiescent Current<br>V <sub>IN_LD034</sub> Shutdown Current | LDO4 Enabled, LDO4_FB = 0.85V<br>LDO4 Disabled                                                             | • |                                  | 14<br>0                  | 22<br>1                          | μA<br>μA                               |

| I <sub>VIN</sub>                                     | Enabled V <sub>IN</sub> Quiescent Current                                         |                                                                                                            | • |                                  | 50                       | 80                               | μА                                     |

| V <sub>LD04</sub>                                    | LDO 4 Output Voltage                                                              | I <sub>LD04</sub> = 1mA, L2DTV2[6:5] = 00<br>L2DTV2[6:5] = 01<br>L2DTV2[6:5] = 10<br>L2DTV2[6:5] = 11      | • | 2.716<br>2.245<br>1.746<br>3.201 | 2.8<br>2.5<br>1.8<br>3.3 | 2.884<br>2.575<br>1.854<br>3.399 | V<br>V<br>V                            |

|                                                      | LD04 Line Regulation                                                              | $I_{LDO4} = 1$ mA, $V_{INLDO4} = 2.7$ V to 5.5V, $V_{OUT} = 1.8$ V                                         |   |                                  | 0.1                      |                                  | %/V                                    |

|                                                      | LDO4 Load Regulation                                                              | I <sub>LD04</sub> = 1mA to 250mA                                                                           |   |                                  | 0.1                      |                                  | %                                      |

| I <sub>LD04</sub>                                    | LDO4 Available Output Current                                                     |                                                                                                            | • | 250                              |                          |                                  | mA                                     |

| I <sub>LD04_SC</sub>                                 | LDO4 Short Circuit Current Limit                                                  |                                                                                                            |   | 300                              | 420                      | 600                              | mA                                     |

| V <sub>DROP4</sub>                                   | LDO4 Dropout Voltage (Note 4)                                                     | $I_{LD04} = 200 \text{mA}, V_{LD04} = 3.3 \text{V}$<br>$I_{LD04} = 200 \text{mA}, V_{LD04} = 1.8 \text{V}$ |   |                                  | 100<br>180               | 130<br>250                       | mV<br>mV                               |

| <b>Enable Inputs</b>                                 |                                                                                   |                                                                                                            |   |                                  |                          |                                  |                                        |

| $V_{ENx\_THR}$                                       | Threshold Rising, All Enables Low                                                 |                                                                                                            | • |                                  | 0.8                      | 1.2                              | V                                      |

| V <sub>ENx_THR2</sub><br>V <sub>ENx_THF2</sub>       | Threshold Rising, Any Enable High<br>Threshold Falling, Any Enable High           |                                                                                                            | • | 0.425                            | 0.5<br>0.45              | 0.525                            | V                                      |

| R <sub>ENX</sub>                                     | Input Pull-Down Resistance                                                        |                                                                                                            |   |                                  | 4.5                      |                                  | MΩ                                     |

| VSTB, PWR_0                                          | ON Inputs                                                                         |                                                                                                            |   |                                  |                          |                                  |                                        |

| V <sub>VSTB_THR</sub><br>V <sub>VSTB_THF</sub>       | VSTB Pin Threshold Rising<br>VSTB Pin Threshold Falling                           |                                                                                                            | • | 0.4                              | 0.8<br>0.7               | 1.2                              | V                                      |

| R <sub>VSTB</sub>                                    | Pull-Down Resistence                                                              |                                                                                                            |   |                                  | 4.5                      |                                  | MΩ                                     |

| V <sub>PWR_ONTHR</sub><br>V <sub>PWR_ONTHF</sub>     | PWR_ON Pin Threshold Rising PWR_ON Pin Threshold Falling                          |                                                                                                            | • | 0.4                              | 0.8<br>0.7               | 1.2                              | V                                      |

| R <sub>PWR_ON</sub>                                  | Pull-Down Resistence                                                              |                                                                                                            |   |                                  | 4.5                      |                                  | MΩ                                     |

| I <sup>2</sup> C Port                                |                                                                                   |                                                                                                            |   |                                  |                          |                                  |                                        |

| $DV_DD$                                              | DV <sub>DD</sub> Input Supply Voltage                                             |                                                                                                            |   | 1.6                              |                          | 5.5                              | V                                      |

| I <sub>DVDD</sub>                                    | DV <sub>DD</sub> Quiescent Current                                                | SCL/SDA = 0kHz                                                                                             |   |                                  | 0.3                      |                                  | μA                                     |

| $V_{DVDD\_UVLO}$                                     | DV <sub>DD</sub> UVLO Level                                                       |                                                                                                            |   |                                  | 1                        |                                  | V                                      |

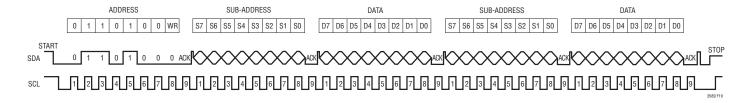

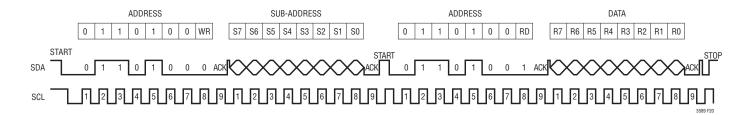

| ADDRESS                                              | LTC3589 Device Address – Write<br>LTC3589 Device Address – Read                   |                                                                                                            |   |                                  | 01101000<br>01101001     |                                  |                                        |

| V <sub>IH</sub> SDA, SCL<br>V <sub>IL</sub> SDA, SCL | SDA and SCL Input Threshold Rising<br>SDA and SCL Input Threshold Falling         |                                                                                                            |   | 70                               |                          | 30                               | %DV <sub>DD</sub><br>%DV <sub>DD</sub> |

| I <sub>IHSCx</sub> I <sub>ILSCx</sub>                | SDA and SCL Input Current                                                         | SDA = SCL = 0V to 5.5V                                                                                     |   | -1                               |                          | 1                                | μA                                     |

| $V_{OL}$ SDA                                         | SDA Output Low Voltage                                                            | I <sub>SDA</sub> = 3mA                                                                                     |   |                                  |                          | 0.4                              | V                                      |

| f <sub>SCL</sub>                                     | SCL Clock Operating Frequency                                                     |                                                                                                            |   |                                  |                          | 400                              | kHz                                    |

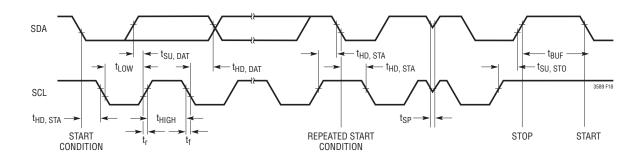

| t <sub>BUF</sub>                                     | Bus Free Time Between Stop and Start<br>Condition                                 |                                                                                                            |   | 1.3                              |                          |                                  | μѕ                                     |

| t <sub>HD_STA</sub>                                  | Hold Time After (Repeated) Start Condition                                        |                                                                                                            |   | 0.6                              |                          |                                  | μs                                     |

| t <sub>SU_STA</sub>                                  | Repeated Start Condition Setup Time                                               |                                                                                                            |   | 0.6                              |                          |                                  | μs                                     |

| t <sub>SU_STO</sub>                                  | Stop Condition Setup Time                                                         |                                                                                                            |   | 0.6                              |                          |                                  | μs                                     |

| t <sub>HD_DAT(0)</sub>                               | Data Hold Time Output                                                             |                                                                                                            |   | 0                                |                          | 900                              | ns                                     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_LD02} = V_{IN\_LD034} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| SYMBOL                           | PARAMETER                                                             | CONDITIONS                                                          |   | MIN                    | TYP          | MAX | UNITS    |

|----------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|---|------------------------|--------------|-----|----------|

| t <sub>HD_DAT(I)</sub>           | Data Hold Time Input                                                  |                                                                     |   | 0                      |              |     | ns       |

| t <sub>SU_DAT</sub>              | Data Setup Time                                                       |                                                                     |   | 100                    |              |     | ns       |

| $t_{LOW}$                        | SCL Clock Low Period                                                  |                                                                     |   | 1.3                    |              |     | μs       |

| t <sub>HIGH</sub>                | SCL Clock High Period                                                 |                                                                     |   | 0.6                    |              |     | μs       |

| t <sub>f</sub>                   | Clock/Data Fall Time                                                  | C <sub>B</sub> = Capacitance of One BUS Line (pF)                   |   | 20 + 0.1C <sub>B</sub> |              | 300 | ns       |

| t <sub>r</sub>                   | Clock/Data Rise Time                                                  | C <sub>B</sub> = Capacitance of One BUS Line (pF)                   |   | 20 + 0.1C <sub>B</sub> |              | 300 | ns       |

| t <sub>SP</sub>                  | Input Spike Supression Pulse Width                                    |                                                                     |   |                        |              | 50  | ns       |

| Pushbutton I                     | nterface                                                              | ·                                                                   |   |                        |              |     |          |

| V <sub>ON_TH</sub>               | ON Threshold Rising ON Threshold Falling                              |                                                                     | • | 0.4                    | 0.8<br>0.7   | 1.2 | V        |

| I <sub>ON</sub>                  | ON Input Current                                                      | $\frac{\overline{ON}}{\overline{ON}} = V_{IN}$ $\overline{ON} = 0V$ |   | -1                     | 40           | 1   | μA<br>μA |

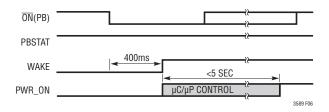

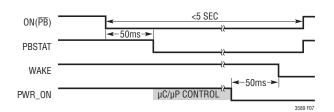

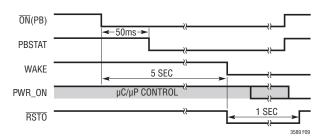

| ton_pbstat1                      | ON Low Time to PBSTAT Low                                             |                                                                     |   |                        | 50           |     | ms       |

| t <sub>ON_PBSTAT2</sub>          | ON High Time to PBSTAT High                                           |                                                                     |   |                        | 0.2          |     | μs       |

| t <sub>on_wake</sub>             | ON Low Time to WAKE High                                              |                                                                     |   |                        | 400          |     | ms       |

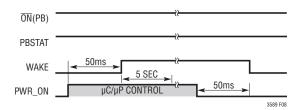

| t <sub>ON_HR</sub>               | ON Low time to Hard Reset                                             |                                                                     |   |                        | 5            |     | S        |

| t <sub>PBSTAT_PW</sub>           | PBSTAT Minimum Pulse Width                                            |                                                                     |   |                        | 50           |     | ms       |

| t <sub>PBSTAT_BK</sub>           | PBSTAT Blanking from WAKE Low                                         |                                                                     |   |                        | 1            |     | S        |

| t <sub>WAKE_OFF</sub>            | Minimum WAKE Low Time                                                 |                                                                     |   |                        | 1            |     | S        |

| t <sub>WAKE_ON</sub>             | WAKE High Time with PWR_ON = 0V                                       |                                                                     |   |                        | 5            |     | S        |

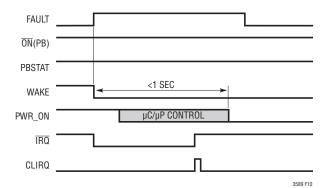

| t <sub>PWR_ON</sub>              | PWR_ON High to WAKE High                                              |                                                                     |   |                        | 50           |     | ms       |

| t <sub>PWR_OFF</sub>             | PWR_ON Low WAKE Low                                                   |                                                                     |   |                        | 50           |     | ms       |

| Status Outpu                     | Pins (PBSTAT, WAKE, PGOOD, RSTO, IRQ)                                 |                                                                     |   |                        |              |     |          |

| V <sub>PBSTAT</sub>              | PBSTAT Output Low Voltage                                             | I <sub>PBSTAT</sub> = 3mA                                           |   |                        | 0.1          | 0.4 | V        |

| I <sub>PBSTAT</sub>              | PBSTAT Output High Leakage Current                                    | V <sub>PBSTAT</sub> = 3.8V                                          |   | -0.1                   |              | 0.1 | μА       |

| V <sub>WAKE</sub>                | WAKE Output Low Voltage                                               | I <sub>WAKE</sub> = 3mA                                             |   |                        | 0.1          | 0.4 | V        |

| I <sub>WAKE</sub>                | WAKE Output High Leakage Current                                      | V <sub>WAKE</sub> = 3.8V                                            |   | -0.1                   |              | 0.1 | μА       |

| V <sub>PGOOD</sub>               | PGOOD Output Low Voltage                                              | I <sub>PGOOD</sub> = 3mA                                            |   |                        | 0.1          | 0.4 | V        |

| I <sub>PGOOD</sub>               | PGOOD Output High Leakage Current                                     | V <sub>PG00D</sub> = 3.8V                                           |   | -0.1                   |              | 0.1 | μА       |

| $V_{PGOOD}$                      | PGOOD Threshold Rising<br>PGOOD Threshold Falling                     |                                                                     |   |                        | -6<br>-8     |     | %<br>%   |

| V <sub>NRSTO</sub>               | LD01 Power Good Threshold Rising<br>LD01 Power Good Threshold Falling |                                                                     |   |                        | -6<br>-8     |     | %<br>%   |

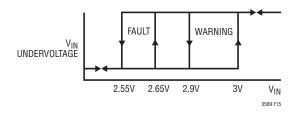

| V <sub>UVLO</sub>                | Undervoltage Lockout Rising<br>Undervoltage Lockout Falling           |                                                                     |   |                        | 2.65<br>2.55 | 2.7 | V        |

| V <sub>UVWARN</sub>              | Undervoltage Warning Rising<br>Undervoltage Warning Falling           |                                                                     |   |                        | 3<br>2.9     |     |          |

| $\overline{V_{\overline{RSTO}}}$ | RSTO Output Low Voltage                                               | I <sub>RSTO</sub> = 3mA                                             |   |                        |              | 0.4 | V        |

| I <sub>RSTO</sub>                | RSTO Output High Leakage Current                                      | V <sub>RSTO</sub> = 3.8V                                            |   | -0.1                   |              | 0.1 | μА       |

| $\overline{V_{\overline{IRQ}}}$  | ĪRQ Output Low Voltage                                                | I <sub>ĪRQ</sub> = 3mA                                              |   |                        |              | 0.4 | V        |

| I <sub>IRQ</sub>                 | IRQ Output High Leakage Current                                       | V <sub>IRQ</sub> = 3.8V                                             |   | -0.1                   |              | 0.1 | μА       |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed Under Absolute Maximum ratings may cause permanent damage to the device. Exposure to any Absolute Maximum rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3589 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3589E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the  $-40^{\circ}$ C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3589I is guaranteed over the  $-40^{\circ}$ C to 125°C operating junction temperature range and the LTC3589H is guaranteed over the full  $-40^{\circ}$ C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. The junction temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation (PD, in Watts) according to the formula:

$T_J = T_A + (PD \bullet \theta_{JA})$ , where the package junction to ambient thermal impedance  $\theta_{JA} = 34^{\circ}C/W$ .

Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:** The LTC3589 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating temperature may impair device reliability.

**Note 4:** Dropout voltage is defined as  $(V_{IN}-V_{LD0})$  for LD01 or  $(V_{IN\_LD0}-V_{LD0})$  for other LD0s when  $V_{LD0}$  is 3% lower than  $V_{LD0}$  measured with  $V_{IN}=V_{IN\_LD0}=4.3V$ .

**Note 5:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency.

**Note 6:** Soft-Start measured in test mode with regulator error amplifier in unity gain mode.

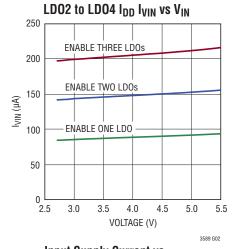

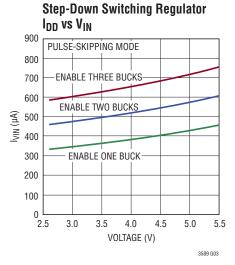

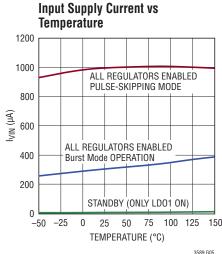

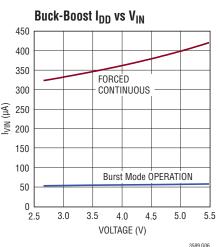

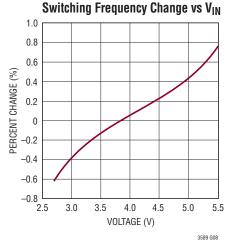

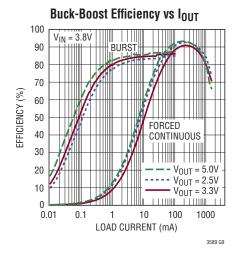

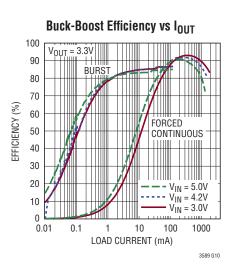

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

www.DataSheet4U.com

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

#### **Buck-Boost Current Limit vs Temperature**

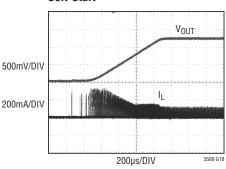

#### Step-Down Switching Regulator **Soft-Start**

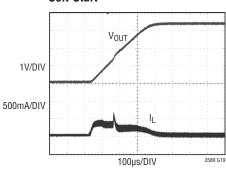

#### **Buck-Boost Switching Regulator Soft-Start**

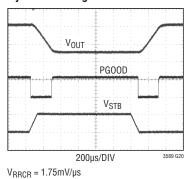

**Dynamic Voltage Slew**

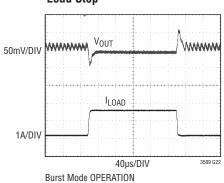

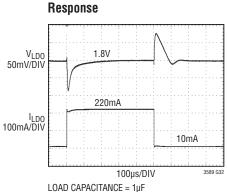

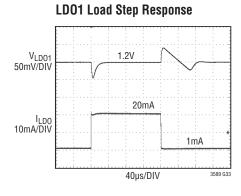

Step-Down Switching Regulator 1 Load Step

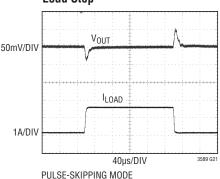

Step-Down Switching Regulator 1 Load Step

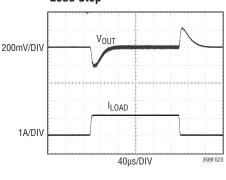

**Buck-Boost Switching Regulator 1 Load Step**

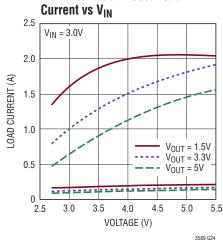

## **Maximum Buck-Boost Load**

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

LD02, LD03, LD04 Dropout Voltage vs Temperature 500  $V_{LD0} = 1.2V$ 400 DROPOUT VOLTAGE (mV) 300  $V_{LDO} = 1.8V$ 200  $V_{LD0} = 3.3V$ 100 -25 0 125 150 -50 50 75 100

TEMPERATURE (°C)

## PIN FUNCTIONS

$V_{IN\_LD02}$  (Pin 1): Power Input for LD02. This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

**LD02** (**Pin 2**): Output Voltage of LD02. Nominal output voltage is set with a resistor feedback divider that servos to an  $I^2C$  register controlled DAC reference. This pin must be bypassed to ground with a  $1\mu F$  or greater ceramic capacitor.

**LD03 (Pin 3):** Output Voltage of LD03. Nominal output voltage is fixed at 1.8V. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

**LD04 (Pin 4):** Output Voltage of LD04. Output voltages of 1.8V, 2.5V, 2.8V, and 3.3V are selected via the  $I^2C$  port. This pin must be bypassed to ground with a  $1\mu F$  or greater ceramic capacitor.

$V_{IN\_LD034}$  (Pin 5): Power Input for LD03 and LD04. This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

**PV**<sub>IN1</sub> (**Pin 6**): Power Input for Step-Down Switching Regulator 1. This pin should be bypassed to ground with a  $4.7\mu$ F or greater ceramic capacitor.

**SW1 (Pin 7):** Switch Pin for Step-Down Switching Regulator 1. Connect one side of step-down switching regulator 1 inductor to this pin.

**RSTO** (Pin 8): Reset Output. Open drain output pulls low when the always on regulator LDO1 is below regulation and during a hard reset initiated by a pushbutton input.

**EN\_LD02** (**Pin 9**): Enable LD02 Logic Input. Active high input to enable LD02. A weak pull-down forces EN\_LD02 low when left floating.

**EN1 (Pin 10):** Enable Step-Down Switching Regulator 1. Active high input to enable step-down switching regulator 1. A weak pull-down forces EN1 low when left floating.

**EN2 (Pin 11):** Enable Step-Down Switching Regulator 2. Active high input to enable step-down switching regulator 2. A weak pull-down forces EN2 low when left floating.

**SW4AB (Pin 12):** Switch Pin for Buck-Boost Switching Regulator 4. Connected to the buck-boost internal power switches A and B. Connect an inductor between this pin and SW4CD (Pin 19).

**EN3 (Pin 13):** Enable Step-Down Switching Regulator 3. Active high input to enable step down switching regulator 3. A weak pull-down forces EN3 low when left floating.

**EN4 (Pin 14):** Enable Buck-Boost Switching Regulator 4. Active high input to enable buck-boost switching regulator 4. A weak pull-down forces EN4 low when left floating.

$PV_{IN4}$  (Pin 15): Power Input for Switching Regulator 4. This pin should be bypassed to ground with a  $4.7\mu F$  or greater ceramic capacitor.

**BB\_OUT (Pin 16):** Output Voltage of Buck-Boost Switching Regulator 4. This pin must be bypassed to ground with a 22µF or greater ceramic capacitor.

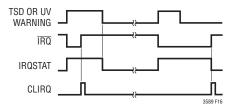

$\overline{\textbf{IRQ}}$  (Pin 17): Interrupt Request Output. Open drain driver is pulled low for power good, undervoltage, and over temperature warning and fault conditions. Clear  $\overline{\textbf{IRQ}}$  by writing to the I<sup>2</sup>C CLIRQ command register.

**EN\_LD034 (Pin 18):** Enable LD03 and LD04 Logic Input. Active high to enable LD03 and LD04. Disable LD04 via I<sup>2</sup>C software commands using I<sup>2</sup>C command registers OVEN or L2DTV2. A weak pull-down forces EN\_LD034 low when left floating.

**SW4CD (Pin 19):** Switch Pin for Buck-Boost Switching Regulator 4. Connected to the buck-boost internal power switches C and D. Connect an inductor between this node and SW4AB (Pin 12).

**PWR\_ON (Pin 20):** External Power-On. Handshaking pin to acknowledge successful power-on sequence. PWR\_ON must be driven high within five seconds of WAKE going high to keep power on. It can be used to activate the WAKE output by driving high. Drive low to shut down WAKE.

$\overline{\textbf{ON}}$  (Pin 21): Pushbutton Input. A weak internal pull-up forces  $\overline{\textbf{ON}}$  high when left floating. A normally open pushbutton is connected from  $\overline{\textbf{ON}}$  to ground to force a low state on this pin.

www.DataSheet4U.com

## PIN FUNCTIONS

**PBSTAT (Pin 22):** Pushbutton Status. Open drain output to be used for processor interrupts. PBSTAT mirrors the status of  $\overline{ON}$  pushbutton pin. PBSTAT is delayed 50ms from  $\overline{ON}$  pin for debounce.

**WAKE (Pin 23):** System Wake Up. Open drain driver output releases high when signaled by pushbutton activation or PWR\_ON input. It may be used to initiate a pin-strapped power-up sequence by connecting to a regulator enable pin to initiate a pin strapped power-on sequence.

**PVIN2** (Pin 24): Power Input for Step-Down Switching Regulator 2. This pin should be bypassed to ground with a  $4.7\mu\text{F}$  or greater ceramic capacitor.

**SW2 (Pin 25):** Switch Pin for Step-Down Switching Regulator 2. Connect one side of step-down switching regulator 2 inductor to this pin.

**SW3 (Pin 26):** Switch Pin for Step-Down Switching Regulator 3. Connect one side of step-down switching regulator 3 inductor to this pin.

**PVIN3 (Pin 27):** Power Input for Switching Regulator 3. Tie this pin to the  $V_{IN}$  supply. This pin should be bypassed to ground with a  $4.7\mu F$  or greater ceramic capacitor.

**VSTB** (**Pin 28**): Voltage Standby. When VSTB is low, DAC reference voltages are selected by bit values in command register VCCR. When VSTB is high, the DAC voltages are forced to the bit values found in the V2 registers. Tie VSTB to ground if unused.

**PGOOD (Pin 29):** Power Good Output. Open drain output pulls down when any regulator falls below power good threshold and during regulator dynamic voltage slew. Unless disabled in I<sup>2</sup>C register. Pulls down when all regulators are disabled.

**SCL (Pin 30):** Clock Input Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to DV<sub>DD</sub>.

**SDA (Pin 31):** Data Input Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to DV<sub>DD</sub>.

**DV**<sub>DD</sub> (**Pin 32**): Supply Voltage for  $I^2C$  Serial Port. This pin sets the logic reference level of SCL and SDA  $I^2C$  pins. DV<sub>DD</sub> resets  $I^2C$  registers to power on state when driven to <1V. SCL and SDA logic levels are scaled to DV<sub>DD</sub>. Connect a 0.1µF decoupling capacitor from this pin to ground.

**BUCK2\_FB** (**Pin 33**): Feedback Input for Step-Down Switching Regulator 2. Set full scale output voltage using resistor divider connected from the output of step-down switching regulator 2 to this pin to ground.

**BUCK3\_FB** (**Pin 34**): Feedback Input for Step-Down Switching Regulator 3. Set full scale output voltage using resistor divider connected from the output of step-down switching regulator 3 to this pin to ground.

**LD01\_FB (Pin 35):** Feedback Input for LD01. Set output voltage using a resistor divider connected from LD01\_STDBY to this pin to ground.

**LD01\_STDBY (Pin 36):** Always On LD01 Output. This pin provides an always on supply voltage useful for light loads such as a watchdog microprocessor or a real time clock. Connect a  $1\mu F$  capacitor from LD01\_STBY to ground.

$V_{IN}$  (Pin 37): Supply Voltage Input. This pin should be bypassed to ground with a 1 $\mu$ F or greater ceramic capacitor.

**LD02\_FB (Pin 38):** Feedback Input for LD02. Set full scale output voltage using a resistor divider connected from LD02\_OUT to this pin to ground.

**BUCK1\_FB** (**Pin 39**): Feedback Input for Step-Down Switching Regulator 1. Set full scale output voltage using resistor divider connected from the output of step-down switching regulator 1 to this pin to ground.

**BB\_FB (Pin 40):** Feedback Input for Buck-Boost Switching Regulator 4. Set the output voltage using resistor divider connected from BB\_OUT to this pin to ground.

**GND** (Exposed Pad Pin 41): Ground. The Exposed Pad must be connected to a continuous ground plane on the second layer of the printed circuit board by several interconnect vias directly under the LTC3589 for maximum heat transfer.

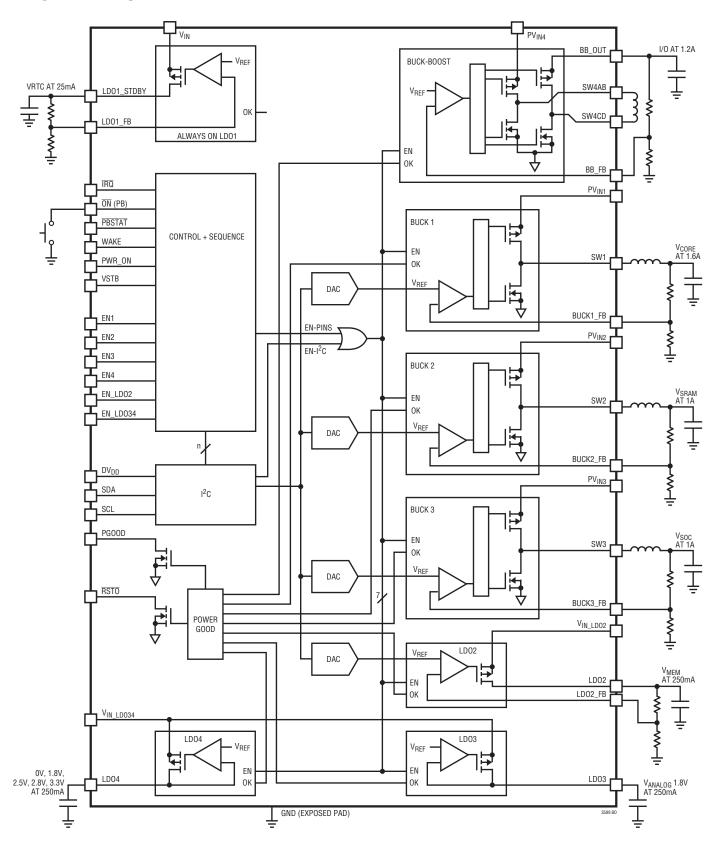

## **BLOCK DIAGRAM**

#### INTRODUCTION

The LTC3589 is a complete power management solution for portable microprocessors and peripheral devices. It generates a total of eight voltage rails for supplying power to the processor core, SDRAM, system memory, PC cards, always-on real time clock and HDD functions. Supplying the voltage rails are an always-on low quiescent current 25mA LDO, one 1.6A and two 1A step-down regulators, a 1.2A buck-boost regulator, and three 250mA low dropout regulators. Supporting the multiple regulators is a highly configurable power-on sequencing capability, dynamic voltage slewing DAC output voltage control, a pushbutton interface controller, regulator control via an I<sup>2</sup>C interface, and extensive status and interrupt outputs.

The LTC3589 operates over an input supply range of 2.7V to 5.5V. The input supplies for the 250mA LDO regulators may operate as low as 1.7V to limit power loss at low output voltages.

The always-on LDO1 provides a resistor programmable output voltage as low as 0.8V and is capable of supplying 25mA. With only the always-on LDO active the LTC3589 draws just  $10\mu A$  (typical). Always on LDO1 will continue to operate with  $V_{IN}$  levels as low as 2.0V (typical) to maintain memory and RTC function as long as possible.

Each of the 250mA LDO regulators has unique output voltage configurations. LDO3 has a fixed 1.8V output. LDO4 has four output levels selectable via the  $\rm I^2C$  interface. Its possible outputs are 1.8V, 2.5V, 2.8V, and 3.3V. LDO2 has a dynamically slewing DAC set point reference and an external feedback pin to set the output voltage range with a resistive divider. Each LDO draws  $\rm 60\mu A$  (typical) quiescent current.

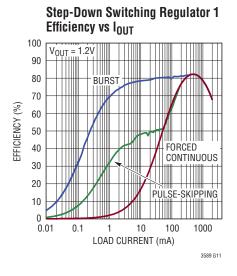

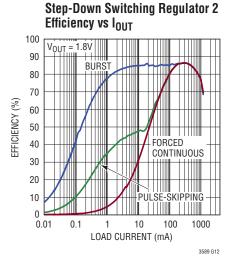

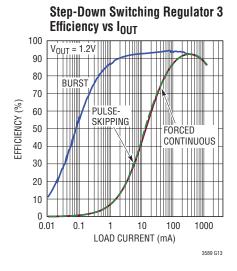

The LTC3589 includes three internally compensated constant frequency current mode step-down switching regulators providing 1A, 1A, and 1.6A. Step-down regulator switching frequencies of 2.25MHz or 1.125MHz are independently selected for each step-down regulator using the I<sup>2</sup>C command registers. The power-on default frequency is 2.25MHz. Each of the step-down regulators have dynamically slewing DAC input references and external feedback pins to set output voltage range. The step-down regulators three operating modes, pulse-skipping, burst,

or forced continuous, are set using the I<sup>2</sup>C interface. In pulse-skipping mode the regulator will support 100% duty cycle. For best efficiency at low output loads select Burst Mode operation. Forced continuous mode minimizes output voltage ripple at light loads.

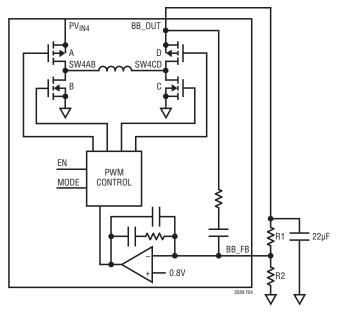

The 4-switch buck-boost DC/DC voltage mode converter generates a user-programmable output voltage rail from 2.5V to 5V. Utilizing a proprietary switching algorithm, the buck-boost converter maintains high efficiency and low noise operation with input voltages that are above, below or equal to the required output rail. The buck-boost error amplifier uses a fixed 0.8V reference and the output voltage is set by an external resistor divider. Burst Mode operation is enabled through the I<sup>2</sup>C control registers. No external compensation components are required for the buck-boost converter.

The reference inputs for the three step-down regulators and LDO2 are 5-bit D to A converters with up-down ramping at selectable slew rates. The slew endpoint voltages and select bits are stored in  $\rm I^2C$  registers for each DAC. A select bit in the  $\rm I^2C$  command registers chooses which register to use for each target voltage. Variable reference slew rates from 0.88mV/µs to 7mV/µs are selectable in the  $\rm I^2C$  register. Each of the four DACs has independent voltage, voltage select, and slew rate control registers.

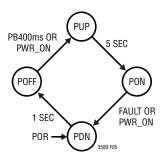

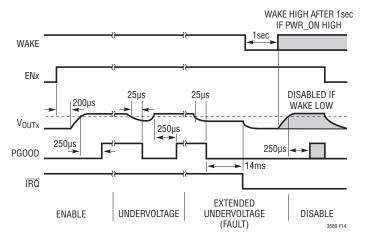

The LTC3589 is equipped with a pushbutton control circuit that will activate the WAKE output, indicate pushbutton status via the PBSTAT pin, and initiate a hard reset shutdown of the regulators. Grounding the  $\overline{\text{ON}}$  pin with the pushbutton for 400ms will force the WAKE pin to release HIGH. The WAKE pin output can be tied to the enable pin of the first regulator in a power-on sequence. Once in the power-on state, subsequent pushes of the button longer than 50ms are mirrored by the PBSTAT output. Holding  $\overline{\text{ON}}$  LOW for five seconds disables all the regulators, pulls down the WAKE pin, and pulls down  $\overline{\text{RSTO}}$  for one second to indicate to the processor that a hard reset occurred. All regulator enables and pushbutton inputs are inhibited for one second following the hard reset.

The LTC3589 has flexible options for enabling and sequencing the regulator enables. The regulators are enabled using input pins or the I<sup>2</sup>C serial port. To define a power-on

sequence tie the enable of the first regulator to be powered up to the WAKE pin. Connect the first regulators output to the enable pin of the second regulator, and so on. One or more regulators may be started in any sequence. Each enable pin has a 200µs (typical) delay between the pin and the internal enable of the regulator. When the system controllers are satisfied that power rails are up, the controller must drive PWR ON HIGH to keep WAKE active. Shutdown sequencing is monitored by output voltage comparators which require each output to discharge below 300mV before re-enabling. A software control command register function is available which sets the regulators to effectively ignore their enable pins but respond to I<sup>2</sup>C register enables. This function enables software-only control of any combination of pin-strapped regulators and is useful for implementing system power saving modes. Keep-alive mode exempts selected regulators from turning off during normal shutdown. In keep-alive mode, the LTC3589 powers down normally and is ready for the next start-up sequence, but selected regulators are kept on to power memory or other function during system standby modes.

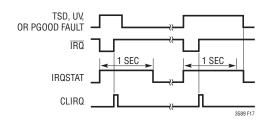

The LTC3589 will shut down all regulators and pull down the WAKE pin under high temperature,  $V_{IN}$  under voltage, and extended low regulator output voltage conditions. Status of a hard shutdown is reported by the  $\overline{IRQ}$  status pin and the IRQSTAT status register.

The I<sup>2</sup>C serial port on the LTC3589 contains 13 command registers for controlling each of the regulators, one read only register for monitoring each regulators power good status, one read only register for reading the cause of an IRQ event, and one clear IRQ command register. The LTC3589 I<sup>2</sup>C supports random addressing of any register and registers may be written in any order using multiple START sequences.

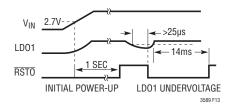

#### **ALWAYS-ON LDO**

The LTC3589 includes a low quiescent current low dropout regulator that remains powered whenever a valid supply is present on  $V_{IN}$ . The always-on LDO will remain active until  $V_{IN}$  drops below 2.0V (typical). This is below the 2.5V undervoltage threshold in effect for the rest of the LTC3589 circuits. The always-on LDO is used to provide power to a standby microcontroller, real time clock, or

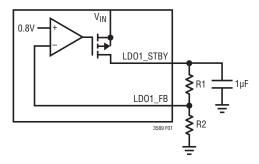

other keep-alive circuits. The LDO is guaranteed to support a 25mA load. A 1 $\mu$ F low impedance ceramic bypass capacitor from LDO1\_STBY to GND is required for compensation. A power good monitor pulls RSTO LOW for a minimum of 14ms (typical) whenever LDO1\_STBY is 8% below its regulation target. An LDO1\_STBY undervoltage condition is reported in the PGOOD status register. The output voltage of LDO1 is set with a resistor divider connected from LDO1\_STBY to the feedback pin LDO1\_FB as shown in Figure 1.

$$V_{LDO\_STBY} = 0.8 \bullet \left(1 + \frac{R1}{R2}\right)(V)$$

Typical values for R1 are in the range of 40k to 1M.

Figure 1. Always-On LDO Application Circuit

LDO1\_STBY is protected from short circuits and over loading.

#### 250MA LDO REGULATORS

Three LDO regulators on the LTC3589 will each deliver up to 250mA output. The LDO regulators are enabled by pin input or I<sup>2</sup>C command register. Pin EN\_LDO2 enables LDO2 and pin EN\_LDO34 enables LDO3 and LDO4 together. An I<sup>2</sup>C command register bit is available to decouple LDO4 from pin EN\_LDO34 so that LDO4 is under command register control only. All the regulators have current limit protection circuits. When disabled, a 2k internal pull-down resistor is connected to the regulators output. Depending on settings in I<sup>2</sup>C system control register 2 (SCR2), a regulator's output must discharge to less than 300mV before it will respond to its enable. The output discharge

www.DataSheet4U.com

feature is to guarantee proper startup sequencing. This feature and the 2k pull-down resistors may be overridden by bit settings in command register SCR2.

To help reduce LDO power loss in the system, the regulators have dedicated supply inputs that may be lower than the main  $V_{IN}$  supply. Connect a low ESR 1µF capacitor to each of the output pins LDO2, LDO3, and LDO4.

### LDO Regulator 2

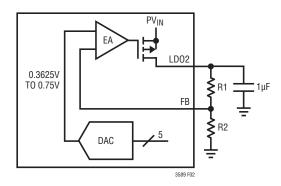

One of the LTC3589 dynamic slewing DACs serves as the reference input of LDO2. The output range of LDO2 is set using an external resistor divider connected from LDO2 to the feedback pin LDO2\_FB as shown in Figure 2. Set the output voltage of LDO2 using the following formula:

$$V_{OUT} = \left(1 + \frac{R1}{R2}\right) \cdot (0.3625 + L2DTVx \cdot 0.0125)$$

L2DTVx is the five bit word contained in the LDO2 dynamic target voltage 1 (L2DTV1) or the LDO2 dynamic target voltage 2 (L2DTV2) command registers. The default value of L2DTVx[4-0] is 11001 to output a reference voltage of 0.675V. LDO2 is enabled by writing bit 4 in the output voltage enable (OVEN) command register to 1 or driving the LDO2\_EN pin high. Whenever the command is given to slew LDO2 DAC reference to a lower voltage an integrated 2k pull down resistor is connected to LDO2 output.

Figure 2. LDO2 Application Circuit

Table 1. Shows the I<sup>2</sup>C command register settings used to control LDO2.

**Table 1. LDO 2 Command Register Settings**

| COMMAND<br>REGISTER[BIT] | VALUE                 | SETTING                                                                                                                              |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| OVEN[4]                  | 0*<br>1               | Disable<br>Enable                                                                                                                    |

| SCR2[4]                  | 0*<br>1               | Wait for Output Below 300mV Before Enable Enable Immediately                                                                         |

| VCCR[5]                  | 0*<br>1               | Select Register L2DTV1 (V1) Reference<br>Select Register L2DTV2 (V2) Reference                                                       |

| VCCR[6]                  | 1                     | Initiate Dynamic Voltage Slew                                                                                                        |

| VRRCR[7-6]               | 00*<br>01<br>10<br>11 | Reference Slew Rate = 0.88mV/µs<br>Reference Slew Rate = 1.75mV/µs<br>Reference Slew Rate = 3.5mV/µs<br>Reference Slew Rate = 7mV/µs |

| L2DTV1[4-0]              | 11001*                | DAC Dynamic Target Voltage V1                                                                                                        |

| L2DTV1[5]                | 0*<br>1               | Force PGOOD Low When Slewing<br>Normal PGOOD Operation When Slewing                                                                  |

| L2DTV1[7]                | 0*<br>1               | Shutdown LDO2 Normally<br>Keep LDO2 Alive                                                                                            |

| L2DTV2[4-0]              | 11001*                | DAC Dynamic Target Voltage V2                                                                                                        |

<sup>\*</sup> Denotes Default Power-On Value

#### LDO Regulator 3

LD03 is a fixed 1.8V output regulator. LD03 is enabled by driving pin EN\_LD034 high or by writing command register OVEN[5] to 1.

Table 2 shows the I<sup>2</sup>C command register settings used to control LDO3.

**Table 2. LDO 3 Command Register Settings**

| COMMAND<br>REGISTER[BIT] | VALUE   | SETTING                                                      |

|--------------------------|---------|--------------------------------------------------------------|

| OVEN[5]                  | 0*<br>1 | Disable<br>Enable                                            |

| SCR2[5]                  | 0*<br>1 | Wait for Output Below 300mV Before Enable Enable Immediately |

<sup>\*</sup> Denotes Default Power-On Value

## LDO Regulator 4

LDO4 has four output voltage options that are controlled by the contents of command register L2DTV2 bits 6 and 5. By default, pin EN\_LDO34 enables and disables LDO3 and LDO4 simultaneously when command register bits OVEN[6] and OVEN[7] are LOW. When EN\_LDO34 is LOW, LDO3 and LDO4 are controlled by writing to command register bits OVEN[6] and OVEN[7] respectively. When command register bit L2DTV2[7] is HIGH, control of LDO4 is disconnected from pin EN\_LDO34 and controlled by command register bit OVEN[7] regardless of the status of EN\_LDO34. Table 3 shows the I<sup>2</sup>C command register settings used to control LDO4.

Table 3. LDO 4 Command Register Settings

| COMMAND<br>REGISTER[BIT] | VALUE                 | SETTING                                                                                                      |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|

| OVEN[6]                  | 0*<br>1               | Disable<br>Enable                                                                                            |

| SCR2[6]                  | 0*<br>1               | Wait for Output Below 300mV Before Enable Enable Immediately                                                 |

| L2DTV2[6-5]              | 00*<br>01<br>10<br>11 | V <sub>LD04</sub> = 2.8V<br>V <sub>LD04</sub> = 2.5V<br>V <sub>LD04</sub> = 1.8V<br>V <sub>LD04</sub> = 3.3V |

| L2DTV2[7]                | 0<br>1                | LDO4 Enable Controlled by EN_LDO34<br>LDO4 Enable Controlled by OVEN[6]                                      |

<sup>\*</sup> Denotes Default Power-On Value

#### STEP-DOWN SWITCHING REGULATORS

#### **Output Voltage Programming**

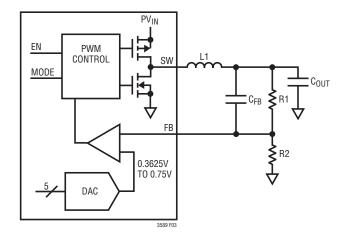

Each of the step-down converters uses a dynamically slewing DAC output for its reference. The full-scale output voltage is set by using a resistor divider connected from the step-down switching regulator output to the feedback pins (B1\_FB, B2\_FB, and B3\_FB) as shown in Figure 3. Set the output voltage of step-down switching regulators using the following formula:

$$V_{OUT} = \left(1 + \frac{R1}{R2}\right) \cdot (0.3625 + BxDTVx \cdot 0.0125)(V)$$

BxDTVx is the decimal value of the five bit binary number in the I<sup>2</sup>C BxDTV1 or BxDTV2 command registers. BxDTV1 and BxDTV2 default to 11001 to output a reference voltage

Figure 3. Step-Down Switching Regulator Application Circuit

of 0.675V. Typical values for R1 are in the range of 40k to 1M. The capacitor  $C_{FB}$  cancels the pole created by the feedback resistors and the input capacitance on the FB pin and also helps to improve load step transient response. A value of 10pF is recommended for most applications. Experimentation with capacitor sizes between 10pF and 33pF may yield improved transient response.

#### **Operating Modes**

The step-down switching regulators include three possible operating modes to meet the noise and power needs of a variety of applications.

In pulse-skipping mode, at the start of every cycle, a latch is set that turns on the main P-channel MOSFET switch. During the cycle, a current comparator compares the peak inductor current to the output of an error amplifier. The output of the current comparator resets the latch. At this time the P-channel MOSFET switch turns off and the N-channel MOSFET synchronous rectifier turns on. The N-channel MOSFET synchronous rectifier will turn off when the end of the clock cycle is reached or if the inductor current drops through zero. Using this method of operation, the error amplifier adjusts the peak inductor current to deliver the required output power. All necessary loop compensation is internal to the step-down switching regulator requiring only a single ceramic output capacitor for stability. At light loads in pulse-skipping mode, the inductor current may reach zero on each pulse that will