# Synchronous Regulator Controller for N- or P-Channel MOSFETs

#### **FEATURES**

- Ultra-High Efficiency: Over 95% Possible

- Drives N-Channel MOSFET for High Current or P-Channel MOSFET for Low Dropout

- Pin Selectable Burst Mode Operation

- 1% Output Accuracy (LTC1266A)

- Pin Selectable Phase of Topside Driver for Boost or Step-Down Operation

- Wide V<sub>IN</sub> Range: 3.5V to 20V

- On-Chip Low-Battery Detector

- High Efficiency Maintained over Large Current Range

- Low 170µA Standby Current at Light Loads

- Current Mode Operation for Excellent Line and Load Transient Response

- Logic Controlled Micropower Shutdown: I<sub>0</sub> < 40μA

- Short Circuit Protection

- Synchronous Switching with Nonoverlaping Gate Drives

- Available in 16-Pin Narrow SO Package

## **APPLICATIONS**

- Notebook and Palmtop Computers

- Portable Instruments

- Cellular Telephones

- DC Power Distribution Systems

- GPS Systems

### DESCRIPTION

The LTC®1266 series is a family of synchronous switching regulator controllers featuring automatic Burst Mode $^{\text{TM}}$  operation to maintain high efficiencies at low output currents. These devices drive external power MOSFETs at switching frequencies up to 400kHz using a constant off-time current mode architecture providing constant ripple current in the inductor. They can drive either an N-channel or a P-channel topside MOSFET.

The operating current level is user-programmable via an external current sense resistor. Wide input supply range allows operation from 3.5V to 18V (20V maximum). Constant off-time architecture provides low dropout regulation limited only by the  $R_{DS(ON)}$  of the topside MOSFET (when using the P-channel) and the resistance of the inductor and current sense resistor.

The LTC1266 series combines synchronous switching for maximum efficiency at high currents with an automatic low current operating mode, called Burst Mode operation, which reduces switching losses. Standby power is reduced to only 1mW at  $V_{IN} = 5V$  (at  $I_{OUT} = 0$ ). Load currents in Burst Mode operation are typically 0mA to 500mA.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode is a trademark of Linear Technology Corporation.

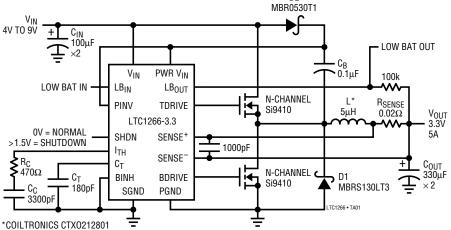

# TYPICAL APPLICATION

Figure 1. High Efficiency Step-Down Converter

LTC1266 • TA02

# **ABSOLUTE MAXIMUM RATINGS**

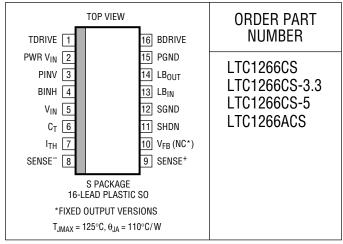

# PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

# **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN} = 10V$ , $V_{SHDN} = V_{BINH} = 0V$ unless otherwise noted.

| SYMBOL               | PARAMETER                                                                               | CONDITIONS                                                                                                                                                                                                                                                                                   |   | MIN          | TYP                  | MAX                   | UNITS             |

|----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|----------------------|-----------------------|-------------------|

| V <sub>FB</sub>      | Feedback Voltage<br>LTC1266ACS<br>LTC1266CS                                             | V <sub>IN</sub> = 9V, I <sub>LOAD</sub> = 700mA, V <sub>PINV</sub> = V <sub>PWR</sub> ,<br>Topside Switch = N-Ch                                                                                                                                                                             | • | 1.210        | 1.275<br>1.25        | 1.290                 | V                 |

| I <sub>FB</sub>      | Feedback Current (LTC1266 Only)                                                         |                                                                                                                                                                                                                                                                                              | • |              | 0.2                  | 1                     | μА                |

| V <sub>OUT</sub>     | Regulated Output Voltage<br>LTC1266CS-3.3<br>LTC1266CS-5                                | $V_{IN} = 9V$ , $I_{LOAD} = 700$ mA, $V_{PINV} = V_{PWR}$ , Topside Switch = N-Ch, $V_{PWR} = 14V$                                                                                                                                                                                           | • | 3.23<br>4.90 | 3.33<br>5.05         | 3.43<br>5.20          | V<br>V            |

|                      | Output Ripple (Burst Mode Operation)                                                    | I <sub>LOAD</sub> = 150mA                                                                                                                                                                                                                                                                    |   |              | 50                   |                       | mV <sub>P-P</sub> |

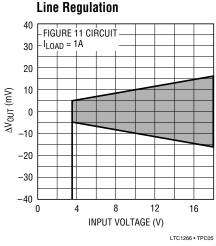

| ΔV <sub>OUT</sub>    | Output Voltage Line Regulation                                                          | I <sub>LOAD</sub> = 50mA<br>  V <sub>PINV</sub> = 0V, Topside Switch = P-Ch, V <sub>IN</sub> = 7V to 12V<br>  V <sub>PINV</sub> = V <sub>PWR</sub> , Topside Switch = N-Ch, V <sub>IN</sub> = 7V to 12V                                                                                      |   | -40<br>-40   | 0<br>0               | 40<br>40              | mV<br>mV          |

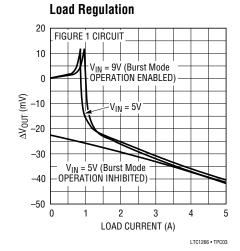

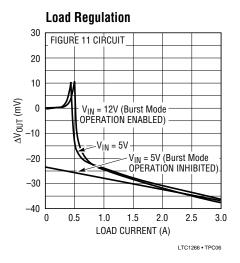

|                      | Output Voltage Load Regulation<br>LTC1266-3.3<br>LTC1266-3.3<br>LTC1266-5<br>LTC1266-5  | 5mA < I <sub>LOAD</sub> < 2A, R <sub>SENSE</sub> = 0.05Ω<br>Burst Mode Operation Enabled, V <sub>BINH</sub> = 0V<br>Burst Mode Operation Inhibited, V <sub>BINH</sub> = 2V<br>Burst Mode Operation Enabled, V <sub>BINH</sub> = 0V<br>Burst Mode Operation Inhibited, V <sub>BINH</sub> = 2V | • |              | 40<br>15<br>60<br>25 | 65<br>25<br>100<br>40 | mV<br>mV<br>mV    |

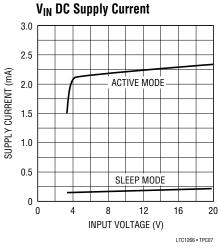

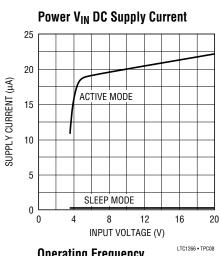

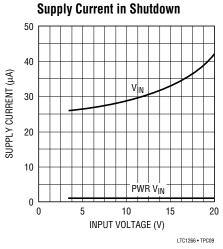

| I <sub>Q1</sub>      | V <sub>IN</sub> Pin DC Supply Current (Note 2)<br>Normal Mode<br>Sleep Mode<br>Shutdown | 3.5V < V <sub>IN</sub> < 18V<br>3.5V < V <sub>IN</sub> < 18V<br>V <sub>SHDN</sub> = 2.1V, 3.5V < V <sub>IN</sub> < 18V                                                                                                                                                                       |   |              | 2.1<br>170<br>25     | 3.0<br>250<br>50      | mA<br>μA<br>μA    |

| I <sub>Q2</sub>      | PWR V <sub>IN</sub> DC Supply Current (Note 2)<br>Normal Mode<br>Sleep Mode<br>Shutdown | 3.5V < PWR V <sub>IN</sub> < 18V<br>3.5V < PWR V <sub>IN</sub> < 18V<br>V <sub>SHDN</sub> = 2.1V, 3.5V < PWR V <sub>IN</sub> < 18V                                                                                                                                                           |   |              | 20<br>1<br>1         | 40<br>5<br>5          | μΑ<br>μΑ<br>μΑ    |

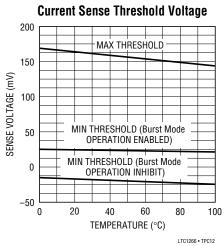

| V <sub>SENSE 1</sub> | Current Sense Threshold<br>(Burst Mode Operation Enabled)<br>LTC1266                    | $V_{BINH} = 0V$ $V_{SENSE}^- = 3.3V, V_{FB} = V_{OUT}/2.64 + 25mV (Forced)$                                                                                                                                                                                                                  |   |              | 25                   |                       | mV                |

|                      | LTC1266-3.3                                                                             | $V_{SENSE}^- = 3.3V$ , $V_{FB} = V_{OUT}/2.64 - 25mV$ (Forced)<br>$V_{SENSE}^- = V_{OUT} + 100mV$ (Forced)                                                                                                                                                                                   | • | 135          | 155<br>25            | 175                   | mV<br>mV          |

|                      | LTC1266-5                                                                               | V <sub>SENSE</sub> <sup>-</sup> = V <sub>OUT</sub> - 100mV (Forced)<br>V <sub>SENSE</sub> <sup>-</sup> = V <sub>OUT</sub> + 100mV (Forced)<br>V <sub>SENSE</sub> <sup>-</sup> = V <sub>OUT</sub> - 100mV (Forced)                                                                            |   | 135<br>135   | 155<br>25<br>155     | 175<br>175            | mV<br>mV<br>mV    |

# $\textbf{ELECTRICAL CHARACTERISTICS} \quad \textbf{T}_{A} = 25^{\circ}\text{C}, \ \textbf{V}_{IN} = 10 \text{V}, \ \textbf{V}_{SHDN} = \textbf{V}_{BINH} = 0 \text{V} \ unless otherwise noted}.$

| SYMBOL                          | PARAMETER                                                  | CONDITIONS                                                                                                                 |   | MIN  | TYP          | MAX      | UNITS    |

|---------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|------|--------------|----------|----------|

| V <sub>SENSE 2</sub>            | Current Sense Threshold<br>(Burst Mode Operation Disabled) | V <sub>BINH</sub> = 2.1V                                                                                                   |   |      |              |          |          |

|                                 | LTC1266                                                    | $V_{SENSE}^- = 3.3V, V_{FB} = V_{OUT}/2.64 + 25mV (Forced)$<br>$V_{SENSE}^- = 3.3V, V_{FB} = V_{OUT}/2.64 - 25mV (Forced)$ | • | 135  | -20<br>155   | 175      | mV<br>mV |

|                                 | LTC1266-3.3                                                | V <sub>SENSE</sub> -= V <sub>OUT</sub> + 100mV (Forced)<br>V <sub>SENSE</sub> -= V <sub>OUT</sub> - 100mV (Forced)         |   | 135  | -20<br>155   | 175      | mV<br>mV |

|                                 | LTC1266-5                                                  | $V_{SENSE}^- = V_{OUT} - 100 \text{mV} (Forced)$<br>$V_{SENSE}^- = V_{OUT} + 100 \text{mV} (Forced)$                       | • | 133  | -20          | 173      | mV       |

|                                 | -101-00                                                    | $V_{SENSE}$ = $V_{OUT}$ – 100mV (Forced)                                                                                   | • | 135  | 155          | 175      | mV       |

| $V_{SHDN}$                      | Shutdown Pin Threshold                                     |                                                                                                                            |   | 0.6  | 0.8          | 2        | V        |

| I <sub>SHDN</sub>               | Shutdown Pin Input Current                                 | 0V < V <sub>SHDN</sub> < 8V, V <sub>IN</sub> = 16V                                                                         |   |      | 1.2          | 5        | μΑ       |

| I <sub>PINV</sub>               | Phase Invert Pin Input Current                             | 0V < V <sub>PINV</sub> < 18V, V <sub>IN</sub> = 18V                                                                        |   |      | 0.2          | 1        | μΑ       |

| V <sub>BINH</sub>               | Burst Mode Operation<br>Inhibit Pin Threshold              |                                                                                                                            |   | 0.8  | 1.2          | 2        | V        |

| I <sub>BINH</sub>               | Burst Mode Operation<br>Inhibit Pin Input Current          | 0V < V <sub>BINH</sub> < 18V, V <sub>IN</sub> = 18V                                                                        |   |      | 0.2          | 1        | μА       |

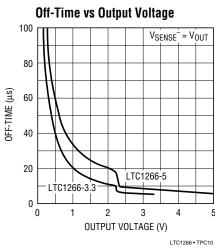

| I <sub>CT</sub>                 | C <sub>T</sub> Pin Discharge Current                       | $V_{SENSE}$ + = $V_{OUT}$ - 100mV, $V_{SENSE}$ - = $V_{OUT}$ - 300mV<br>$V_{OUT}$ = 0V                                     |   | 50   | 70<br>2      | 90<br>10 | μA<br>μA |

| t <sub>OFF</sub>                | Off-Time (Note 3)                                          | $C_T = 390 pF$ , $I_{LOAD} = 700 mA$                                                                                       |   | 4    | 5            | 6        | μs       |

| t <sub>MAX</sub>                | Max On-Time                                                | $V_{OUT} = 0V$ , $V_{IN} = 18V$                                                                                            |   |      | 60           |          | μs       |

| t <sub>r</sub> , t <sub>f</sub> | Driver Output Transition Times                             | C <sub>L</sub> = 3000pF (Pins 1, 16), V <sub>IN</sub> = 6V                                                                 |   |      | 100          | 200      | ns       |

| V <sub>CLAMP</sub>              | Output Voltage Clamp in<br>Burst Mode Operation Inhibit    | V <sub>BINH</sub> = 2.1V                                                                                                   |   |      |              |          |          |

|                                 | LTC1266                                                    | Measured at V <sub>FB</sub>                                                                                                |   |      | 1.30         |          | V        |

|                                 | LTC1266-3.3<br>LTC1266-5                                   | Measured at V <sub>SENSE</sub> –<br>Measured at V <sub>SENSE</sub> –                                                       |   |      | 3.43<br>5.20 |          | V<br>V   |

| V <sub>LBTRIP</sub>             | Low-Battery Trip Point                                     | V <sub>IN</sub> = 5V                                                                                                       |   | 1.14 | 1.25         | 1.35     | V        |

| - LDTINII                       | 20.1. 20.1.5                                               | $V_{IN} = 12V$                                                                                                             |   | 1.17 | 1.30         | 1.42     | V        |

| I <sub>LBLEAK</sub>             | Max Leakage Current into Pin 14                            | V <sub>LBOUT</sub> = 18V, V <sub>LBIN</sub> = 2V                                                                           |   |      | 25           | 200      | nA       |

| I <sub>LBSINK</sub>             | Max Sink Current into Pin 14                               | V <sub>LBOUT</sub> = 1V, V <sub>LBIN</sub> = 0V, 2.5V < V <sub>IN</sub> < 18V                                              |   | 1    | 8            |          | mA       |

| I <sub>LBIN</sub>               | Max Leakage Current into Pin 13                            | V <sub>LBIN</sub> = 18V                                                                                                    |   |      | 0.2          | 1        | μА       |

#### $-40^{\circ}C < T_A < 85^{\circ}C$ (Note 4), $V_{IN} = 10V,$ unless otherwise noted.

| SYMBOL           | PARAMETER                                                                               | CONDITIONS                                                                                                                             | MIN          | TYP              | MAX              | UNITS          |

|------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------|------------------|----------------|

| $V_{FB}$         | Feedback Voltage (LTC1266 only)                                                         | V <sub>IN</sub> = 9V, I <sub>LOAD</sub> = 700mA                                                                                        | 1.21         | 1.25             | 1.29             | V              |

| V <sub>OUT</sub> | Regulated Output Voltage<br>LTC1266-3.3<br>LTC1266-5                                    | V <sub>IN</sub> = 9V, I <sub>LOAD</sub> = 700mA                                                                                        | 3.23<br>4.90 | 3.33<br>5.05     | 3.43<br>5.20     | V              |

| I <sub>Q1</sub>  | V <sub>IN</sub> Pin DC Supply Current (Note 2)<br>Normal Mode<br>Sleep Mode<br>Shutdown | 3.5V < V <sub>IN</sub> < 18V<br>3.5V < V <sub>IN</sub> < 18V<br>V <sub>SHUTDOWN</sub> = 2.1V, 3.5V < V <sub>IN</sub> < 18V             |              | 2.1<br>170<br>25 | 3.3<br>260<br>60 | mA<br>μA<br>μA |

| I <sub>Q2</sub>  | PWR V <sub>IN</sub> DC Supply Current (Note 2)<br>Normal Mode<br>Sleep Mode<br>Shutdown | 3.5V < PWR V <sub>IN</sub> < 18V<br>3.5V < PWR V <sub>IN</sub> < 18V<br>V <sub>SHUTDOWN</sub> = 2.1V, 3.5V < PWR V <sub>IN</sub> < 18V |              | 20<br>1<br>1     | 50<br>7<br>7     | Ац<br>Ац<br>Ац |

# **ELECTRICAL CHARACTERISTICS**

| SYMBOL              | PARAMETER                                                  | CONDITIONS                                                          | MIN  | TYP | MAX | UNITS |

|---------------------|------------------------------------------------------------|---------------------------------------------------------------------|------|-----|-----|-------|

| V <sub>SENSE1</sub> | Current Sense Threshold<br>(Burst Mode Operation Enabled)  | V <sub>BINH</sub> = 0V                                              |      |     |     |       |

|                     | LTC1266                                                    | $V_{SENSE}^{-} = 3.3V, V_{FB} = V_{OUT}/2.64 + 25mV (Forced)$       |      | 25  |     | mV    |

|                     |                                                            | $V_{SENSE}^- = 3.3V, V_{FB} = V_{OUT}/2.64 - 25mV (Forced)$         | 135  | 155 | 180 | mV    |

|                     | LTC1266-3.3, LTC1266-5                                     | $V_{SENSE}^- = V_{OUT} + 100 \text{mV (Forced)}$                    |      | 25  |     | mV    |

|                     |                                                            | $V_{SENSE}^- = V_{OUT} - 100 \text{mV (Forced)}$                    | 135  | 155 | 180 | mV    |

| Sense 2             | Current Sense Threshold<br>(Burst Mode Operation Disabled) | V <sub>BINH</sub> = 2.1V                                            |      |     |     |       |

|                     | LTC1266                                                    | $V_{SENSE}^{-}$ 3.3V, $V_{FB} = V_{OUT}/2.64 + 25mV$ (Forced)       |      | -20 |     | mV    |

|                     |                                                            | $V_{SENSE}^{-}$ 3.3V, $V_{FB} = V_{OUT}/2.64 - 25mV$ (Forced)       | 130  | 155 | 185 | mV    |

|                     | LTC1266-3.3, LTC1266-5                                     | V <sub>SENSE</sub> <sup>-</sup> = V <sub>OUT</sub> + 100mV (Forced) |      | -20 |     | mV    |

|                     |                                                            | $V_{SENSE}^- = V_{OUT} - 100 \text{mV (Forced)}$                    | 130  | 155 | 185 | mV    |

| V <sub>SHDN</sub>   | Shutdown Pin Threshold                                     |                                                                     | 0.55 | 0.8 | 2   | V     |

| t <sub>OFF</sub>    | Off-Time (Note 3)                                          | C <sub>T</sub> = 390pF, I <sub>LOAD</sub> = 700mA                   | 3.8  | 5   | 6.5 | μS    |

The lacktriangle denotes specifications which apply over the full operating temperature range.

**Note 1:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$$T_J = T_A + (P_D \times 110^{\circ}C/W)$$

**Note 2:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See Applications Information.

Note 3: In applications where  $R_{SENSE}$  is placed at ground potential, the off-time increases approximately 40%.

**Note 4:** The LTC1266, LTC1266-3.3, and LTC1266-5 are not tested and not quality assurance sampled at  $-40^{\circ}$ C and 85°C. These specifications are guaranteed by design and/or correlation.

**Note 5:** Unless otherwise noted the specifications for the LTC1266A are the same as those for the LTC1266.

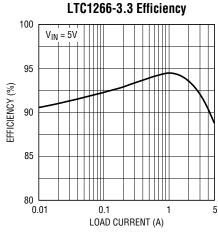

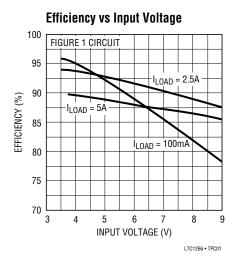

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**TDrive (Pin 1):** High Current Drive for Topside MOSFET. This MOSFET can be either P-channel or N-channel, user selectable by Pin 3. Voltage swing at this pin is from PWR  $V_{\text{IN}}$  to ground.

**PWR V**<sub>IN</sub> (**Pin 2**): Power Suppy for Drive Signals. Must be closely decoupled to power ground (**Pin 15**).

**PINV (Pin 3):** Phase Invert. Sets the phase of the topside driver to drive either a P-channel or an N-channel MOSFET as follows:

P-channel: Pin 3 = 0V N-channel: Pin 3 = PWR V<sub>IN</sub>

**BINH (Pin 4):** Burst Mode Operation Inhibit. A CMOS logic high on this pin will disable the Burst Mode operation feature forcing continuous operation down to zero load.

**V**<sub>IN</sub> (**Pin 5**): Main Supply Pin.

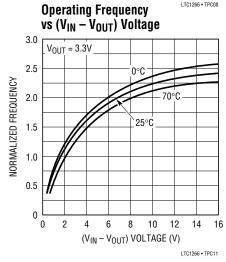

$C_T$  (Pin 6): External Capacitor.  $C_T$  from Pin 4 to ground sets the operating frequency. The actual frequency is also dependent on the input voltage.

**I**<sub>TH</sub> (**Pin 7**): Gain Amplifier Decoupling Point. The current comparator threshold increases with the Pin 7 voltage.

**Sense**<sup>-</sup> (**Pin 8**): Connects to internal resistive divider which sets the output voltage in LTC1266-3.3 and LTC1266-5 versions. Pin 8 is also the (–) input for the current comparator.

**Sense** + (Pin 9): The (+) Input to the Current Comparator. A built-in offset between Pins 8 and 9 in conjunction with R<sub>SENSE</sub> sets the current trip threshold.

**V<sub>FB</sub> (Pin 10):** For the LTC1266 adjustable version, Pin 10 serves as the feedback pin from an external resistive divider used to set the output voltage. On LTC1266-3.3 and LTC1266-5 versions this pin is not used.

**SHDN (Pin 11):** When grounded, the LTC1266 series operates normally. Pulling Pin 11 high holds both MOSFETs off and puts the LTC1266 in micropower shutdown mode. Requires CMOS logic signal with  $t_r$ ,  $t_f < 1\mu s$ . Should not be left floating.

**SGND** (Pin 12): Small-Signal Ground. Must be routed separately from other grounds to the (-) terminal of  $C_{OUT}$ .

**LB**<sub>IN</sub> (**Pin 13**): Input to the Low-Battery Comparator. This input is compared to an internal 1.25V reference.

**LB<sub>OUT</sub>** (**Pin 14**): Open Drain Output of the Low-Battery Comparator. This pin will sink current when Pin 13 is below 1.25V.

**PGND (Pin 15):** Driver Power Ground. Connects to source of N-channel MOSFET and the (-) terminal of  $C_{IN}$ .

**BDrive (Pin 16):** High Current Drive for Bottom N-Channel MOSFET. Voltage swing at Pin 16 is from ground to PWR  $V_{\text{IN}}$ .

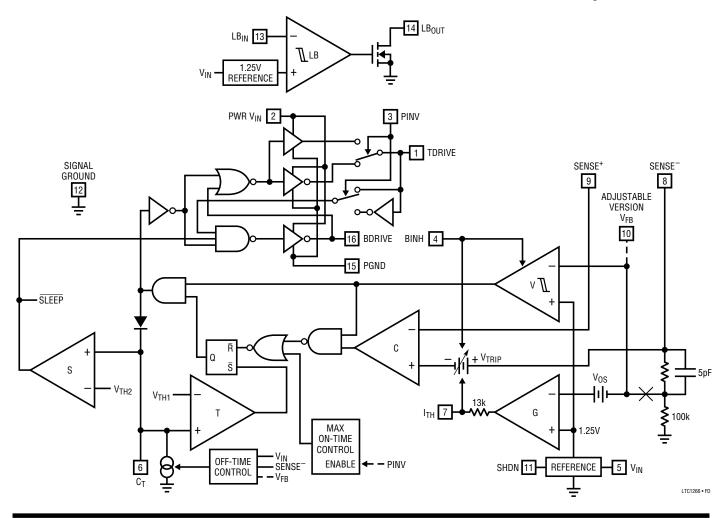

# FUNCTIONAL DIAGRAM Pin 10 Connection Shown for LTC1266-3.3 and LTC1266-5; Changes Create LTC1266

# **OPERATION**

The LTC1266 series uses a current mode, constant offtime architecture to synchronously switch an external pair of power MOSFETs. Operating frequency is set by an external capacitor at the timing capacitor Pin 6.

The output voltage is sensed by an internal voltage divider connected to Sense<sup>-</sup>, Pin 8, (LTC1266-3.3 and LTC1266-5) or external divider returned to V<sub>FB</sub>, Pin 10, (LTC1266). A voltage comparator V, and a gain block G, compare the divided output voltage with a reference voltage of 1.25V. To optimize efficiency, the LTC1266 automatically switches between two modes of operation, burst and continuous. The voltage comparator is the primary control element when the device is in Burst Mode operation, while the gain block controls the output voltage in continuous mode.

During the switch ON cycle in continuous mode, current comparator C monitors the voltage between Pins 8 and 9 connected across an external shunt in series with the inductor. When the voltage across the shunt reaches its threshold value, the topside driver output is switched to turn off the topside MOFSET (Power  $V_{IN}$  for P-channel or ground for N-channel). The timing capacitor connected to Pin 6 is now allowed to discharge at a rate determined by the off-time controller. The discharge current is made proportional to the output voltage (measured by Pin 8) to model the inductor current, which decays at a rate which is also proportional to the output voltage. While the timing capacitor is discharging, the bottom-side drive output is switched to power  $V_{IN}$  to turn on the bottom-side N-channel MOSFET.

## **OPERATION**

When the voltage on the timing capacitor has discharged past  $V_{TH1}$ , comparator T trips, setting the flip-flop. This causes the bottom-side output to switch off and the topside output to switch on (ground for P-channel and Power  $V_{IN}$  for N-channel). The cycle then repeats.

As the load current increases, the output voltage decreases slightly. This causes the output of the gain stage (Pin 7) to increase the current comparator threshold, thus tracking the load current.

The sequence of events for Burst Mode operation is very similar to continuous operation with the cycle interrupted by the voltage comparator. When the output voltage is at or above the desired regulated value, the topside MOSFET is held off by comparator V and the timing capacitor continues to discharge below  $V_{TH1}$ . When the timing capacitor discharges past  $V_{TH2}$ , voltage comparator S trips, causing the internal sleep line to go low and the bottom-side MOSFET to turn off.

The circuit now enters sleep mode with both power MOSFETs turned off. In sleep mode, a majority of the circuitry is turned off, dropping the quiescent current from 2.1mA to  $170\mu A$ . The load current is now being supplied from the output capacitor. When the output voltage has dropped by the amount of hysteresis in comparator V, the topside MOSFET is again turned on and this process repeats.

To avoid the operation of the current loop interfering with Burst Mode operation, a built-in offset  $V_{OS}$  is incorporated in the gain stage. This prevents the current comparator threshold from increasing until the output voltage has dropped below a minimum threshold.

To prevent both the external MOSFETs from ever being turned on at the same time, feedback is incorporated to sense the state of the driver output pins. Before the bottom-side drive output can turn on, the topside output must be off. Likewise, the topside output is prevented from turning on while the bottom-side drive output is still on.

The LTC1266 has two select pins which provide the user with choice of topside switch and with the option of inhibiting Burst Mode operation. The phase select pin allows the user to choose whether the topside MOSFET is a P-channel or an N-channel. The phase select pin does two things: sets the proper phase of the drive signal (ON = Power  $V_{IN}$  for N-channel and ON = OV for P-channel) and also sets an upper limit for the on-time (60 $\mu$ s) when set to the N-channel. The on-time limit ensures proper start-up when used in a single supply bootstrap circuit configuration (see Applications Information). In P-channel mode there is no on-time limit and thus, in dropout, the P-channel MOSFET is turned on continuously (100% duty cycle).

The Burst Mode operation inhibit (BINH, Pin 4) allows the Burst Mode operation to be disabled by applying a CMOS logic high to this pin. With Burst Mode operation disabled, the LTC1266 will remain in continuous mode down to zero load. Burst Mode operation is disabled by allowing the lower current threshold limit to go below zero so that the voltage comparator will never trip. The voltage comparator trip point is also raised up so that it will not be tripped by transients. It is still active to provide a voltage clamp to prevent the output from overshooting.

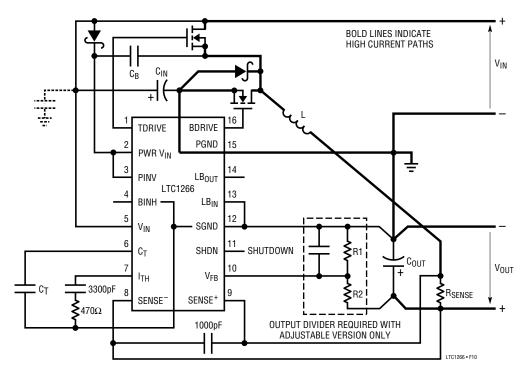

# APPLICATIONS INFORMATION

One of the three basic LTC1266 application circuits is shown in Figure 1. This circuit uses an N-channel topside driver and a single supply. The other two circuit configurations (see Typical Applications) use an N-channel topside driver and dual supply, and a P-channel topside driver. Selections of other external components are driven by the load requirement and are the same for all three circuit configurations. The first

step is the selection of  $R_{SENSE}$ . Once  $R_{SENSE}$  is known,  $C_T$  and L can be chosen. Next, the power MOSFETs and D1 are selected. Finally,  $C_{IN}$  and  $C_{OUT}$  are selected and the loop is compensated. Using an N-channel topside switch, input voltages are limited to a maximum of about 15V. With a P-channel, the input voltage may be as high as 20V.

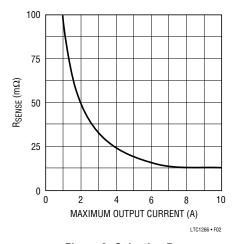

#### **RSENSE Selection for Output Current**

$R_{SENSE}$  is chosen based on the required output current. The LTC1266 series current comparator has a threshold range which extends from a minimum of 25mV/ $R_{SENSE}$  (when Burst Mode operation is enabled) to a maximum of 155mV/ $R_{SENSE}$ . The current comparator threshold sets the peak of the inductor ripple current, yielding a maximum output current  $I_{MAX}$  equal to the peak value less half the peak-to-peak ripple current. For proper Burst Mode operation,  $I_{RIPPLE(P-P)}$  must be less than or equal to the minimum current comparator threshold.

Since efficiency generally increases with ripple current, the maximum allowable ripple current is assumed, i.e.,  $I_{RIPPLE(P-P)} = 25 \text{mV/R}_{SENSE}$  (see  $C_T$  and L Selection for Operating Frequency). Solving for  $R_{SENSE}$  and allowing a margin for variations in the LTC1266 series and external component values yields:

$$R_{SENSE} = \frac{100mV}{I_{MAX}}$$

A graph for selecting  $R_{SENSE}$  vs maximum output current is given in Figure 2.

Figure 2. Selecting R<sub>SENSE</sub>

The load current, below which Burst Mode operation commences, ( $I_{BURST}$ ), and the peak short circuit current, ( $I_{SC(PK)}$ ), both track  $I_{MAX}$ . Once  $R_{SENSE}$  has been chosen,  $I_{BURST}$  and  $I_{SC(PK)}$  can be predicted from the following:

$$I_{BURST} \approx \frac{15mV}{R_{SENSE}}$$

$$I_{SC(PK)} = \frac{155mV}{R_{SENSE}}$$

The LTC1266 series automatically extends  $t_{OFF}$  during a short circuit to allow sufficient time for the inductor current to decay between switch cycles. The resulting ripple current causes the average short circuit current  $l_{SC(AVG)}$  to be reduced to approximately  $l_{MAX}$ .

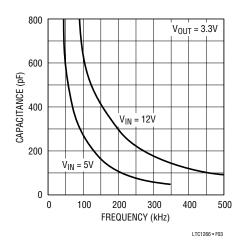

#### L and C<sub>T</sub> Selection for Operating Frequency

The LTC1266 series uses a constant off-time architecture with  $t_{OFF}$  determined by an external timing capacitor  $C_T$ . Each time the topside MOSFET switch turns on, the voltage on  $C_T$  is reset to approximately 3.3V. During the off-time,  $C_T$  is discharged by a current which is proportional to  $V_{OUT}$ . The voltage on  $C_T$  is analogous to the current in inductor L, which likewise decays at a rate proportional to  $V_{OUT}$ . Thus the inductor value must track the timing capacitor value.

The value of  $C_T$  is calculated from the desired continuous mode operating frequency, f:

$$C_T = \frac{1}{2.6 \times 10^4 \times f}$$

assumes  $V_{IN} = 2V_{OUT}$ , (Figure 1 circuit).

A graph for selecting  $C_T$  vs frequency including the effects of input voltage is given in Figure 3.

Figure 3. Timing Capacitor Value

As the operating frequency is increased the gate charge losses will be higher, reducing efficiency (see Efficiency Considerations). The complete expression for operating frequency of the circuit in Figure 1 is given by:

$$f = \frac{1}{t_{OFF}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

where:

$$t_{OFF} = 1.3 \times 10^4 \times C_T \times \left(\frac{V_{REG}}{V_{OUT}}\right)$$

$V_{REG}$  is the desired output voltage (i.e., 5V, 3.3V).  $V_{OUT}$  is the measured output voltage. Thus  $V_{REG}/V_{OUT} = 1$  in regulation.

Once the frequency has been set by  $C_T$ , the inductor L must be chosen to provide no more than  $25 \text{mV/R}_{SENSE}$  of peak-to-peak inductor ripple current. This results in a minimum required inductor value of:

$$L_{MIN} = 5.1 \times 10^5 \times R_{SENSE} \times C_T \times V_{REG}$$

As the inductor value is increased from the minimum value, the ESR requirements for the output capacitor are eased at the expense of efficiency. If too small an inductor is used, the inductor current will decrease past zero and change polarity. A consequence of this is that the LTC1266 series may not enter Burst Mode operation and efficiency will be slightly degraded at low currents.

#### **Inductor Core Selection**

Once the minimum value for L is known, the type of inductor must be selected. The highest efficiency will be obtained using ferrite, Kool  $M\mu^{\otimes}$  on molypermalloy (MPP) cores. Lower cost powdered iron cores provide suitable performance but cut efficiency by 3% to 7%. Actual core loss is independent of core size for a fixed inductor value, but it is very dependent on inductance selected. As inductance increases, core losses go down. Unfortunately, increased inductance requires more turns of wire and therefore copper losses increase.

Ferrite designs have very low core loss, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates "hard," which means that inductance collapses abruptly when the peak design cur-

rent is exceeded. This results in an abrupt increase in inductor ripple current and consequent output voltage ripple which can cause Burst Mode operation to be falsely triggered. Do not allow the core to saturate!

Kool M $\mu$  is a very good, low loss core material for toroids, with a "soft" saturation characteristic. Molypermalloy is slightly more efficient at high (>200kHz) switching frequency. Toroids are very space efficient, especially when you can use several layers of wire. Because they generally lack a bobbin, mounting is more difficult. However, new designs for surface mount are available from Coiltronics and Beckman Industrial Corp. which do not increase the height significantly.

#### **Power MOSFET and D1 Selection**

Two external power MOSFETs must be selected for use with the LTC1266 series: either a P-channel MOSFET or an N-channel MOSFET for the main switch and an N-channel MOSFET for the synchronous switch. The main selection criteria for the power MOSFETs are the type of MOSFET, threshold voltage  $V_{GS(TH)}$  and on-resistance  $R_{DS(ON)}$ .

The cost and maximum output current determine the type of MOSFET for the topside switch. N-channel MOSFETs have the advantage of lower cost and lower  $R_{DS(0N)}$  at the expense of slightly increased circuit complexity. For lower current applications where the losses due to  $R_{DS(0N)}$  are small, a P-channel MOSFET is recommended due to the lower circuit complexity. However, at load currents in excess of 3A where the  $R_{DS(0N)}$  becomes a significant portion of the total power loss, an N-channel is strongly recommended to maximize efficiency.

The maximum output current  $I_{MAX}$  determines the  $R_{DS(ON)}$  requirement for the two MOSFETs. When the LTC1266 series is operating in continuous mode, the simplifying assumption can be made that one of the two MOSFETs is always conducting the average load current. The duty cycles for the two MOSFETs are given by:

TopSide Duty Cycle =

$$\frac{V_{OUT}}{V_{IN}}$$

Bottom-Side Duty Cycle =

$$\frac{V_{IN} - V_{OUT}}{V_{IN}}$$

Kool  $\text{M}\mu$  is a registered trademark of Magnetics, Inc.

From the duty cycles, the required  $R_{DS(ON)}$  for each MOSFET can be derived:

$$\begin{split} \text{TS R}_{DS(ON)} &= \quad \frac{V_{IN} \times P_T}{V_{OUT} \times I_{MAX}^2 \times (1 + \delta_T)} \\ \text{BS R}_{DS(ON)} &= \quad \frac{V_{IN} \times P_B}{(V_{IN} - V_{OUT}) \times I_{MAX}^2 \times (1 + \delta_B)} \end{split}$$

where  $P_T$  and  $P_B$  are the allowable power dissipations and  $\delta_T$  and  $\delta_B$  are the temperature dependencies of  $R_{DS(ON)}.\,P_T$  and  $P_B$  will be determined by efficiency and/or thermal requirements (see Efficiency Considerations). For a MOSFET,  $(1+\delta)$  is generally given in the form of a normalized  $R_{DS(ON)}$  vs temperature curve, but  $\delta_{PCH}=0.007/^{\circ}C$  and  $\delta_{NCH}=0.005/^{\circ}C$  can be used as an approximation for low voltage MOSFETs.

The minimum input voltage determines whether standard threshold or logic-level threshold MOSFETs must be used. For  $V_{\text{IN}} > 8V$ , standard threshold MOSFETs ( $V_{\text{GS}(\text{TH})} < 4V$ ) may be used. If  $V_{\text{IN}}$  is expected to drop below 8V, logic-level threshold MOSFETs ( $V_{\text{GS}(\text{TH})} < 2.5V$ ) are strongly recommended. The LTC1266 series Power  $V_{\text{IN}}$  must always be less than the absolute maximum  $V_{\text{GS}}$  ratings for the MOSFETs.

The Schottky diode D1 shown in Figure 1 only conducts during the deadtime between the conduction of the two power MOSFETs. D1's sole purpose in life is to prevent the body diode of the bottom-side MOSFET from turning on and storing charge during the deadtime, which could cost as much as 1% in efficiency (although there are no other harmful effects if D1 is omitted). Therefore, D1 should be selected for a forward voltage of less than 0.7V when conducting  $I_{MAX}$ .

## CIN and COUT Selection

In continuous mode, the current through the topside MOSFET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . To prevent large voltage transients, a low ESR (Effective Series Resistance) input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:

$$C_{IN} \text{ Required } I_{RMS} \approx I_{MAX} \, \frac{[V_{OUT}(V_{IN} - V_{OUT})]^{1/2}}{V_{IN}}$$

This formula has a maximum at  $V_{IN}=2V_{OUT}$ , where  $I_{RMS}=I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that capacitor manufacturer's ripple current ratings are often based on only 2000 hours of life. This makes it advisable to further derate the capacitor, or to choose a capacitor rated at a higher temperature than required. Always consult the manufacturer if there is any question. An additional  $0.1\mu F$  to  $1\mu F$  ceramic capacitor is also required on Power  $V_{IN}$  (Pin 2) for high frequency decoupling.

The selection of  $C_{OUT}$  is driven by the required ESR. The ESR of  $C_{OUT}$  must be less than twice the value of  $R_{SENSE}$  for proper operation of the LTC1266 series:

Cout Required ESR < 2R<sub>SENSE</sub>

Optimum efficiency is obtained by making the ESR equal to  $R_{SENSE}$ . As the ESR is increased up to  $2R_{SENSE}$ , the efficiency degrades by less than 1%. If the ESR is greater than  $2R_{SENSE}$ , the voltage ripple on the output capacitor will prematurely trigger Burst Mode operation, resulting in disruption of continuous mode and an efficiency hit which can be several percent. If Burst Mode operation is disabled, the ESR requirement can be relaxed and is limited only by the allowable output voltage ripple.

Manufacturers such as Nichicon and United Chemicon should be considered for high performance capacitors. The OS-CON semiconductor dielectric capacitor available from Sanyo has the lowest ESR/size ratio of any aluminum electrolytic at a somewhat higher price. Once the ESR requirement for  $C_{OUT}$  has been met, the RMS current rating generally far exceeds the  $I_{RIPPLE(P-P)}$  requirement.

In surface mount applications multiple capacitors may have to be paralleled to meet the capacitance, ESR or RMS current handling requirements of the application. An excellent choice is the AVX TPS series of surface mount tantalums.

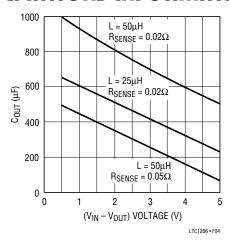

At low supply voltages, a minimum capacitance at  $C_{OUT}$  is needed to prevent an abnormal low frequency operating mode (see Figure 4). When  $C_{OUT}$  is made too small, the output ripple at low frequencies will be large enough to trip the voltage comparator. This causes Burst Mode operation to be activated when the LTC1266

Figure 4. Minimum Value of Cout

series would normally be in continuous operation. The output remains in regulation at all times. This minimum capacitance requirement may be relaxed if Burst Mode operation is disabled.

#### **N-Channel vs P-Channel MOSFETs**

The LTC1266 has the capability to drive either an N-channel or a P-channel topside switch to give the user more flexibility. N-channel MOSFETs are superior in performance to P-channel due to their lower  $R_{DS(ON)}$  and lower gate capacitance and are typically less expensive; however, they do have a slightly more complicated gate drive requirement and a more limited input voltage range (see following sections).

#### **Driving P-Channel Topside MOSFETs**

The P-channel topside switch circuit configuration is the most straightforward due to the requirement of only one supply voltage level. This is due to the negative gate threshold of the P-channel MOSFET which allows the MOSFET to be switched on and off by swinging the gate between  $V_{IN}$  and ground. The phase invert (Pin 3) is tied to ground to choose this operating mode. Normally, the converter input ( $V_{IN}$ ) is connected to the LTC1266 supply Pins 2 and 5 and can go as high as 20V. Pin 2 supplies the high frequency current pulses to switch the MOSFETs and should be decoupled with a  $0.1\mu F$  to  $1\mu F$  ceramic capacitor. Pin 5 supplies most of the quiescent power to the rest of the chip.

#### **Driving N-Channel Topside MOSFETs**

Driving an N-channel topside MOSFET (PINV, Pin 3, tied to PWR  $V_{IN}$ ) is a little trickier than driving a P-channel since the gate voltage must be positive with respect to the source to turn it on, which means that the gate voltage must be higher than  $V_{IN}$ . This requires either a second supply at least  $V_{GS(ON)}$  above  $V_{IN}$  or a bootstrapping circuit to boost the  $V_{IN}$  to the proper level. The easiest method is using a higher supply (see Figure 14) but if one is not available, the bootstrap method can be used at the expense of an additional diode (see Figure 1). The bootstrap works by charging the bootstrap capacitor to  $V_{IN}$  during the off-time. During the on-time, the bottom plate of the capacitor is pulled up to  $V_{IN}$  so that the voltage at Pin 2 is now twice  $V_{IN}$  (plus any ringing on the switch node).

Since the maximum allowable voltage at Pin 2 is 20V, the Figure 1 bootstrap circuit limits  $V_{IN}$  to less than 10V. A higher  $V_{IN}$  can be achieved if the bootstrap capacitor is charged to a voltage less than  $V_{IN}$ , in which case  $V_{IN(MAX)} = 20 - V_{CAP}$ .

N-channel mode, internal circuitry limits the maximum on-time to  $60\mu s$  to guarantee start-up of the bootstrap circuit. This maximum on-time reduces the maximum duty cycle to:

Max Duty Cycle =

$$\frac{60\mu s}{60\mu s + t_{OFF}}$$

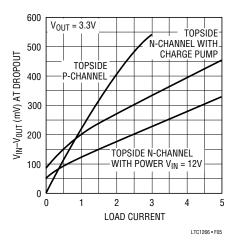

which slightly increases the minimum input voltage at which dropout occurs. However, because of the superior on-conductance of the N-channel, the dropout performance of an all N-channel regulator is still better (see Figure 5) even with the duty cycle limitation, except at light loads.

#### **Low-Battery Comparator**

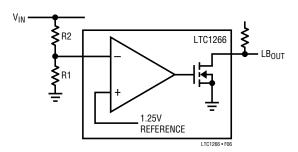

The LTC1266 has an on-chip low-battery comparator which can be used to sense a low-battery condition when implemented as shown in Figure 6. The resistor divider R1, R2 sets the comparator trip point as follows:

$$V_{TRIP} = 1.25 \left( 1 + \frac{R2}{R1} \right)$$

Figure 5. Comparison of Dropout Performance

Figure 6. Low-Battery Comparator

The divided down voltage at the "-" input to the comparator is compared to an internal 1.25V reference. This reference is separate from the 1.25V reference used by the voltage comparator and current comparator for regulation and is not disabled by the shutdown pin, therefore the low-battery detection is operational even when the rest of the chip is shut down. The comparator is functional down to an input voltage of 2.5V. Thus, the output will provide a valid state even when the rest of the chip does not have sufficient voltage to operate. For best performance, the value of the pull-up resistor should be high enough that the output is pulled down to ground when sinking 200µA or less.

#### **Suppressing Burst Mode Operation**

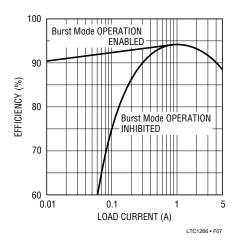

Normally, enabling Burst Mode operation is desired due to its superior efficiency at low load currents (see Figure 7).

However, in certain applications it may be desirable to inhibit this feature. Some reasons for doing so are:

To eliminate audible noise from certain types of inductors at light loads.

Figure 7. Effect of Disabling Burst Mode Operation on Efficiency

- 2. If the load is never expected to drop low enough to benefit from the efficiency advantages of Burst Mode operation, the output capacitor ESR and minimum capacitance requirements (which may falsely trigger Burst Mode operation if not met) can be relaxed if Burst Mode operation is disabled.

- 3. If an auxiliary winding is used. Disabling Burst Mode operation guarantees switching independent of the load on the primary. This allows power to be taken from the auxiliary winding independently.

- 4. Tighter load regulation (< 1%).

Burst Mode operation is disabled by applying a CMOS logic high voltage (>2.1V) to Pin 4. When it is disabled, the voltage comparator limit is raised high enough so that it no longer is involved in regulation; however it is still active and is useful as a voltage clamp to keep the output from overshooting.

Note that since the inductor current must reverse to regulate the output at zero load when Burst Mode operation is disabled, the minimum inductance ( $L_{MIN}$ ) specified during Inductor Core Selection is no longer applicable.

#### **Checking Transient Response**

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in DC (resistive) load current. When a load step occurs,  $V_{OUT}$  shifts by an amount equal to  $\Delta I_{LOAD}$  (ESR), where ESR is the effective series resistance of  $C_{OUT}$ .  $\Delta I_{LOAD}$  also begins to charge or

discharge  $C_{OUT}$  until the regulator loop adapts to the current change and returns  $V_{OUT}$  to its steady-state value. During this recovery time  $V_{OUT}$  can be monitored for overshoot or ringing which would indicate a stability problem. The Pin 7 external components shown in the Figure 1 circuit will prove adequate compensation for most applications.

#### **Efficiency Considerations**

The percent efficiency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Percent efficiency can be expressed as:

% Efficiency =

$$100\% - (L1 + L2 + L3 + ...)$$

where L1, L2, etc., are the individual losses as a percentage of input power. (For high efficiency circuits, only small errors are incurred by expressing losses as a percentage of output power).

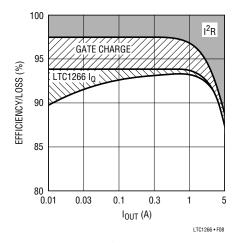

Although all dissipative elements in the circuit produce losses, three main sources usually account for most of the losses in LTC1266 series circuits: 1) LTC1266 DC bias current, 2) MOSFET gate charge current and 3) I<sup>2</sup>R losses.

- 1. The DC supply current is the current which flows into  $V_{IN}$  (Pin 2). For  $V_{IN}=10V$  the LTC1266 DC supply current is  $170\mu A$  for no load, and increases proportionally with load up to a constant 2.1mA after the LTC1266 series has entered continuous mode. Because the DC bias current is drawn from  $V_{IN}$ , the resulting loss increases with input voltage. For  $V_{IN}=5V$  the DC bias losses are generally less than 1% for load currents over 30mA. However, at very low load currents the DC bias current accounts for nearly all of the loss.

- 2. MOSFET gate charge current results from switching the gate capacitance of the power MOSFETs. Each time a MOSFET gate is switched from low to high to low again, a packet of charge dQ moves from Power  $V_{IN}$  to ground. The resulting dQ/dt is a current flowing into Power  $V_{IN}$  (Pin 5) which is typically much larger than the DC supply current. In continuous mode,  $I_{GATECHG} = f(Q_N + Q_P)$ . The typical gate charge for a 0.05 $\Omega$  N-channel

power MOSFET is 15nC. This results in  $I_{GATECHG}$  = 6mA in 200kHz continuous operation for a 2% to 3% typical mid-current loss with  $V_{IN}$  = 5V.

Note that the gate charge loss increases directly with both input voltage and operating frequency. This is the principal reason why the highest efficiency circuits operate at moderate frequencies. Furthermore, it argues against using larger MOSFETs than necessary to control I<sup>2</sup>R losses, since overkill can cost efficiency as well as money!

3. I<sup>2</sup>R losses are easily predicted from the DC resistances of the MOSFET, inductor and current shunt. In continuous mode the average output current flows through L and R<sub>SENSE</sub>, but is "chopped" between the topside and bottom-side MOSFETs. If the two MOSFETs have approximately the same R<sub>DS(ON)</sub>, then the resistance of one MOSFET can simply be summed with the resistances of L and R<sub>SENSE</sub> to obtain I<sup>2</sup>R losses. For example, if each R<sub>DS(ON)</sub> = 0.05 $\Omega$ , R<sub>L</sub> = 0.05 $\Omega$  and R<sub>SENSE</sub> = 0.02 $\Omega$ , then the total resistance is 0.12 $\Omega$ . This results in losses ranging from 3.5% to 15% as the output current increases from 1A to 5A. I<sup>2</sup>R losses cause the efficiency to roll off at high output currents.

Figure 8 shows how the efficiency losses in a typical LTC1266 series regulator end up being apportioned. The gate charge loss is responsible for the majority of the efficiency lost in the mid-current region. If Burst Mode operation was not employed at low currents, the gate charge loss alone would cause efficiency to drop to

Figure 8. Efficiency Loss

unacceptable levels (see Figure 7). With Burst Mode operation, the DC supply current represents the lone (and unavoidable) loss component which continues to become a higher percentage as output current is reduced. As expected the I<sup>2</sup>R losses dominate at high load currents.

Other losses including  $C_{IN}$  and  $C_{OUT}$  ESR dissipative losses, MOSFET switching losses, Schottky conduction losses during deadtime and inductor core losses, generally account for less than 2% total additional loss.

#### **Design Example**

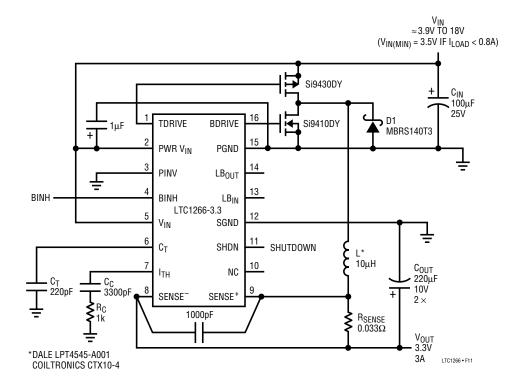

As a design example, assume  $V_{IN}=5V$  (nominal),  $V_{OUT}=3.3V$ ,  $I_{MAX}=5A$  and f=200kHz;  $R_{SENSE}$ ,  $C_T$  and L can immediately be calculated:

$$\begin{split} R_{SENSE} &= 100 mV/5 = 0.02 \Omega \\ t_{OFF} &= (1/200 kHz) \times [1 - (3.3/5)] = 1.7 \mu s \\ C_T &= 1.7 \mu s/(1.3 \times 10^4) = 130 pF \\ L_{MIN} &= 5.1 \times 10^5 \times 0.02 \Omega \times 130 pF \times 3.3 V = 5 \mu H \end{split}$$

Assume that the MOSFET dissipations are to be limited to  $P_T = P_B = 2W$ .

If  $T_A$  = 40°C and the thermal resistance of each MOSFET is 50°C/W, then the junction temperatures will be 140°C and  $\delta_T$  =  $\delta_B$  = 0.60. The required  $R_{DS(0N)}$  for each MOSFET can now be calculated:

TS

$$R_{DS(ON)} = \frac{5(2)}{3.3(5)^2 (1.60)} = 0.076\Omega$$

BS

$$R_{DS(ON)} = \frac{5(2)}{1.7(5)^2 (1.60)} = 0.147\Omega$$

The topside FET requirement can be met by an N-channel Si9410DY which has an  $R_{DS(0N)}$  of about  $0.04\Omega$  at  $V_{GS}=5V$ . The bottom-side FET requirement is exceeded by an Si9410DY. Note that the most stringent requirement for the bottom-side MOSFET is with  $V_{OUT}=0$  (i.e., short circuit). During a continuous short circuit, the worst-case dissipation rises to:

$$P_B = I_{SC(AVG)}^2 \times R_{DS(ON)} \times (1 + \delta_B)$$

With the  $0.02\Omega$  sense resistor,  $I_{SC(AVG)} \approx 6A$  will result, increasing the  $0.04\Omega$  bottom-side FET dissipation to 2.3W.

$C_{IN}$  will require an RMS current rating of at least 2.5A at temperature and  $C_{OUT}$  will require an ESR of 0.02 $\Omega$  for optimum efficiency.

Now allow  $V_{IN}$  to drop to its minimum value. The minimum  $V_{IN}$  can be calculated from the maximum duty cycle and voltage drop across the topside FET,

$$V_{MIN} = \frac{V_{OUT} + I_{LOAD} \times (R_{DS(ON)} + R_L + R_{SENSE})}{D_{MAX}} = 4.0V$$

At this lower input voltage, the operating frequency decreases and the topside FET will be conducting most of the time, causing the power dissipation to increase. At dropout,

$$f_{MIN} = \frac{1}{t_{ON (MAX)} + t_{OFF}} = 16kHz$$

$$P_T = I^2_{LOAD} \times R_{DS(ON)} \times (1 + \delta_T) \times D_{MAX}$$

This last step is necessary to assure that the power dissipation and junction temperature of the topside FET are not exceeded.

These last calculations assume that Power  $V_{IN}$  is high enough to keep the topside FET fully turned on at dropout, as would be the case with the Figure 11circuit. If this isn't true (as with the Figure 1 circuit) the  $R_{DS(ON)}$  will increase which in turn increases  $V_{MIN}$  and  $P_T$ .

## **Adjustable Applications**

When an output voltage other than 3.3V or 5V is required, the LTC1266 adjustable version is used with an external resistive divider from  $V_{OUT}$  to  $V_{FB}$ , Pin 10. The regulated voltage is determined by:

$$V_{OUT} = 1.25 \left( 1 + \frac{R2}{R1} \right)$$

To prevent stray pickup a 100pF capacitor is suggested across R1 located close to the LTC1266.

For Figure 1 applications with  $V_{OUT}$  below 2V, or when  $R_{SENSE}$  is moved to ground, the current sense comparator inputs operate near ground. When the current comparator is operated at less than 2V common mode, the off-time increases approximately 40%, requiring the use of a smaller timing capacitor  $C_T$ .

#### **Troubleshooting Hints**

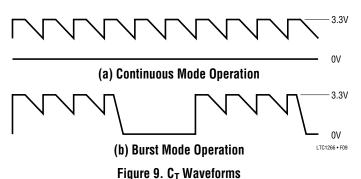

Since efficiency is critical to LTC1266 series applications, it is very important to verify that the circuit is functioning correctly in both continuous and Burst Mode operation. The waveform to monitor is the voltage on the timing capacitor, Pin 6.

In continuous mode ( $I_{LOAD} > I_{BURST}$ ) the voltage on the  $C_T$  pin should be a sawtooth with a  $0.9V_{P-P}$  swing. This voltage should never dip below 2V as shown in Figure 9a.

When load currents are low ( $I_{LOAD} < I_{BURST}$ ) Burst Mode operation should occur with the  $C_T$  pin waveform periodically falling to ground for periods of time as shown in Figure 9b.

If Pin 6 is observed falling to ground at high output currents, it indicates poor decoupling or improper grounding. Refer to the Board Layout Checklist.

#### **Board Layout Checklist**

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the LTC1266 series. These items are also illustrated graphically in the layout diagram of Figure 10. Check the following in your layout:

- Are the signal and power grounds segregated? The LTC1266 signal ground (Pin 12) must return to the (-) plate of C<sub>OUT</sub>. The power ground returns to the source of the bottom-side MOSFET, anode of the Schottky diode and (-) plate of C<sub>IN</sub>, which should have as short lead lengths as possible.

- 2. Does the LTC1266 Sense $^-$  (Pin 8) connect to a point close to R<sub>SENSE</sub> and the (+) plate of C<sub>OUT</sub>? In adjustable applications, the resistive divider R1 and R2 must be connected between the (+) plate of C<sub>OUT</sub> and signal ground.

Figure 10. LTC1266 Layout Diagram (See Layout Checklist)

- 3. Are the Sense and Sense leads routed together with minimum PC trace spacing? The 1000pF capacitor between Pins 8 and 9 should be as close as possible to the LTC1266.

- 4. Does the (+) plate of  $C_{\text{IN}}$  connect to the source of the topside MOSFET as closely as possible? This capacitor provides the AC current to the topside MOSFET.

- 5. A  $0.1\mu F$  to  $1\mu F$  decoupling capacitor connected between  $V_{IN}$  (Pin 5) and ground is optional, but is some-

- times helpful in eliminating instabilities at high input voltage and high output loads.

- 6. Is the Shutdown (Pin 11) actively pulled to ground during normal operation? The Shutdown pin is high impedance and must not be allowed to float. The Select (Pins 3 and 4) are also high impedance and must be tied high or low depending on the application.

## TYPICAL APPLICATIONS (Layout Assist Schematics)

Figure 11. Low Dropout, 3.3V/3A High Efficiency Regulator

# TYPICAL APPLICATIONS (Layout Assist Schematics)

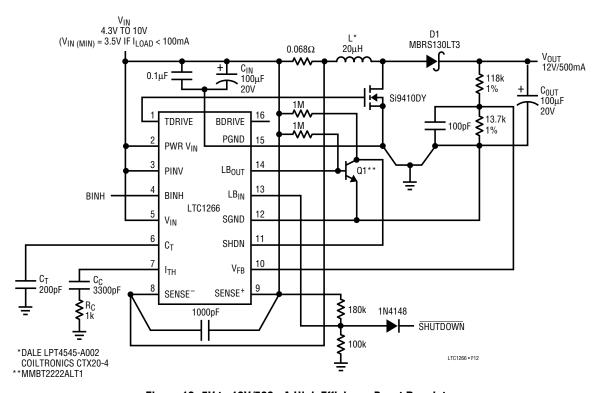

Figure 12. 5V to 12V/500mA High Efficiency Boost Regulator

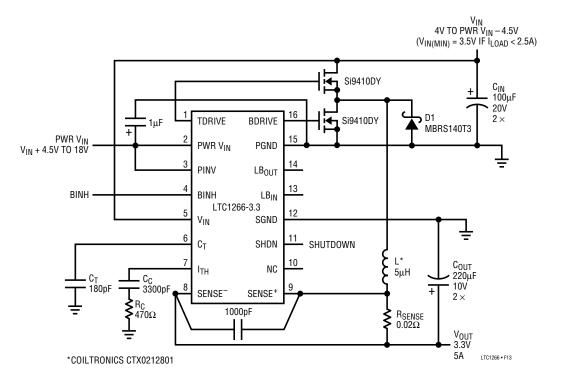

Figure 13. All N-Channel 5V to 3.3V/5A Converter with Drivers Powered from External PWR VIN Supply

# TYPICAL APPLICATIONS (Layout Assist Schematics)

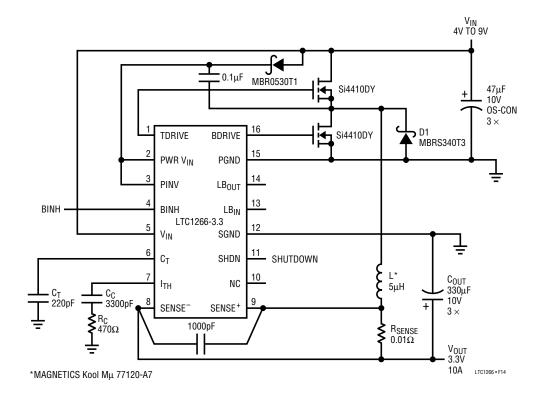

Figure 14. All N-Channel 5V to 3.3V/10A High Efficiency Regulator

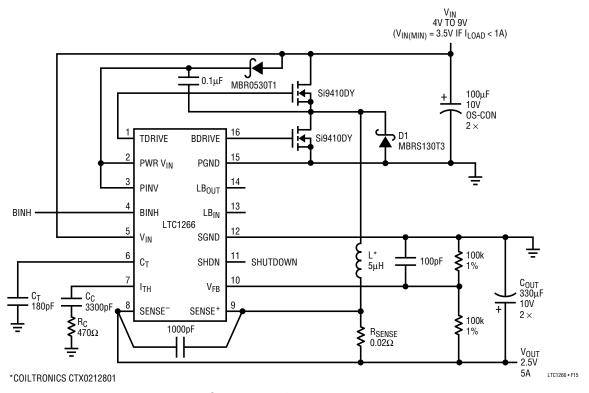

Figure 15. All N-Channel 5V to 2.5V/5A High Efficiency Regulator

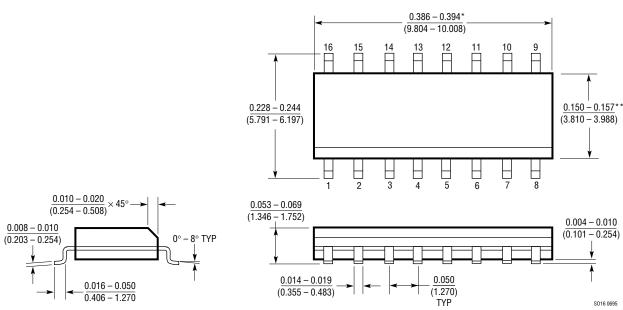

PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### S Package 16-Lead Plastic SOIC

<sup>\*</sup>DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                     | COMMENTS                                                    |

|-------------|-----------------------------------------------------------------|-------------------------------------------------------------|

| LTC1142     | Dual High Efficiency Synchronous Step-Down Switching Regulator  | Dual Version of LTC1148                                     |

| LTC1143     | Dual High Efficiency Step-Down Switching Regulator Controller   | Dual Version of LTC1147                                     |

| LTC1147     | High Efficiency Step-Down Switching Regulator Controller        | Nonsynchronous, 8-Lead, V <sub>IN</sub> ≤ 16V               |

| LTC1148     | High Efficiency Step-Down Switching Regulator Controller        | Synchronous, V <sub>IN</sub> ≤ 20V                          |

| LTC1149     | High Efficiency Step-Down Switching Regulator                   | Synchronous, $V_{IN} \le 48V$ , for Standard Threshold FETs |

| LTC1159     | High Efficiency Synchronous Step-Down Switching Regulator       | V <sub>IN</sub> ≤ 40V, for Logic Level FETs                 |

| LTC1174     | High Efficiency Step-Down and Inverting DC/DC Converter         | 0.5A Switch, V <sub>IN</sub> ≤ 18.5V, Comparator            |

| LTC1265     | High Efficiency Step-Down DC/DC Converter                       | 1.2A Switch, V <sub>IN</sub> ≤ 13V, Comparator              |

| LTC1267     | Dual High Efficiency Synchronous Step-Down Switching Regulators | Dual Version of LTC1159                                     |

<sup>\*\*</sup>DIMENSION DOES NOT INCLUDE INTERLEAD FLASH, INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE