# PRELIMINARY PRODUCT INFORMATION

# MOS INTEGRATED CIRCUIT $\mu PD63711$

## COMPACT DISC DIGITAL SERVO/DATA PROCESSOR WITH ON-CHIP RF AMPLIFIER

The  $\mu$ PD63711 is an LSI that has all of the functions required to control a CD player, with a digital servo, data processor, RF amplifier, audio DAC, and post-processing filter incorporated on a single chip. CD-TEXT is also supported.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.  $\mu$ PD63711 User's Manual: To be prepared

#### **FEATURES**

- Realization of set miniaturization by integrating a digital servo, data processor, 8-fs oversampling digital filter, D/A converter, and RF amplifier on a single chip.

- On-chip SCF (Switched Capacitor Filter) as audio DAC block post-processing filter

- Employment of digital loop filter for four servo systems. Since the filter coefficient is programmable, a variety of characteristics can be realized.

- On-chip automatic adjustment function. Automatic adjustments of focus offset, focus gain, focus balance, tracking offset, tracking gain, and tracking balance are possible.

- · On-chip 16-Kbit SRAM needed for de-interleaving.

- Since a digital PLL circuit is employed, the external components of the bit clock regeneration circuit are not needed.

- CIRC error correction capability C1: Double correction C2: Quadruple correction (CD-ROM mode)

- On-chip fourth order  $\Delta\Sigma$  type one-bit D/A converter and post-processing filter

- On-chip mirror circuit, DEFECT circuit, RFOK circuit, and EFM comparator.

- A de-emphasis circuit can be controlled via a microcontroller for supporting connection with shock-proof ICs.

- Crystal oscillation stop function

- · Pickup of both current and voltage output can be supported.

- Single 5-V power supply

#### ORDERING INFORMATION

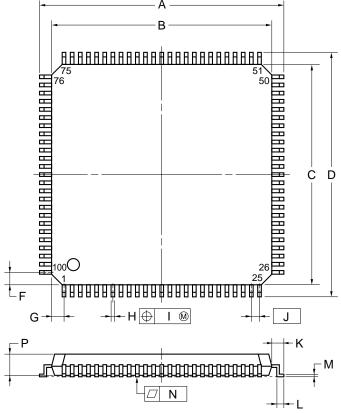

| Part Number    | Package                                        |

|----------------|------------------------------------------------|

| μPD63711GC-8EU | 100-pin plastic LQFP (fine pitch) (14 × 14 mm) |

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

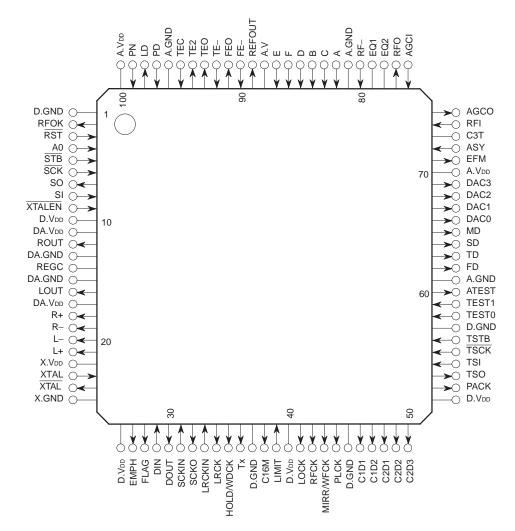

## PIN CONFIGURATION (Top View)

• 100-pin plastic LQFP (fine pitch) (14  $\times$  14 mm)  $\mu$ PD63711GC-8EU

/ww.DataSheet4U.cor

NEC  $\mu$ PD63711

| A, C, B, D, F, E:    | Error Signal Input                    | PLCK:       | PLL Lock                             |

|----------------------|---------------------------------------|-------------|--------------------------------------|

| A.GND:               | Analog Ground                         | PN:         | APC Circuit Polarity Control         |

| A.V <sub>DD</sub> :  | Analog Power Supply                   | LIMIT:      | Pick Inner Detect                    |

| A0:                  | Address 0                             | R+, R-:     | R-channel Sound Data Output (PWM)    |

| AGCI:                | AGC Amp Input                         | REFOUT:     | Reference Output                     |

| AGCO:                | AGC Amp Output                        | REGC:       | Capacitor Connection for Regulator   |

| ASY:                 | Slice Level                           | RF-:        | Impedance Connection to RF Amp for   |

| ATEST:               | Analog Test                           |             | Negative Feedback                    |

| C16M:                | Clock 16 MHz                          | RFCK:       | Read Frame Clock                     |

| C1D1, C1D2,:         | Correction Data                       | RFI:        | RF Signal Input                      |

| C2D1 to C2D3         |                                       | RFO:        | RF Amp Output                        |

| C3T:                 | Capacitance Connection for 3T Signal  | RFOK:       | RFOK Signal                          |

|                      | Detecting Circuit                     | ROUT:       | R-channel Audio Signal Output        |

| D.GND:               | Digital Ground                        | RST:        | Reset                                |

| D.V <sub>DD:</sub>   | Digital Power Supply                  | SCK:        | Serial Clock                         |

| DA.GND:              | D/A Converter Ground                  | SCKIN:      | Serial Clock Input                   |

| DA.V <sub>DD</sub> : | D/A Converter Power Supply            | SCKO:       | Serial Clock Output                  |

| DAC0 to DAC3:        | D/A Converter Output                  | SD:         | Sled Drive                           |

| DIN:                 | Data Input                            | SI:         | Serial Data Input                    |

| DOUT:                | Data Output                           | SO:         | Serial Data Output                   |

| EFM:                 | EFM Signal                            | STB:        | Strobe                               |

| EMPH:                | Emphasis                              | TD:         | Tracking Drive                       |

| EQ1, EQ2:            | Equalizer Parts Connection for RF Amp | TE:         | Tracking Error                       |

| FD:                  | Focus Drive                           | TE-:        | Impedance Connection to Tracking     |

| FE:                  | Focus Error                           |             | Error Amp for Negative Feedback      |

| FE-:                 | Impedance Connection to Focus Error   | TE2:        | Tracking Error Amp Output Multiplied |

|                      | Amp for Negative Feedback             |             | by Two                               |

| FEO:                 | Focus Error Amp Output                | TEC:        | Tracking Error Comparator            |

| FLAG:                | Flag                                  | TEO:        | Tracking Error Amp Output            |

| HOLD/WDCK:           | Hold Control/Word Clock               | TESTO,      |                                      |

| L+, L-:              | L-channel Sound Data Output (PWM)     | TEST1:      | Test                                 |

| LD:                  | Laser Diode Control Current Output    | TSCK:       | Serial Clock for Text Data           |

| LOCK:                | Lock                                  | TSI:        | Parameter Input for Text Data        |

| LOUT:                | L-channel Audio Signal Output         | TSO:        | Serial Text Data Output              |

| LRCK:                | LR Clock                              | TSTB:       | Text Parameter Strobe                |

| LRCKIN:              | LR Clock Input                        | Tx:         | Transmit Data                        |

| MD:                  | Motor Drive                           | X.GND:      | Crystal Oscillator Ground            |

| MIRR/WFCK:           | MIRR Signal/Write Frame Clock         | X.VDD:      | Crystal Oscillator Power Supply      |

| PACK:                | Pack Signal Sync                      | XTAL, XTAL: | Crystal Connection                   |

| PD:                  | Photo Diode Signal (for Detecting     | XTALEN:     | Crystal Oscillation Enable           |

|                      |                                       |             |                                      |

Laser Power) Input

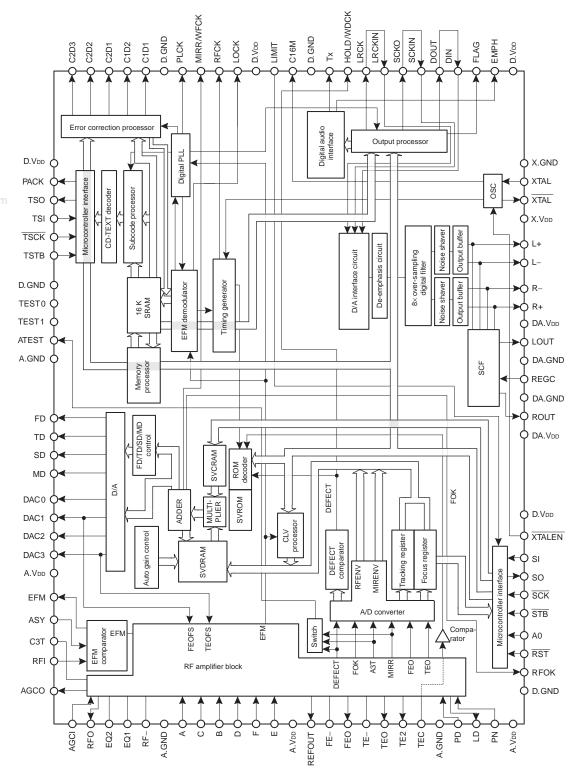

## **BLOCK DIAGRAM**

www.DataSheet4U.co

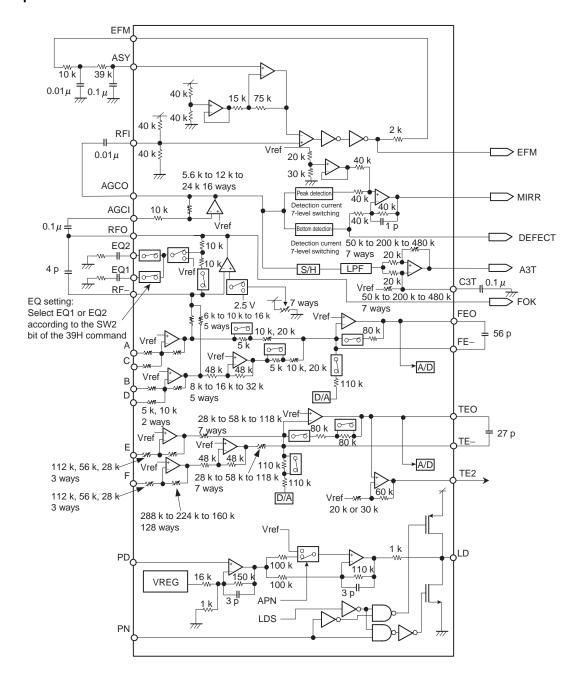

## RF amplifier block

**Remark** The unit of resistance is  $\Omega$  and capacitance is F.

www.DataSheet4U.com

# **CONTENTS**

| 1.   | PIN FUNCTIONS                         | 7  |

|------|---------------------------------------|----|

| 2.   | DIGITAL FILTER FLOWCHARTS             | 12 |

| 3.   | MICROCONTROLLER INTERFACE COMMANDS    |    |

|      | 3.1 Servo System Commands             | 16 |

|      | 3.2 RF System Commands                | 30 |

|      | 3.3 Signal Processing System Commands | 41 |

|      | 3.4 CD-TEXT Function                  |    |

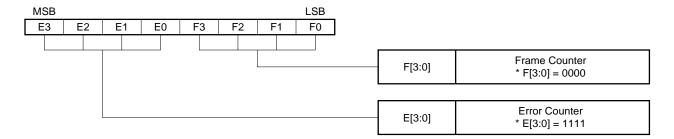

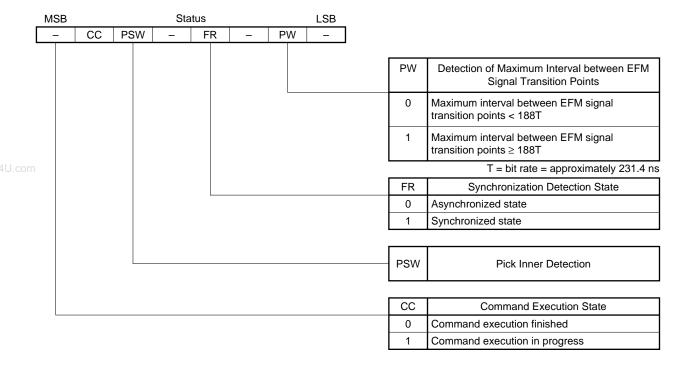

| et4U | 3.5 Status                            | 57 |

| 4.   | PACKAGE DRAWING                       | 58 |

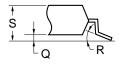

| 5    | RECOMMENDED SOLDERING CONDITIONS      | 59 |

# 1. PIN FUNCTIONS

| F | in No. | Pin Name           | Description                                                                                                                                                                                                                                                                                                            | I/O | Initial Value |

|---|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|

|   | 1      | D.GND              | Logic circuit GND                                                                                                                                                                                                                                                                                                      | -   | _             |

|   | 2      | RFOK               | RFOK signal output pin                                                                                                                                                                                                                                                                                                 | 0   | Undefined     |

|   | 3      | RST                | Reset signal input pin (Active low)                                                                                                                                                                                                                                                                                    | I   | _             |

|   | 4      | A0                 | I                                                                                                                                                                                                                                                                                                                      | -   |               |

| m | 5      | STB                | Data strobe signal input pin This is the signal for latching serial data inside the LSI.                                                                                                                                                                                                                               | ı   | _             |

|   | 6      | SCK                | Clock signal input pin for serial data input and output Input data from the SI pin is captured when this signal rises and serial data from the SO pin is output when it falls.                                                                                                                                         | I   | _             |

|   | 7      | SO                 | Outputs serial data and status signal                                                                                                                                                                                                                                                                                  | 0   | Undefined     |

|   | 8      | SI                 | Serial data input pin                                                                                                                                                                                                                                                                                                  | I   | _             |

|   | O      | XTALEN             | Crystal oscillation control pin. Be sure to input the reset signal before stopping crystal oscillation. When the status shifts from crystal oscillation stop mode to normal mode, input the reset signal after crystal oscillation has stabilized.  XTALEN = L: Normal mode  XTALEN = H: Crystal oscillation stop mode | I   | _             |

|   | 10     | D.V <sub>DD</sub>  | Positive power supply pin to logic circuit                                                                                                                                                                                                                                                                             | _   | -             |

|   | 11     | DA.V <sub>DD</sub> | Positive power supply pin to D/A converter block                                                                                                                                                                                                                                                                       | -   | _             |

|   | 12     | ROUT               | R-ch audio signal output pin                                                                                                                                                                                                                                                                                           | AO  | Undefined     |

|   | 13     | DA.GND             | D/A converter block GND                                                                                                                                                                                                                                                                                                | -   | _             |

|   | 14     | REGC               | SCF regulator external capacitor connection pin                                                                                                                                                                                                                                                                        | A-  | _             |

|   | 15     | DA.GND             | D/A converter block GND                                                                                                                                                                                                                                                                                                | _   | _             |

|   | 16     | LOUT               | L-ch audio signal output pin                                                                                                                                                                                                                                                                                           | AO  | Undefined     |

|   | 17     | DA.V <sub>DD</sub> | Positive power supply pin to D/A converter block                                                                                                                                                                                                                                                                       | -   | -             |

|   | 18     | R+                 | Right channel sound data output pin. PWM output                                                                                                                                                                                                                                                                        | 0   | L             |

|   | 19     | R-                 |                                                                                                                                                                                                                                                                                                                        |     | Н             |

|   | 20     | L–                 | Left channel sound data output pin. PWM output                                                                                                                                                                                                                                                                         | 0   | Н             |

|   | 21     | L+                 |                                                                                                                                                                                                                                                                                                                        |     | L             |

|   | 22     | X.V <sub>DD</sub>  | Positive power supply pin to crystal oscillator                                                                                                                                                                                                                                                                        | _   | _             |

|   | 23     | XTAL               | Crystal oscillator connection pin (input)                                                                                                                                                                                                                                                                              | I   | _             |

|   | 24     | XTAL               | Crystal oscillator connection pin (output)                                                                                                                                                                                                                                                                             | 0   | _             |

|   | 25     | X.GND              | Crystal oscillator GND                                                                                                                                                                                                                                                                                                 | _   | _             |

|   | 26     | D.V <sub>DD</sub>  | Positive power supply pin to logic circuit                                                                                                                                                                                                                                                                             | _   | _             |

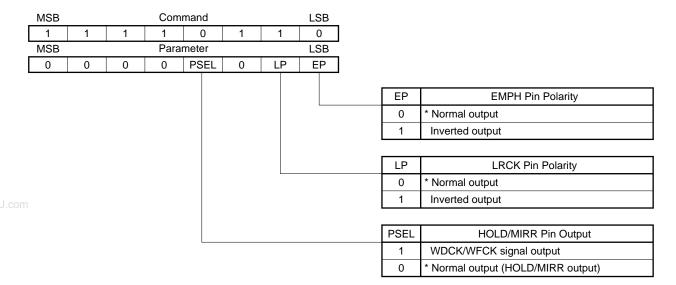

|   | 27     | EMPH               | Subcode Q pre-emphasis information output pin When applying emphasis, a high level is output. Commands can be used to switch polarity.  F6H LSB EP = 0: Normal output  EP = 1: Inverted output                                                                                                                         | 0   | Undefined     |

MANAY DataSheet411

| Pin No.          | Pin Name          | Description                                                                                                                                                                                                                                                                                                                          | I/O | Initial Value |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|

| 28               | FLAG              | Flag output pin indicating that the data currently being output was configured with uncorrectable data. (Active high)                                                                                                                                                                                                                | 0   | Undefined     |

| 29               | DIN               | Serial data input pin to on-chip DAC If a DSP (etc.) is not connected, this must be shorted with the DOUT pin.                                                                                                                                                                                                                       | I   | -             |

| 30               | DOUT              | Serial sound data output pin                                                                                                                                                                                                                                                                                                         | 0   | L             |

| 31               | SCKIN             | Serial clock input pin to on-chip DAC                                                                                                                                                                                                                                                                                                | - 1 | -             |

| 32               | SCKO              | Sound data output from DOUT changes with the falling of this clock. Ensure that the system connected in the next stage captures the data at the rising of this signal.                                                                                                                                                               | 0   | Undefined     |

| 33               | LRCKIN            | LRCK signal input pin to on-chip DAC                                                                                                                                                                                                                                                                                                 | I   | _             |

| t4U. <b>34</b> m | LRCK              | Signal that distinguishes left channel and right channel of sound data output from DOUT                                                                                                                                                                                                                                              | 0   | Undefined     |

| 35               | HOLD/<br>WDCK     | Defect detection output pin (HOLD) Pin that outputs a signal twice the frequency of LRCK (88.2 kHz) (WDCK) HOLD and WDCK can be switched by microcontroller.                                                                                                                                                                         | 0   | Undefined     |

| 36               | Tx                | Data output pin of digital audio interface                                                                                                                                                                                                                                                                                           | 0   | L             |

| 37               | D.GND             | Logic circuit GND                                                                                                                                                                                                                                                                                                                    | _   | -             |

| 38               | C16M              | Buffering output pin of oscillation clock                                                                                                                                                                                                                                                                                            | 0   | -             |

| 39               | LIMIT             | The state of this pin is output in Bit5 of the status output.                                                                                                                                                                                                                                                                        | I   | -             |

| 40               | D.V <sub>DD</sub> | Positive power supply pin to logic circuit                                                                                                                                                                                                                                                                                           | _   | -             |

| 41               | LOCK              | EFM synchronization detection signal  This is high level if the frame counter output matches the synchronization pattern detection signal in the EFM demodulation block, and low level if they do not match.                                                                                                                         | 0   | Undefined     |

| 42               | RFCK              | Frame synchronization signal of XTAL system This is the divided crystal resonator clock and indicates a period of one frame (7.35 kHz).                                                                                                                                                                                              | 0   | Undefined     |

| 43               | MIRR/<br>WFCK     | Mirror output pin (MIRR) Frame synchronization signal of PLL system. This signal is a signal with a frequency that is a division of the basic frequency (44.1 kHz) of the read signal acquired from the PLL system and is approximately equal to 1 frame cycle (7.35 kHz) (WFCK).  MIRR and WFCK can be switched by microcontroller. | 0   | Undefined     |

| 44               | PLCK              | Pin for bit clock monitor When a PLL lock occurs, the falling edge of this signal locks to the EFM signal.                                                                                                                                                                                                                           | 0   | Undefined     |

| 45               | D.GND             | Logic circuit GND                                                                                                                                                                                                                                                                                                                    | _   | _             |

| 46               | C1D1              | Output pins that indicate the results of C1 error correction                                                                                                                                                                                                                                                                         | 0   | Undefined     |

| 47               | C1D2              | These pins are defined until the falling edge of RFCK.                                                                                                                                                                                                                                                                               |     |               |

| 48               | C2D1              | Output pins that indicate the results of C2 error correction                                                                                                                                                                                                                                                                         | 0   | Undefined     |

| 49               | C2D2              | These pins are defined until the falling edge of RFCK.                                                                                                                                                                                                                                                                               |     |               |

| 50               | C2D3              |                                                                                                                                                                                                                                                                                                                                      |     |               |

| 51               | D.V <sub>DD</sub> | Positive power supply pin to logic circuit                                                                                                                                                                                                                                                                                           | -   | -             |

| 52               | PACK              | PACK synchronization signal of CD-TEXT The fall of this signal indicates the beginning of the pack.                                                                                                                                                                                                                                  | 0   | Undefined     |

www.DataShe

I/O Initial Value Pin No. Pin Name Description TSO 0 53 CD-TEXT data serial output pin Undefined TSI CD-TEXT control parameter serial input pin 54 1 TSCK 55 CD-TEXT serial clock input pin 1 56 **TSTB** CD-TEXT parameter strobe signal input pin Τ D.GND 57 Logic circuit GND 58 TEST0 Test pins. Normally, connect to GND. 59 TEST1 **ATEST** Undefined 60 Test pin. Normally, leave open. AO 61 A.GND Analog circuit GND FD 62 Focus drive output pin ΑO 1/2 A.VDD TD 1/2 A.VDD 63 Tracking drive output pin AO SD 64 Sled drive output pin AO 1/2 A.VDD 65 MD Spindle drive output pin AO 1/2 A.VDD 66 DAC<sub>0</sub> DAC output pin for adjustment. Outputs CRAM 7FH setting value. AO 1/2 A.VDD 67 DAC1 DAC output pin for adjustment. Outputs CRAM 7CH setting value. AO 1/2 A.VDD (On-chip RF FE amplifier offset) DAC2 68 DAC output pin for adjustment. Outputs CRAM 7DH setting value. AO 1/2 A.VDD 69 DAC3 DAC output pin for adjustment. Outputs CRAM 7EH setting value. AO 1/2 A.VDD (On-chip RF TE amplifier offset) 70 A.V<sub>DD</sub> Positive power supply pin to analog circuit **EFM** 71 EFM signal output pin 0 Undefined 72 ASY EFM comparator reference voltage input pin ΑI 73 C3T Capacitor connection pin for 3T detection Α-74 RFI RF signal input pin for EFM data generation ΑI 75 **AGCO** RF signal output pin after gain adjustment AO 1/2 A.VDD 76 **AGCI** RF-AGC amplifier input pin ΑI 1/2 A.VDD 77 RFO RF summing amplifier output pin ΑO Undefined 78 EQ2 RF amplifier equalizer parts connection pin 79 EQ1 RF-RF summing amplifier inverse input pin 80 ΑI 81 A.GND Analog circuit GND 82 Α Photo-detector A input pin ΑI 1/2 A.VDD С 1/2 A.VDD 83 Photo-detector C input pin ΑI 84 В Photo-detector B input pin ΑI 1/2 A.VDD 85 D Photo-detector D input pin ΑI 1/2 A.VDD F 1/2 A.VDD 86 Photo-detector F input pin ΑI Ε 87 Photo-detector E input pin ΑI 1/2 A.VDD 88 A.V<sub>DD</sub> Positive power supply pin to analog circuit 89 REFOUT AO 1/2 A.VDD Reference potential output pin FE-90 Focus error amplifier inverse input pin ΑI 1/2 A.VDD

MANA DataSheet411

| Pin No.      | Pin Name          | Description                                                                                                                                                 | I/O | Initial Value       |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|

| 91           | FEO               | Focus error amplifier output pin                                                                                                                            | AO  | ½ A.V <sub>DD</sub> |

| 92           | TE-               | Tracking error amplifier inverse input pin                                                                                                                  | Al  | ½ A.V <sub>DD</sub> |

| 93           | TEO               | Tracking error amplifier output pin                                                                                                                         | AO  | ½ A.V <sub>DD</sub> |

| 94           | TE2               | Pin from which tracking error is output after amplification                                                                                                 | AO  | ½ A.VDD             |

| 95           | TEC               | Tracking comparator input pin Inputs a tracking error signal whose DC component is cut. A tracking zero-cross is detected inside the LSI using this signal. | AI  | -                   |

| 96           | A.GND             | Analog circuit GND                                                                                                                                          | -   | -                   |

| 97           | PD                | PD detection signal input pin for LD output monitor                                                                                                         | Al  | GND                 |

| 98<br>4U com | LD                | LD control current output pin                                                                                                                               | AO  | Undefined           |

| 99           | PN                | APC circuit control polarity setting pin                                                                                                                    | I   | -                   |

| 100          | A.V <sub>DD</sub> | Positive power supply pin to analog circuit                                                                                                                 | _   | -                   |

Cautions 1. Do not allow any input pin to exceed the power supply voltage.

2. Make each power supply voltage (D.VDD, A.VDD, X.VDD, DA.VDD) the same potential.

**Remark** The meanings of symbols in the I/O column are as follows.

I: Logic level input pin

O: Logic level output pin

AI: Analog input pin

AO: Analog output pin

A-: Analog parts connection pin

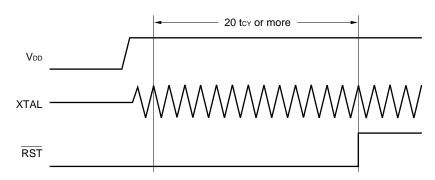

#### Reset input

In the  $\mu$ PD63711, when the reset signal (active low) is input from the  $\overline{RST}$  pin (pin 3) while the clock is being input from the XTAL pin (pin 23), it takes up to 20 clocks (about 1.2  $\mu$ s) before the statuses of all the pins are defined. To allow for this, therefore, be sure to input the reset signal for a sufficient amount of time.

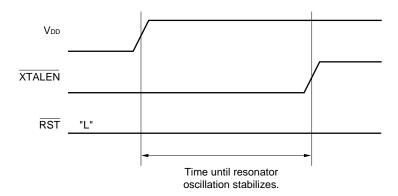

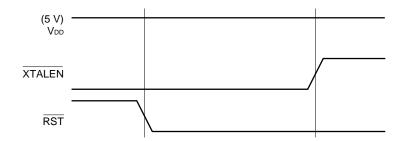

# Cautions on using the XTALEN pin

When stopping oscillation using the XTALEN pin, note the following.

1. When stopping oscillation immediately after the power supply is turned on.

ww.DataSheet4U.com

The clock must be supplied while the reset signal is active, as in the above chart, even when stopping oscillation immediately after turning on the power supply.

2. When stopping oscillation in the normal use state

Be sure to set the reset signal to active before stopping oscillation.

If oscillation is stopped without setting the reset signal to active, output of the servo drive or sound will stop or become unstable, which may cause bugs in external devices.

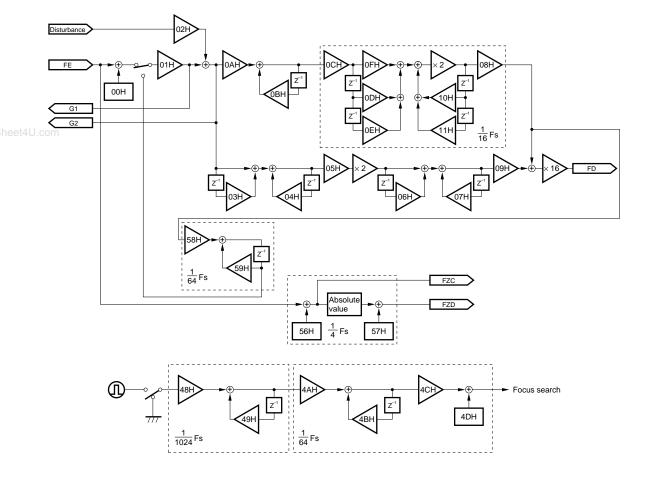

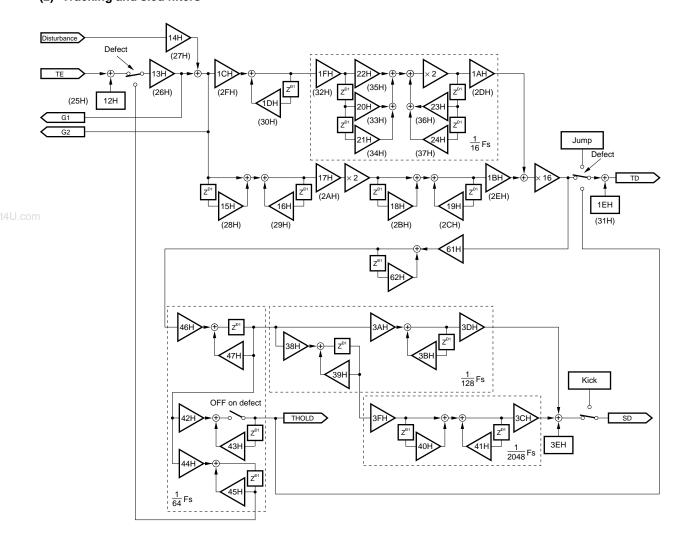

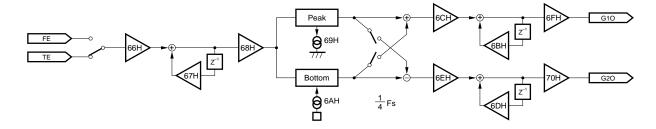

# 2. DIGITAL FILTER FLOWCHARTS

Flowcharts of the digital filters are shown below. Fs = 176.4 kHz.

# (1) Focus filter

# (2) Tracking and sled filters

**Remark** Bank 1 addresses are shown in parentheses.

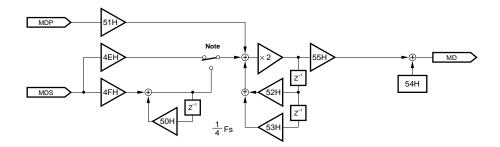

## (3) Spindle system

Note This switch is controlled according to the CLV lock decision signal (same signal as FR bit in status signal).

Asynchronous state:  $FR = 0 \rightarrow Switch$  is down Synchronous state:  $FR = 1 \rightarrow Switch$  is up

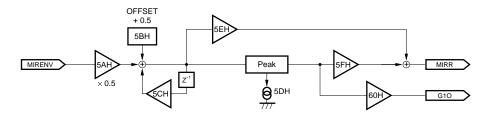

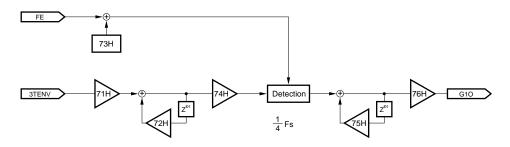

# (4) MIRR signal

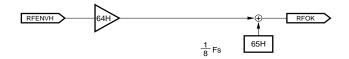

## (5) RFOK signal

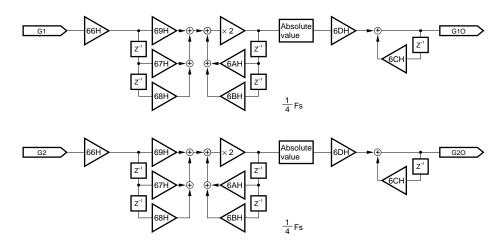

## (6) Gain detection filter

# (7) Balance adjustment filter

# (8) 3T detection filter

## 3. MICROCONTROLLER INTERFACE COMMANDS

# 3.1 Servo System Commands

Table 3-1. Servo System Command Functions

| Command | Function                                           | Reference |

|---------|----------------------------------------------------|-----------|

| 00H     | Writing data to CRAM                               | -         |

| 01H     | CRAM address setting                               | _         |

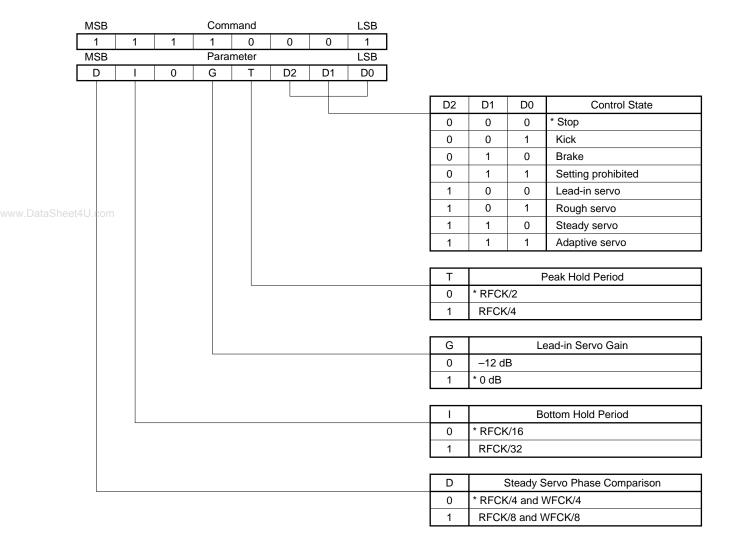

| 10H     | Servo control 0                                    | p.18      |

| 11H     | Servo control 1                                    | p.20      |

| 12H     | Servo control 2                                    | p.22      |

| 13H     | Focus search setting                               | p.23      |

| 14H     | Disturbance generation and SO data output settings | p.24      |

| 15H     | Half-wave brake control                            | p.26      |

| 17H     | Disturbance frequency and level settings           | p.27      |

| 18H     | Defect comparator level setting                    | p.28      |

| 22H     | Track jump kick time setting,                      | p.29      |

| 23H     | traverse counter setting                           |           |

| 24H     |                                                    |           |

Table 3-2. List of Servo System Commands (1/2)

| Command        |                      |                                          |           | Paramet     | er (Data)   |           |       |      |  |  |  |  |  |

|----------------|----------------------|------------------------------------------|-----------|-------------|-------------|-----------|-------|------|--|--|--|--|--|

| (Command Code) | MSB                  | 6                                        | 5         | 4           | 3           | 2         | 1     | LSB  |  |  |  |  |  |

| 00H            | Writing data to CRAM |                                          |           |             |             |           |       |      |  |  |  |  |  |

| 01H            |                      | CRAM address                             |           |             |             |           |       |      |  |  |  |  |  |

| 10H            | SK                   | TM                                       | TEH       | FR          | TK          | ТВ        | T-CNT | BRK  |  |  |  |  |  |

| 11H            | FON                  | TON                                      | SON       | MON         | FST         | DFCT      | JSK   | TAB  |  |  |  |  |  |

| 12H            | BALON                | SDMSK                                    | SDL1      | SDL0        | DFCTT       | SCV       | 0     | TFP  |  |  |  |  |  |

| 13H            | 0                    | 0                                        | 0         | 0           | 0           | 0         | T1    | T0   |  |  |  |  |  |

| 14H            | GST                  | GON                                      | GFT       | T/3         | G/B         | SEL2      | SEL1  | SEL0 |  |  |  |  |  |

| 15H            | BALSW                | 0                                        | 0         | 0           | BKLMT       | 0         | 0     | 0    |  |  |  |  |  |

| 17H            | FD2                  | FD1                                      | FD0       | FRQ4        | FRQ3        | FRQ2      | FRQ1  | FRQ0 |  |  |  |  |  |

| 18H            | DF7                  | DF6                                      | DF5       | DF4         | DF3         | DF2       | DF1   | DF0  |  |  |  |  |  |

| 22H            | 0                    |                                          |           | TRA         | CK KICK TIM | 1E A      |       |      |  |  |  |  |  |

| 23H            | 0                    | TRACK KICK TIME B/TRAVERSE COUNTER N (H) |           |             |             |           |       |      |  |  |  |  |  |

| 24H            |                      | Т                                        | RAVERSE C | OUNTER N (L | _)/TRACK JU | MP COUNTE | R     |      |  |  |  |  |  |

www.DataSheet4II.com

Table 3-2. List of Servo System Commands (2/2)

| CRAM Address | CRAM Data                                                                           |

|--------------|-------------------------------------------------------------------------------------|

| 77H          | TRACK KICK LEVEL A (kick level)                                                     |

| 78H          | TRACK KICK LEVEL B (brake level)                                                    |

| 79H          | SLED KICK LEVEL                                                                     |

| 7AH          | Sled dead zone level setting (–)                                                    |

| 7BH          | Sled dead zone level setting (+)                                                    |

| 7CH          | DAC level setting for adjustment (DAC1 pin output) (On-chip RF FE amplifier offset) |

| 7DH          | DAC level setting for adjustment (DAC2 pin output)                                  |

| 7EH          | DAC level setting for adjustment (DAC3 pin output) (On-chip RF TE amplifier offset) |

| 7FH          | DAC level setting for adjustment (DAC0 output)                                      |

Caution Do not send an undefined command.

..... DetaCha

# (1) 10H command (Servo control 0)

| MSB        |      |      | Com | mand  |    |     |     | LSB |       |                                                      |

|------------|------|------|-----|-------|----|-----|-----|-----|-------|------------------------------------------------------|

| 0          | 0    | 0    | 1   | 0     | 0  | C   | )   | 0   |       |                                                      |

| MSB        | T. 4 | TELL |     | meter | TD | T-0 | NIT | LSB |       |                                                      |

| SK         | TM   | TEH  | FR  | TK    | ТВ | T.C | ΝI  | BRK |       |                                                      |

|            |      |      |     |       |    |     |     |     | BRK   | Half-Wave Brake Circuit                              |

|            |      |      |     |       |    |     |     |     | 0     | _                                                    |

|            |      |      |     |       |    |     |     |     | 1     | ON                                                   |

|            |      |      |     |       |    |     |     |     |       |                                                      |

|            |      |      |     |       |    |     |     |     | T-CNT | Function of TK Bit                                   |

|            |      |      |     |       |    |     |     |     | 0     | Start of track jump sequencer                        |

| heet4U.com |      |      |     |       |    |     |     |     | 1     | Load value in traverse counter                       |

|            |      |      |     |       |    |     |     |     | ТВ    | Tracking Filter Coefficient Bank                     |

|            |      |      |     |       |    |     |     |     | 0     | Bank 0                                               |

|            |      |      |     |       |    |     |     |     | 1     | Bank 1                                               |

|            |      |      |     |       |    |     |     |     |       |                                                      |

|            |      |      |     |       |    |     |     |     | TK    | Track Jump/Load Trigger                              |

|            |      |      |     |       |    |     |     |     | 0     | -                                                    |

|            |      |      |     |       |    |     |     |     | 1     | Execute operation specified by T-CNT b               |

|            |      |      |     |       |    |     |     |     | FR    | Output Polarity Switching                            |

|            |      |      |     |       |    |     |     |     | 0     | Output level × -1                                    |

|            |      |      |     |       |    |     |     |     | 1     | Leave output level unchanged                         |

|            |      |      |     |       |    |     |     |     |       | 3                                                    |

|            |      |      |     |       |    |     |     |     | TEH   | Error Hold Function on Track Jum                     |

|            |      | •    |     |       |    |     |     |     | 0     | Hold reference (data 00)                             |

|            |      |      |     |       |    |     |     |     | 1     | Hold previous value                                  |

|            |      |      |     |       |    |     |     |     | TM    | Tracking Mute                                        |

|            |      |      |     |       |    |     |     |     | 0     | Output results of tracking filter (normal operation) |

|            |      |      |     |       |    |     |     |     | 1     | Output value specified by TEH bit                    |

|            |      |      |     |       |    |     |     |     |       |                                                      |

|            |      |      |     |       |    |     |     |     | SK    | Sled Kick                                            |

|            |      |      |     |       |    |     |     |     | 0     |                                                      |

|            |      |      |     |       |    |     |     |     | 1     | Execute sled kick                                    |

## [Functional description]

BRK: Controls the half-wave brake circuit.

"1" Half-wave brake circuit is ON

T-CNT: Used in combination with the TK bit.

"0" If TK = 1 is set, start a track jump sequencer

"1" If TK = 1 is set, load the values of registers 23H and 24H in the traverse counter

TB: Switches the tracking filter coefficient bank.

"0" Tracking filter bank 0

"1" Tracking filter bank 1

TK: This is the track jump trigger and traverse counter load control.

It has two meanings depending on the T.CNT bit. An operation using the TK bit is a one-shot operation

that operates only in the instant this is set to "1".

FR: Controls the output level polarity when tracking and sled kicking.

"0" Output the value in the output level register (CRAM 77H to 79H) multiplied by -1

"1" Output the value in the output level register unchanged

TEH: Controls the error hold function when track jumping.

Selects tracking output when SK = TM = 1.

"0" Hold reference

"1" Hold previous value

TM: Controls tracking mute.

"0" Output the arithmetic result of the tracking filter (normal operation)

"1" Either hold the previous value or hold a reference (data value 00) depending on the TEH bit specification

SK: Controls sled kick.

'1" Perform sled kick using the value set in CRAM 79H

www.DataShee**‡5**U.com

# (2) 11H command (Servo control 1)

| _  | MSB       |     |      | Comr  |     |      |      | LSB |                                            |        |

|----|-----------|-----|------|-------|-----|------|------|-----|--------------------------------------------|--------|

| L  | 0         | 0   | 0    | 1     | 0   | 0    | 0    | 1   |                                            |        |

| г  | MSB       | TON | LOON | Parar |     | DECT | ICIC | LSB |                                            |        |

| L  | FON       | TON | SON  | MON   | FST | DFCT | JSK  | TAB |                                            |        |

|    |           |     |      |       |     |      |      |     | TAB Track Jump Sequencer                   |        |

|    |           |     |      |       |     |      |      |     | 0 -                                        |        |

|    |           |     |      |       |     |      |      |     | 1 Halt operation                           |        |

|    |           |     |      |       |     |      |      |     |                                            |        |

|    |           |     |      |       |     |      |      |     | JSK Sled Kick                              |        |

|    |           |     |      |       |     |      |      |     | 0 _                                        |        |

| Sh | n e e t 4 | ł U |      |       |     |      |      |     | 1 Execute sled kick                        |        |

|    |           |     |      |       |     |      |      |     | DFCT Error Hold Output Upon Defect De      | tectio |

|    |           |     |      |       |     |      |      |     | 0 No                                       |        |

|    |           |     |      |       |     |      |      |     | 1 Yes                                      |        |

|    |           |     |      |       |     |      |      |     |                                            |        |

|    |           |     |      |       |     |      |      |     | FST Focus Search                           |        |

|    |           |     |      |       |     |      |      |     | 0 –                                        |        |

|    |           |     |      |       |     |      |      |     | 1 Start focus search                       |        |

|    |           |     |      |       |     |      |      |     | MON Spindle Servo Output                   |        |

|    |           |     |      |       |     |      |      |     | 0 OFF (D/A output stopped, 1/2 A.Vdd)      |        |

|    |           |     |      |       |     |      |      |     | 1 ON                                       |        |

|    |           |     |      |       |     |      |      |     | SON Sled Servo Output                      |        |

|    |           |     |      |       |     |      |      |     | 0 OFF (D/A output stopped, 1/2 A.VDD)      |        |

|    |           |     |      |       |     |      |      |     | 1 ON                                       |        |

|    |           |     |      |       |     |      |      |     | TON! Trealing Come Output                  |        |

|    |           |     |      |       |     |      |      |     | TON Tracking Servo Output                  |        |

|    |           |     |      |       |     |      |      |     | 0 OFF (D/A output stopped, 1/2 A.Vbb) 1 ON |        |

|    |           |     |      |       |     |      |      |     | 1 ON                                       |        |

|    |           |     |      |       |     |      |      |     | FON Focus Servo Output                     | _      |

|    |           |     |      |       |     |      |      |     | 0 OFF (D/A output stopped, 1/2 A.Vdd)      |        |

|    |           |     |      |       |     |      |      |     | 1 ON                                       |        |

#### [Functional description]

TAB: Controls close of track jump sequencer operation.

"1" Halt track jump sequencer operation

An operation using the TAB bit is a one-shot operation that operates only on the instant this is set to "1".

JSK: Controls sled kick when track jumping.

"1" Perform sled kick in the track jump period using the level set in CRAM 79H

DFCT: Controls error hold output on defect detection.

"0" No hold output

All switches controlled by a DEFECT signal in the focus filter and tracking filter are fixed in the up position (normal position).

"1" Hold output

Switch the above switches according to the DEFECT signal state.

FST: Focus search control.

"1" Start focus search

FON must be "1" at this time.

MON: Controls whether spindle servo output (D/A output) is ON or OFF.

"0" D/A output is OFF, output  $\frac{1}{2}$ A.VDD

"1" D/A output is ON

SON: Controls whether sled servo output (D/A output) is ON or OFF.

"0" D/A output is OFF, output  $\frac{1}{2}$ A.V<sub>DD</sub>

"1" D/A output is ON

TON: Controls whether tracking servo output (D/A output) is ON or OFF.

"0" D/A output is OFF, output  $\frac{1}{2}$ A.VDD

"1" D/A output is ON

FON: Controls whether focus servo output (D/A output) is ON or OFF.

"0" D/A output is OFF, output  $\frac{1}{2}$ A.VDD

"1" D/A output is ON

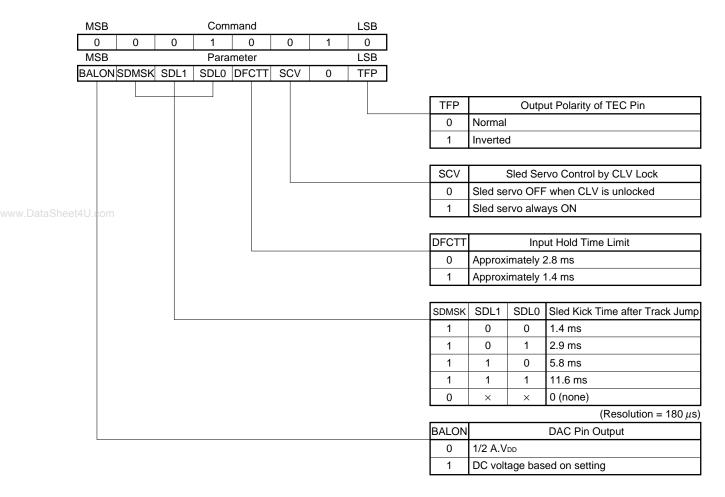

#### (3) 12H command (Servo control 2)

## [Functional description]

TFP: TEC signal (tracking error zero-cross signal) polarity control.

"0" Normal output

"1" Inverted output

SCV: Sled servo control by CLV lock.

"0" Sled servo is OFF (D/A output halted) when CLV is unlocked (when FR bit in status signal

is 0)

"1" Sled servo is always ON regardless of CLV lock

At the time of a sled kick, D/A output is performed regardless of a CLV lock.

DFCTT: Sets the tracking or focus input hold time limit when the absence of an RF signal is detected.

"0" Approximately 2.8 ms

"1" Approximately 1.4 ms

SDMSK, SDL[1:0]: Sets the sled kick time after a track jump.

BALON: Sets DAC0 to DAC3 pin outputs.

This bit is set to "0" on a reset.

"0" Output  $\frac{1}{2}$ A.VDD

"1" Output DC voltage set using CRAM 7FH, 7CH, 7DH, and 7EH from DAC0 to DAC3 pins

respectively

## (4) 13H command (Focus search setting)

| MSB           | MSB Command |   |   |   |   |    |    |  |  |  |  |

|---------------|-------------|---|---|---|---|----|----|--|--|--|--|

| 0             | 0           | 0 | 1 | 0 | 0 | 1  | 1  |  |  |  |  |

| MSB Parameter |             |   |   |   |   |    |    |  |  |  |  |

| 0             | 0           | 0 | 0 | 0 | 0 | T1 | T0 |  |  |  |  |

|               |             |   |   |   |   |    |    |  |  |  |  |

| T1 | T0 | Square Wave Period on Focus Search |

|----|----|------------------------------------|

| 0  | 0  | Approximately 0.37 s               |

| 0  | 1  | Approximately 0.74 s               |

| 1  | 0  | Approximately 1.49 s               |

| 1  | 1  | Approximately 2.97 s               |

# www.DataSheet4U.com[Functional description]

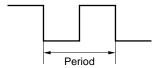

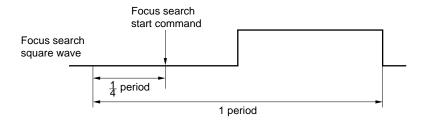

T[1:0]: Sets the period of the square wave for focus search.

As shown below, square wave output on focus search is begun from the time one quarter of the period has gone by.

MSB

## (5) 14H command (Disturbance generation and SO data output setting)

Command

| _ | IVISD |   |    |     | Con  |       |      |      | LOD  |      |         |           |                                        |

|---|-------|---|----|-----|------|-------|------|------|------|------|---------|-----------|----------------------------------------|

| L | 0     |   | 0  | 0   | 1    | 0     | 1    | 0    | 0    |      |         |           |                                        |

|   | MSB   |   |    |     | Para | meter |      |      | LSB  |      |         |           |                                        |

|   | GST   | G | ON | GFT | T/3  | G/B   | SEL2 | SEL1 | SEL0 |      |         |           |                                        |

|   |       |   |    |     |      |       |      |      |      |      | T       |           | T                                      |

|   |       |   |    |     |      |       |      |      |      | SEL2 | SEL1    | SEL0      | +                                      |

|   |       |   |    |     |      |       |      |      |      | 0    | 1       | 0         | FE                                     |

|   |       |   |    |     |      |       |      |      |      | 0    | 1       | 1         | TE                                     |

|   |       |   |    |     |      |       |      |      |      | 1    | 0       | 0         | G1                                     |

|   |       |   |    |     |      |       |      |      |      | 1    | 0       | 1         | G2                                     |

|   |       |   |    |     |      |       |      |      |      |      |         |           |                                        |

|   | U.co  |   |    |     |      |       |      |      |      | T/3  | G/B     | (         | Output Data                            |

|   |       |   |    |     |      |       |      |      |      | 0    | 0       | Gain d    | letection resu                         |

|   |       |   |    |     |      |       |      |      |      | 0    | 1       | adjustr   | f filter for tra<br>ment<br>EAK, TE·BO |

|   |       |   |    |     |      |       |      |      |      | 1    | 0       | <b>!</b>  | plitude dete                           |

|   |       |   |    |     |      |       |      |      |      | 1    | 1       | 3T det    | ection result                          |

|   |       |   |    |     |      |       |      |      |      |      | '       |           |                                        |

|   |       |   |    |     |      |       |      |      |      | GFT  |         |           | ce Feed Desi                           |

|   |       |   |    |     |      |       |      |      |      | 0    | Focus   | equalize  | er (FE signal)                         |

|   |       |   |    |     |      |       |      |      |      | 1    | Trackin | ıg equal  | izer (TE sigr                          |

|   |       |   |    |     |      |       |      |      |      |      |         |           |                                        |

|   |       |   | L  |     |      |       |      |      |      | GON  | Feed o  | of Distur | bance to TE                            |

|   |       |   |    |     |      |       |      |      |      | 0    | Disturb | ance O    | FF                                     |

|   |       |   |    |     |      |       |      |      |      | 1    | Disturb | ance Ol   | N                                      |

|   |       |   |    |     |      |       |      |      |      |      |         |           |                                        |

|   |       |   |    |     |      |       |      |      |      | GST  | Fetch A | rithmetic | Result of Fil                          |

|   |       |   |    |     |      |       |      |      |      | 0    |         |           | _                                      |

|   |       |   |    |     |      |       |      |      |      | 1    | Fetch   |           |                                        |

LSB

## [Functional description]

SEL[2:0]: Sets SO data output.

G/B, T/3: Sets data to latch to G1 and G2 registers inside the LSI.

GFT: Selects the disturbance feed destination.

GON: Controls whether disturbance feed to the TE or FE filters is ON or OFF.

GST: Controls fetching of arithmetic result of filter for gain detection.

"1" Arithmetic result of filter for gain detection (G10, G20) is latched to G1 and G2 registers inside LSI (during which time S0 pin outputs high level and is in BUSY state)

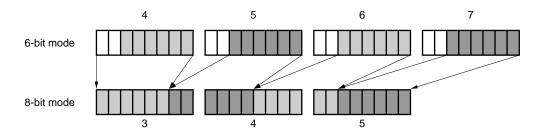

On data readout from the serial interface using the 14H command, the following one-bit shift processing toward the MSB is executed for G1 and G2 data read from the serial interface by means of the settings of T/3 and G/B bits.

From signal flow MSB LSB 15 14 13 12 11 10 8 6 5 0 Double 6 5 4 2 0 3

Figure 3-1. Data Readout Block

The aim of one-bit shift processing toward the MSB is to improve the bit precision of values that are read. For filters such as the gain detection filter, which always output positive values, the sign bit has no meaning. By performing one-bit shift processing toward the MSB on values read from the serial interface in the  $\mu$ PD63711, the precision of a value that is read is improved by one bit from reading the LSB bit instead of the sign bit.

When reading sign output (positive and negative values) as in the case of balance detection, as a procedure for avoiding losing a sign due to one-bit shift processing toward the MSB, multiply (shift one bit to the right) a value less than 0.5 in the final output stage multiplier in advance. By doing so, the correct sign value is read.

## (6) 15H command (Half-wave brake control)

| MSB      |   |   | Com  | nmand |   |   | LSB | _ |       |                                                      |

|----------|---|---|------|-------|---|---|-----|---|-------|------------------------------------------------------|

| 0        | 0 | 0 | 1    | 0     | 1 | 0 | 1   |   |       |                                                      |

| MSB      |   |   | Para | meter |   |   | LSB |   |       |                                                      |

| BALSW    | 0 | 0 | 0    | BKLMT | 0 | 0 | 0   |   |       |                                                      |

|          |   |   |      |       |   |   |     |   |       |                                                      |

|          |   |   |      |       |   |   |     |   | BKLMT | Half-Wave Brake Control                              |

|          |   |   |      |       |   |   |     |   | 0     | -                                                    |

|          |   |   |      |       |   |   |     |   | 1     | Half-wave brake OFF at or above approximately 1.4 ms |

|          |   |   |      |       |   |   |     | ' |       |                                                      |

|          |   |   |      |       |   |   |     |   | BALSW | TBAL or FBAL Detection Filter Internal SW            |

| et4U.com |   |   |      |       |   |   |     |   | 0     | OFF                                                  |

|          |   |   |      |       |   |   |     |   | 1     | ON                                                   |

## [Functional description]

BKLMT: Controls half-wave brake circuit

"1" Half-wave brake is OFF at or above approximately 1.4 ms

BALSW: Controls addition/subtraction switch inside tracking or focus balance detection filter.

"0" OFF

"1" ON

## (7) 17H command (Disturbance frequency and level setting)

| MSB |     |     | Com   | mand  |      |      | LSB  | _ |          |                               |

|-----|-----|-----|-------|-------|------|------|------|---|----------|-------------------------------|

| 0   | 0   | 0   | 1     | 0     | 1    | 1    | 1    |   |          |                               |

| MSB |     |     | Parar | meter |      |      | LSB  |   |          |                               |

| FD2 | FD1 | FD0 | FRQ4  | FRQ3  | FRQ2 | FRQ1 | FRQ0 |   |          |                               |

|     |     |     |       |       |      |      |      |   |          |                               |

|     |     |     |       |       |      |      |      |   | FRQ[4:0] | Disturbance Frequency Setting |

|     |     |     |       |       |      |      |      |   |          |                               |

|     |     |     |       |       |      |      |      |   | FD[2:0]  | Disturbance Level Setting     |

## [Functional description]

FRQ[4:0]: Sets the disturbance frequency (5-bit absolute value).

FD[2:0]: Sets the disturbance level (3-bit absolute value).

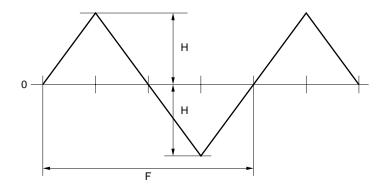

The disturbance frequency and disturbance level are calculated using the following expressions.

Frequency (F) =

$$\frac{fs}{(FQ + 1) \times 4}$$

Level  $(H) = FD \times (FQ + 1)$

fs:  $\frac{176.4 \text{ kHz}}{2} = 88.2 \text{ kHz}$

FQ: Value set in FRQ[4:0]

FD: Value set in FD[2:0]

#### Caution Set FD to the greatest value that satisfies $H \le 127$ .

**Example** When 17H register = B5H

$B5H = 10110101B \rightarrow FD = 101B, FQ = 10101B$

Since FQ = 21,  $F = \frac{88.2 \text{ kHz}}{(21 + 1) \times 4} = 1.0 \text{ kHz}$

Since FD = 5, H =  $5 \times (21 + 1) = 110 = 6EH$

17H register = D5H is not possible because FD = 6, H =  $6 \times (21+1) = 132$ , and H then exceeds 127.

#### (8) 18H command (Defect comparator level setting)

| MSB |     |     | Com  | mand  |     |     | LSE |

|-----|-----|-----|------|-------|-----|-----|-----|

| 0   | 0   | 0   | 1    | 1     | 0   | 0   | 0   |

| MSB |     |     | Para | meter |     |     | LSB |

| DF7 | DF6 | DF5 | DF4  | DF3   | DF2 | DF1 | DF0 |

|     |     |     |      |       |     |     |     |

|     |     |     |      |       |     |     |     |

|     |     |     |      |       |     |     |     |

# [Functional description]

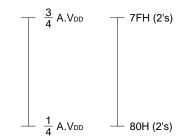

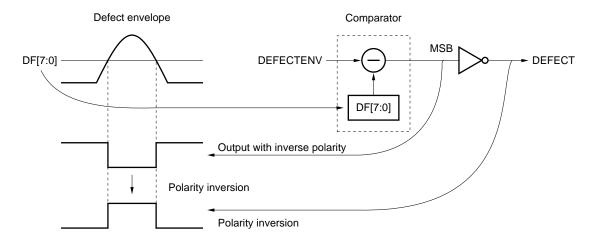

DF[7:0]: Set the defect signal comparator level.

The range of  $\frac{1}{2}$ A.V<sub>DD</sub>  $\pm \frac{1}{4}$ A.V<sub>DD</sub> can be set in 256 8-bit levels.

The setting value becomes the comparison threshold value.

The comparison result has the inverse polarity of the input (because the MSB after subtracting is used).

Output is inverted (because the signal after comparator output handled as a signal absence detection by DEFECT = H).

The relationship between comparator level setting values and defect envelope signal voltages is shown below.

#### (9) 22H, 23H, and 24H commands (Track jump control)

| _ | MSB |    |    | Comi  | mand  |    |    | LSB |

|---|-----|----|----|-------|-------|----|----|-----|

|   | 0   | 0  | 1  | 0     | 0     | 0  | 1  | 0   |

|   | MSB |    |    | Parar | meter |    |    | LSB |

|   | 0   | D6 | D5 | D4    | D3    | D2 | D1 | D0  |

|   |     |    |    |       |       |    |    |     |

|   |     |    |    |       |       |    |    |     |

D[6:0] Track Kick Time A

| MSB |    |    | Com   | mand  |    |    | LSB |

|-----|----|----|-------|-------|----|----|-----|

| 0   | 0  | 1  | 0     | 0     | 0  | 1  | 1   |

| MSB |    |    | Parai | meter |    |    | LSB |

| 0   | D6 | D5 | D4    | D3    | D2 | D1 | D0  |

|     |    |    |       |       |    |    |     |

D[6:0] Track Kick Time B/Traverse Counter N (H)

D[7:0] Traverse Counter N (L)/ Track Jump Counter

#### [Functional description]

#### Track jump

22H: The kick time setting

7 bits wide. Always set the MSB to 0.

The kick time is calculated using the following expression.

Kick time =

$$\frac{\text{(Setting value + 1)} \times 1}{\text{fs}} \text{ (fs = } \frac{176.4 \text{ kHz}}{2} = 88.2 \text{ kHz)}$$

23H: Brake time setting

7 bits wide. Always set the MSB to 0.

The brake time is calculated using the following expression.

Brake time =

$$\frac{\text{(Setting value + 1)} \times 1}{\text{fs}} \text{ (fs = } \frac{176.4 \text{ kHz}}{2} = 88.2 \text{ kHz)}$$

24H: Track counter setting

7 bits wide. Always set the MSB to 0.

The value set in 24H is used as a counter value.

#### Traverse count

23H: Traverse counter setting (higher 7 bits, always set MSB to 0)

24H: Traverse counter setting (lower 8 bits)

The values set in 23H and 24H (15 bits wide) are used as counter values.

23H and 24H are used both when track jumping and when counting traverses, and are switched according to the setting of the T-CNT bit of the 10H command.

# 3.2 RF System Commands

Table 3-3. Functions of RF System Commands

| Command | Function                                                                                                            | Reference |

|---------|---------------------------------------------------------------------------------------------------------------------|-----------|

| 30H     | AGC amplifier gain setting, RF amplifier offset setting                                                             | p.31      |

| 31H     | 3T component detection gain setting,<br>3T detection circuit LPF setting,<br>TE amplifier gain setting              | p.32      |

| 32H     | FE, RF, and TE amplifier gain settings                                                                              | p.33      |

| 33H     | TE amplifier balance setting                                                                                        | p.34      |

| 34H     | MIRR detection block peak and bottom time constant settings, TE2 signal gain setting                                | p.35      |

| 35H     | 3T component extraction from RF signal timing setting                                                               | p.37      |

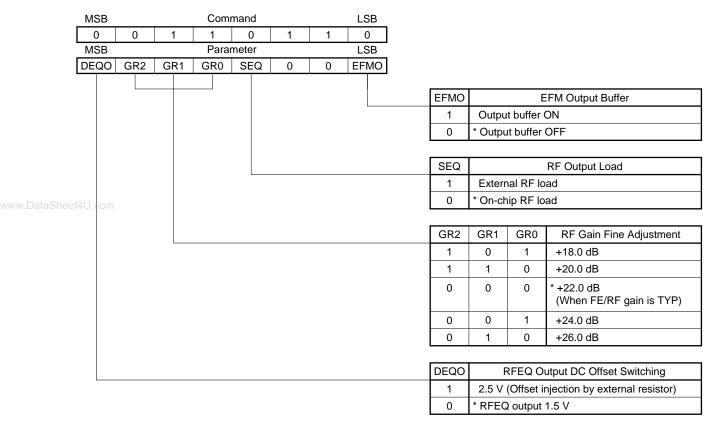

| 36H     | EFM output block buffer setting, RF amplifier external load resistor setting                                        | p.38      |

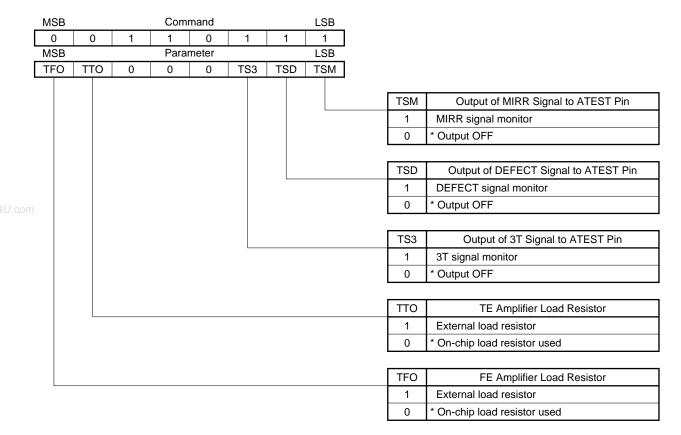

| 37H     | Setting of output to ATEST pin, FE and TE amplifier load resistors setting                                          | p.39      |

| 39H     | Playback speed setting, EQ speed selection (x1 or x2), APC amplifier polarity selection, Current input type setting | p.40      |

Table 3-4. List of RF System Commands

| Command        |      |      |      | Paramet | er (Data) |      |      |      |

|----------------|------|------|------|---------|-----------|------|------|------|

| (Command Code) | MSB  | 6    | 5    | 4       | 3         | 2    | 1    | LSB  |

| 30H            | DRF3 | DRF2 | DRF1 | DRF0    | GA3       | GA2  | GA1  | GA0  |

| 31H            | GTU1 | GTU0 | F31  | F30     | GF5       | G32  | G31  | G30  |

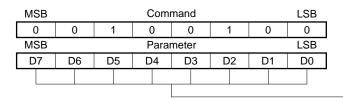

| 32H            | GT2  | GT1  | GT0  | GF4     | GF3       | GF2  | GF1  | GF0  |

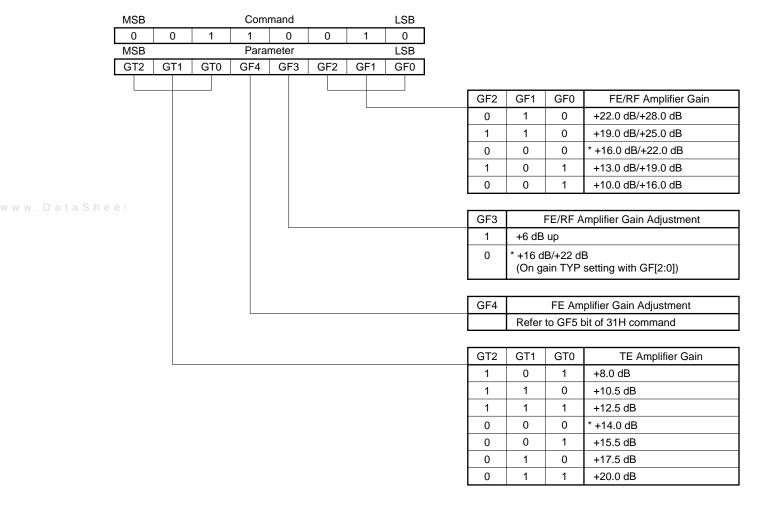

| 33H            | TB6  | TB5  | TB4  | TB3     | TB2       | TB1  | TB0  | IVS2 |

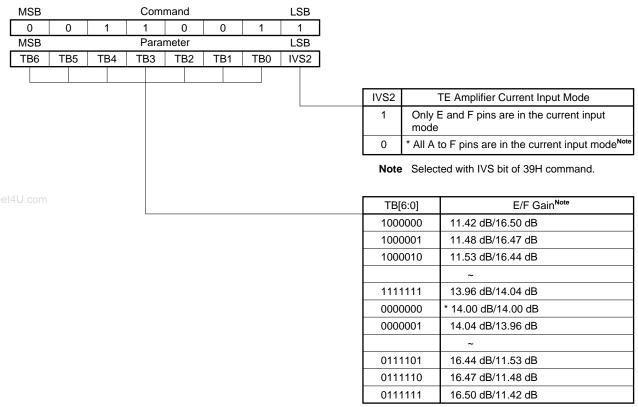

| 34H            | TM3  | TM2  | TM1  | GTEC    | SOST      | TM5  | TM4  | TMC  |

| 35H            | 0    | 3TS6 | 3TS5 | 3TS4    | 3TS3      | 3TS2 | 3TS1 | 3TS0 |

| 36H            | DEQO | GR2  | GR1  | GR0     | SEQ       | 0    | 0    | EFMO |

| 37H            | TFO  | TTO  | 0    | 0       | 0         | TS3  | TSD  | TSM  |

| 39H            | LDS  | 0    | IVS  | SW2     | APN       | 0    | 0    | CV2  |

Caution Do not send an undefined command.

www.DataSheet4U.com

## (1) 30H command (Settings of AGC amplifier gain and RF amplifier offset)

| _ | MSB  |      |          | Com  | mand  |     |         | LSB |

|---|------|------|----------|------|-------|-----|---------|-----|

|   | 0    | 0    | 1        | 1    | 0     | 0   | 0       | 0   |

| - | MSB  |      |          |      | meter |     |         | LSB |

| L | DRF3 | DRF2 | DRF1     | DRF0 | GA3   | GA2 | GA1     | GA0 |

|   |      |      | $\vdash$ |      |       |     | $\perp$ |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

|   |      |      |          |      |       |     |         |     |

**Note** Values shown here are standard values, not rated values.

0.75 V

Remark The mark \* indicates the contents set after a reset.

## [Functional description]

GA[3:0]: Used in setting the AGC amplifier gain.

Perform gain setting while monitoring the MIRR signal's (peak) - (bottom) signal. The 37H command can be used to output the value of a MIRR signal from the ATEST pin before A/D conversion. In addition, in order to monitor amplitude stably, make adjustments by using the 34H command to maximize the time constant.

DRF[3:0]: Used in setting the RF amplifier output DC voltage.

Can be cancelled using DEQO in the 36H command.

## (2) 31H command (Settings of 3T component detection gain, 3T detection circuit LPF, and TE amplifier gain)

|       | MSB    |      |     | Com  | mand  |     |     |   | LSB |   |      |      |          |                                       |

|-------|--------|------|-----|------|-------|-----|-----|---|-----|---|------|------|----------|---------------------------------------|

|       | 0      | 0    | 1   | 1    | 0     | 0   | 0   |   | 1   | 1 |      |      |          |                                       |

|       | MSB    |      |     | Para | meter |     |     |   | LSB | • |      |      |          |                                       |

|       | GTU1   | GTU0 | F31 | F30  | GF5   | G32 | G3° | 1 | G30 | ] |      |      |          |                                       |

|       |        |      |     |      |       |     |     |   |     |   |      |      |          |                                       |

|       |        |      |     |      |       |     |     |   |     |   | G32  | G31  | G30      | 3T Detection Circuit Gai              |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 0    | 1        | +8.0 dB                               |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 1    | 0        | +14.0 dB                              |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 1    | 1        | +16.5 dB                              |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 0    | 0        | * +20.0 dB                            |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 0    | 1        | +23.5 dB                              |

| Sheet | 4U.com |      |     |      |       |     |     |   |     |   | 0    | 1    | 0        | +26.0 dB                              |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 1    | 1        | +28.0 dB                              |

|       |        |      |     |      |       |     |     |   |     |   |      |      |          |                                       |

|       |        |      |     |      |       |     |     |   |     |   | GF5  | GF4  | FI       | E Amplifier Gain Adjustment           |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 1    | +2.5 d   | В                                     |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 0    | -2.0 d   | В                                     |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 1    | +6.0 d   | IB                                    |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 0    | * 0 dB   |                                       |

|       |        |      |     |      |       |     |     |   |     |   |      |      |          |                                       |

|       |        |      |     |      |       |     |     |   |     |   | F31  | F30  |          | 3T Circuit LPF after S/H              |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 0    | fc = 50  | ) kHz                                 |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 0    | * fc = 1 | 00 kHz                                |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 1    | fc = 20  | 00 kHz                                |

|       |        |      |     |      |       |     |     |   |     |   |      | I    |          |                                       |

|       |        |      |     |      |       |     |     |   |     |   | GTU1 | GTU0 | TE       | Amplifier Gain Adjustment             |

|       | 1      |      |     |      |       |     |     |   |     |   | 0    | 0    | * +14 d  | B<br>ain TYP setting of 32H           |

|       |        |      |     |      |       |     |     |   |     |   | 0    | 1    | +6 dB    | · · · · · · · · · · · · · · · · · · · |

|       |        |      |     |      |       |     |     |   |     |   | 1    | 0    | +12 dl   |                                       |