**FEATURES**

**500MSPS Encode Rate**

MIL-STD-883 Available

**APPLICATIONS**

Bipolar Input Range (±1V)

Radar Warning Receivers

**Transient Recorders**

"Smart" Munitions

Digital Oscilloscope

Electronic Countermeasures

Very Low Input Capacitance: 8pF

**Demultiplexed Outputs (AD9016)**

MIL-STD-883-Compliant Versions Available

30dB SNR @ 200MHz Analog Input

# High Speed 6-Bit A/D Converters

## AD9006/AD9016

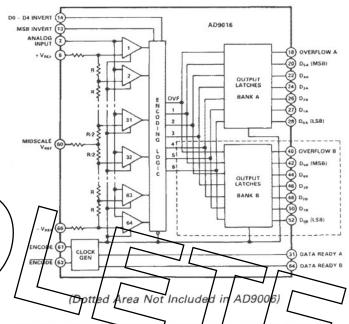

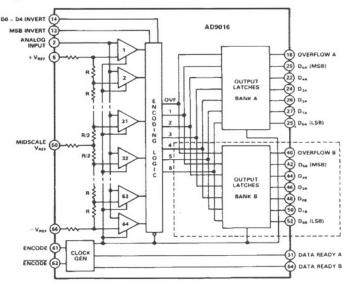

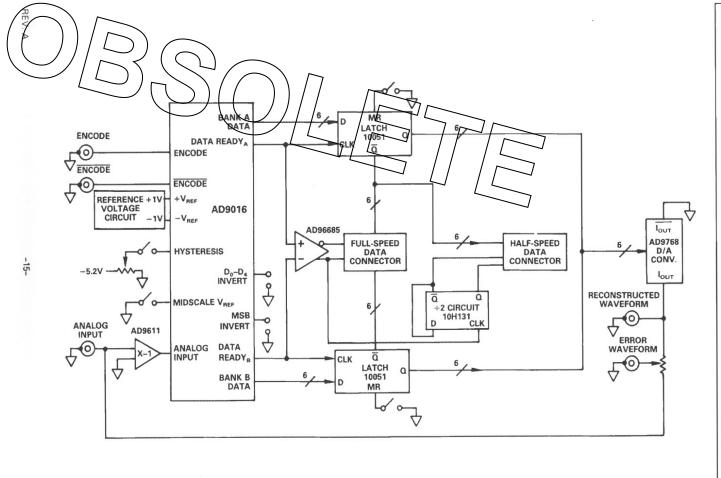

### FUNCTIONAL BLOCK DIAGRAM

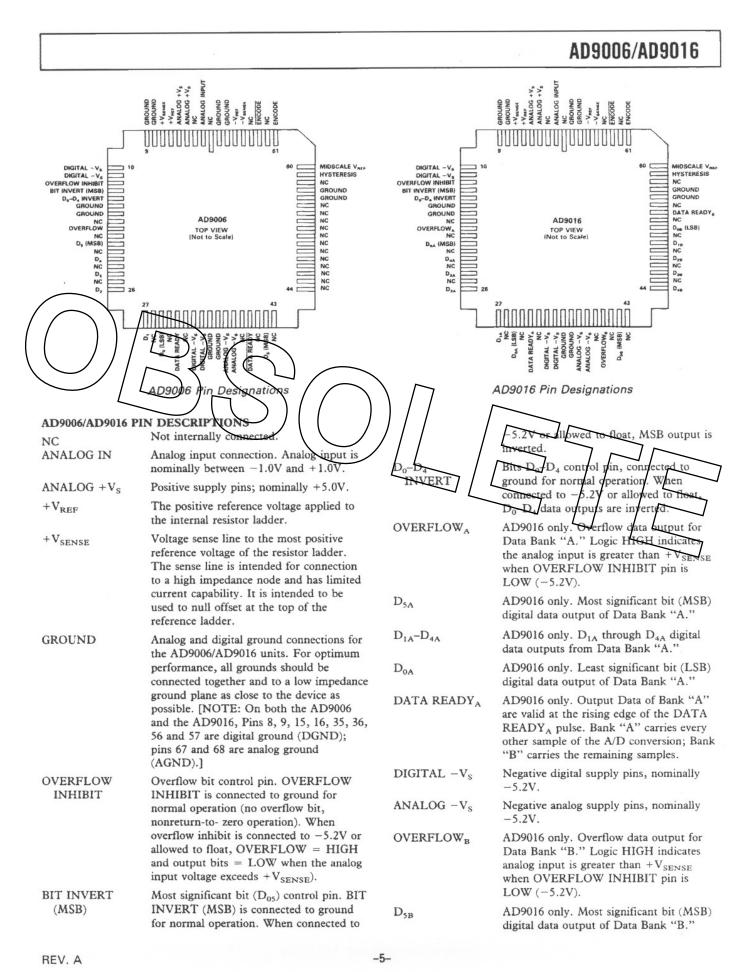

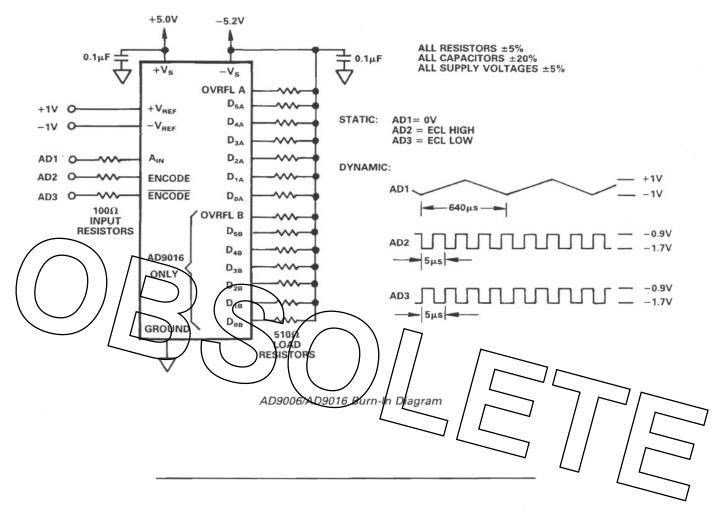

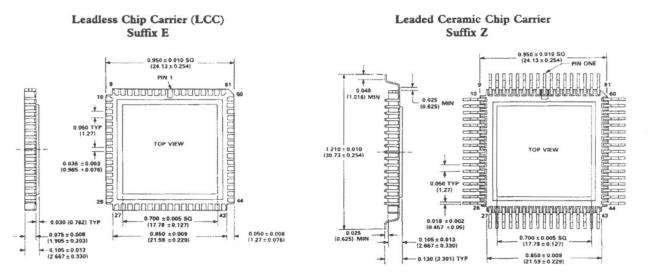

The AD9006 and AD9016 are available as commercial temperature range devices: 0 to  $+70^{\circ}$ C; and military temperature range devices:  $-55^{\circ}$ C to  $+125^{\circ}$ C. Both versions are offered in a ceramic 68-pin LCC, and a ceramic 68-pin leaded package

The AD9006/AD9016 are available in versions compliant with MIL-STD-883. Refer to the *Analog Devices Military Products Databook* or current AD9006/AD9016/883B data sheet for detailed specifications

### GENERAL DESCRIPTION

The AD9006 and AD9016 are 6-bit, ultrahigh seed analog-todigital converters. Both are fabricated in an advanced bipolar process, assuring exceptionally wide analog input bandwidth, and encode rates up to 500MSPS. Functionally, the AD9006 and AD9016 use "flash" architecture; the outputs of 64 parallel comparator stages are decoded to drive a bank of ECL output latches.

The AD9006 features a bipolar analog input range  $(\pm 1V)$ . Output data is provided in a single 6-bit data bank; the data is ECL compatible and also includes complementary Data Ready signals and an overflow bit. ECL-level control pins allow the user to invert the MSB and/or LSBs. The AD9006 exhibits excellent SNR performance (30dB SNR @ 200MHz input), and requires less than two watts of power.

In the AD9016, the performance and features of the AD9006 are combined with on-board demultiplexing circuits. Output data of the AD9016 are demultiplexed to two 6-bit data banks, each of which includes a Data Ready signal and overflow bit.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

617/329-4700

Fax:

617/326-8703

Telex:

924491

Cable:

ANALOG NORWOODMASS

# AD9006-AD9016-SPECIFICATIONS

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $+V_s$ to Ground                             |

|----------------------------------------------|

| AGND to DGND                                 |

| $-V_s$ to Ground                             |

| ANALOG IN, $+V_{REF}-V_{REF}1.5V$ to $+1.5V$ |

| MIDSCALE V <sub>REF</sub> <sup>2</sup>       |

| $+V_{REF}$ to $-V_{REF}$                     |

| MIDSCALE V <sub>REF</sub> Current±4mA        |

| Digital Input Voltages                       |

| ENCODE to ENCODE 4V                          |

| Digital Output Current                            |

|---------------------------------------------------|

| Operating Temperature Range                       |

| AD9006/AD9016KE/KZ0 to +70°C                      |

| AD9006/AD9016TE/TZ/883 55°C to +125°C             |

| Maximum Junction Temperature <sup>3</sup> + 175°C |

| Lead Soldering Temperature (10sec) +300°C         |

| Storage Temperature Range65°C to +150°C           |

|                                                   |

# **ELECTRICAL CHARACTERISTICS** $(+V_s = +5.0V; -V_s = -5.2V; +V_{REF} = +1V; -V_{REF} = -1V, unless otherwise noted)$

|                                                         |          |                   | AD9006/AD9016KE<br>AD9006/AD9016KZ |            |      |           |  |

|---------------------------------------------------------|----------|-------------------|------------------------------------|------------|------|-----------|--|

|                                                         |          | Test              | Min                                | 77         | Marr | Units     |  |

| Parameter (Gonditions)                                  | Temp     | Level             | Min                                | Тур        | Max  |           |  |

| RESOLUTION                                              |          |                   | 6                                  |            |      | Bits      |  |

| DC ACCURACY                                             | $\frown$ |                   |                                    |            |      |           |  |

| Differential Nonlinearity                               | +25°C    | I                 |                                    | 0.2        | 0.25 | LSB       |  |

|                                                         |          | VI                |                                    | 0.25       | 0.5  | LSB       |  |

| Integral Nonlinearity                                   | +25%     | $\langle \rangle$ | $\square$                          | 0.2        | 0.25 | LSB       |  |

|                                                         | Rull     | VI                | 1 /                                | 0.25       | 0.5  | LSB       |  |

| No Missing Codes                                        | Ful      | vi /              |                                    | GUARANTEEI | D    |           |  |

| INITIAL OFFSET ERROR                                    |          |                   | 1                                  |            |      |           |  |

| Top of Reference Ladder                                 | +25°C    |                   |                                    | 15         | 20   | T mV      |  |

| • <b>· p</b> • <b>· · · · · · · · · ·</b>               | Full     | VI                | L /                                |            | 20   | mV        |  |

| Bottom of Reference Ladder                              | +25°C    | I                 |                                    | 14         | 20   | nV        |  |

|                                                         | Full     | VI                |                                    | <u> </u>   | 20   | mV.       |  |

| Offset Drift Coefficient                                | Full     | V                 |                                    | 20         |      | HV/°C     |  |

| ANALOG INPUT                                            |          |                   |                                    |            |      | -         |  |

| Input Voltage Range                                     | Full     | v                 |                                    | ±1         |      |           |  |

| Input Bias Current <sup>4</sup>                         | +25°C    | T                 |                                    | 60         | 100  |           |  |

| mpat bias current                                       | Full     | VI                |                                    | 00         | 130  | μΑ        |  |

| Input Resistance                                        | +25°C    | III               | 25                                 | 70         | 150  | kΩ        |  |

| Input Capacitance                                       | +25°C    | III               | 20                                 | 8          | 10   | pF        |  |

| Analog Bandwidth <sup>5</sup>                           | +25°C    | V                 |                                    | 550        | 10   | MHz       |  |

|                                                         |          |                   |                                    | 220        |      |           |  |

| REFERENCE INPUT                                         | 1 2590   |                   | 1                                  | 00         | 110  |           |  |

| Reference Ladder Resistance                             | +25°C    | I                 | 64                                 | 80         | 110  | Ω         |  |

|                                                         | Full     | VI                | 50                                 | 0.24       | 135  | Ω<br>Ω/°C |  |

| Ladder Temperature Coefficient                          | Full     | V<br>V            |                                    | 30         |      |           |  |

| Reference Input Bandwidth                               | Full     | V                 |                                    | 30         |      | MHz       |  |

| DYNAMIC PERFORMANCE <sup>6</sup>                        |          |                   |                                    |            |      |           |  |

| Conversion Rate                                         | +25°C    | I                 | 470                                | 500        |      | MSPS      |  |

| Aperture Delay $(t_A)$                                  | +25°C    | V                 |                                    | 1.2        |      | ns        |  |

| Aperture Uncertainty (Jitter)                           | +25°C    | V                 |                                    | 3          |      | ps        |  |

| Output Delay $(t_{OD})^7$                               | +25°C    | I                 | 2.7                                | 3.6        | 4.4  | ns        |  |

| Output Rise Time                                        | + 25°C   | I                 |                                    | 1.3        | 1.5  | ns        |  |

| Output Fall Time                                        | +25°C    | I                 |                                    | 1.3        | 1.5  | ns        |  |

| Output Time Skew <sup>8</sup>                           | +25°C    | I                 |                                    | 0.45       | 0.7  | ns        |  |

| Data Ready Output Delay (t <sub>DR</sub> ) <sup>9</sup> |          | -                 |                                    |            |      |           |  |

| AD9006                                                  | +25°C    | I                 | 2.7                                | 3.2        | 4.4  | ns        |  |

| AD9016                                                  | +25°C    | I                 | 3                                  | 3.6        | 4.7  | ns        |  |

| Transient Response <sup>10</sup>                        | +25°C    | V                 |                                    | 1          |      | ns        |  |

| Overvoltage Recovery Time <sup>11</sup>                 | +25°C    | V V               |                                    | 1          |      | ns        |  |

|                                                       |        |                  | AD9006/AD9016KE<br>AD9006/AD9016KZ |              |              |       |

|-------------------------------------------------------|--------|------------------|------------------------------------|--------------|--------------|-------|

| Parameter (Conditions)                                | Temp   | Test<br>Level    | Min                                | Тур          | Max          | Units |

| ENCODE INPUT                                          |        |                  |                                    | - <i>J</i> F |              |       |

| Logic "1" Voltage                                     | Full   | VI               | -1.1                               |              |              | V     |

|                                                       | Full   | VI               | 1.1                                |              | -1.5         | v     |

| Logic "0" Voltage<br>Logic "1" Current                | Full   | VI               |                                    |              | 400          | μA    |

| Logic "0" Current                                     | Full   | VI               |                                    |              | 200          | μA    |

|                                                       | +25°C  | v                |                                    | 3            | 200          | pF    |

| Input Capacitance<br>Encode Pulse Width <sup>12</sup> | +25°C  | I                | 1.0                                | 5            |              | ns    |

|                                                       | +25 C  | 1                | 1.0                                |              |              |       |

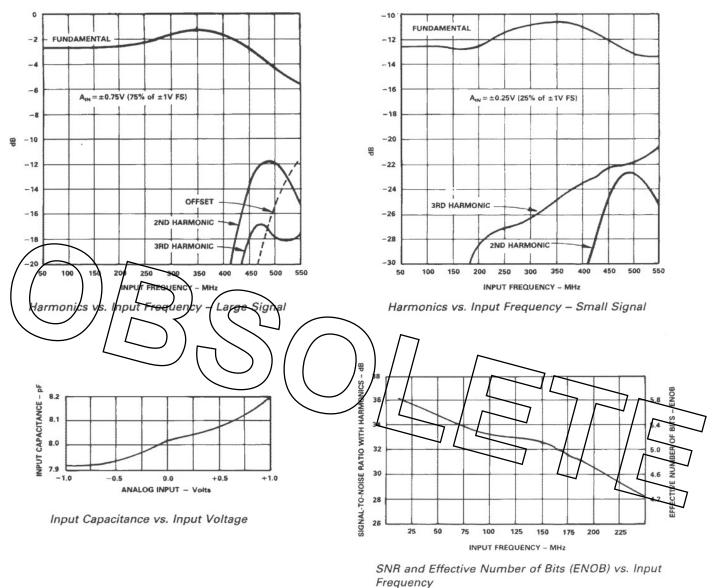

| AC LINEARITY <sup>13</sup>                            |        |                  |                                    |              |              |       |

| Effective Number of Bits (ENOB)                       |        |                  |                                    |              |              | D     |

| Analog Input @ 49MHz                                  | +25°C  | I                | 5.2                                | 5.5          |              | Bits  |

| Analog Input @ 196MHz                                 | +25°C  | I                | 4.4                                | 5.0          |              | Bits  |

| In-Band Harmonics                                     |        |                  |                                    | 100          |              |       |

| Analog Input @ 9.3MHz                                 | +25°C  | I                | 42                                 | 48           |              | dBc   |

| Analog Input @ 49MHz                                  | +25°C  | I                | 38                                 | 44           |              | dBc   |

| Analog Input @ 92MHz                                  | +25°C  | I                | 33                                 | 36           |              | dBc   |

| Analog Input (a 145MHz                                | +25°C  | I                | 33                                 | 36           |              | dBc   |

| Analog Input @ 196MHz                                 | +25°C  | I                | 31                                 | 36           |              | dBc   |

| Signal-to-Noise Ratio+4                               |        | $\sim$           |                                    |              |              |       |

| (With Harmonics)                                      |        |                  |                                    |              |              |       |

| Analog Input @ 9.3MHz                                 | +25°C  |                  | 34                                 | 37           |              | dB    |

| Analog Input @ 49MHz                                  | +25°C  |                  | 30                                 | 35           |              | dB    |

| Analog Input @ 92MHz                                  | +25°C  |                  | 30                                 | 347          | _            | dB    |

| Analog Input @ 145MHz                                 | +25°C  | $X \downarrow I$ | 30                                 | 33           |              | dB    |

| Analog Input @ 196MHz                                 | +85°C  |                  | 29                                 | 32           |              | dB    |

| Signal-to-Noise Ratio <sup>14</sup>                   |        |                  |                                    | $\sim 1$     | $    \neg  $ |       |

| (Without Harmonics)                                   |        |                  | $\neg    $                         | -            |              | /     |

| Analog Input @ 9.3MHz                                 | +25°C  | I                | 36                                 | 37           |              | dB    |

| Analog Input @ 49MHz                                  | +25°C  | I                | 33                                 | 86           |              | dB    |

| Analog Input @ 92MHz                                  | +25°C  | 1                | 33                                 | 36           |              | dB    |

| Analog Input @ 145MHz                                 | +25°C  | I                | 33                                 | 35           |              | dB    |

| Analog Input @ 196MHz                                 | +25°C  | Î                | 31                                 | 34           | <u> </u>     | dB    |

| Two-Tone Intermodulation                              | 1250   | -                | 54                                 | 54           |              |       |

| Distortion Rejection <sup>15</sup>                    | +25°C  | v                |                                    | 50           |              | dB    |

|                                                       | 1250   |                  |                                    | 50           |              |       |

| DIGITAL OUTPUTS <sup>6</sup>                          |        |                  |                                    |              |              | X7    |

| Logic "1" Voltage                                     | Full   | VI               | -1.1                               |              | 1.6          | V     |

| Logic "0" Voltage                                     | Full   | VI               |                                    |              | -1.5         | V     |

| POWER SUPPLY (AD9006)                                 |        |                  |                                    |              |              |       |

| Positive Supply Current                               | +25°C  | I                | 1                                  | 25           | 29           | mA    |

| $(+V_{s} = +5.0V)$                                    | Full   | VI               |                                    |              | 30           | mA    |

| Negative Supply Current                               | +25°C  | I                |                                    | 320          | 380          | mA    |

| $(-V_s = -5.2V)$                                      | Full   | VI               |                                    |              | 395          | mA    |

| Nominal Power Dissipation                             | +25°C  | v                |                                    | 1.7          |              | W     |

| Reference Ladder Dissipation                          | +25°C  | V                |                                    | 50           |              | mW    |

| Power Supply Rejection Ratio <sup>16</sup>            | Full   | VI               |                                    | 2            | 4            | mV/   |

|                                                       |        |                  |                                    |              |              |       |

| POWER SUPPLY (AD9016)                                 | 1.3590 | т                |                                    | 25           | 29           | mA    |

| Positive Supply Current                               | +25°C  | I                |                                    | 23           | 30           | mA    |

| $(+V_{s} = +5.0V)$                                    | Full   | VI               |                                    | 275          |              |       |

| Negative Supply Current                               | +25°C  | I                |                                    | 375          | 420          | mA    |

| $(-V_{\rm S} = -5.2V)$                                | Full   | VI               |                                    | 2.0          | 450          | mA    |

| Nominal Power Dissipation                             | +25°C  | V                |                                    | 2.0          |              | W     |

| Reference Ladder Dissipation                          | +25°C  | v                |                                    | 50           |              | mW    |

| Power Supply Rejection Ratio <sup>16</sup>            | Full   | VI               |                                    | 2            | 4            | mV/   |

For applications assistance, phone Computer Labs Division at (919) 668-9511.

NOTES

Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.  $^{2}+V_{REF} > -V_{REF}$  under all circumstances.

<sup>3</sup>Typical thermal impedances:

68-pin leaded ceramic chip carrier  $\theta_{JA} = 31^{\circ}C/W$ ;  $\theta_{JC} = 1.1^{\circ}C/W$ .

68-pin ceramic LCC  $\theta_{JA} = 36^{\circ}$ C/W;  $\theta_{JC} = 2.6^{\circ}$ C/W. \*Measured with analog input =0V.

Measured with use of Fast Fourier Transform (FFT). See Definitions.

<sup>6</sup>Outputs terminated through 100Ω to -2.0V; C<sub>L</sub><4pF

<sup>7</sup>Measured from 50% point of leading edge of ENCODE command to -1.3V point of output data.

8Output time skew includes HIGH-to-LOW and LOW-to-HIGH transitions as well as bit-to-bit time skew differences.

<sup>9</sup>Measured from 50% point of trailing edge of ENCODE command to 50% point of Data Ready pulse.

<sup>10</sup>For full scale step input, 6-bit accuracy is attained in the specified time.

<sup>11</sup>Recovers to 6-bit accuracy in specified time after 150% full scale input overvoltage.

<sup>12</sup>ENCODE command rise/fall times should be less than 2.5ns for normal operation.

<sup>13</sup>Measured at 400MSPS encode rate; input level 1.0dB below full scale (FS).

<sup>14</sup>RMS signal to rms noise with analog input signal of 1dB below full scale at specified frequency. <sup>15</sup>Intermodulation measured with analog input frequencies of 60MHz and 70MHz at 7dB below full scale.

16 Measured at + Vs  $\pm 5.0V \pm 5\%$  or  $-V_s = -5.2V \pm 5\%$ ; specification shown is for worst case (see Definitions).

change without notice. Speci catio

EX ATION OF **TEST LEVELS** 1 100 ctio h tested. D iction tested a 100% d sample tested d DI at specified ten peratures III Sample tested only and characte IV Parameter is guaranteed des rization ign testing. V Parameter is a typical value only. VI All devices are 100% production tested at 100% production tested at temperature extremes for extended temperature devices; sample tested at temperature extremes for commercial/industrial devices.

#### ORDERING GUIDE

| Model <sup>1</sup> Temperatu |            | Description                          | Package<br>Option <sup>2</sup> |  |

|------------------------------|------------|--------------------------------------|--------------------------------|--|

| AD9006KE                     | 0 to +70°C | 68-Pin Ceramic LCC                   | E-68A                          |  |

| AD9006KZ                     | 0 to +70°C | 68-Pin Leaded Ceramic Chip Carrier   | Z-68                           |  |

| AD9016KE                     | 0 to +70°C | 68-Pin Ceramic LCC                   | E-68A                          |  |

| AD9016KZ                     | 0 to +70°C | 68-Pin Leaded Ceramic Chip Carrier   | Z-68                           |  |

| AD9016KE/PCB                 | 0 to +70°C | Evaluation Board; AD9016KE Installed |                                |  |

| AD9016/PCB                   | 0 to +70°C | Evaluation Board; No Converter       |                                |  |

NOTES

MIL-STD-883 versions available; contact factory.

<sup>2</sup>E = Ceramic Leadless Chip Carrier; Z = Ceramic Leaded Chip Carrier.

Downloaded from Elcodis.com electronic components distributor

#### Signal-to-Noise Ratio (SNR)

The ratio of the rms signal amplitude to the rms value of "noise", which is defined as the sum of all other spectral components, including harmonics but excluding dc, with an analog input signal 1dB below full scale.

### **Transient Response**

The time required for the converter to achieve 6-bit accuracy when a full scale step function input is applied to the unit.

### Two-Tone Intermodulation Distortion (IMD) Rejection

The ratio of the power of a two-tone signal to the power of the strongest third-order IMD signal.

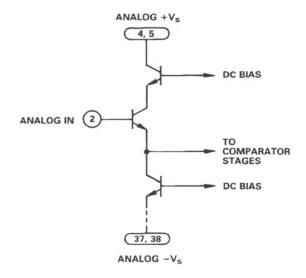

"Flash" architecture used in the AD9006 and AD9016 units makes it unnecessary to use a track-and-hold (T/H) ahead of the converter in many applications. The analog input signal is impressed across 64 parallel comparator stages.

Bias points of these comparators are established by the voltages applied to the reference ladder via  $+V_{REF}$ , MIDSCALE<sub>REF</sub> and  $-V_{REF}$ .

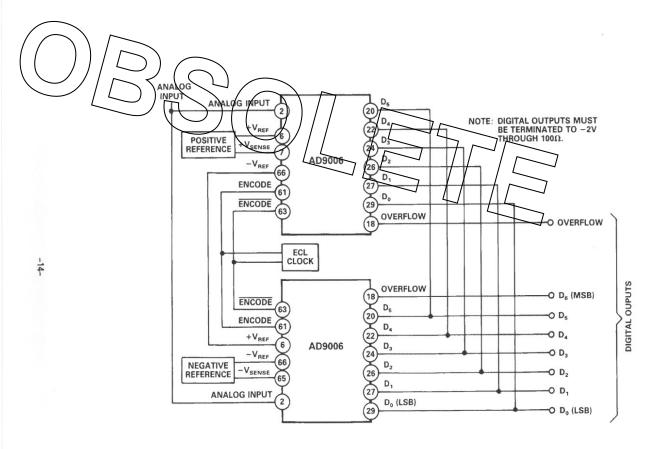

The outputs of the comparators are applied to the decoding logic; from here, the data are applied to output latches as six bits of digital data and an overflow bit. The overflow bit can be used to stack converters to obtain additional bits of resolution and can also be used as a "flag" for indicating positive out-ofrange inputs.

Capturing output data at the (guaranteed) encode rates of 470MSPS of the AD9016 is simplified by virtue of using two Data Ready pulses. Output data words alternate between Bank A and Bank B; this allows clocking demultiplexed data from the AD9016 at half the converter's sample rate.

The Data Ready pulses track the propagation delay of the output data and relieve the need to build an external clock circuit for tracking prop delay over the full operating temperature range.

Demultiplexed ports connected to Bank A and Bank B allow the user to capture output data with 100K ECL logic even when the converter is operating at 470MSPS. The AD9016 introduces only one pipeline delay in the processing of these digital output data, thereby reducing the number of clock cycles required to obtain the digital representation of the analog input at the appropriate output port.

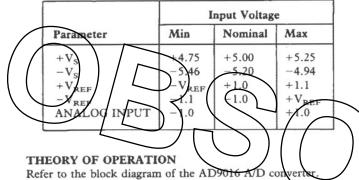

The analog input voltage range is determined by the usersupplied voltage references:  $+V_{REF}$  and  $-V_{REF}$ . The references can be adjusted between -1V and +1V. In all cases,  $+V_{REF}$  should be greater than  $-V_{REF}$ ; and the differential voltage between the references should not exceed 2.1V. MIDSCALE  $V_{REF}$  can be used to improve the integral linearity of the converter.

Another attractive feature of the analog input characteristics of the AD9016 is its low input capacitance of 8pF. In many other flash converters, this value is three or four times larger, making them difficult to drive at high input frequencies.

For those applications in which a single output port is preferred, the recommended choice is the AD9006 A/D converter.

The AD9006 is identical to the AD9016 in performance specifications; it is best suited for systems in which demultiplexing is not performed immediately after the flash converter. As in the AD9016, the AD9006 produces Data Ready pulses on chip; these can be used to clock external latches.

There are two control pins for determining the format of the output data on the AD9006/AD9016. BIT INVERT (MSB) allows the user to invert the most significant bit (D0<sub>5</sub>); and D<sub>0</sub>-D<sub>4</sub> INVERT allows the five least significant bits to be inverted. The AD9006/AD9016 Truth Table elsewhere in the data sheet provides the necessary information to select among binary, inverted binary, twos complement and inverted twos complement coding schemes.

The OVERFLOW INHIBIT pin controls the overflow bit (called out as OVERFLOW BIT in the AD9006, and OVER-FLOW<sub>A</sub> and OVERFLOW<sub>B</sub> in the AD9016). In normal operation, the OVERFLOW INHIBIT is connected to -5.2V, and OVERFLOW will be a digital HIGH whenever the analog input voltage exceeds the most positive comparator reference (+V<sub>SENSE</sub>). The digital outputs (D<sub>c</sub>-D<sub>b</sub>) will be LOW, i.e., returned-to-zero operation.

This feature means two AD9006 devices can be cauded or "stacked" to obtain seven-bit operation, as shown in the diagram below.

Connecting OVERFLOW INHIBIT to ground forces the overflow bit to remain low and disables the return-to-zero operation.

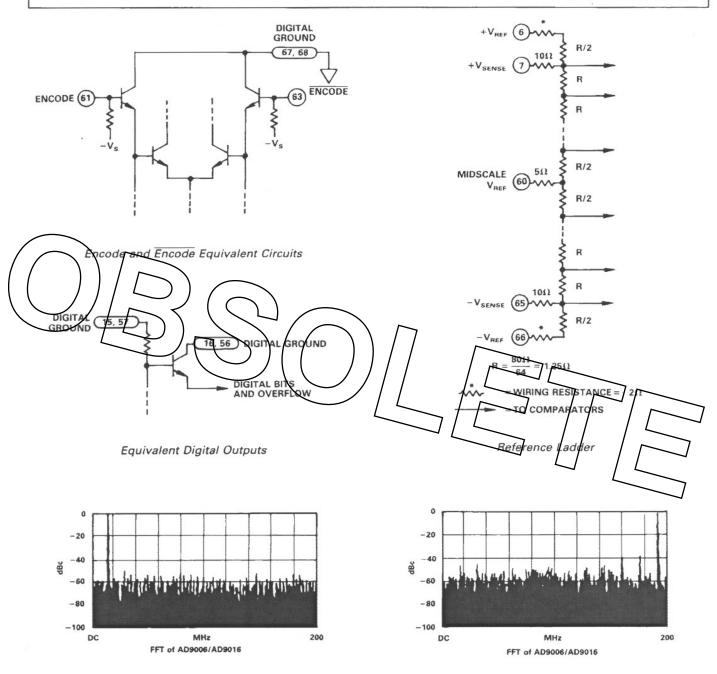

AD9016 Functional Block Diagram (Dotted Area Not Included in AD9006)

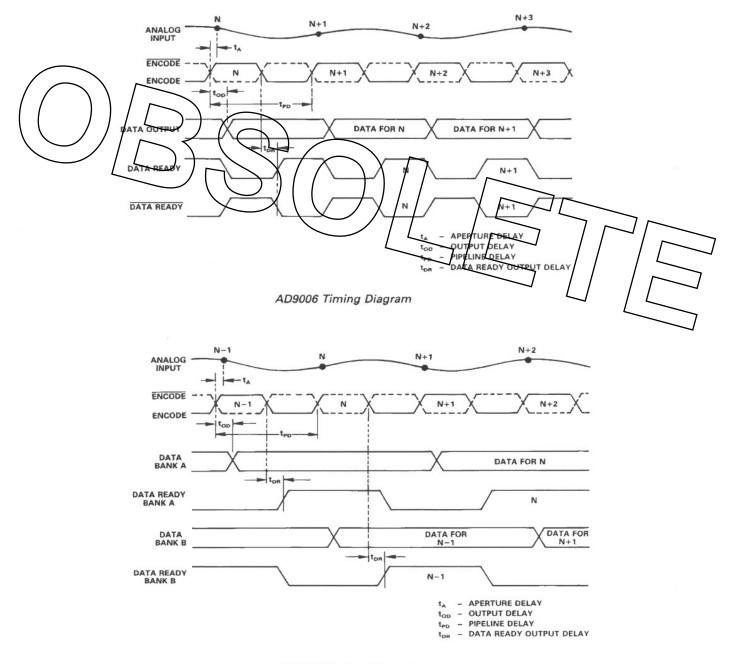

Timing for the AD9006 and AD9016 is shown in their respective timing diagrams. In both illustrations, the complementary encode command is shown in dashed lines.

The DATA READY and DATA READY pulses of the AD9006 correspond, respectively, to the DATA READY BANK A and DATA READY BANK B pulses of the AD9016. As shown in the SPECIFICATIONS table, Data Ready Output Delay is slightly different in the two units: 3.2ns in the AD9006 and 3.6ns in the AD9016.

Availability and timing of a DATA READY pulse help in retrieving data from either the AD9006 or the AD9016. When setting system timing, the user simply takes into account the (single) pipeline delay and the Data Ready Output Delay (3.2ns in the AD9006; 3.6ns in the AD9016) and uses the next DATA READY (or DATA READY in the AD9006) to strobe the desired output into external circuits.

### APPLYING THE AD9006/AD9016

#### Setting Reference Levels

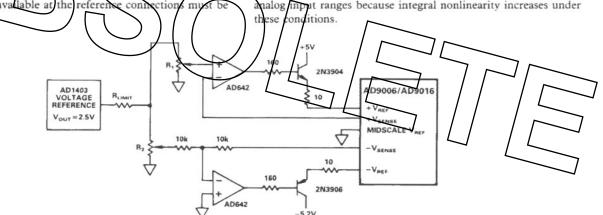

The AD9006/AD9016 requires that the user provide two voltage references:  $+V_{REF}$  and  $-V_{REF}$ . These two voltages are applied across the internal resistor ladder (nominally 80Ω) and determine the analog input range of the converter.

Care should be taken to assure that these references are driven from stable, low impedance sources. Reference connections should be capacitively coupled to ground to reduce interference generated by noise and/or digital switching.

Resistance between the reference connections and the point at which the first comparator threshold is connected causes offset errors. These errors, called "top and bottom of the ladder offsets," can be nulled out using the  $+V_{\text{SENSE}}$  and  $-V_{\text{SENSE}}$  connections. These sense lines are intended for connection only to high impedance (low current) nodes such as the input of an

op mp. Applying a v er than V across the internal resistor 2 ltage ler will cause current densities to exceed rated values and add permanent of cause amage to the AD9006/AD9016. The amoun current available at the reference connections must be limited.

One method of nulling the offset errors is shown in Figure 1.

The Analog Devices AD1403 voltage reference supplies a stable 2.5V reference for the circuit, and  $R_{LIMIT}$  determines the range over which the reference can be adjusted.  $R_1$  adjusts the voltage at the top of the internal reference ladder through the AD642/2N3904 combination. Feedback from the  $+V_{SENSE}$  line causes the op amp to compensate for offset which appears at the top comparator threshold. The transistor limits the amount of current drawn directly from the op amp; resistors at the base and emitter of the transistor stabilize its operation.

Voltage at the bottom of the reference ladder is controlled in essentially the same way, using  $R_2$  to adjust the reference ladder voltage; and using feedback from the  $-V_{\rm SENSE}$  connection to null any offset between the reference and the threshold of the bottom comparator.

The midpoint of the comparator reference ladder (MIDSCALE  $V_{REF}$ ) is shown tied to ground in Figure 1. This allows the user to adjust the voltage reference for minimum integral nonlinearity. This feature becomes important in applications with reduced analog input ranges because integral nonlinearity increases under

Figure 1. Reference Circuit

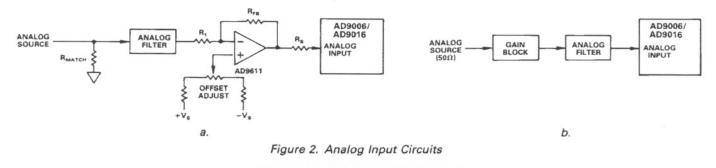

### Driving the Analog Input

Careful design and layout of the AD9006/AD9016 have resulted in a typical input capacitance of 8pF (9.5pF max). This is low in comparison to most flash converters, but it is still a significant load at high input frequencies and must be taken into account when choosing a drive amplifier.

DC-coupled applications require the performance characteristics of a wide bandwidth, low distortion op amp such as the Analog Devices AD9611. AC-coupled applications at high frequencies may be better served by using a low distortion gain block for the driver.

Figure 2 illustrates possible connections for both approaches.

Regardless of which driving circuit is selected for the application, the overall dynamic performance of the amplifier is enhanced by inserting a small series resistor between the output of the amplifier and the analog input of the converter.

REV. A

### **Clocking the Converter**

The encode command circuits of the AD9006/AD9016 (ENCODE and ENCODE) are designed to be driven by a differential ECL source.

A differential signal is recommended as the encode command to reduce jitter of the encode signal; increased jitter raises the noise floor of the converter. Full logic levels are preferred for triggering the clock circuits, but reduced levels can also be used. Caution should be exercised when using reduced-level encode commands because their slew rates will be decreased, which can raise the noise floor.

Refer again to the timing diagrams for the AD9006 and AD9016.

The rising edge of the ENCODE signal initiates the conversion process in the AD9006 unit. This same signal, delayed, becomes the DATA READY and complementary DATA READY pulses. Fast rise and fall times (<0.5ns) and "clean" edges are always required for encode commands, but are especially critical for high frequency analog signals.

In the AD9016, the leading edges of the DATA READY<sub>A</sub> and DATA READY<sub>B</sub> pulses are triggered by the trailing edge of an ENCODE command. Their trailing edges are triggered by the trailing edge of the next ENCODE command.

Although the AD9006/AD9016 is designed and tested to operate with a 50% duty cycle, the dynamic performance at high encode rates can be improved by changing the divy cycle.

Two possible methods of clocking the AD9006/AD9016 are shown in Figure 3. Users planning to implement these circuits need to be aware they may not function over the same temperature ranges possible with the converters.

Both ECL oscillators and saw filter oscillators are available as comercial products, with each type operating at some preselected frequency. The type of oscillator which is selected is a function of the desired operating frequency for the circuit being designed.

### Layout and Power Supplies

Correct layout of high speed circuits is always critical, but is particularly important when both analog and digital signals are involved. Analog signal paths should be kept as short as practical, and be properly terminated to avoid reflections and signal distortions. The analog input and voltage references should be kept away from digital signal paths; this reduces the possibility of capacitvely coupling digital switching noise into the analog section of the circuit.

Digital signal paths should also be kept short, and digital run lengths should be matched because propagation delays through digital paths become significant at high data rates. Proper ECL terminations should be used at or near the packages containing successive gates.

Ideally, analog signal paths and digital signal paths should be routed as far away from one another as possible and should never closely parallel one another's paths. If they must cross, they should do so at right angles to avoid interference.

In any layout of high speed circuits, the layout of ground connections is the most important factor. To reduce noise and interference on the circuit ground, a double-sided copper-clad printed circuit board (PCB) is recommended. Every part of the board not used for components or conducting runs should be ground plane. Components are mounted on one side; the opposite side is used for power and signal connections.

It is especially important to retain the continuity of the ground plane under and around the AD9006/AD9016 converter. If the system design separates the digital and analog ground returns, both should be connected together and to ground close to the unit to form a continuous ground plane around the A/D section of the system.

Low noise, low ripple temperature-stable linear power supplies are the preferred choices for high speed circuits. Switching power supplies often seem to meet these criteria, including rip ple specifications. But ripple specs are generally expressed in terms of rms – and the spikes generated in switchers can produce hard to-filter, uncontrollable noise peaks with amplitudes of several hundred millivolts. Their high frequency components may be extremely difficult to keep out of the ground system.

If switching power supplies cannot be avoided for high speed designs, they should be *carefully* shielded and their outputs should be well filtered.

Figure 3. Clock Circuits

Every power supply line leading into a high speed PCB or data acquisition circuit must be carefully bypassed to its ground return to prevent noise from entering the circuit. Ceramic capacitors, ranging in value from  $0.01\mu$ F to  $0.1\mu$ F, should be used generously in the layout, mounted as closely as possible to the device or circuit being bypassed.

The capacitors which are used should have a high resonant frequency to insure they maintain their characteristics in the range of frequencies involved in the encoding process. Ceramic surface mount (chip) capacitors meet that requirement and are easily placed near the package connections.

At least one high quality tanatalum capacitor of  $3\mu F$ -  $20\mu F$  should be assigned to each power supply voltage, mounted as near as possible to the incoming power pins to minimize low frequency ripple.

### Handling the AD9006/AD9016 Package

Several predautions have been included in the design of the AD9006/AD9016 converter to help reduce its sensitivity to electrostatic discharge (ESD). But the user should always use normal ESD precautions to help insure device reliability and avoid degrading the unit's performance.

Package options which are available include both leaded and leadless 68-pin ceramic chip carriers; these are shown in the data sheet as leaded ceramic chip carrier and leadless chip carrier (LC), respectively. Both of these packages have been specially designed to maintain the converter's high frequency parameters while operating over a standard military temperature range.

Regardless of package type, the top of the package (containing the model number and the Analog Devices logo) is internally connected to the device substrate and is designed to be used as a heat sink. The substrate is connected to  $-V_s$  internally; therefore the top of the package should be allowed to "float" in voltage. The bottom of the package is not connected internally on the device.

High speed devices such as the AD9006/AD9016 converters should be soldered into final applications. There is a temptation to use sockets, but they can limit dynamic performance and should be used only for evaluation or prototype applications.

| Step | Input Voltage<br>(FS =±1.0V) | True                                 | Inverted                                                                                               | Offset Twos<br>True                  | Complement<br>Inverted                                                            | _  |

|------|------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------|----|

|      |                              | $MSB INVERT = 1$ $D_0 - D_4 INV = 1$ | $\begin{array}{l} \text{MSB INVERT} = 0 \\ \text{D}_0 \text{-} \text{D}_4 \text{ INV} = 0 \end{array}$ | $MSE INVERT = 0$ $D_0 - D_4 INV = 1$ | $\begin{array}{c} \text{MSB INVERT} = 1 \\ D_0 - D_4 \text{ INV} = 0 \end{array}$ | _  |

| 00   | -1.000                       | 000000                               | 111111                                                                                                 | 100000                               |                                                                                   | _7 |

| 01   | -0.968                       | 000001                               | 111110                                                                                                 | 100001                               | 011110                                                                            |    |

|      |                              | *                                    |                                                                                                        |                                      |                                                                                   | -  |

|      | · ·                          |                                      | •                                                                                                      | •                                    |                                                                                   |    |

| 0    |                              |                                      |                                                                                                        | ÷.                                   |                                                                                   |    |

| 31   | -0.031                       | 011111                               | 100000                                                                                                 | 111111                               | 000000                                                                            |    |

| 32   | 0.000                        | 100000                               | 011111                                                                                                 | 000000                               | 111111                                                                            |    |

| 33   | +0.031                       | 100001                               | 011110                                                                                                 | 000001                               | 111110                                                                            |    |

|      |                              | *                                    |                                                                                                        | 10                                   |                                                                                   |    |

|      | •                            |                                      | •                                                                                                      | •                                    |                                                                                   |    |

|      |                              |                                      | ¥.                                                                                                     | •                                    |                                                                                   |    |

| 62   | +0.938                       | 111110                               | 000001                                                                                                 | 011110                               | 100001                                                                            | e  |

| 63   | +0.969                       | 111111                               | 000000                                                                                                 | 011111                               | 100000                                                                            |    |

| 63+  | +1.000                       | (0)1111111*                          | *000000(0)                                                                                             | (0)0111111*                          | (0)100000*                                                                        |    |

| 1999 |                              | (1)000000#                           | (1)111111#                                                                                             | (1)100000#                           | (1)011111#                                                                        |    |

\*OVERFLOW INHIBIT ="1"; #OVERFLOW INHIBIT ="0."

The overflow bit is always 0 except where noted in parentheses ( ). MSB INVERT, D<sub>0</sub>-D<sub>4</sub> INVERT

and OVERFLOW INHIBIT are considered dc controls. They are tied to ground for logic "1" and -V, for logic "0"; their "trip point" occurs at approximately -1.3V.

#### AD9006/AD9016 Truth Table

Equivalent Analog Input

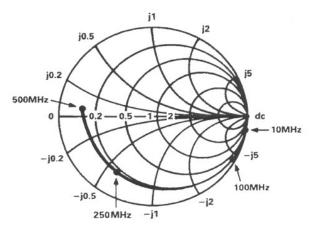

rrequency

Normalized 50 $\Omega$  Input Impedance vs. Input Frequency

400MSPS:  $F_{IN} = 14.8MHz$ ;  $V_{IN} = 1.0dB$  Below FS

400MSPS:  $F_{IN} = 192MHz$ ;  $V_{IN} = 1.0dB$  Below FS

Connections for 7-Bit Operation

AD9006/AD9016

REV. A

AD9016/PCB Block Diagram

AD9006/AD9016

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

PRINTED IN U.S.A

C1270-10-1/89