### DOT MATRIX LCD 40-OUT SEGMENT DRIVER

## ■ GENERAL DESCRIPTION

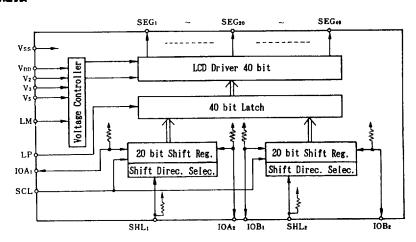

The NJU6407B is a serial input, 40-out segment driver for dot matrix LCDs, especially useful as extension driver for LCD controller drivers like NJU6408B.

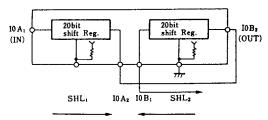

It consists of 40-bit (two of 20-bit) shift register, 40-bit latch, and 40 high voltage LCD drivers.

The shift direction of each 20-bit shift register can be set independently to each other, consequently the efficient extension driver allocation according to the number of characters and easy wiring with the LCD panel can be performed.

As the 40-driver have 4 level voltage inputs to drive the LCD, adjustable driving voltage according to the LCD panel can be supplied from the external power source.

#### ■ FEATURES

- 40 Segment Drivers

- 40-bit Shift Register

( Two of 20-bit Shift Registers )

Shift Direction of each 20-bit

Shift Registers Selection

- Two of Shift Direction Select Terminal

- Duty Ratio 1/8 to 1/16

- Fast Data Transmission ( Shift Clock 3.3 MHz Min. )

- External Power Supply for LCD Driving Voltage

- LCD Driving Voltage --- V<sub>DD</sub> 3V ~ V<sub>DD</sub> 13.5V

- Operating Voltage --- 5 V ± 10 %

- Package Outline --- QFP 56

- C-MOS Technology

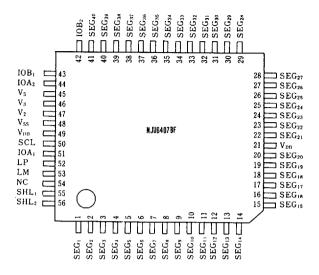

#### **■ PACKAGE OUTLINE**

NJU6407BF

#### ■ BLOCK DIAGRAM

**■** 6569883 0005305 805 **■**

#### ■ PIN CONFIGURATION

#### TERMINAL DESCRIPTION

| No.                  | SYMBOL                               | F U N C T I O N                                                                                                                                                                                                                                                                           |

|----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~20<br>22~41        | SEG₁~<br>SEG₄₀                       | LCD segment driving terminal.<br>Each terminal corresponds to each bit of shift register                                                                                                                                                                                                  |

| 21, 49<br>48         | V <sub>DD</sub><br>Vss               | Power supply terminal (connect to the controller's V <sub>DD</sub> terminal)<br>Power supply terminal (connect to the controller's V <sub>SS</sub> terminal)                                                                                                                              |

| 42<br>43             | 10B <sub>2</sub><br>10B <sub>1</sub> | Data input/output terminals for 21st to 40th bits shift register. Display data is input (output) syncronized with clock pulse. Input or output is selected by SHL2 terminal.                                                                                                              |

| 44<br>51             | 10A <sub>2</sub><br>10A <sub>1</sub> | Data input/output terminals for 1st to 20th bits shift register. Display data is input (output) syncronized with clock pulse. Input or output is selected by SHL1 terminal.                                                                                                               |

| 45 <sub>.47</sub> 46 | V <sub>5</sub> , V <sub>3</sub>      | LCD driving power source terminals. VDD ≥V2≥V3≥V5                                                                                                                                                                                                                                         |

| 50                   | SCL                                  | Shift register clock pulse input terminal. The data is shifted in the shift register by the falling edge of the clock pulse. A data setup time and hold time are required between data input and SCL. Clock pulse rising time and falling time should be set less than 50ns respectively. |

| 52                   | LP                                   | Latch pulse input terminal. The data in the shift register is latched to the Latch by this signal. "H": Data writing, "L": Data latch                                                                                                                                                     |

| 53                   | LM                                   | Alternate signal input for LCD driving.                                                                                                                                                                                                                                                   |

| 55                   | SHL <sub>1</sub>                     | Shift direction and input/output control terminal(Pull-up R). "H" or Open: Shift direction is from 1st bit to 20th bit. "L": Shift direction is from 20th bit to 1st bit.                                                                                                                 |

| 56                   | SHL <sub>2</sub>                     | Shift direction and input/output control terminal(Pull-up R). "H" or Open: Shift direction is from 21st bit to 40th bit. "L": Shift direction is from 40th bit to 21st bit.                                                                                                               |

| 54                   | NC                                   | Non connection.                                                                                                                                                                                                                                                                           |

## **■ 6569883 0005306 741 ■**

### FUNCTIONAL DESCRIPTION

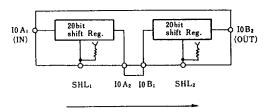

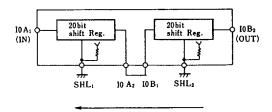

#### (1) Shift register control

The 40-bit shift register is devided into two of 20-bit shift register.

The shift direction of each 20-bit shift register can be set independently to each other shown in below.

| Control Terminal | Input       | Shift Direction                     |  |  |

|------------------|-------------|-------------------------------------|--|--|

| OUI              | "H" or Open | 10A₁ → 10A₂                         |  |  |

| SHL 1            | "L"         | 10A₁ ← 10A₂                         |  |  |

| OUI              | "H" or Open | $10B_1 \rightarrow 10B_2$           |  |  |

| SHL <sub>2</sub> | "L"         | 10B <sub>1</sub> ← 10B <sub>2</sub> |  |  |

(1-1) When the terminals SHL1 and SHL2 are "H" or open, the data shift from SEG1 to SEG40.

(1-2) When the terminals SHL1 and SHL2 are "L", the data shift from SEG40 to SEG1.

(1-3) Reversed sift direction to each other is also available.  $SEG_1 \rightarrow SEG_{20} \rightarrow SEG_{40} \rightarrow SEG_{21}$  example is shown in below:

**■** 6569883 0005307 688 **■**

## (2) LCD driver output truth table.

| Input Data | Selection/Non-selection | LM | Driver Output (SEG <sub>1</sub> to SEG <sub>40</sub> ) |

|------------|-------------------------|----|--------------------------------------------------------|

| "H"        | Selection               | Н  | V <sub>5</sub>                                         |

|            | Selection               | L  | <b>V</b> <sub>DD</sub>                                 |

| "L"        | Non-selection           | Н  | V <sub>3</sub>                                         |

|            | Non-serection           | L  | V <sub>2</sub>                                         |

#### ■ ABSOLUTE MAXIMUM RATINGS

( Ta=25℃ )

| PARAMETER                  | SYMBOL               | RATINGS                        | UNIT |

|----------------------------|----------------------|--------------------------------|------|

| Supply Voltage (1)         | <b>V</b> DD          | - 0.3 ~ + 7.0                  | ٧    |

| Supply Voltage (2) Note 1) | V <sub>DD</sub> ~ V₅ | $V_{DD}$ -13.5 ~ $V_{DD}$ +0.3 | ٧    |

| Input Voltage              | VIN                  | - 0.3 ~ V <sub>DD</sub> +0.3   | ٧    |

| Operating Temperature      | Topr                 | - 30 ~ + 80                    | ъ    |

| Storage Temperature        | Tstg                 | - 55 ~ + 150                   | ဗ    |

Note 1) The relation :  $V_{DD} \ge V_2 \ge V_3 \ge V_5$  must be maintained.

### ■ ELECTRICAL CHARACTERISTICS

• DC Characteristics

( V<sub>DD</sub>=5V±10% , Ta=-20 ~ +75℃ )

| PARAMETER            | SYMBOL          | CONDITIONS                        |                                                                                           | MIN                      | TYP  | MAX                       | UNIT |

|----------------------|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------|--------------------------|------|---------------------------|------|

| Input Voltage        | V <sub>ІН</sub> | LM, LP, SHL1, SHL2 Terminals      |                                                                                           | 0.8V <sub>DD</sub>       |      | <b>V</b> DD               | V    |

| Triput Yortage       | VIL             |                                   |                                                                                           |                          |      | 0.2V <sub>DD</sub>        |      |

|                      | IH1             | V <sub>1 H</sub> =V <sub>DD</sub> | LM, LP Terminals                                                                          |                          |      | 1                         | uA   |

| Innut Current        | IL1             | V1 L=0V                           |                                                                                           |                          |      | - 1                       |      |

| Input Current        | IH2             | V <sub>1 H</sub> =V <sub>DD</sub> | SHL <sub>1</sub> , SHL <sub>2</sub><br>Terminals                                          |                          |      | 1                         |      |

|                      | 1112            | V: "=0A                           |                                                                                           | - 10                     | - 15 | - 25                      |      |

| Output Voltage       | <b>V</b> он     | l₀=- 40uA                         | 10A <sub>1</sub> , 10A <sub>2</sub> ,<br>10B <sub>1</sub> , 10B <sub>2</sub><br>Terminals | 4.2                      |      |                           | ٧    |

|                      | Aor             | I₀= 400uA                         |                                                                                           |                          |      | 0.4                       |      |

| Driver On-resistance | Ron             | ld=0.05mA                         | SEG <sub>1</sub> ~ SEG <sub>40</sub><br>Terminals                                         |                          |      | 30                        | kΩ   |

| Operating Current    | مما             | SCL=1.5MHz,<br>No Load            | LM,LP=130us cycle                                                                         |                          | 0.6  | 1.0                       | mA   |

| LCD Driving Voltage  | VLCD            | V <sub>DD</sub> - V <sub>5</sub>  |                                                                                           | V <sub>DD</sub> -<br>3.0 |      | V <sub>DD</sub> -<br>13.5 | ٧    |

# **■ 6569883 0005308 514 ■**

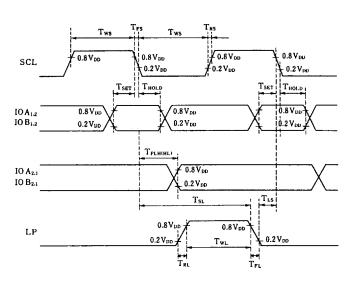

## • AC Characteristics

| PARAMETER                   | SYMBOL                            | CONDITIONS  | MIN | TYP | MAX | UNIT |

|-----------------------------|-----------------------------------|-------------|-----|-----|-----|------|

| Propagation Delay Time      | T <sub>PLH(HL)</sub>              |             |     |     | 250 | ns   |

| Maximum Operating Frequency | fscl                              | Duty = 50 % | 3.3 |     |     | MHz  |

| SCL Pulse Width             | Tws                               |             | 125 |     |     | ns   |

| LP Pulse Width              | Twl                               |             | 125 |     |     | ns   |

| Set up Time                 | Tset                              |             | 50  |     |     | ns   |

| SCL → LP Time               | Tsl                               |             | 250 |     |     | ns   |

| LP → SCL Time               | TLS                               |             | 0   |     |     | ns   |

| Data Hold Time              | THOLD                             |             | 50  |     |     | ns   |

| SCL Rise, Fall Time         | T <sub>FS</sub> , T <sub>RS</sub> |             |     |     | 50  | ns   |

| LP Rise, Fall Time          | T <sub>FL</sub> , T <sub>RL</sub> | ·           |     |     | 1   | us   |

10

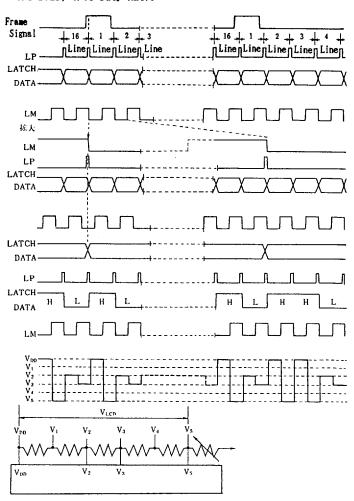

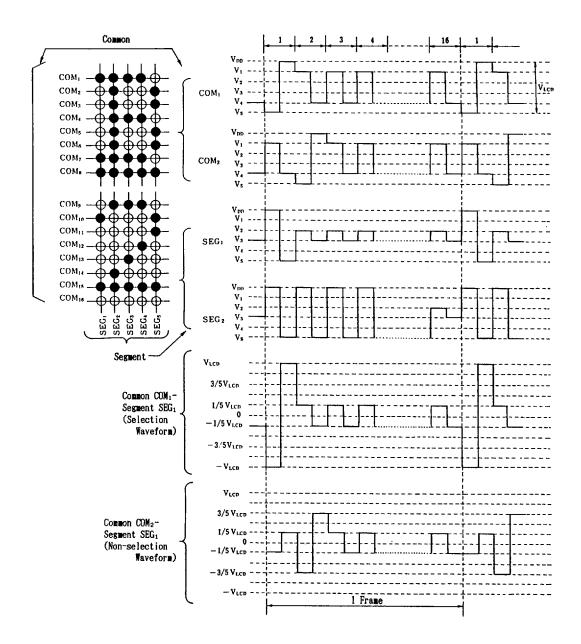

## TIMING CHART

## 1/5 Bias, 1/16 Duty Ratio

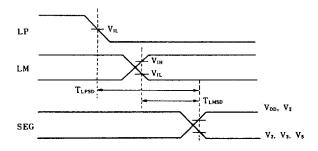

## M SEGMENT SIGNAL OUTPUT TIMING

| PARAMETER                  | SYMBOL | CONDITIONS             | MIN | TYP | MAX | UNIT |

|----------------------------|--------|------------------------|-----|-----|-----|------|

| LP - SEG Output Delay Time | TLPSD  | C <sub>L</sub> = 100pF |     |     | 4.5 |      |

| LM - SEG Output Delay Time | TLMSD  | C <sub>L</sub> = 100pF |     |     | 4.5 | us   |

**■** 6569883 0005310 172 **■**

LCD DRIVING WAVEFORM EXAMPLE

1/5 Bias, 1/16 Duty Ratio

10

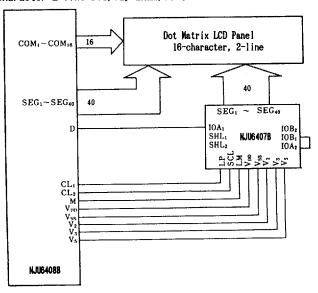

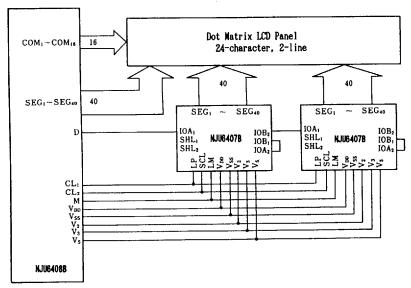

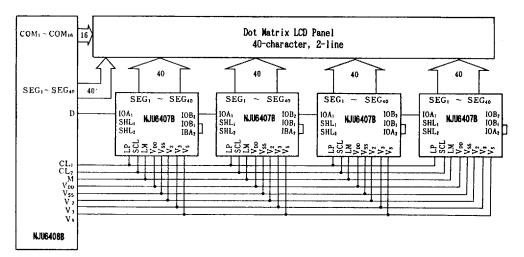

## ■ APPLICATION CIRCUITS

(1) 16-character 2-line Display Example (Combine with NJU6408B)

(2) 24-character 2-line Display Example ( NJU6408B + NJU6407B x 2 )

(3) 40-character 2-line Display Example (  $NJU6408B + NJU6407B \times 4$  )

■ 6569883 0005313 981 ■