# **CYNCP80192 Network Database Coprocessor**

## **CONTENTS**

| 1.0 OVERVIEW                                                                                                                              | 5           |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2.0 FEATURES                                                                                                                              | 6           |

| 3.0 FUNCTIONAL DESCRIPTION                                                                                                                | 7           |

| 3.1 Configuration Registers 3.2 Operating Registers 3.3 Pipeline and Table Management and Bus Protocol Conversion Logic 3.4 NSE Interface | 7<br>7<br>7 |

| 3.5 Associative SSRAM Interface                                                                                                           |             |

| 4.0 SIGNAL DESCRIPTION                                                                                                                    |             |

| 5.0 CLOCKS                                                                                                                                |             |

| 6.0 REGISTERS                                                                                                                             | 12          |

| 6.1 Coprocessor Interface Register                                                                                                        |             |

| 7.0 OPERATING REGISTERS                                                                                                                   | 15          |

| 7.1 Address Mapping                                                                                                                       | 16          |

| 8.0 NDC SUBSYSTEM POWER-UP INITIALIZATION PROCEDURE                                                                                       | 23          |

| 9.0 ZBT PIPELINED SSRAM INTERFACE MODE                                                                                                    | 24          |

| 10.0 ZBT FLOWTHROUGH SSRAM INTERFACE MODE                                                                                                 | 25          |

| 11.0 SYNCBURST PIPELINED SSRAM INTERFACE (EARLY WRITE)                                                                                    | 26          |

| 12.0 SYNCBURST PIPELINED SSRAM INTERFACE MODE (LATE WRITE)                                                                                |             |

| 13.0 APPLICATION INFORMATION                                                                                                              |             |

| 14.0 INFORMATION ON EXTERNAL TRANSCEIVERS                                                                                                 | 29          |

| 15.0 JTAG (1149.1) TESTING                                                                                                                | 30          |

| 16.0 ELECTRICAL CHARACTERISTICS                                                                                                           | 31          |

| 17.0 ORDERING INFORMATION                                                                                                                 | 39          |

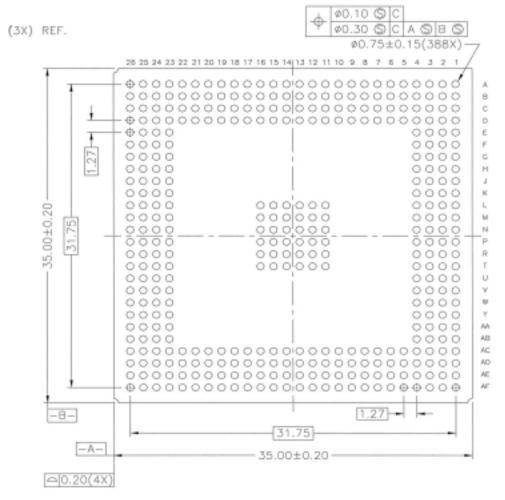

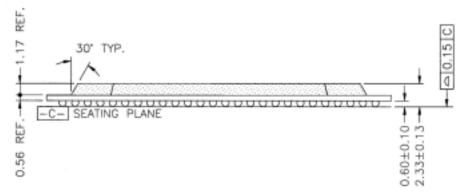

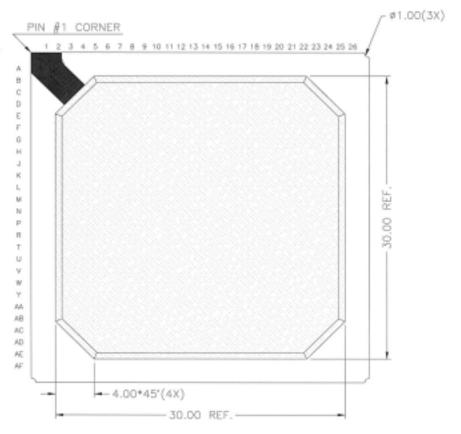

| 19 O DACKACE DRAWINGS                                                                                                                     | 40          |

## **LIST OF FIGURES**

| Figure 2-1. CYNCP80192 Block Diagram                                         | 6  |

|------------------------------------------------------------------------------|----|

| Figure 5-1. NDC Clocks                                                       |    |

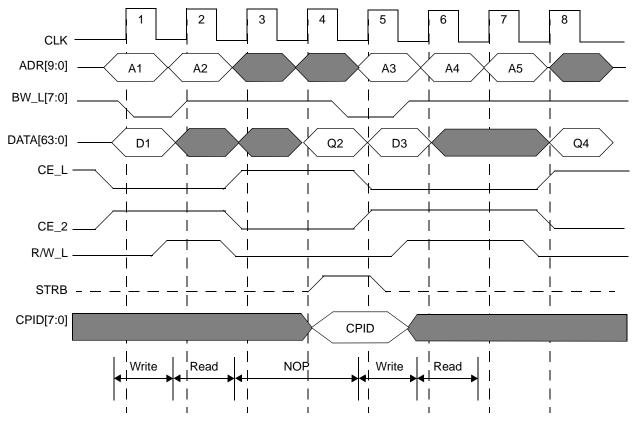

| Figure 9-1. ZBT Pipelined SRAM Interface (Mode 000)                          |    |

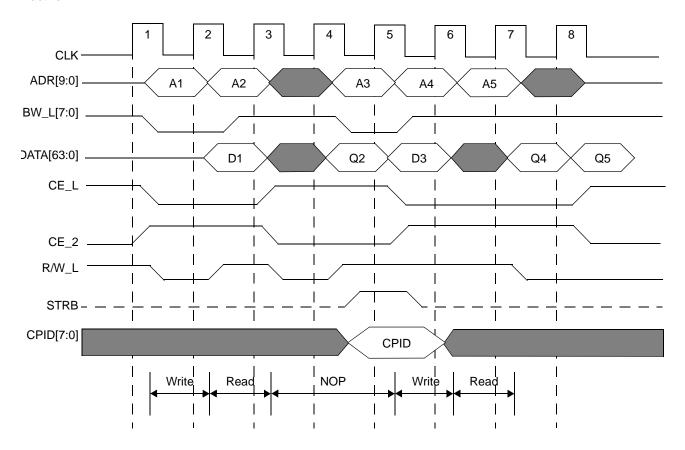

| Figure 10-1. ZBT Flowthrough SSRAM Interface (Mode 001)                      | 25 |

| Figure 11-1. SyncBurst Pipelined SSRAM Interface (Early Write)               | 26 |

| Figure 12-1. SyncBurst Pipelined SSRAM Interface (Late Write)                | 27 |

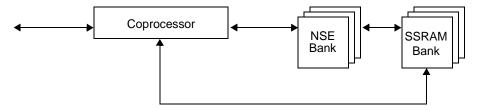

| Figure 13-1. Configuration 1—Associative SSRAM Mode                          | 28 |

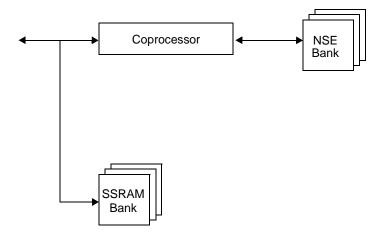

| Figure 13-2. Configuration 2—Index Mode                                      | 28 |

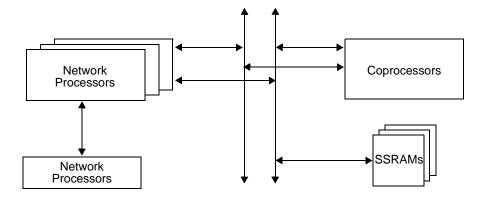

| Figure 13-3. Switching Systems Block Diagram                                 |    |

| Figure 14-1. Use of Transceiver Enables                                      |    |

| Figure 14-2. Transceiver Connected Between CYNPC80192 and CYNSE70XXX Devices | 29 |

| Figure 16-1. Pinout Diagram                                                  |    |

| Figure 18-1. Package Bottom View                                             |    |

| Figure 18-2. Package Side View                                               |    |

| Figure 18-3. Package Top View                                                |    |

|                                                                              |    |

## **LIST OF TABLES**

| Table 4-1. Search Coprocessor Pin Description                                | 8  |

|------------------------------------------------------------------------------|----|

| Table 6-1. Register Partitions for Coprocessor Access                        | 12 |

| Table 6-2. Configuration and Status Registers Area                           | 12 |

| Table 6-3. Configuration Register                                            | 12 |

| Table 6-4. Error and Status Register                                         | 13 |

| Table 6-5. Error Codes                                                       | 13 |

| Table 6-6. Information Register Description                                  |    |

| Table 7-1. Operating Registers Addressing Mapping (ADR[9] = 1)               | 15 |

| Table 7-2. Context Descriptor Organization                                   | 16 |

| Table 7-3. Descriptor Command                                                | 16 |

| Table 7-4. Read Command                                                      |    |

| Table 7-5. Write Command                                                     |    |

| Table 7-6. Search Data                                                       |    |

| Table 7-7. Move Command Parameters                                           |    |

| Table 7-8. Swap Command Parameters                                           | 19 |

| Table 7-9. SSRAM Data                                                        |    |

| Table 7-10. NSE Data, Mask, and Register Locations                           |    |

| Table 7-11. Read Response at Result Register 0                               |    |

| Table 7-12. Data Read from NSE                                               |    |

| Table 7-13. Data Read from SSRAM                                             |    |

| Table 7-14. Write/Move/Swap/Learn Results Register 0                         |    |

| Table 7-15. Result Register 0 for Search Operation                           |    |

| Table 7-16. Result Register 1 (Search Result Bit in Data Field = 0)          |    |

| Table 7-17. Result Register 1 (Search Result Bit in Data Field = 1)          |    |

| Table 7-18. Search Response in Result Register 0 (type I)                    |    |

| Table 7-19. Index Bits for NSEs                                              |    |

| Table 15-1. Test Access Port Controller Instructions                         |    |

| Table 15-2. Test Access Port Device ID Register                              | 30 |

| Table 16-1. Electrical Characteristics                                       |    |

| Table 16-2. Capacitance                                                      |    |

| Table 16-3. Operating Conditions                                             |    |

| Table 16-4. AC Timing Parameters for Pipelined ZBT SSRAM and SyncBurst SSRAM |    |

| Table 16-5. AC Timing Parameters for ZBT and Flow-Through SSRAM              |    |

| Table 16-6. CYNPC80192 Pinout Description                                    |    |

| Table 17-1. Ordering Information                                             | 39 |

#### 1.0 Overview

Cypress Semiconductor Corporation's (Cypress's) network database coprocessor (NDC) performs the following three primary functions.

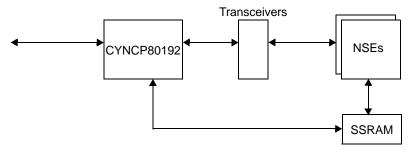

- Interconnection bridge function. The CYNCP80192 device acts as a bridge between network processor(s) and a search subsystem of Cypress's CYNSE70XXX network search engines (NSEs) plus optional associated SSRAMs that contain a search database and the associated data for a variety of network protocol layers. The CYNCP80192 device interfaces to the network processor with an SSRAM interface and offloads the search function to provide support for fast packet processing in routers and switches.

- **Pipeline management function**. Cypress's NSEs have a pipelined architecture to optimize search performance and throughput. The CYNCP80192 device manages the pipeline for optimal search performance and packs instructions back to back in order to avoid any bubbles in the pipeline.

- Table management function. The CYNCP80192 device builds on the simple instructions of the NSEs to provide advanced instructions for table management.

There are two ways to build the NDC system.

- In the first system the associative data SRAMs are connected to the CYNCP80192 device and the NSE(s) (see "NDC Subsystem Power-up Initialization Procedure" on page 23), and the CYNCP80192 device returns the associated data in response to a search operation. This type of implementation is suited to applications where the associative data size is up to eight bytes.

- In the second system, the CYNCP80192 device returns the index of the successful search entry to the network processor. The network processor uses this index to access SSRAMs in order to get the required results. The SSRAMs containing the associative data are connected directly to the network processor's SSRAM bus. This is suitable for applications where the associative data size is longer than eight bytes.

The NDC runs up to 100 MHz. At that speed and running with a 64-bit bus interface, the NDC performs at a peak rate of 33 million searches on 68-bit entries, 25 million searches on 136-bit entries, and 16.67 million searches on 272-bit entries. At 100-MHz speed and running with a 32-bit bus interface, the NDC performs at a peak rate of 25 million searches on 68-bit entries, 16.67 million searches on 136-bit entries, and 10 million searches on 272-bit entries.

The NDC supports centralized, multiple layer, multiwidth tables in order to provide cost effective search solutions for Ethernet, asynchronous transfer mode (ATM), and Sonet-based switches and routing systems. It supports the following advanced capabilities: quality of service (QoS), class of service (CoS), virtual private network (VPN), packet and flow classification, and security.

Document #: 38-02043 Rev. \*B Page 5 of 42

## 2.0 Features

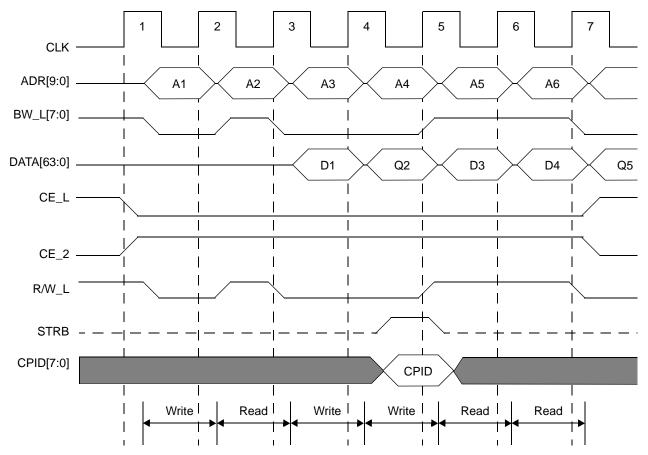

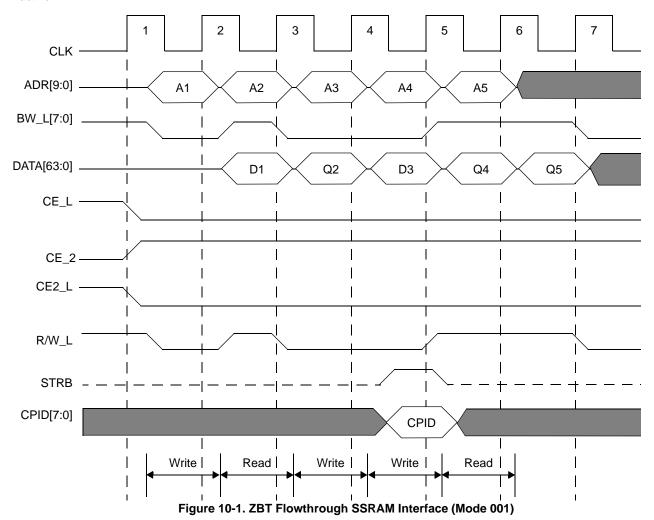

- The hardware interface to the NDC uses an SSRAM interface. The CYNCP80192 device supports ZBT™ pipelined, ZBT flowthrough, and SyncBurst™ pipelined (late and early write) types of SSRAMs.

- · All instructions and/or responses are mapped into the SSRAM address (ADR) space.

- The CYNCP80192 device provides simultaneous multiple layer, variable-width tables (x68, x136, x272).

- There is support for table sizes up to four million x34 entries.

- There are 33 million searches per second (Msps) in the x68 configuration (CFG).

- The CYNCP80192 device is compatible with 1-Mb, 2-Mb, and 4-Mb NSEs.

- It has a glueless interface to industry standard synchronous SRAMs and NSEs.

- The CYNCP80192 device uses up to 100 MHz master clock frequency.

- It has an IEEE 1149.1 test access port.

- There is a 2.5V/3.3V power supply and a 388-pin BGA package.

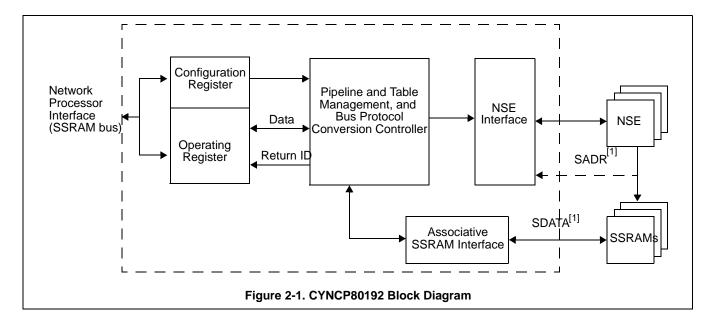

The CYNPC80192 NDC contains the following function blocks, shown in Figure 2-1.

#### Note

1. 1. The device can be configured for returning SADR or SDATA.

Document #: 38-02043 Rev. \*B Page 6 of 42

## 3.0 Functional Description

#### 3.1 Configuration Registers

The CFG registers contain information for configuring the CYNPC80192. These registers also include error, status, mask, and information registers.

## 3.2 Operating Registers

This logic block contains the random access registers through which the network processor(s) perform most of the table programming, management functions, and search operations (via a request-response protocol). A network processor posts operation requests and Reads responses back from this access block.

## 3.3 Pipeline and Table Management and Bus Protocol Conversion Logic

This unit uses pipeline management logic to optimize the search performance through the NSE pipeline. This unit posts the commands to the NSE and steers the results to the appropriate locations in the operating registers. It also converts the SSRAM interface information from a network processor into protocol cycles of the NSE transactions. This unit builds on the commands provided by the NSE to provide more advanced table management commands to the network processor.

#### 3.4 NSE Interface

This interface generates the appropriate hardware handshake with the NSE(s). This block is a slave to the pipeline control unit and drives the NSE(s) bus with the appropriate commands.

#### 3.5 Associative SSRAM Interface

The data transfer between the SSRAM and the pipeline unit takes place in this interface. The pipeline unit further transfers this information to the operating registers.

Document #: 38-02043 Rev. \*B Page 7 of 42

# 4.0 Signal Description

Table 4-1 provides information on pins and signal names for the CYNCP80192 device. Under the "Type" heading, I = Input, O = Output, and T = three-state.

Table 4-1. Search Coprocessor Pin Description

| Parameter          | Type       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Network Proces     | sor Interf | ace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| IRST_L             | I          | Synchronous Reset Input. Active low. Initializes the device to a known state.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| CLK <sup>[2]</sup> | I          | Coprocessor Clock Input. CLK may be run up to 100 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| ADR[9:0]           | I          | Coprocessor Location Address. This 10-bit address bus ADRs up to 1024 32-bit locations in the coprocessor. These 1024 locations are further divided into 512 32-bit locations of CFG area and 512 32-bit locations of the operating register area. When the data bus is configured as 64 bits wide (using the IWIDTH pin described below), the ADR[0] is ignored by the device. When the data bus is configured as 32 bits wide (using the IWIDTH pin described below), all the ADR bits are used by the device. |  |  |  |  |  |

| DATA[63:0]         | Ю          | <b>Coprocessor Data Bus</b> . Only the [31:0] field of this bus is used when the coprocessor is configured for a 32-bit interface (using the IWIDTH pin described below).                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CE_L               | I          | <b>Coprocessor Chip Enable</b> . This active low signal is used to enable the device. This is one of the three chip enables (CEs) to the coprocessor. All three CEs must be active to select the coprocessor.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| CE2_L              | I          | <b>Coprocessor Chip Enable</b> . This active low signal is used to enable the device. This is another one of the three CEs to coprocessor. All three CEs must be active to select the coprocessor.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| CE2                | I          | <b>Coprocessor Chip Enable</b> . This active high signal is used to enable the device. This is another one of the three CEs to the coprocessor. All three CEs must be active to select the coprocessor.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| R/W_L              | I          | <b>Read/Write</b> . This input determines whether it is a Read or a Write cycle. A low on this pin means it is a Write operation, and a High means it is a Read operation.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| OE_L               | I          | <b>Coprocessor Output Enable</b> . This active low asynchronous signal enables the output drivers of the data bus.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| BW_L[7:0]          | I          | <b>Synchronous Byte Write Enables</b> . These active low signals allow individual bytes to be written when a Write cycle is active. When the data bus is configured as 32 bits wide, only BW_L[3:0] is used and the BW_L[7:4] should be tied to V <sub>DD</sub> externally.                                                                                                                                                                                                                                      |  |  |  |  |  |

| BWE_L              | I          | <b>Byte Write Enable</b> . This active low signal allows the byte Write signals (BW_L[7:0]) to control the Write operation.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| STRB               | 0          | When the done bit is set in result register 0, STRB qualifies the CPID[7:0]. The network processor can use STRB signal to latch the CPID signals.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CPID[7:0]          | 0          | Context ID and Processor ID. When the result is Ready in the descriptor, the NDC outputs the processor and context IDs are concatenated as follows: {processor ID, context ID}. The bit length of the processor and context IDs can be programmed using the CFG register 0 (see CPCFG). See the STRB signal description also.                                                                                                                                                                                    |  |  |  |  |  |

| INTR/INTR_L        | 0          | This interrupt pin is asserted when the SE_FULL, DESC_AFULL, or error bits filed is set in the error status register. Interrupt can be active high or low, depending upon the polarity selected in the CFG register.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| SE_FULL            | 0          | NSE table full indicator to the network processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| DESC_AFUL          | 0          | This bit indicates that the descriptor array is almost full. When this flag is set, the processor can send only two more commands to the descriptor. The DESC_AF flag will be cleared if more that two descriptors are available.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| <b>NSE Command</b> | and DQ E   | Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

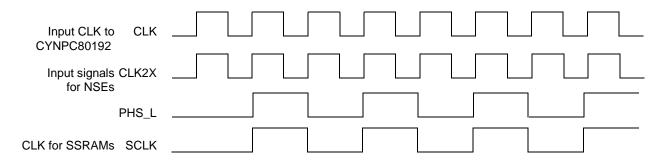

| CLK2X              | 0          | <b>NSE Master Clock</b> . CYNPC80192 drives this CLK to the NSE. The frequency of this CLK is twice the frequency of the NSE. This CLK runs up to 100 MHz and is derived by buffering the input CLK at the coprocessor interface.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| PHS_L              | 0          | <b>Phase Signal to the NSE</b> . This signal runs at half the frequency of CLK2X and synchronizes the alignment of the instruction to the NSE.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

#### Note:

2. "CLK" is an internal clock signal.

Document #: 38-02043 Rev. \*B Page 8 of 42

Table 4-1. Search Coprocessor Pin Description (continued)

| Parameter                  | Туре       | Description                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ORST_L                     | 0          | Reset Output to the NSE. Driving ORST_L low initializes the NSE.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| CMD[8:0]                   | 0          | <b>Command Bus to the NSE</b> . Bits [1:0] specify the command and [8:2] contain the command parameters. The descriptions of individual commands explain the details of the parameters. The encoding of commands based on the [1:0] field are: 00: Read; 01: Write; 10: Search; 11: Learn.                                                                       |  |  |  |  |

| CMDV                       | 0          | Command Valid to the NSE. Qualifies the CMD bus. 0: No command. 1: Command valid.                                                                                                                                                                                                                                                                                |  |  |  |  |

| DQ[67:0]                   | Ю          | SE Address/Data Bus. This signal carries the Read and Write address and data during register, ata, and mask array operations. It carries the compare data during search operations. It also carries the SSRAM address during SSRAM accesses to the SSRAMs containing the associative data.                                                                       |  |  |  |  |

| DQ_72                      | Ю          | When the CYNSE70128 NSE is used, the four additional DQ bits DQ[68:71] on the CYNSE70128 should be connected to the DQ_72 output from the CYNPC80192. The DQ_72 signal is driven low from the CYNPC80192.                                                                                                                                                        |  |  |  |  |

| ACK                        | I          | <b>Read Acknowledge</b> . This signal indicates that valid data is available on the DQ bus during register, data, and mask array Read operations to the NSE, or that the data is available on the SRAM data bus during Read operations of the SRAM containing associative data.                                                                                  |  |  |  |  |

| EOT                        | I          | <b>End of Transfer</b> . This signal indicates the end of a burst transfer during Read or Write burst operations to the NSE.                                                                                                                                                                                                                                     |  |  |  |  |

| SSF                        | I          | Search Successful Flag. This signal indicates that the search was successful in the NSE bank.                                                                                                                                                                                                                                                                    |  |  |  |  |

| SSV                        | I          | Search Successful Flag Valid. When asserted, this signal qualifies the SSF signal.                                                                                                                                                                                                                                                                               |  |  |  |  |

| FULL                       | I          | NSE entries full indicator.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

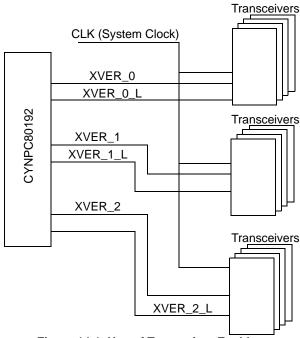

| XVER_0                     | 0          | Transceiver enable for driving signals to the NSE. Active high.[3]                                                                                                                                                                                                                                                                                               |  |  |  |  |

| XVER_0_L                   | 0          | Transceiver enable for driving signals from the NSE. Active low. <sup>[3]</sup>                                                                                                                                                                                                                                                                                  |  |  |  |  |

| XVER_1                     | 0          | Transceiver enable for driving signals to the NSE. Active high. <sup>[3]</sup>                                                                                                                                                                                                                                                                                   |  |  |  |  |

| XVER_1_L                   | 0          | Transceiver enable for driving signals from the NSE. Active low. [3]                                                                                                                                                                                                                                                                                             |  |  |  |  |

| XVER_2                     | 0          | Transceiver enable for driving signals to the NSE. Active high. <sup>[3]</sup>                                                                                                                                                                                                                                                                                   |  |  |  |  |

| XVER_2_L                   | 0          | Transceiver enable for driving signals from the NSE. Active low.[3]                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Associated SR              | AM Interfa | ce                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| SDATA[63:0]/<br>SADR[23:0] | I/O<br>I/O | SRAM Data/Address. This bus contains either the data from the associative SSRAM or the ADR (Index) from an NSE, depending on the value of the SRAM present bit in CFG register 0. {SDATA[63:0]} from SSRAMs should be connected to the 64-bit bus if the associative SSRAM is present, or else {SADR[23:0]} from the NSEs should be connected to the 64-bit bus. |  |  |  |  |

| SOE_L                      | I          | <b>SSRAM Output Enable</b> . This signal is the output enable control for the off-chip SSRAM bank that contains associative data and is driven by the NSE.                                                                                                                                                                                                       |  |  |  |  |

| SCLK                       | 0          | <b>SSRAM Clock</b> . This is the same in phase and frequency as the one created internally by the NSE. It is generated by dividing CLK by two, and is used to drive the SSRAM CLK input.                                                                                                                                                                         |  |  |  |  |

| Configuration              | I.         |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| IWIDTH                     | I          | This signal selects coprocessor data bus width. 1: 64 bits; 0: 32 bits.                                                                                                                                                                                                                                                                                          |  |  |  |  |

| BIG/LTL_L                  | I          | This selects how data from the network processor is interpreted.  1: Big Endian; 0: Little Endian.                                                                                                                                                                                                                                                               |  |  |  |  |

| IFC_CFG[2:0]               | I          | This signal selects coprocessor interface type: 000: ZBT pipelined mode 001: ZBT flowthrough mode 010: SyncBurst pipelined mode (early Write) 011: SyncBurst pipelined mode (late Write) 100-111: Reserved.                                                                                                                                                      |  |  |  |  |

## Note:

Document #: 38-02043 Rev. \*B Page 9 of 42

<sup>3.</sup> Detailed information on the external transceiver is given in "Information on External Transceivers" on page 29.

Table 4-1. Search Coprocessor Pin Description (continued)

| Parameter     | Туре | Description                      |  |  |  |

|---------------|------|----------------------------------|--|--|--|

| Test Access F | Port |                                  |  |  |  |

| TDI           | I    | IEEE 1149 JTAG test data in.     |  |  |  |

| TCK           | I    | IEEE 1149 JTAG test clock.       |  |  |  |

| TDO           | Т    | IEEE 1149 JTAG test data out.    |  |  |  |

| TMS           | I    | IEEE 1149 JTAG test mode select. |  |  |  |

| TRST_L        | I    | IEEE 1149 JTAG reset.            |  |  |  |

Document #: 38-02043 Rev. \*B Page 10 of 42

Page 11 of 42

## 5.0 Clocks

The CYNPC80192 receives up to a 100-MHz master CLK at the coprocessor interface. The CYNPC80192 then generates the CLK2X and a phase signal PHS\_L for the NSEs, and the SCLK for the associative data SSRAMs, as shown in *Figure 5-1*.

Figure 5-1. NDC Clocks

Downloaded from Elcodis.com electronic components distributor

#### 6.0 Registers

#### 6.1 Coprocessor Interface Register

The network processor(s) access the NDC using the coprocessor (SSRAM) interface. The NDC has a CFG and status registers area and an operating registers area, as shown in Table 6-1.

Table 6-1. Register Partitions for Coprocessor Access

| Address                | Abbreviation                | Туре | Description                                                                                                                                                                                                                               |

|------------------------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–511                  | CFG and Status<br>Registers |      | These registers are for configuring the NDC (Read/Write), reporting the error code in the status register (Read-only), setting up the mask register for asserting INTR (Read/Write), and obtaining information on the device (Read-only). |

| 512–1023<br>ADR[9] = 1 | Operating Registers         |      | Dynamic access for searches and table management happens through this area of the coprocessor address space. [4]                                                                                                                          |

The CFG area shown in *Table 6-2* is used for programming the NDC via a 64-bit CFG register.<sup>[5]</sup>

Table 6-2. Configuration and Status Registers Area

| Address | Configuration and Status Registers Area |

|---------|-----------------------------------------|

| 0–1     | CFG Register                            |

| 2–3     | Error, Status Registers (Read-only)     |

| 4–5     | Mask Registers                          |

| 6–7     | Reserved                                |

| 8–9     | Information Registers (Read-only)       |

| 10–511  | Reserved                                |

#### 6.2 **Configuration and Status Registers**

#### 6.2.1 Configuration Register

The 64-bit CFG register contains the following fields, as shown in Table 6-3.

Table 6-3. Configuration Register

|     | Configuration Register [63:0] |                                    |                                       |               |                  |       |      |      |      |

|-----|-------------------------------|------------------------------------|---------------------------------------|---------------|------------------|-------|------|------|------|

| ADR | 63–12                         | 11                                 | 10                                    | 9             | 8                | 7–6   | 5–3  | 2–1  | 0    |

| 0–1 | Reserved                      | External<br>Transceiver<br>Present | Search Result<br>Bit in Data<br>Field | INTR_Polarity | SSRAM<br>Present | CPCFG | HLAT | TLSZ | SRST |

SRST. This active high bit resets the state of the device. The reset bit will be active for 32 CLK cycles and will be automatically cleared after the reset has taken effect.

Table Size (TLSZ). This determines the NSE CFG for the specific table size. [6]

Latency of Hit Signals (HLAT). This determines the data access latency of associated data SSRAM.<sup>[7]</sup>

CPCFG. This field sets the width of the processor and context IDs that will be driven on the CPID bus after the completion of the operation. The contents of the CPID bus are generated by concatenating LSBs of the processor ID and the LSBs of the context ID.

- 00: CPID[7:0] = {processor ID[2:0], context ID[4:0]}.

- 01: CPID[7:0] = {processor ID[3:0], context ID[3:0]}.

- 10: CPID[7:0] = {processor ID[4:0], context ID[2:0]}.

- 11: Reserved.

#### Notes:

- The resulting registers of the context descriptors are Read-only.

Once the NDC is configured, the network processors will use the operating registers area to configure the NSEs, initialize and manage the protocol layer tables, and perform searches through such tables.

- Though the NDC does not program the NSE with this information, the coprocessor uses it to determine the duration of operations such as Search and Learn.

- (More details on this field can be found in the data sheets for CYNSE70XXX NSEs.)

Though the NDC does not program the NSE with this information, the coprocessor uses it to determine the duration of operations such as Search and Read from the SSRAMs. (More details on this field can be found in the data sheet on CYNSE70XXX NSEs.)

Document #: 38-02043 Rev. \*B Page 12 of 42

**SSRAM Present**. This field informs the coprocessor whether the associative data SSRAM is connected to the NSE (bit is set to 1; see *Figure 13-1*) or connected to the network processor SRAM interface (bit is set to 0; see *Figure 13-2*).

**INTR\_Polarity**. This bit controls the polarity of the INTR/INTR\_L signal. When this signal is high, the INTR/INTR\_L signal is active high. When this signal is low, the INTR/INTR\_L signal is active low.

**Search Result Bit in Data Field.** If this bit is set to 1, the Hit or Miss information will be attached to the associative data field in bit 63. This bit has significance only when associative SSRAM is present (see Result Register 1 for the Search command). This bit does not replace the hit bit located in Result Register 0.

External Transceiver Present. If an external transceiver is used to drive several NSE devices, this bit should be set to 1.

#### 6.2.2 Error and Status Register

The error and status register is 64 bits wide. *Table 6-4* shows the bit positions of the error status register. The errors shown in *Table 6-5* will be detected by the NDC and the corresponding error bit will be set in the error and status register. Once it is Read, the error and status register will be cleared.

**Error Bits**. The error bits field holds the type of error. In the case of multiple errors, multiple error bits may be set. The context descriptor index will contain the index where the last error occurred. When an error occurs, the error bit is set along with the done bit in Result Register 0. The class and type of error (soft error [SE] or hard error [HE]) are indicated in the error and status register. When an error occurs, the INTR signal is asserted and a corresponding error bit is set along with the context descriptor index to identify the erroneous command. The interrupt signal is programmable as active low or active high depending upon the system requirement. See the description of the CFG register for further detail.

Table 6-4. Error and Status Register

| 63–32    | 31 | 30 | 29      | 28        | 27         | 26–13    | 12–8               | 7–0        |

|----------|----|----|---------|-----------|------------|----------|--------------------|------------|

| Reserved | HE | SE | SE_FULL | DESC_FULL | DESC_AFULL | Reserved | Context Desc Index | Error Bits |

Table 6-5. Error Codes

| Error Bit | Error Description                                                               |  |  |  |

|-----------|---------------------------------------------------------------------------------|--|--|--|

| 0         | Invalid Command (SE)                                                            |  |  |  |

| 1         | Reserved                                                                        |  |  |  |

| 2         | Reserved                                                                        |  |  |  |

| 3         | earch or Learn size invalid (i.e., 11 in search size field is not allowed) (SE) |  |  |  |

| 4         | NSE access time out (HE)                                                        |  |  |  |

| 5         | Reserved                                                                        |  |  |  |

| 6         | Reserved                                                                        |  |  |  |

| 7         | Reserved                                                                        |  |  |  |

Context Descriptor Index. This field identifies the context descriptor that caused the last error condition. In the case of multiple errors, this field will be overwritten.

**DESC\_AFULL**. This bit indicates that the descriptor array is almost full. When this flag is set, the processor(s) can send only two more commands to the descriptors. The DESC\_AF flag will be cleared if more that two descriptors are available.

**DESC\_FULL**. This bit indicates that the descriptor array is full. When this flag is set, the processor can send no commands to the descriptor. The DESC\_FULL flag is cleared upon Reading the status register.

**SE FULL**.<sup>[8]</sup> This bit indicates that the table in the NSE is full.

SE. The SE bit indicates that the error is recoverable and that the command has to be reissued.

**HE**. The HE bit indicates that the error is not recoverable, and that the coprocessor has to be reset and reinitialized by the software before further operations are attempted.

#### 6.2.3 Mask Register

The mask register is 64 bits wide. The bits in this field can be used to mask the INTR generated by any of the bits set in the error and status register. Setting the bits in this register causes the interrupt to be masked. The default value in the mask register is FFFFFFFF (lower 32 bits only).

#### Note

8. SE\_FULL may be altered as a result of executing a Learn or Write command by the NSE. This flag will be cleared upon reading the status register.

Document #: 38-02043 Rev. \*B Page 13 of 42

## 6.2.4 Information Register

The information register is 64 bits wide. *Table 6-6* describes the lower-order 32 bits in the information register. It uses ADRs 8 and 9 of the CFG register area.

Table 6-6. Information Register Description

| ADR | Field          | Range   | Initial Value           | Description                                                                                                                                    |

|-----|----------------|---------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | Revision       | [3:0]   | 0001                    | <b>Revision Number.</b> This is the current device revision number. Numbers start at one and increment by one for each revision of the device. |

|     | Implementation | [6:4]   | 001                     | This is the CYNPC80192 implementation number.                                                                                                  |

|     |                | 7       | 0                       | Reserved.                                                                                                                                      |

|     | Device ID      | [15:8]  | 00000011                | Product code for CYNPC80192.                                                                                                                   |

|     | MFID           | [31:16] | 1101_1100_<br>0111_1111 | <b>Manufacturer ID</b> . This field is the same as the manufacturer ID used in the TAP controller.                                             |

| 9   | _              | [63:32] | _                       | Reserved.                                                                                                                                      |

Document #: 38-02043 Rev. \*B Page 14 of 42

## 7.0 Operating Registers

There are 512 uniquely addressable 32-bit-wide registers (see *Table 7-1*). These 512 registers are divided into 32 descriptors and are called context descriptors (or "context"). Each context comprises 16 registers (i.e.,  $32 \times 16 = 512$ ). Each of these contexts is used for storing commands, data, and responses (returned results from NSEs). These 32 contexts provide a 32-deep pipeline for the network processor(s) system. The allocation of contexts between the multiple processors (or one processor running multiple processors) can be done by the network processor system. For example, a network processor system having four processing elements can assign eight contexts for each processor.

## 7.1 Address Mapping

Table 7-1. Operating Registers Addressing Mapping (ADR[9] = 1)

| ADR[8:0] | Contents   |

|----------|------------|

| 0–15     | Context 0  |

| 16–31    | Context 1  |

| 32–47    | Context 2  |

| 48–63    | Context 3  |

| 64–79    | Context 4  |

| 80–95    | Context 5  |

| 96–111   | Context 6  |

| 112–127  | Context 7  |

| 128–143  | Context 8  |

| 144–159  | Context 9  |

| 160–175  | Context 10 |

| 176–191  | Context 11 |

| 192–207  | Context 12 |

| 208–223  | Context 13 |

| 223–239  | Context 14 |

| 240–255  | Context 15 |

| 256–271  | Context 16 |

| 272–287  | Context 17 |

| 288–303  | Context 18 |

| 304–319  | Context 19 |

| 320–335  | Context 20 |

| 336–351  | Context 21 |

| 352–367  | Context 22 |

| 368–383  | Context 23 |

| 384–399  | Context 24 |

| 400–415  | Context 25 |

| 416–431  | Context 26 |

| 432–447  | Context 27 |

| 448–463  | Context 28 |

| 464–479  | Context 29 |

| 480–495  | Context 30 |

| 496–511  | Context 31 |

Document #: 38-02043 Rev. \*B Page 15 of 42

#### 7.2 Context Descriptor Organization

Table 7-2 shows the organization of the context descriptor. During normal operation, the network processor Writes in the context descriptor block (addresses 0–9 within the block) with the command and the appropriate data and Reads the results from the context descriptor block (addresses 12–15 within the block). **Note**. In 64-bit bus mode, the even and the next odd location are accessed in the same cycle, and ADR[0] is ignored.

Table 7-2. Context Descriptor Organization

| ADR   | Context Descriptor Organization | Access |

|-------|---------------------------------|--------|

| 0–1   | Command Descriptor              | R/W    |

| 2–3   | Data 0                          | R/W    |

| 4–5   | Data 1                          | R/W    |

| 6–7   | Data 2                          | R/W    |

| 8–9   | Data 3                          | R/W    |

| 10–11 | Reserved                        | _      |

| 12–13 | Result Register 0               | R      |

| 14–15 | Result Register 1 F             |        |

Depending on the type of command, the network processor may only need to Write to selected locations of Data 0–3, and may only need to Read from selected locations of Result Register 0 or 1. **Note**. Addresses 0–9 are Read/Write and addresses 12–15 are Read-only locations.

## 7.3 Context Descriptor Commands

This 64-bit word (eight bytes) describes the command to the coprocessor. The contents of each of these eight bytes and a description of each of these fields are described below in *Table 7-3*.

Table 7-3. Descriptor Command

| Bit Positions |                                                                           | Field Description               |                  |        |                                      |              |               |       |

|---------------|---------------------------------------------------------------------------|---------------------------------|------------------|--------|--------------------------------------|--------------|---------------|-------|

|               | 7                                                                         | 6                               | 5                | 4      | 3                                    | 2            | 1             | 0     |

| 63–56         | Reserved                                                                  |                                 |                  |        |                                      | Context ID   |               | •     |

| 55–48         | Reserved                                                                  |                                 |                  |        |                                      | Processor ID | )             |       |

| 47–40         | Reserved                                                                  | d Search Successful Register Ir |                  |        | Reserved                             | Glo          | bal Mask Ind  | dex   |

| 39–32         | Reserved                                                                  | SS                              | RAM Address Pref | ix     | (                                    | Comparand F  | Register Inde | X     |

| 31–24         | Rese                                                                      | erved                           | Direct/Indirect  | Access | Location                             | Searc        | h Size        | Start |

| 23–16         | Layer Attribute/Valid Bit for Data 3 Layer Attribute/Valid Bit for Data 2 |                                 |                  |        |                                      | ata 2        |               |       |

| 15–8          | Layer Attribute/Valid Bit for Data 1                                      |                                 |                  |        | Layer Attribute/Valid Bit for Data 0 |              |               |       |

| 7–0           |                                                                           |                                 |                  | Commai | nd                                   |              |               |       |

Context ID. This field contains the context ID that a network processor has assigned to this specific context.

Processor ID. This field contains the ID number of the network processor that wrote the descriptor.

**Global Mask Index**. This field is used only for Search, Write, Move, and Swap commands to the NSE(s). This field selects one of the eight global mask register (GMR) pairs from the NSE bank for Search, Write, Move and Swap commands. In the case of a 272-bit search, two pairs of GMRs are used. These two pairs include one that is specified in the command and other is a subsequent pair. For example, if the GMR pair 7 is specified, the GMR pair 0 will be used as the subsequent pair for 272-bit-wide searches.

**Search Successful Register Index**. The search successful register (SSR) index field is used only for Search and Write operations to the NSEs. Up to eight search successful indexes are stored in each of the NSEs. This field selects one of those eight registers for the Search and indirect Write operations to the NSEs. (Refer to the data sheet specifications of the CYNSE70XXX devices for further information.)

Comparand Register Index. This field is used only for Search and Learn operations. This field specifies the comparand register in each of the NSEs that will store the comparands (as they are searched). A subsequent Learn instruction can insert the stored comparands in a table residing in the NSE(s). (Refer to the data sheet specifications of CYNSE70XXX devices for further information.)

Document #: 38-02043 Rev. \*B Page 16 of 42

**SSRAM Address Prefix**. In the implementation with a SSRAM connected to the NSE (see *Figure 13-1*), these three bits are used as an SSRAM address prefix (SAP) to generate the address of the associative SSRAM. (Refer to the data sheet specifications of the CYNSE70XXX devices for further information.)

**Start**. When the command and associated parameters have been written to the command descriptor, a process running on the network processor can set this bit to initiate the operation by the CYNPC80192.

**Search Size**. This two-bit field is used only by Search and Learn instructions and describes the word size for these operations. **Note**. Learn command is not supported in the 272-bit wide table. The following describes the data that will be presented to the NSE for various search sizes.

000: x68 ({Data 0, layer attribute/valid bit for Data 0})

001: x136 ({Data 1, layer attribute/valid bit for Data 1; Data 0, layer attribute/valid bit for Data 0})

010: x272 ({Data 3, layer attribute/valid bit for Data 3; Data 2, layer attribute/valid bit for Data 2;

Data 1, layer attribute/valid bit for Data 1; Data 0, layer attribute/valid bit for Data 0}.

Note. The two-bit search size must contain 00 for non-Search/Learn instructions.

**Access Location**. This two-bit field is used by Read, Write, Move, and Swap instructions, and indicates the region accessed in the NSEs or the associative data SSRAMs.

000: NSE data array.

001: NSE mask array.

010: SRAM connected to the NSE.

011: NSE internal registers.

**Direct/Indirect**. This one-bit field is used by Read and Write instructions and controls the address generation to the NSEs and the associated data SSRAMs. When this bit is set, it specifies indirect addressing using SSRs in the NSEs. (Refer to the specifications of CYNSE70XXX for further information.)

Layer Attribute and Valid Bit for Data 0. This field contains the three-bit layer attribute as well as a valid bit to accompany data in the Data 0, in the context descriptor. The layer attributes bits may be used for maintaining multiple search tables (of different widths) in the NSE(s). However, if multiple search tables are not used, these bits can be used for any purpose.

Layer Attribute and Valid Bit for Data 1. This field contains a three-bit layer attribute as well as a valid bit to accompany data in the Data 1, in the context descriptor. The layer attributes bits may be used for maintaining multiple search tables (of different widths) in the NSE(s). However, if multiple search tables are not used, these bits can be used for any purpose.

Layer Attribute and Valid Bit for Data 2. This field contains the three-bit layer attribute as well as a valid bit to accompany data in the Data 2, in the context descriptor. The layer attributes bits may be used for maintaining multiple search tables (of different widths) in the NSE(s). However, if multiple search tables are not used, these bits can be used for any purpose.

Layer Attribute and Valid Bit for Data 3. This field contains the three-bit layer attribute as well as valid bit to accompany data in the Data 3, in the context descriptor. The layer attributes bits may be used for maintaining multiple search tables (of different widths) in the NSE(s). However, if multiple search tables are not used, these bits can be used for any purpose.

**Commands**. NDC currently supports six basic commands. Command bits 7 through 3 are reserved and must be programmed as 0s for the following commands:

000: Read

001: Write

010: Search

011: Learn

100: Move

101: Swap.

#### 7.3.1 Command Description and Parameters

**Read Command (00 H).** Table 7-4 shows the format for the Read command. The Read command's structure is rd(ADR). The Read command uses two 64-bit words in the context descriptor, command descriptor word, and Data 0 word. The Read command is issued through the command descriptor. The Read access location, either data array, mask array, NSE register, or external SSRAM is encoded in the command descriptor word. Bits 15–0 of the Data 0 word contain the Read address. Bits 23–19 of the Data 0 word supply the NSE ID (SEID).

Document #: 38-02043 Rev. \*B Page 17 of 42

Result Registers 0 and 1 return the result of the Read operation in two 64-bit words.

Table 7-4. Read Command

| Address | 63–24    | 23–19 | 18–16    | 15–0            |

|---------|----------|-------|----------|-----------------|

| Data 0  | Reserved | SEID  | Reserved | Address Pointer |

Write Command (01 H). Table 7-5 shows the format for the Write command. The Write command's structure is wr(ADR, dt). The Write command uses three 64-bit words in the context descriptor: command word, Data 0 word and Data 1 word. The Write command is issued through the command descriptor. The Write access location could be either the data array, mask array, NSE register or associative SSRAM connected to the NSE. Bits 15–0 of the Data 0 word contain the Write address. Bits 23–19 of the Data 0 supply the SEID. The Data 1 word contains the data bits [67:4], while the data bits [3:0] (called layer bits for Data 1) are passed in the command descriptor word.

Table 7-5. Write Command

| Address | 63–24        | 23–19 | 18–16    | 15–0            |  |

|---------|--------------|-------|----------|-----------------|--|

| Data 0  | Reserved     | SEID  | Reserved | Address Pointer |  |

| Data 1  | Data [67: 4] |       |          |                 |  |

**Search Command (02H)**. The Search command's structure is se(dt0) for 68-bit word, se(dt0,dt1) for 136-bit word and se(dt0,dt1,dt2,dt3) for 272-bit word. The Search command uses two, three, or five 64-bit words in the context descriptor depending upon the size of the search entry (68-bit, 136-bit, or 272-bit). The search size is encoded in the command word, bits [26:25]. Data bits [3:0] for each 68-bit NSE word are stored in the command word in layer attribute bits for Data 0 through Data 3. The number of layer attribute bits used in the command word depends upon the search size. Thus, for a 68-bit search the descriptor command bits [11:8] will be used; for a 136-bit search, bits [15:8] will be used and for a 272-bit search, bits [23:8] will be used. The indices for SSR, GMR, and comparand register are stored in the command word also. (For further explanation of these indices, refer to data sheets for the CYNSE70XXX NSEs.)

Successive search operations are pipelined. For a 64-bit network processor interface running at 100 MHz, the NDC can sustain 33 Msps for tables configured as ×68 bit in the NSEs. For ×136-bit CFG, the performance will be 25 Msps, and for ×272-bit CFG, the peak performance will be 16.67 Msps. For a 32-bit network processor Interface, the peak performance will drop by a factor of one half compared to the performance of the 64-bit interface.

## 7.3.2 Context Descriptor Data 0-Data 3

For the Search command these words contain the search key that will be presented to the NSEs. *Table 7-6* shows the meaningful fields for each search size that are driven on the NSE bus DQ from the descriptors. The data driven on the DQ[3:0] for various searches is picked from the command word as follows.

68-bit search: layer attribute and valid bits for Data 0.

136-bit search: layer attribute and valid bits for Data 0 and Data 1.

272-bit search: layer attribute and valid bits for Data 0, Data 1, Data 2, and Data 3.

Table 7-6. Search Data

| Search Size | Meaningful Data (64 bits each)                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 00          | Data 0 —> DQ[67:4] (Cycle A and B)                                                                                    |

| 01          | Data 0 —> DQ[67:4] (Cycle A), Data 1 —> DQ[67:4] (Cycle B)                                                            |

| 10          | Data 0 —> DQ[67:4] (Cycle A), Data 1 —> DQ[67:4] (Cycle B) Data 2 —> DQ[67:4] (Cycle C), Data 3 —> DQ[67:4] (Cycle D) |

| 11          | Reserved                                                                                                              |

Result Registers 0 and 1 return the result of the search operation.

**Learn Command (03H)**. The Learn command's structure is le(indx). The Learn command will use two 64-bit words (command descriptor word and Data 0) in the context descriptor. The command includes an index for a Comparand register of the NSE, where the data to be Learnt was stored by a prior search instruction. Data 0 contains the data to be written in associative SRAM. Learn will result in error if the Learn is performed when the NSE SE\_FULL is high. The error bit in the result register will indicate the error. The Learn error will be set in the error and status register.

**Move Command (04 H)**. The Move command's structure is mv(addr1, addr2, len). The Move command utilizes two 64-bit words in the context descriptor: command descriptor word, and Data 0 word. Bits 15–0 of the Data 0 word will contain the source address; bits 23–19 will contain the SEID; bits 39–24 will contain the destination address, bits 47–43 will contain the destination SEID; and bits 56–48 will contain the move block length (see *Table 7-7*). Current implementation restricts the maximum move block length to 256 words (of 68-bit each) in between/within the NSE(s). The minimum length for the Move command is four locations.

Document #: 38-02043 Rev. \*B Page 18 of 42

**Table 7-7. Move Command Parameters**

| ADF  | 63–57      | 56–48       | 47–43               | 42–40    | 39–24                          | 23–19       | 18–16    | 15–0                      |

|------|------------|-------------|---------------------|----------|--------------------------------|-------------|----------|---------------------------|

| Data | 0 Reserved | Move Length | Destination<br>SEID | Reserved | Destination<br>Address Pointer | Source SEID | Reserved | Source Address<br>Pointer |

For Move instruction, Data 0 is used to pass the source address pointer and SEID, destination address pointer and the SEID, and the number of x68 entries to be moved move/swap length.

The NDC implements the Move instruction as Burst Read and then a Burst Write into the NSEs.

**Swap Command (05H)**. The Swap command's structure is sw(addr1, addr2, len). The Swap command will use two 64-bit words in the context descriptor: command word, and Data 0 word. Bits 15–0 of the Data 0 word will contain the first address; bits 23–19 will contain the first SEID; bits 39–24 will contain the second address, bits 47–43 will contain the second SEID; and bits 56–48 will contain the Swap block length (see *Table 7-8*). The maximum Swap block length is 128 words (of 68-bit each) in the NSE. The minimum length for Swap is four locations.

**Table 7-8. Swap Command Parameters**

| ADR    | 63–7     | 56–48       | 47–43          | 42–40    | 39–24                     | 23–19      | 18–16    | 15–0                     |

|--------|----------|-------------|----------------|----------|---------------------------|------------|----------|--------------------------|

| Data 0 | Reserved | Swap Length | Second<br>SEID | Reserved | Second Address<br>Pointer | First SEID | Reserved | First Address<br>Pointer |

For Swap instruction, Data 0 is used to pass the first address pointer and SEID, the second address pointer and SEID, and the number of x68 entries to be swapped. The NDC implements the Swap instruction as two burst Reads and then two burst Writes into the NSEs. **Note**. The Move and Swap commands will not work across the NSE boundaries if several NSEs are cascaded.

#### 7.3.3 SSRAM Read/Write

For SSRAM (connected to the NSE) Read or Write operations, Data 0 is used to pass the SSRAM address and SEID. Data 1 is used for passing the data for a Write operation. *Table 7-9* shows the format for Data 0 and Data 1 for accessing the SSRAM.

Table 7-9. SSRAM Data

| ADR    | 63–24      | 23–19 | 18–16    | 15–0          |  |

|--------|------------|-------|----------|---------------|--|

| Data 0 | Reserved   | SEID  | Reserved | Address[15:0] |  |

| Data 1 | Data[63:0] |       |          |               |  |

For NSE Read and Write operations, the Data 0 is used to pass address and SEID. Data 1 is used for passing data for Write operations. This 64-bit Data 1 field holds data[67:4] for the NSE, while data[3:0] is held in the layer attribute and valid bits field of the command descriptor word. The NSE operation can be on the array, mask array, or the command registers. *Table 7-10* shows the format for Data 0 and Data 1 for accessing the NSE data, mask, and register locations.

Table 7-10. NSE Data, Mask, and Register Locations

| ADR    | 63–24      | 23–19 | 18–16    | 15–0          |  |  |

|--------|------------|-------|----------|---------------|--|--|

| Data 0 | Reserved   | SEID  | Reserved | Address[15:0] |  |  |

| Data 1 | Data[67:4] |       |          |               |  |  |

#### 7.3.4 Result Register 0 and 1 for Read Operation

These two registers return the result of the Read operation in two 64-bit words. Result Register 0 contains the four least significant bits of data (layer attribute/valid bits) and the status of Read operation along with the processor and context ID. This is shown in *Table 7-11*.

Table 7-11. Read Response at Result Register 0

| Bit Positions | Associative Data SSRAM Connected to Coprocessor Bus |          |   |   |   |                |     |   |

|---------------|-----------------------------------------------------|----------|---|---|---|----------------|-----|---|

|               | 7                                                   | 6        | 5 | 4 | 3 | 2              | 1   | 0 |

| 63–56         |                                                     | Reserved |   |   |   |                |     |   |

| 55–48         | Reserved                                            |          |   |   |   |                |     |   |

| 47–40         |                                                     | Reserved |   |   |   |                |     |   |

| 39–32         | Reserved                                            |          |   |   |   | Processor ID[4 | :0] |   |

| 31–24         | Done Reserved                                       |          |   |   |   | Context ID [4: | 0]  |   |

Document #: 38-02043 Rev. \*B Page 19 of 42

Table 7-11. Read Response at Result Register 0 (continued)

| Bit Positions | Associative Data SSRAM Connected to Coprocessor Bus |              |  |  |  |

|---------------|-----------------------------------------------------|--------------|--|--|--|

| 23–16         | Reserved                                            |              |  |  |  |

| 15–8          | Rese                                                | Reserved     |  |  |  |

| 7–0           | Reserved                                            | SE Data[3:0] |  |  |  |

Processor ID[4:0]. The processor ID from the command descriptor is identified here.

Context ID[4:0]. The context ID from the command descriptor is identified here.

**Done**. This field indicates that the Read operation is complete. When the done bit is set, the next command can be written in the descriptor. The done bit is cleared when the Result Register 0 is Read by the network processor.

**SE Data[3:0]**. This field contains the least four significant bits (layer attribute/valid bits) Read from the NSE 68-bit word. (This field is valid only when Reads are done from the NSE.)

Result Register 1 contains the SE Data[67:4] Read from the NSE (*Table 7-12*) or Data[63:0] Read from the SSRAM connected to the NSE (*Table 7-13*).

#### Table 7-12. Data Read from NSE

| ADR      | 63–0          |

|----------|---------------|

| Result 1 | SE Data[67:4] |

#### Table 7-13. Data Read from SSRAM

| ADR      | 63–0             |

|----------|------------------|

| Result 1 | SSRAM Data[63:0] |

#### 7.3.5 Result Register 0 and 1 for Write/Move/Swap/Learn Operations

Only Result Register 0 carries meaningful data, as is shown in Table 7-14 below.

Table 7-14. Write/Move/Swap/Learn Results Register 0

| Bit Positions |          | Associative Data SSRAM Connected to Coprocessor Bus |          |          |   |          |   |   |

|---------------|----------|-----------------------------------------------------|----------|----------|---|----------|---|---|

|               | 7        | 6                                                   | 5        | 4        | 3 | 2        | 1 | 0 |

| 63–56         |          | •                                                   |          | Reserved | d | •        |   |   |

| 55–48         |          |                                                     |          | Reserved | d |          |   |   |

| 47–40         |          | Reserved                                            |          |          |   |          |   |   |

| 39–32         |          | Reserved                                            |          |          |   | Reserved |   |   |

| 31–24         | Done     | Reserved                                            | Reserved |          |   | Reserved |   |   |

| 23–16         |          | Reserved                                            |          |          |   |          |   |   |

| 15–8          | Reserved |                                                     |          |          |   |          |   |   |

| 7–0           |          |                                                     |          | Reserved | d |          |   |   |

**Done**. This field indicates that the command has been processed. When the done bit is set, the next command can be written in the descriptor. The done bit is cleared when the Result Register 0 is Read by the network processor.

Result Register 1 is not used for Write/Move/Swap/Learn commands.

## 7.3.6 Result Register 0 and 1 for Search Operation (Case 1)

For the search operation where an SSRAM is connected to the NSE (Figure 7), the Result Register 0 carries search status, processor ID and context ID and is shown in *Table 7-15*. The associative data is returned in Result Register 1 if the search succeeded, as shown in *Table 7-16*. In addition, if the search result in data field bit in the CFG register is set, then bit[63] of Result Register 1 indicates a search success (bit[63] = 1) or search failure (bit[63] = 0). In this case bits 62–0 contain the 63-bit associative data from the SSRAM, as is shown in *Table 7-17*.

Document #: 38-02043 Rev. \*B Page 20 of 42

Table 7-15. Result Register 0 for Search Operation

| Bit Positions | SE Data/Mask Array access Results |          |          |      |      |                |      |   |

|---------------|-----------------------------------|----------|----------|------|------|----------------|------|---|

|               | 7                                 | 6        | 5        | 4    | 3    | 2              | 1    | 0 |

| 63–56         |                                   |          |          | Rese | rved |                |      |   |

| 55–48         |                                   |          |          | Rese | rved |                |      |   |

| 47–40         |                                   | Reserved |          |      |      |                |      |   |

| 39–32         |                                   | Reserved |          |      | Р    | rocessor ID [4 | 1:0] |   |

| 31–24         | Done                              | Hit      | Reserved |      | (    | Context ID [4: | 0]   |   |

| 23–16         |                                   | Reserved |          |      |      |                |      |   |

| 15–8          | Reserved                          |          |          |      |      |                |      |   |

| 7–0           |                                   |          |          | Rese | rved |                |      |   |

Processor ID[4:0]. The processor ID from the command descriptor is identified here.

Context ID[4:0]. The context ID from the command descriptor is identified here.

Hit. The hit flag indicates whether the search was successful.