## MICRF507

## 470MHz to 510MHz Low-Power FSK Transceiver with +10dBm Power Amplifier

RadioWire<sup>®</sup>

## **General Description**

The MICRF507 is a fully integrated FSK transceiver with +10dBm power amplifier and transmit/receive switch. The device is targeted at automated meter reading (AMR) applications in the China Short Range Device (SRD) frequency band of 470MHz to 510MHz. The device supports data rates up to 20kbps with PLL divider modulation and up to 200kbps with VCO modulation. The receiver achieves a sensitivity of -113dBm at a data rate of 2.4kbps while only consuming 12mA of supply current. The integrated power amplifier (PA) delivers +10dBm of output power while only consuming 21.5mA of supply current. Power down supply current is a low 0.2μA while retaining register information and a low 280μA in standby mode where only the crystal oscillator is enabled.

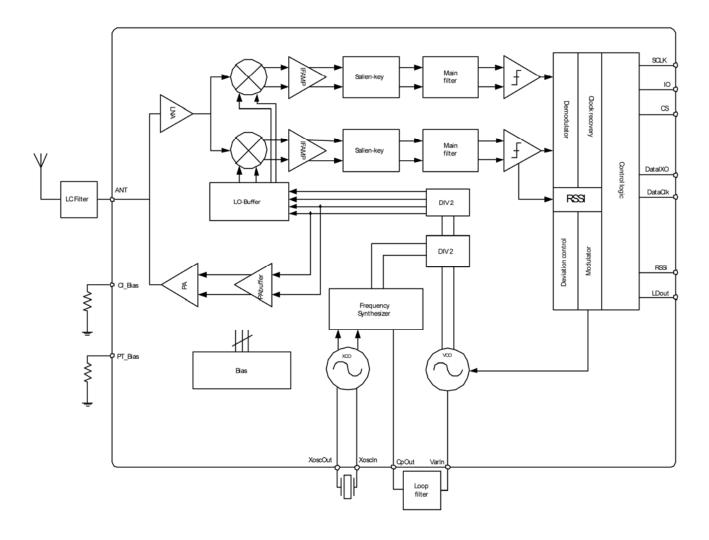

The receiver of the MICRF507 utilizes a Zero IF (ZIF) I/Q architecture, integrating a low-noise amplifier (LNA) with bypass mode, I/Q quadrature mixers, three-pole Sallen-Key IF channel pre-filters, and six-pole elliptic switched capacitor IF filters, providing excellent selectivity, adjacent channel rejection and blocking performance. FSK demodulation is implemented digitally and a synchronizer, when enabled, recovers the received bit clock. A receive signal strength indicator (RSSI) circuit indicates the received signal level over a 50dB range. An integrated Frequency Error Estimator (FEE) and crystal tuning capability allow fine tuning of the RF frequency.

The transmitter of the MICRF507 consists of an FSK modulator and power amplifier with output power adjustable from +10dBm to -3.5dBm in seven steps. Modulation can be achieved by applying two sets of PLL divider ratios or through direct VCO modulation by varying VCO tank capacitance.

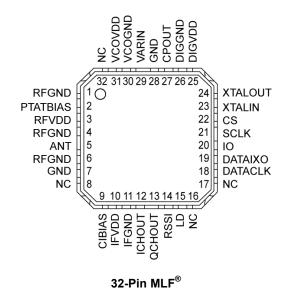

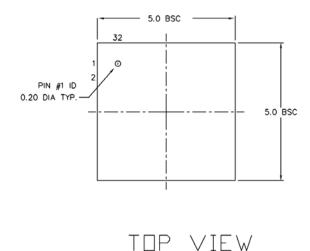

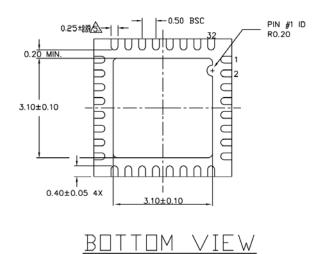

The MICRF507 requires a 2.0V to 2.5V supply voltage, operates over the -40°C to +85°C temperature range, and is available in a 32-pin MLF® package.

#### **Features**

- -113dBm sensitivity at 2.4kbps encoded bit rate

- +10dBm power amplifier with seven gain steps

- 12mA receive supply current

- 21.5mA transmit supply current at +10dBm

- 0.2µA power down current (registers retain settings)

- 280µA standby current (crystal oscillator enabled)

- Data rates up to 20kbps with PLL divider modulation

- Data rates up to 200kbps with VCO modulation

- Integrated transmit and receive (T/R) switch

- LNA with bypass mode

- Zero IF I/Q receiver architecture

- IF pre-amplifiers with DC-offset removal

- Three-pole Sallen-Key IF channel low-pass pre-filter

- · Six-pole elliptic switched capacitor IF low-pass filter

- 50kHz to 350kHz programmable baseband bandwidth

- 59dB blocking at ±1MHz offset

- 53dB adjacent channel rejection at ±500kHz offset

- FSK digital demodulator with clock recovery

- 50dB Received Signal Strength Indicator (RSSI)

- Frequency Error Estimator (FEE)

- Reference crystal tuning capability

- 2.0 to 2.5V supply voltage range

- -40°C to +85°C operating temperature range

- Available in 32-pin MLF<sup>®</sup> package (5.0mm x 5.0mm x 0.85mm)

## **Applications**

- China Short Range Device (SRD) Communications

- Automated Meter Reading (AMR)

- Advanced Metering Infrastructure (AMI)

- Wireless Remote Meter Reading

RadioWire is a registered trademark of Micrel, Inc. MLF is a registered trademark of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

| RadioWire® FSK Transceiver Selection Guide                         | 4  |

|--------------------------------------------------------------------|----|

| Ordering Information                                               | 4  |

| Block Diagram                                                      | 4  |

| Pin Configuration                                                  | 5  |

| Pin Description                                                    |    |

| Absolute Maximum Ratings <sup>(1)</sup>                            |    |

| Operating Ratings <sup>(2)</sup>                                   |    |

| Electrical Characteristics <sup>(4)</sup>                          |    |

| Functional Description                                             |    |

| Control (3-wire) Interface                                         |    |

| Reading                                                            |    |

| Control Interface Timing                                           |    |

| Power-on Reset                                                     |    |

| Clock Generation                                                   | 15 |

| Crystal Oscillator (XCO)                                           | 16 |

| BITSYNC CLK (Receiver Bit Synchronization Clock)                   | 17 |

| BITRATE_CLK (Transmitter Bit Rate Clock)                           |    |

| MODULATOR_CLK (VCO Modulator Clock)                                |    |

| Data Interface and Bit Synchronization                             |    |

| Sync_en = 0                                                        |    |

| Sync_en = 1                                                        |    |

| Additional Considerations in the Use of Synchronizer (Sync_en = 1) |    |

| Frequency Synthesizer                                              |    |

| VCOCharge Pump                                                     |    |

| PLL Filter                                                         |    |

| Lock Detect                                                        |    |

| Receiver                                                           |    |

| Front End                                                          |    |

| Sallen-Key Filters                                                 |    |

| Switched Capacitor Filter                                          |    |

| RSSI                                                               |    |

| FEE                                                                |    |

| XCOtune Procedure Example                                          | 27 |

| Transmitter                                                        | 28 |

| Power Amplifier                                                    |    |

| Frequency Modulation                                               |    |

| Divider Modulation                                                 |    |

| VCO Modulation and the Modulator                                   |    |

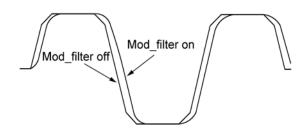

| Modulator Filter                                                   |    |

| System Modes and Initialization                                    |    |

| Start-up and Initialization                                        |    |

| Mode Transitions                                                   |    |

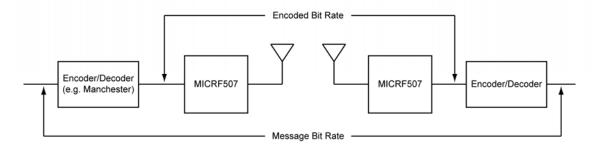

| Message Coding and Formatting                                      |    |

| DC Balanced Line Coding                                            |    |

| Message Formatting: Preamble                                       |    |

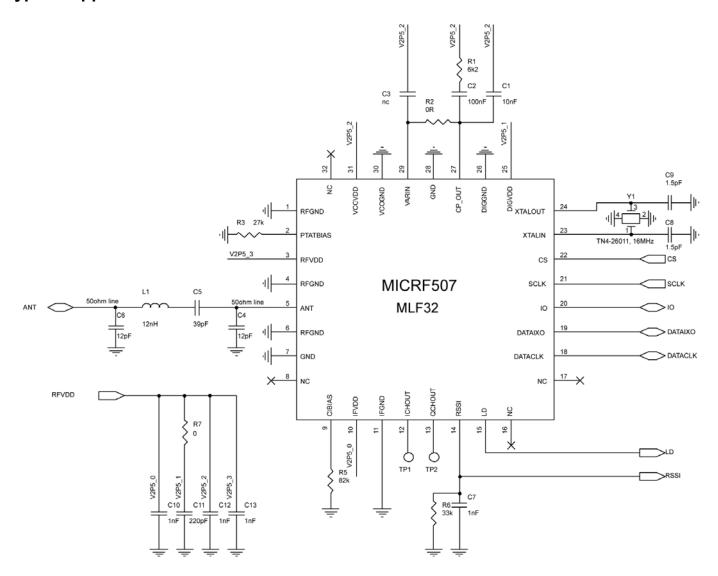

| Typical Application                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Typical Application  Bill of Materials  Layout Considerations  Layer Definition  Grounding.  RF Traces.  Supply Routing.  PLL Loop Filter | 36 |

| Layout Considerations                                                                                                                     | 37 |

| Layer Definition                                                                                                                          | 37 |

| Grounding                                                                                                                                 | 37 |

|                                                                                                                                           |    |

|                                                                                                                                           |    |

| PLL Loop Filter                                                                                                                           | 37 |

| Overview of Programming Bits                                                                                                              | 38 |

| Detailed Description of Programming Bits                                                                                                  | 39 |

| Package Information                                                                                                                       | 46 |

# RadioWire® FSK Transceiver Selection Guide

| Device    | Frequency Range  | Maximum<br>Data Rate | Receive Current | Supply Voltage | Transmit Current | Package |

|-----------|------------------|----------------------|-----------------|----------------|------------------|---------|

| MICRF505  | 850MHz to 950MHz | 200kbps              | 13.5mA          | 2.0 to 2.5V    | 28mA             | MLF-32  |

| MICRF505L | 850MHz to 950MHz | 200kbps              | 13.5mA          | 2.25 to 5.5V   | 28mA             | MLF-32  |

| MICRF506  | 410MHz to 450MHz | 200kbps              | 12mA            | 2.0 to 2.5V    | 21.5mA           | MLF-32  |

| MICRF507  | 470MHz to 510MHz | 200kbps              | 12mA            | 2.0 to 2.5V    | 21.5mA           | MLF-32  |

# **Ordering Information**

| Part Number    | Junction Temperature Range | Package             |

|----------------|----------------------------|---------------------|

| MICRF507YML TR | -40° to +85°C              | Pb-Free 32-Pin MLF® |

# **Block Diagram**

# **Pin Configuration**

## **Pin Description**

| Pin Number    | Pin Name | Type | Pin Function                                           |

|---------------|----------|------|--------------------------------------------------------|

| 1             | RFGND    |      | LNA and PA ground.                                     |

| 2             | PTATBIAS | 0    | Connection for bias resistor.                          |

| 3             | RFVDD    |      | LNA and PA power supply.                               |

| 4             | RFGND    |      | LNA and PA ground.                                     |

| 5             | ANT      | I/O  | Antenna Input/Output.                                  |

| 6             | RFGND    |      | LNA and PA ground.                                     |

| 7             | RFGND    |      | LNA and PA ground.                                     |

| 8, 16, 17, 32 | NC       |      | No connect. Leave these pins floating.                 |

| 9             | CIBIAS   | 0    | Connection for bias resistor.                          |

| 10            | IFVDD    |      | IF/mixer power supply.                                 |

| 11            | IFGND    |      | IF/mixer ground.                                       |

| 12            | ICHOUT   | 0    | Test pin.                                              |

| 13            | QCHOUT   | 0    | Test pin.                                              |

| 14            | RSSI     | 0    | Received signal strength indicator.                    |

| 15            | LD       | 0    | PLL lock indicator.                                    |

| 18            | DATACLK  | 0    | RX/TX data clock output.                               |

| 19            | DATAIXO  | I/O  | RX/TX data input/output.                               |

| 20            | Ю        | I/O  | 3-wire interface data in/output                        |

| 21            | SCLK     | I    | 3-wire interface serial clock.                         |

| 22            | CS       | I    | 3-wire interface chip select.                          |

| 23            | XTALIN   | I    | Crystal oscillator input.                              |

| 24            | XTALOUT  | I/O  | Crystal oscillator output or external reference input. |

| 25            | DIGVDD   |      | Digital power supply.                                  |

# Pin Description (continued)

| Pin Number | Pin Name          | Туре | Pin Function                     |

|------------|-------------------|------|----------------------------------|

| 26         | DIGGND            |      | Digital ground.                  |

| 27         | CPOUT             | 0    | PLL charge pump output.          |

| 28         | GND               |      | Substrate ground.                |

| 29         | VARIN             | I    | VCO varactor tune voltage input. |

| 30         | VCOGND            |      | VCO ground.                      |

| 31         | VCOVDD            |      | VCO power supply.                |

|            | Exposed<br>Paddle |      | Ground.                          |

## **Absolute Maximum Ratings**(1)

###

# Operating Ratings<sup>(2)</sup>

| Supply voltage (V <sub>IN</sub> )          | +2.0V to +2.5V   |

|--------------------------------------------|------------------|

| RF Frequencies                             | 470MHz to 510MHz |

| Encoded Bit Rate                           | 200kbps          |

| Ambient Temperature (T <sub>A</sub> )      | 40°C to +85°C    |

| Package Thermal Resistance                 |                  |

| 32-Pin MLF <sup>®</sup> (θ <sub>JA</sub> ) | 41.7°C/W         |

## **Electrical Characteristics**(4)

$f_{RF}$  = 490MHz,  $f_{XTAL}$  = 16MHz, MICRF507 Development Board, Modulation type = closed-loop VCO modulation, Sync\_en bit = 1,  $V_{DD}$  = 2.5V;  $T_A$  = 25°C, the term "bit rate" refers to encoded bit rate throughout the EC table (see Figure 24), **bold** values indicate -40°C $\leq T_A \leq +85$ °C, unless noted.

| Symbol          | Parameter                                          | Condition                               | Min | Тур  | Max | Units |

|-----------------|----------------------------------------------------|-----------------------------------------|-----|------|-----|-------|

| f <sub>RF</sub> | RF Frequency Operating Range                       |                                         | 470 |      | 510 | MHz   |

| $V_{DD}$        | Power Supply                                       |                                         |     | 2.5  |     | V     |

|                 | Power Down Current                                 |                                         |     | 0.2  | 3   | μΑ    |

|                 | Standby Current                                    |                                         |     | 280  |     | μΑ    |

| VCO and         | PLL Section                                        |                                         |     |      |     |       |

|                 | Reference Frequency                                |                                         | 4   |      | 40  | MHz   |

|                 | PLL Lock Time, 3kHz Bandwidth                      | 490MHz to 490.5MHz                      |     | 0.7  |     | ms    |

|                 |                                                    | 485MHz to 495MHz                        |     | 1.3  |     | ms    |

|                 | PLL Lock Time, 20kHz Bandwidth                     | 490MHz to 490.5MHz                      |     | 0.3  |     | ms    |

|                 | Switch Time, 3kHz Loop Bandwidth                   | Rx – Tx                                 |     | 1.0  |     |       |

|                 |                                                    | Tx – Rx                                 |     | 1.0  |     |       |

|                 |                                                    | Standby to Rx                           |     | 1.0  |     | ms    |

|                 |                                                    | Standby to Tx                           |     | 1.0  |     |       |

|                 | Crystal Oscillator Start-Up Time                   | With MICRF507 development board BOM     |     | 1.0  |     | ms    |

|                 | Charge Pump Current                                | V <sub>CPOUT</sub> = 1.1V, CP_HI = 0    | 100 | 125  | 170 | μA    |

|                 |                                                    | V <sub>CPOUT</sub> = 1.1V, CP_HI = 1    | 420 | 500  | 680 | μA    |

| Transmit        | t Section                                          |                                         |     |      |     |       |

| Pout            | Output Power                                       | R <sub>LOAD</sub> = 50Ω, PA[2:0] = 111  |     | 10   |     | dBm   |

|                 |                                                    | R <sub>LOAD</sub> = 50Ω, PA[2:0] = 001  |     | -3.5 |     | dBm   |

|                 | Output Power Variation Relative to                 | Over temperature range                  |     | ±1   |     | dB    |

|                 | $V_{DD} = 2.5V, T_A = 25^{\circ}C$                 | V <sub>DD</sub> = 2.0V                  |     | -2   |     | dB    |

|                 | Transmit Mode Current                              | R <sub>LOAD</sub> = 50Ω, PA[2:0] = 111  |     | 21.5 |     | mA    |

|                 | Consumption                                        | $R_{LOAD} = 50\Omega$ , $PA[2:0] = 001$ |     | 10.5 |     | mA    |

|                 |                                                    | $R_{LOAD} = 50\Omega$ , $PA[2:0] = 000$ |     | 8.0  |     | mA    |

|                 | Single-Sided Frequency<br>Deviation <sup>(5)</sup> |                                         | 10  |      | 250 | kHz   |

|                 | Maximum Bit Rate                                   | VCO modulation                          |     | 200  |     | kbps  |

|                 |                                                    | Divider modulation                      |     | 20   |     | kbps  |

# Electrical Characteristics<sup>(4)</sup> (Continued)

| Symbol  | Parameter                                                                                                                                           | Condition                                                   | Min | Тур  | Max | Units |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|------|-----|-------|

|         | Occupied Bandwidth <sup>(5)</sup>                                                                                                                   | 38.4kbps, β = 2, 20dBc                                      |     | 140  |     | kHz   |

|         |                                                                                                                                                     | 125kbps, β = 2, 20dBc                                       |     | 550  |     | kHz   |

|         |                                                                                                                                                     | 200kbps, β = 2, 20dBc                                       |     | 800  |     | kHz   |

|         | 2 <sup>nd</sup> Harmonic <sup>(5)</sup>                                                                                                             |                                                             |     | -43  | -36 | dBm   |

|         | 3 <sup>rd</sup> Harmonic <sup>(5)</sup>                                                                                                             |                                                             |     | -59  | -36 | dBm   |

|         | Spurious Emission in Restricted<br>Bands < 1GHz <sup>(5)</sup>                                                                                      |                                                             |     |      | -54 | dBm   |

|         | Spurious Emission < 1GHz <sup>(5)</sup>                                                                                                             |                                                             |     |      | -36 | dBm   |

|         | Spurious Emission > 1GHz <sup>(5)</sup>                                                                                                             |                                                             |     |      | -30 | dBm   |

| Receive | Section                                                                                                                                             |                                                             |     | •    | •   | 1     |

|         | Rx Current Consumption                                                                                                                              | All Functions on                                            |     | 12   |     |       |

|         |                                                                                                                                                     | LNA bypassed                                                |     | 10.3 |     |       |

|         | ]                                                                                                                                                   | Switch cap filter bypassed, LNA on                          |     | 9.8  |     | mA    |

|         |                                                                                                                                                     | Both switch cap filter and LNA bypassed                     |     | 8    |     |       |

|         | Rx Current Consumption Variation                                                                                                                    | Over temperature                                            |     | 2    |     | mA    |

|         |                                                                                                                                                     | 2.4kbps, β = 16                                             |     | -113 |     |       |

|         |                                                                                                                                                     | 4.8kbps, β = 16                                             |     | -111 |     | dBm   |

|         | Receiver Sensitivity (BER 10 <sup>-3</sup> )                                                                                                        | 19.2kbps, β = 4                                             |     | -107 |     |       |

|         |                                                                                                                                                     | 38.4kbps, β = 4                                             |     | -104 |     |       |

|         |                                                                                                                                                     | 76.8kbps, $\beta = 2$                                       |     | -101 |     |       |

|         |                                                                                                                                                     | 125kbps, β = 2                                              |     | -100 |     | -     |

|         |                                                                                                                                                     | 200kbps, β = 2                                              |     | -97  |     |       |

|         | Receiver Maximum Input Power                                                                                                                        | 125kbps, 125kHz deviation, LNA on                           |     | +7   |     |       |

|         |                                                                                                                                                     | 125kbps, 125kHz deviation, LNA bypassed                     |     | +12  |     | dBm   |

|         |                                                                                                                                                     | 20kbps, 40kHz deviation                                     |     | +2   |     |       |

|         | Receiver Sensitivity Tolerance                                                                                                                      | Over temperature                                            |     | 2    |     | dB    |

|         |                                                                                                                                                     | Over power supply range                                     |     | 1    |     | dB    |

|         | Receiver Baseband Bandwidth                                                                                                                         |                                                             | 50  |      | 350 | kHz   |

|         | Co-Channel Rejection, BER = 10 <sup>-3</sup>                                                                                                        | 19.2kbps, β = 6, PF_FC[1:0] = 01, f <sub>CUT</sub> = 133kHz |     | -8   |     | dB    |

|         | Adjacent Channel Rejection, both                                                                                                                    | ±500kHz spacing                                             |     | 53   |     | dB    |

|         | interferer and desired signal are modulated at 19.2 kbps encoded bit rate, $\beta$ = 6, PF_FC[1:0] = 01, $f_{CUT}$ = 133kHz, BER = 10 <sup>-3</sup> | ±1MHz spacing                                               |     | 58   |     | dB    |

|         | CW Blocking above desired                                                                                                                           | ±1MHz                                                       |     | 59   |     | dB    |

|         | signal, desired signal is modulated at 19.2kbps, $\beta$ = 6, 3dB above                                                                             | ±2MHz                                                       |     | 60   |     | dB    |

|         | sensitivity, PF FC[1:0] = 01,                                                                                                                       | ±5MHz                                                       |     | 47   |     | dB    |

|         | f <sub>CUT</sub> = 133kHz, BER = 10 <sup>-3</sup>                                                                                                   | ±10MHz                                                      |     | 60   |     | dB    |

# Electrical Characteristics<sup>(4)</sup> (Continued)

| Symbol           | Parameter                                   | Condition                    | Min                 | Тур   | Max                 | Units |

|------------------|---------------------------------------------|------------------------------|---------------------|-------|---------------------|-------|

| P <sub>1dB</sub> | 1dB Compression                             |                              |                     | -34   |                     | dBm   |

|                  | Input IP3                                   | 2 tones with 1MHz separation |                     | -25   |                     | dBm   |

|                  | LO Leakage                                  |                              |                     | -90   |                     | dBm   |

|                  | Spurious Emission <sup>(5)</sup>            | <1GHz                        |                     |       | -57                 | dBm   |

|                  |                                             | >1GHz                        |                     |       | -47                 | dBm   |

|                  | Input Impedance with no matching components |                              |                     | 33+7j |                     | Ω     |

|                  | RSSI Dynamic Range                          |                              |                     | 50    |                     | dB    |

|                  | D0010 12 1 D 22 2                           | P <sub>IN</sub> = -110dBm    |                     | 0.9   |                     | V     |

|                  | RSSI Output Range                           | P <sub>IN</sub> = -60dBm     |                     | 2     |                     | V     |

| Digital In       | puts/Outputs                                |                              | <b>,</b>            |       | •                   |       |

| V <sub>IH</sub>  | Logic Input High                            |                              | 0.7*V <sub>DD</sub> |       | V <sub>DD</sub>     | V     |

| V <sub>IL</sub>  | Logic Input Low                             |                              | 0                   |       | 0.3*V <sub>DD</sub> | V     |

|                  | Clock/Data Frequency <sup>(5)</sup>         |                              |                     |       | 10                  | MHz   |

|                  | Clock/Data Duty Cycle <sup>(5)</sup>        |                              | 45                  |       | 55                  | %     |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model; 1.5k in series with 100pF.

- 4. Specification for packaged product only.

- 5. Guaranteed by design.

## **Functional Description**

#### Control (3-wire) Interface

#### General

The MICRF507 operation is controlled through a set of 8-bit registers. The chip has a total of 23 readable registers (addresses 0-22) of which 22 (addresses 0-21) are writeable. Through this register set, the user can set the MICRF507 in transmit or receive mode, program the carrier frequency, and select a bit rate, among other options.

Table 1 identifies all register bits. Table 26 gives more detail and Table 27 shows the register fields grouped by category, with don't-care and mandatory bits omitted. Some bits shown as '0' or '1' are mandatory bits and must always be written with the values given. Other bits marked as "-" are "don't care" bits.

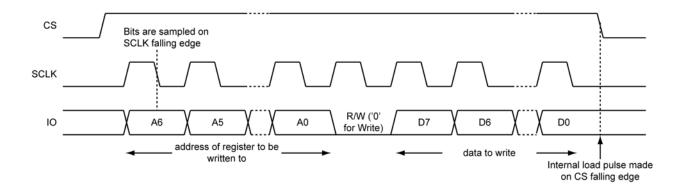

Registers are accessed serially through the control interface consisting of the CS, IO, and SCLK pins.

Positive-going pulses at SCLK serve to clock bits in and out of IO at a rate determined by the user. When IO is an input, falling edges of SCLK strobe each bit in; when IO is an output, each bit appears at IO after the rising edge of SCLK.

The IO is an input for entry of starting addresses, the R/W bit, and bytes being written to registers, and an output for bytes read from registers.

CS enables transactions at the control interface, active high. Transitions at the other two pins are ignored when CS is low. This allows the MICRF507 to share SCLK and IO with other devices as long as they have separate CS lines.

To start a transaction (with SCLK and CS initially low), bring CS high. To end a transaction (with SCLK low), bring CS low.

To write a bit into IO (when IO is an input); first bring SCLK high and drive IO with the bit level to be input (in either order, or simultaneously). Then bring SCLK low.

To read a bit out of IO (when IO is an output); first bring SCLK high and read the level on IO. Then bring SCLK low (in either order, or simultaneously).

The first byte to be clocked in during a transaction is made of seven bits (MSB first) of register address followed by the R/W bit, 0 for write, 1 for read. Then, one or more bytes to be written to or read from registers are clocked in or out respectively, always MSB first.

| Adr     |               | Data Field    |            |             |               |               |               |               |  |  |  |

|---------|---------------|---------------|------------|-------------|---------------|---------------|---------------|---------------|--|--|--|

| A6A0    | D7            | D6            | D5         | D4          | D3            | D2            | D1            | D0            |  |  |  |

| 0000000 | LNA_by        | PA2           | PA1        | PA0         | Sync_en       | Mode1         | Mode0         | '1'           |  |  |  |

| 0000001 | Modulation1   | Modulation0   | '0'        | <b>'</b> 0' | RSSI_en       | LD_en         | PF_FC1        | PF_FC0        |  |  |  |

| 0000010 | CP_HI         | SC_by         | '0'        | PA_By       | OUTS3         | OUTS2         | OUTS1         | OUTS0         |  |  |  |

| 0000011 | <b>'1'</b>    | <b>'1'</b>    | '0'        | VCO_IB2     | VCO_IB1       | VCO_IB0       | VCO_freq1     | VCO_freq0     |  |  |  |

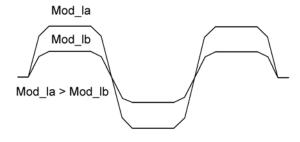

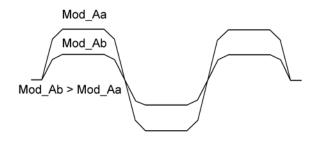

| 0000100 | Mod_F2        | Mod_F1        | Mod_F0     | Mod_I4      | Mod_I3        | Mod_I2        | Mod_I1        | Mod_I0        |  |  |  |

| 0000101 | 1             | -             | '0'        | <b>'1'</b>  | Mod_A3        | Mod_A2        | Mod_A1        | Mod_A0        |  |  |  |

| 0000110 | 1             | Mod_clkS2     | Mod_clkS1  | Mod_clkS0   | BitSync_clkS2 | BitSync_clkS1 | BitSync_clkS0 | BitRate_clkS2 |  |  |  |

| 0000111 | BitRate_clkS1 | BitRate_clkS0 | RefClk_K5  | RefClk_K4   | RefClk_K3     | RefClk_K2     | RefClk_K1     | RefClk_K0     |  |  |  |

| 0001000 | <b>'1'</b>    | <b>'1'</b>    | '0'        | ScClk4      | ScClk3        | ScClk2        | ScClk1        | ScClk0        |  |  |  |

| 0001001 | '0'           | <b>'0'</b>    | <b>'1'</b> | XCOtune4    | XCOtune3      | XCOtune2      | XCOtune1      | XCOtune0      |  |  |  |

| 0001010 | 1             | -             | A0_5       | A0_4        | A0_3          | A0_2          | A0_1          | A0_0          |  |  |  |

| 0001011 | 1             | 1             | ı          | ı           | N0_11         | N0_10         | N0_9          | N0_8          |  |  |  |

| 0001100 | N0_7          | N0_6          | N0_5       | N0_4        | N0_3          | N0_2          | N0_1          | N0_0          |  |  |  |

| 0001101 | 1             | 1             | ı          | ı           | M0_11         | M0_10         | M0_9          | M0_8          |  |  |  |

| 0001110 | M0_7          | M0_6          | M0_5       | M0_4        | M0_3          | M0_2          | M0_1          | M0_0          |  |  |  |

| 0001111 | -             | -             | A1_5       | A1_4        | A1_3          | A1_2          | A1_1          | A1_0          |  |  |  |

| 0010000 | -             | -             | -          | -           | N1_11         | N1_10         | N1_9          | N1_8          |  |  |  |

| 0010001 | N1_7          | N1_6          | N1_5       | N1_4        | N1_3          | N1_2          | N1_1          | N1_0          |  |  |  |

| 0010010 | 1             | 1             | ı          | ı           | M1_11         | M1_10         | M1_9          | M1_8          |  |  |  |

| 0010011 | M1_7          | M1_6          | M1_5       | M1_4        | M1_3          | M1_2          | M1_1          | M1_0          |  |  |  |

| 0010100 | <b>'1'</b>    | '0'           | <b>'1'</b> | <b>'</b> 0' | '0'           | '0'           | <b>'1'</b>    | <b>'1'</b>    |  |  |  |

| 0010101 | -             | -             | -          | -           | FEEC_3        | FEEC_2        | FEEC_1        | FEEC_0        |  |  |  |

| 0010110 | FEE_7         | FEE_6         | FEE_5      | FEE_4       | FEE_3         | FEE_2         | FEE_1         | FEE_0         |  |  |  |

Names of programming bits. Unused bits ("-") and mandatory bits ("1" or "0") are shown. Changes to mandatory bits may cause malfunction.

**Table 1. Control Registers**

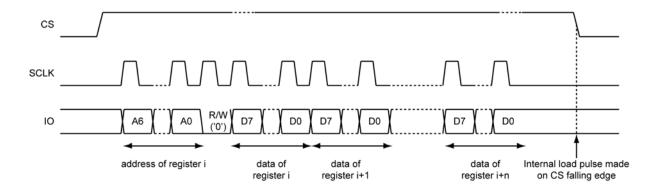

#### Writing

This method is used to write either to one register (see Figure 1), or any number of registers with consecutive addresses up to all 22 writeable registers (see Figure 2) in a single transaction.

#### Procedure:

- Bring CS active (high). IO is initially an input (and remains so for the duration of the transaction).

- Clock in a byte consisting of the address bits and the R/W bit. The first seven bits are the address (starting with MSB) of the register, or the first register if more than one, to be written. The eighth bit is the R/W bit, which is 0 as this is a write operation.

- Clock in one or more bytes, MSB of each byte first.

- Bring CS low to end the transaction.

Bits passing through IO are clocked serially into prebuffers, then transferred in parallel to the actual registers upon de-assertion of CS.

Figure 1. Writing a Byte into a Register

Figure 2. Writing Bytes into n+1 Registers at Consecutive Addresses Starting with Address i

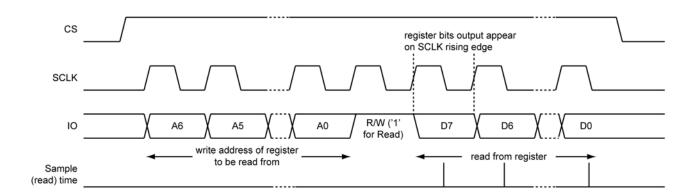

#### Reading

Any number of registers with consecutive addresses, from one up to all 23, can be read.

#### Procedure:

- Bring CS active (high). IO is initially an input.

- Clock in a byte consisting of the address bits and the R/W bit. The first seven bits are the address (starting with MSB) of the register, or the first register if more than one, to be read. The eighth bit is the R/W bit, which is 1 as this is a read operation. After the R/W bit is clocked in (falling edge of SCLK), the next rising edge on SCLK will enable IO as an output for the duration of the transaction.

- Clock out 8 bits per register (one or more) to be read through IO, MSB first. Rising edges of SCLK bring each bit to IO. The user can then conveniently sample the bit at the next falling edge of SCLK.

- Bring CS low to end the transaction. IO reverts to being an input.

Figure 3 shows how to read one register. To read more registers at consecutive addresses, continue pulsing SCLK eight times for each register to be read before de-asserting CS.

Figure 3. Reading a Byte from a Register

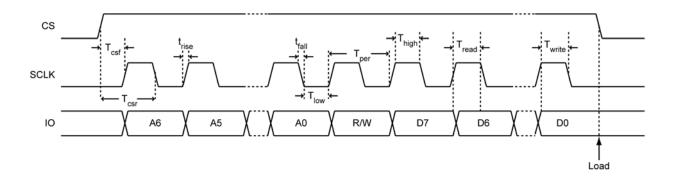

Figure 4. Definitions of Control Interface Timing Parameters

#### **Control Interface Timing**

Figure 4 and Table 2 give the timing specifications for the control interface.

When in Receive or Transmit mode (but not Power-down or Standby mode), an additional timing constraint applies: elapsed time between falling edges of CS must be a minimum of  $2/f_c$ , where  $f_c$  is the synthesizer's comparison frequency (also called phase detector frequency).  $f_c = f_{XCO}/M$ ,

$$f_{c} = \frac{f_{XCO}}{M}$$

$$min time = \frac{2M}{f_{XCO}}$$

where M = M0 when receiving or transmitting with VCO modulation, and  $M = max\{M0, M1\}$  when transmitting with divider modulation.

|                    |                                                                                                                   | Values |      |      |       |

|--------------------|-------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|

| Symbol             | Parameter                                                                                                         | Min.   | Тур. | Max. | Units |

| T <sub>high</sub>  | Min. high time of SCLK                                                                                            | 20     |      |      | ns    |

| T <sub>low</sub>   | Min. low time of SCLK                                                                                             | 20     |      |      | ns    |

| t <sub>fall</sub>  | Fall time of SCLK                                                                                                 |        |      | 1    | μs    |

| t <sub>rise</sub>  | Rise time of SCLK                                                                                                 |        |      | 1    | μs    |

| T <sub>csr</sub>   | Time from rising edge of CS to falling edge of SCLK                                                               | 50     |      |      | ns    |

| T <sub>csf</sub>   | Min. delay from<br>rising edge of CS<br>to rising edge of<br>SCLK                                                 | 25     |      |      | ns    |

| T <sub>write</sub> | Min. delay from<br>valid IO to falling<br>edge of SCLK<br>during a write<br>operation                             | 20     |      |      | ns    |

| T <sub>read</sub>  | Min. delay from rising edge of SCLK to valid IO during a read operation (assuming load capacitance of IO is 25pF) | 75     |      |      | ns    |

| t <sub>POR</sub>   | Power on Reset time                                                                                               |        | 4.6  | 9    | ms    |

**Table 1. Control Interface Timing**

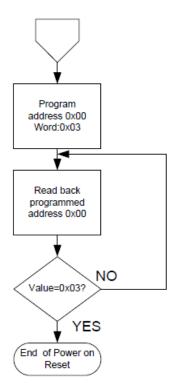

#### **Power-on Reset**

The power-on reset time ( $t_{POR}$ ), given in Table 2, is defined as the time from application of supply voltage to completion of power on reset.

To determine when the chip has completed its power-on without waiting for the worst-case time (maximum  $t_{\text{POR}}$ ), do the following:

- Write hex 03 (binary 00000011) to Register 0.

This puts the chip in Standby mode.

- Read Register 0. If the value read is binary 00000011, then exit; power-on is complete. If not, go to previous step and repeat.

Because registers are initially in an unknown state after power-on (exception: Mode[1:0] initializes to 00), always enter a complete set of register values as the first transaction, and always enter only nonzero values for N and M.

Figure 5. Power-On Programming Flowchart

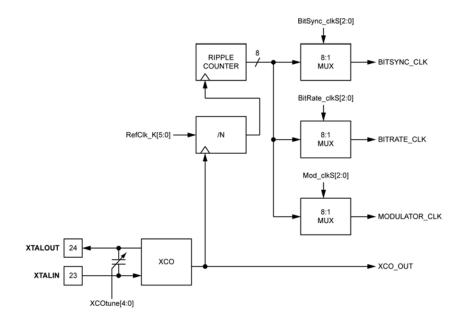

#### **Clock Generation**

The MICRF507's crystal oscillator:

- Serves as the reference for the synthesizer that is the carrier and local oscillator source.

- Is divided down to clock the switched-capacitor IF filter.

- Is divided down to generate three other clocks: bit rate clock, bit synchronization clock, and modulator clock

Figure 6 shows the oscillator with its frequency-shifting capacitor bank (controlled by the register field XCOtune) and the frequency dividers that derive the latter three clocks from its output. This division occurs in two stages. First, the XCO output is divided by the 6-bit field Refclk\_K, which has allowable values between 1 and 63. Then, for each of the three clocks, another field (BitSync\_clkS, BitRate\_ClkS, and ModClkS, respectively) selects the number of further divisions by 2. Complete relationships of field values and resultant frequencies are given below for each clock.

| Field Name   | Number of bits | Location of bits      | Description                                                                                                                                                                                     |  |

|--------------|----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XCOtune      | 5              | Reg9[4:0]             | Crystal oscillator trimming.                                                                                                                                                                    |  |

| RefClk_K     | 6              | Reg7[5:0]             | Reference clock divider.                                                                                                                                                                        |  |

| BitRate_clkS | 3              | Reg6[0],<br>Reg7[7:6] | Transmitter Bit rate clock setting. See Figure 9 and "Data Interface and Bit Synchronization" section for more details.                                                                         |  |

| Mod_clkS     | 3              | Reg6[6:4]             | VCO Modulator clock setting, set the modulator clock to either 8x or 16x the bit rate clock.                                                                                                    |  |

| BitSync_clkS | 3              | Reg6[3:1]             | Receiver Bit Synchronization clock setting, always set bit synchronization clock to 16x the bit rate clock. See Figure 9 and "Data Interface and Bit Synchronization" section for more details. |  |

Table 3. Register Bit Fields for Clock Generation

Figure 6. MICRF507 Clock Sources

## **Crystal Oscillator (XCO)**

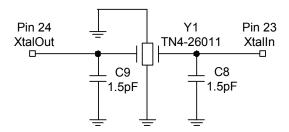

The crystal oscillator's role as the synthesizer reference demands very good phase and frequency stability. As shown in Figure 7, the external components required for the oscillator are a crystal, connected between pins 23 and 24, and loading capacitors.

Figure 7. Crystal Oscillator Circuit

The load capacitance  $C_{\text{L}}$  seen between the crystal terminals is:

$$C_{L} = \frac{1}{\frac{1}{C_{8}} + \frac{1}{C_{9}}} + C_{\text{XCOtune}} + C_{\text{pin}}$$

Where  $C_{\text{XCOtune}}$  is the capacitance of the internal adjustable capacitor bank, and  $C_{\text{pin}}$  is defined as the internal chip capacitance when XCOtune bits are all zeros, plus PCB stray capacitance across pins 23 and 24. The value of  $C_{\text{pin}}$  is about 6pF. The loading capacitor values required depend on the total  $C_{\text{L}}$  specified for the crystal for oscillation at the desired frequency.

It is possible to tune the crystal oscillator internally by giving the 5-bit register field XCOtune a non-zero value, which causes internal capacitors to be switched across the crystal. As this capacitance increases, frequency decreases. When XCOtune is set to its maximum value of 31, approximately 4.5pF additional capacitance is connected across the crystal pins.

The XCO tuning can be used to cancel crystal resonant frequency error, both initial and with temperature. It can be used in combination with the Frequency Error Estimator (FEE). See "FEE" section.

The crystal used is a TN4-26011 from Toyocom. Specification:

- Package TSX-10A,

- Nominal frequency 16.000000MHz

- Frequency tolerance ±10ppm

- Frequency stability ±9ppm, load capacitance 9pF

- Pulling sensitivity 15ppm/pF

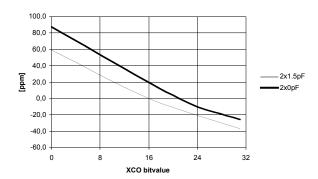

To achieve 9pF load capacitance required to center TN4-26011 at 16MHz, set the external capacitors to 1.5pF and XCOtune= $16_{\rm dec}$ . Figure 8 shows the tuning range for two different capacitor values, 1.5pF and zero (external capacitors omitted). External capacitor values will strongly affect the tuning range. Using 1.5pF with the above crystal gives a tuning range that is approximately symmetrical about the center frequency.

Figure 8. XCO Tuning with the XCOtune Field

The start-up time of the cystal oscillator, given in Table 4, is about a millisecond and increases with capacitance. When the MICRF507's main mode is switched from Power down mode to Transmit mode via Standby mode, or to Receive mode via Standby mode, only the XCO is energized at first. Current consumption during this prestart period is approximately 280µA (the same as for Standby mode). After the XCO amplitude is sufficient to trigger the M-counter and produce two pulses at its output, the remaining circuits on the chip are powered on.

| XCOtune | Start-up Time (µs) |  |  |

|---------|--------------------|--|--|

| 0       | 590                |  |  |

| 1       | 590                |  |  |

| 2       | 700                |  |  |

| 4       | 700                |  |  |

| 8       | 810                |  |  |

| 16      | 1140               |  |  |

| 31      | 2050               |  |  |

Table 4. Typical Crystal Oscillator Start-up Time with C8 = C9 = 1.5pF

An external reference clock, when used instead of a crystal, should be applied to pin 24 (XTALOUT) with pin 23 (XTALIN) not connected. To maintain proper DC biasing within the chip, use AC-coupling between the external reference and the XTALOUT-pin.

#### BITSYNC\_CLK (Receiver Bit Synchronization Clock)

The frequency of the bit synchronization clock  $f_{\text{BITSYNC\_CLK}}$ , is a function of the crystal oscillator frequency  $f_{\text{XCO}}$  and the values of the register fields Refclk\_K and BitSync\_clkS:

$$f_{\text{BITSYNC\_CLK}} = \frac{f_{\text{XCO}}}{\text{Refclk\_K} \times 2^{(7\text{-}BitSync\_clkS)}}$$

The bit synchronizer uses a clock that needs to be programmed to 16 times the actual bit rate. As an example, a bit rate of 20kbps needs a bit synchronizer clock with frequency of 320kHz. Refer to Figure 9 and "Data Interface and Bit Synchronization" section for more details.

#### BITRATE\_CLK (Transmitter Bit Rate Clock)

The frequency  $f_{\text{BITRATE\_CLK}}$  of BITRATE\_CLK is a function of the crystal oscillator frequency  $f_{\text{XCO}}$  and the values of the register fields Refclk K and BitRate clkS:

$$f_{\text{BITRATE\_CLK}} = \frac{f_{\text{XCO}}}{\text{Refclk } K \times 2^{(7\text{-BitRate\_clkS})}}$$

In transmit mode, when Sync\_en = 1, BITRATE\_CLK appears on the DATACLK pin. Its frequency is equal to the bit rate. Example; a bit rate of 20 kbit/sec requires an  $f_{\text{BITRATE\_CLK}}$  of 20kHz. Refer to Figure 9 and the "Data Interface and Bit Synchronization" subsection for more details.

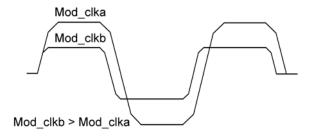

#### MODULATOR\_CLK (VCO Modulator Clock)

The frequency  $f_{MOD\_CLK}$  of MODULATOR\_CLK is a function of the crystal oscillator frequency  $f_{XCO}$  and the values of the register fields Refclk\_K and Mod\_clkS:

$$f_{MOD\_CLK} = \frac{f_{XCO}}{Refclk\_K \times 2^{(7-Mod\_clkS)}}$$

The modulator clock is used if VCO modulation method is selected. Set the modulator clock frequency to either 8x or 16x the bit rate. See "VCO Modulation and the Modulator" subsection for more information.

| BitRate_clkS[2:0] BitSync_clkS[2:0] | Corresponding Clock<br>Frequency        |

|-------------------------------------|-----------------------------------------|

| Mod_clkS[2:0]                       | (f <sub>XCO</sub> is crystal frequency) |

| 000                                 | f <sub>XCO</sub> /(128xRefClk_K)        |

| 001                                 | f <sub>XCO</sub> /(64xRefClk_K)         |

| 010                                 | f <sub>XCO</sub> /(32xRefClk_K)         |

| 011                                 | f <sub>XCO</sub> /(16xRefClk_K)         |

| 100                                 | f <sub>XCO</sub> /(8xRefClk_K)          |

| 101                                 | f <sub>XCO</sub> /(4xRefClk_K)          |

| 110                                 | f <sub>XCO</sub> /(2xRefClk_K) (*)      |

| 111                                 | f <sub>XCO</sub> /RefClk_K (*)          |

<sup>(\*)</sup> Can not be used as BitRate clk.

Table 5. Generation of Bitrate\_clk, BitSync\_clk and Mod\_clk

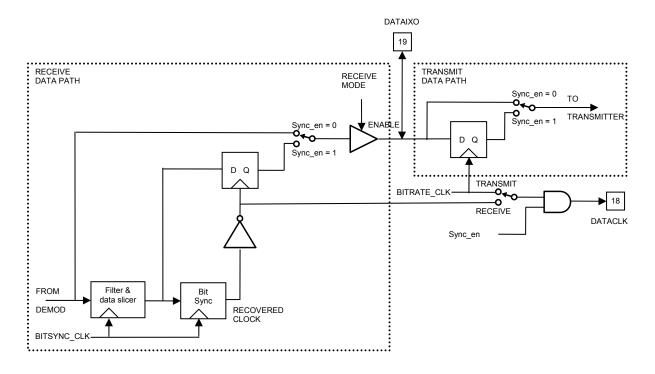

## **Data Interface and Bit Synchronization**

Transmitted and received data bits are coupled to the MICRF507 serially through the Data Interface. This Data Interface consists of the DATAIXO and DATACLK pins. This is a separate interface from the Control Interface (CS, IO, and SCLK), for which see Control (3-wire) Interface.

Figure 9 shows the data interface circuitry aboard the MICRF507. DATAIXO is an input during transmission, whereas during reception a driver is enabled and it becomes an output. DATACLK is always an output.

A rule that applies when using VCO modulation is: after commanding the MICRF507 to enter transmit mode, the microcontroller shall tri-state the driver connected to DATAIXO to leave that pin floating until the microcontroller begins sending data. See "Mode Transitions" section for more details.

The data interface can be programmed for synchronous and non-synchronous operation according to the setting of the Sync en bit; see Table 7.

| Field Name | Number of bits | Location of bits | Description           | Reference |

|------------|----------------|------------------|-----------------------|-----------|

| Sync_en    | 1              | Reg0[3]          | Synchronizer Mode bit | Table 7   |

Table 6. Register Bit Fields for Data Interface and Bit Synchronization

| Sync_en | State                       | Comments                              |

|---------|-----------------------------|---------------------------------------|

| 0       | RX: Bit synchronization off | Transparent reception of data         |

| 0       | TX: DataClk pin off         | Transparent transmission of data      |

| 1       | RX: Bit synchronization on  | Bit clock is generated by transceiver |

| 1       | TX: DataClk pin on          | Bit clock is generated by transceiver |

**Table 7. Synchronizer Mode Bit**

Figure 9. Data Interface and Synchronization

| Mode       | Sync_en | DATACLK   |                                     | DATAIXO   |                                                                                      |  |

|------------|---------|-----------|-------------------------------------|-----------|--------------------------------------------------------------------------------------|--|

|            |         | Direction | Signal                              | Direction | Signal/Function                                                                      |  |

|            | 0       | Output    | 0                                   | Input     | Modulates carrier directly (asynchronously)                                          |  |

| Transmit 1 | 1       | Output    | BitRate clock                       | Input     | Sampled at rising edge of BitRate clock; latched output modulates carrier            |  |

|            | 0       | Output    | 0                                   | Output    | Raw output from demodulator                                                          |  |

| Receive    | 1       | Output    | Clock recovered by bit synchronizer | Output    | Filtered and latched demodulator output; transitions occur at rising edge of DATACLK |  |

**Table 8. Synchronizer Mode and Data Interface**

In sync mode (Sync\_en bit set to 1), the transmitted bit stream is clocked with the precision of the MICRF507's crystal oscillator, which relaxes timing accuracy requirements on the data source. During reception, the synchronizer ensures that transitions of DATAIXO occur only at rising edges of DATACLK, without edge jitter or internal glitches. Receiver sensitivity values given in the Electrical Characteristics table are measured with Sync\_en = 1; with Sync\_en = 0, as much as 3-6 dB of sensitivity could be lost.

#### $Sync_en = 0$

When Sync\_en = 0, the input signal at DATAIXO modulates the transmitter directly during transmission and the output signal from DATAIXO is the raw demodulator output. DATACLK remains fixed at a logic low level during both transmission and reception.

#### $Sync_en = 1$

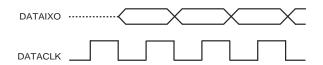

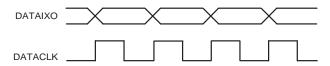

During transmission when Sync\_en = 1 the data bit stream entering DATAIXO is buffered with a flip-flop strobed at the rising edge of BITRATE\_CLK, and the output of the flip-flop modulates the transmitter. BITRATE\_CLK is brought out at the DATACLK output. Figure 10 shows the relationship of DATACLK and DATAIXO transitions.

Figure 10. Data Interface in Transmit Mode

During reception, the bit synchronizer recovers the received signal's clock. This recovered clock strobes a flip-flop that samples in mid-bit-period the demodulated and filtered bit stream. The DATACLK output brings out the

recovered clock. DATAIXO (an output during reception) brings out the synchronized data stream, which has its transitions at rising edges of DATACLK. See Figure 11.

Figure 11. Data Interface in Receive Mode

By being in control of bit timing, the MICRF507 is effectively the "master." For maximum timing margin, the microcontroller, as the "slave," can present or sample (during transmit and receive, respectively) each new bit at the DATAIXO pin at falling edges of DATACLK.

# Additional Considerations in the Use of Synchronizer (Sync\_en = 1)

Two clock signals, BITRATE\_CLK and BITSYNC\_CLK, must be properly programmed when using the synchronizer. BITRATE\_CLK, used in transmission, must be set to a frequency equal to the bit rate. BITSYNC\_CLK, used in reception, must have a frequency 16 times the bit rate. These frequencies are controlled by the crystal oscillator frequency and the settings of register fields, as described in the "Clock Generation" section. Bit clocking of the incoming signal must agree with the receiver's local clocking within  $\pm 2.5\%$  (easily met with 100 PPM or better crystals). For example, if  $f_{\text{BITSYNC\_CLK}}$  is 16x19.231kbps, the incoming bit rate can be between 0.975x19.231kbps to 1.025x19.231kbps.

All incoming messages must start with a 0101... preamble so that the synchronizer can acquire the incoming clock. A 24-bit preamble is typically used; a minimum of 22 bits is required.

## **Frequency Synthesizer**

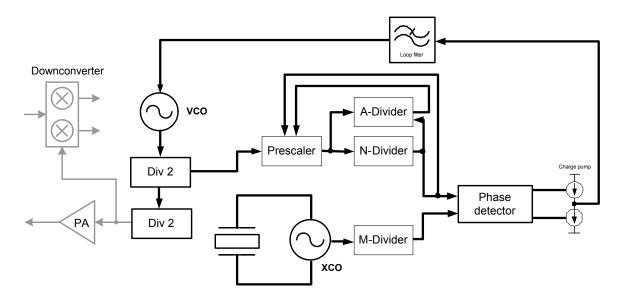

The MICRF507 frequency synthesizer is an integer-N phase-locked loop consisting of:

- a reference source, made of an M-divider clocked by the crystal oscillator

- a voltage controlled oscillator (VCO)

- a programmable frequency divider made of an N-divider, an A-divider, and a dual modulus prescaler

- a phase/frequency detector

The loop filter is external for flexibility and can be a simple passive circuit.

The phase/frequency detector compares the reference frequency (from the M-divider) with the VCO output fed through the programmable frequency divider. The charge pump output of the phase/frequency detector,

after filtering, controls the VCO, closing the loop and forcing the error between the reference frequency and the divided VCO frequency to zero.

The block diagram, Figure 12, shows the basic elements and arrangement of a PLL-based frequency synthesizer. The MICRF507 has a dual modulus prescaler for increased frequency resolution. In a dual modulus prescaler the main divider is split into two parts, the main part N and an additional divider A, where A < N. Both dividers are clocked from the output of the dual-modulus prescaler, but only the output of the N divider is fed into the phase detector. The prescaler will first divide by 16. Both N and A count down until A reaches zero, at which point the prescaler is switched to a division ratio 16+1. At this point, the divider N has completed A counts. Counting continues until N reaches zero, which is an additional N-A counts. At this point, the cycle repeats.

| Field Name | Number of bits | Location of bits          | Description                                    |

|------------|----------------|---------------------------|------------------------------------------------|

| MO         | 12             | Reg13[3:0],<br>Reg14[7:0] | M0 counter                                     |

| A0         | 6              | Reg10[5:0]                | A0 counter                                     |

| N0         | 12             | Reg11[3:0],<br>Reg12[7:0] | N0 counter                                     |

| M1         | 12             | Reg18[3:0],<br>Reg19[7:0] | M1 counter                                     |

| A1         | 6              | Reg15[5:0]                | A1 counter                                     |

| N1         | 12             | Reg16[3:0],<br>Reg17[7:0] | N1 counter                                     |

| CP_HI      | 1              | Reg2[7]                   | High charge pump current (1= 500μA, 0 = 125μA) |

| VCO_Freq   | 2              | Reg3[1:0]                 | Frequency setting of VCO (see Table 11)        |

| VCO_IB     | 3              | Reg3[4:2]                 | VCO bias current setting (see Table 11)        |

| LD_en      | 1              | Reg1[2]                   | Lock detect function on/off                    |

Table 9. Register Bit Fields for Frequency Synthesizer

Figure 12. PLL Block Diagram

| A6A0    | D7   | D6   | D5   | D4   | D3    | D2    | D1   | D0   |

|---------|------|------|------|------|-------|-------|------|------|

| 0001010 | -    | -    | A0_5 | A0_4 | A0_3  | A0_2  | A0_1 | A0_0 |

| 0001011 | -    | -    | -    | -    | N0_11 | N0_10 | N0_9 | N0_8 |

| 0001100 | N0_7 | N0_6 | N0_5 | N0_4 | N0_3  | N0_2  | N0_1 | N0_0 |

| 0001101 | -    | -    | -    | -    | M0_11 | M0_10 | M0_9 | M0_8 |

| 0001110 | M0_7 | M0_6 | M0_5 | M0_4 | M0_3  | M0_2  | M0_1 | M0_0 |

| 0001111 | -    | -    | A1_5 | A1_4 | A1_3  | A1_2  | A1_1 | A1_0 |

| 0010000 | -    | -    | -    | -    | N1_11 | N1_10 | N1_9 | N1_8 |

| 0010001 | N1_7 | N1_6 | N1_5 | N1_4 | N1_3  | N1_2  | N1_1 | N1_0 |

| 0010010 | -    | -    | -    | -    | M1_11 | M1_10 | M1_9 | M1_8 |

| 0010011 | M1_7 | M1_6 | M1_5 | M1_4 | M1_3  | M1_2  | M1_1 | M1_0 |

Table 10. Register Bit Fields for PLL

N, M, and A are numbers of length 12, 12 and 6 bits, respectively The synthesizer's output frequency can be calculated from the following equation:

$$f_{PD} = \frac{f_{XCO}}{M} = \frac{f_{VCO}}{(16 \times N + A) \times 2} = \frac{f_{RF} \times 2}{(16 \times N + A)}$$

$$M \neq 0$$

$1 \le A \le 16$

$$f_{RF} = f_{XCO} \frac{16 \times N + A}{2M}$$

where

f<sub>PD</sub>: Phase detector comparison frequency

f<sub>XCO</sub>: Crystal oscillator frequency

f<sub>VCO</sub>: Voltage controlled oscillator frequency

f<sub>RF</sub>: RF carrier frequency

The MICRF507 has two sets of register fields controlling the synthesizer's frequency multiplication ratio; A0/N0/M0 and A1/N1/M1. During transmission using divider modulation (see "Divider Modulation" section), bit values of '0' and '1' respectively select the 0 and 1 register field set. During reception and during transmission using VCO modulation, only the 0 set is used.

#### **VCO**

The VCO has no external components.

The three-bit field VCO\_IB controls VCO bias current to optimize phase noise. The two bit field VCO\_freq controls a capacitor bank which determines the VCO frequency range. These five bits are set according to the RF frequency as follows:

| RF<br>Freq     | VCO_IB2 | VCO_IB1 | VCO_IB0 | VCO_freq1 | VCO_freq0 |

|----------------|---------|---------|---------|-----------|-----------|

| 470-<br>482MHz | 1       | 0       | 1       | 0         | 1         |

| 482-<br>497MHz | 1       | 0       | 0       | 1         | 0         |

| 497-<br>510MHz | 0       | 1       | 1       | 1         | 1         |

Table 11. VCO Bit Setting

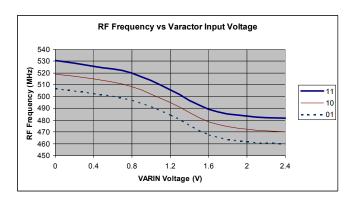

The tuning range, the RF frequency versus VCO tune voltage (varactor input, pin 29), depends on the VCO frequency setting as shown in as shown in Figure 13. When the tuning voltage is in the range from 0.9V to 1.4V, the VCO gain (as seen by the PLL) is at its maximum, approximately 64 to 70MHz/V. Note that the RF frequency is half of the PLL frequency. It is recommended that the VCO tune voltage stays in this range.

The input capacitance at the varactor pin must be taken into consideration when designing the PLL loop filter. This is most critical when designing a loop filter with high bandwidth, which gives relatively small component values. The input capacitance is approximately 6pF.

Figure 13. RF Frequency vs. Varactor Voltage and VCO\_ Freq bits (V<sub>DD</sub> = 2.5V)

#### **Charge Pump**

The charge pump current can be set to either  $125\mu A$  or  $500\mu A$  by CP\_HI ('1'  $\rightarrow$   $500\mu A$ ). This will affect the loop gain and, consequently, filter component values. For applications using high phase detector frequency and high PLL bandwidth, use  $500\mu A$  charge pump current.

#### **PLL Filter**

The design of the PLL filter strongly affects the performance of the frequency synthesizer. Key parameters in PLL filter design are loop bandwidth, the modulation method (VCO modulation or divider modulation) and the bit rate. Filter design also affect the switching time (important when frequency hopping) and phase noise.

Divider modulation requires the PLL to lock on a new carrier frequency for every new data bit. As a rule of thumb, the PLL loop bandwidth should be at least twice as high as the bit rate. In such cases it is recommended to use a third order filter to suppress the phase detector frequency.

For VCO modulation, the PLL loop bandwidth should be less than 1/10 of the bit rate. If the loop bandwidth is high relative to the bit rate, the PLL will keep the VCO at a fixed frequency, preventing it from being modulated.

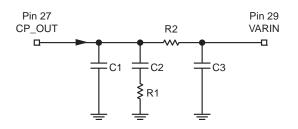

The recommended third-order loop filter (made with external components) is shown in Figure 14. When R2=0 and C3 is omitted, this reduces to a second-order loop filter.

Figure 14. Second and Third Order Loop Filter

Table 12 shows three different loop filter designs, the first two for VCO modulation and the last one for modulation using the internal dividers. The component values are calculated with RF frequency = 490MHz, VCO gain = 67MHz/V as seen by the PLL, and desired phase margin = 56°. Other settings are shown in the table. The VARIN pin capacitance (pin 29) of 6pF can be neglected for the two filters with lowest bandwidth (which have R2=0 and relatively large values of C1). For other loop bandwidth and phase detector values, use the loop filter calculation tool in RF Testbench software available on Micrel's website.

#### **Lock Detect**

A lock detector can be enabled by setting LD\_en = 1. When pin LD is high, it indicates that the PLL is in lock.

After a control word is loaded LD will (typically) go low, then high again when the synthesizer has locked. LD also goes low initially when the PA (power amplifier) is turning on.

After the transceiver has been put into Receive or Transmit mode, or after the power amplifier has been turned on, a low-to-high transition at LD can serve as an indicator that the synthesizer frequency has stabilized.

|         | Encoded<br>Bit Rate<br>(kbps) | PLL<br>BW<br>(kHz) | Charge<br>Pump<br>(µA) | Phase<br>Detector<br>Freq. (kHz) | C1    | C2    | R1    | R2   | С3   |

|---------|-------------------------------|--------------------|------------------------|----------------------------------|-------|-------|-------|------|------|

| VCO     | >8                            | 0.8                | 125                    | 100                              | 10nF  | 100nF | 6.2kΩ | 0    | NC   |

| VCO     | >32                           | 3.2                | 125                    | 100                              | 680pF | 6.8nF | 22kΩ  | 0    | NC   |

| Divider | <6.5                          | 13                 | 500                    | 500                              | 390pF | 8.2nF | 5kΩ   | 68kΩ | 18pF |

**Table 12. Loop Filter Component Values**

#### Receiver

| Field Name | Number of bits | Location of bits | Description                                | Reference |

|------------|----------------|------------------|--------------------------------------------|-----------|

| By_LNA     | 1              | Reg0[7]          | LNA bypass on/off                          |           |

| PF_FC      | 2              | Reg1[1:0]        | Pre-filter corner frequency                | Table 14  |

| SC_by      | 1              | Reg2[6]          | Bypass of switched capacitor filter on/off |           |

| ScClk      | 5              | Reg8[4:0]        | Switched Cap clock divider                 |           |

| RSSI_en    | 1              | Reg1[3]          | RSSI function on/off                       |           |

| FEEC       | 4              | Reg21[3:0]       | FEE control bits                           | Table 15  |

| FEE        | 8              | Reg22[7:0]       | FEE value (read only)                      |           |

Table 13. Register Bit Fields for Receiver

The receiver is a zero intermediate frequency (ZIF) type employing low-power, fully integrated low-pass filters.

A low noise amplifier (LNA) drives a quadrature mixer pair. The mixer outputs feed two identical signal channels. Each channel's signal path has a pre-amplifier, a third order Sallen-Key RC low-pass pre-filter, a six-pole switched-capacitor filter (which determines actual selectivity), and finally a limiter.

The limiter outputs then enter a demodulator which detects the relative phase of the baseband I and Q signals. If the I channel signal lags the Q channel, the FSK tone frequency lies above the LO frequency (data '1'). If the I channel leads the Q channel, then the FSK tone lies below the LO frequency (data '0'). The output of the demodulator is available on the DATAIXO pin; in either raw form or latched with the recovered clock according to the setting of Sync\_en bit. An RSSI (receive signal strength indicator) circuit indicates the received signal level.

#### **Front End**

The MICRF507's low-noise amplifier boosts the incoming signal prior to frequency conversion in order to prevent mixer noise from degrading overall front-end noise performance. The LNA is a two-stage amplifier and has a nominal gain of approximately 23dB at 490MHz. The front end has a gain of about 31dB to34dB. The gain varies by 1-1.5dB over a 2.0V to 2.5V variation in power supply.

The LNA can be bypassed by setting bit LNA\_by to '1'. This can be useful for very strong input signal levels. The front-end gain with the LNA bypassed is about 12dB. The mixers have about 10dB of gain at 490MHz. With appropriate setting of the OUTS field (register 2, bits D3 to D0), the differential outputs of the mixers can be made

available at pins IchOut and QchOut. The output impedance of each mixer is about  $8k\Omega$ .

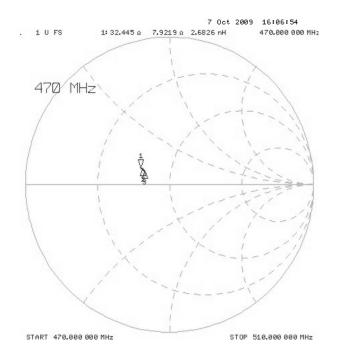

| MARKER | MHz | RESISTANCE | REACTANCE |

|--------|-----|------------|-----------|

| 1      | 470 | 32.4Ω      | 7.9Ω      |

| 2      | 490 | 33.4Ω      | 7.4Ω      |

| 3      | 510 | 34.4Ω      | 6.4Ω      |

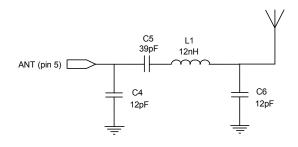

Figure 15. LNA Input Impedance

The front end's input impedance, with no matching network, is close to  $50\Omega$  as shown in Figure 15. This gives an input reflection coefficient of about -13dB. Although the receiver does not require a matching network to optimize the gain, a matching network is recommended for harmonic suppression during transmission and for improved selectivity in reception.

#### Sallen-Key Filters

Each IF channel includes a pre-amplifier and a pre-filter.

The preamplifier has a gain of 22dB. The IF amplifier also removes DC offset. Gain varies by less than 0.5dB over a 2.0V to 2.5V variation in power supply.

The pre-filter is implemented as a three-pole Sallen-Key low-pass filter. It protects the switched-capacitor filter that follows it from strong adjacent channel signals and also serves as an anti-aliasing filter. It is programmable to four different cut-off frequencies as shown in Table 14.

| PF_FC1 | PF_FC0 | Cutoff (3dB filter corner) |

|--------|--------|----------------------------|

| 0      | 0      | 100kHz                     |

| 0      | 1      | 150kHz                     |

| 1      | 0      | 230kHz                     |

| 1      | 1      | 340kHz                     |

Table 14. Pre-Filter Bit Field

### **Switched Capacitor Filter**

The main IF channel filter is a switched-capacitor implementation of a six-pole elliptic low pass filter. This meets selectivity and dynamic range requirements with minimum total capacitance. The cut-off frequency of the switched-capacitor filter is adjustable by changing the clock frequency.

A 6-bit frequency divider, programmed by the ScClk[5:0] field, is clocked by the crystal oscillator. Its output, which is 20 times the filter's cutoff frequency, is then divided by 4 to generate the correct non-overlapping clock phases needed by the filter. The cut-off frequency of the filter is given by:

$$f_{CUT} = \frac{f_{XCO}}{40 \cdot ScClk}$$

f<sub>CUT</sub>: Filter cutoff frequency

f<sub>XCO</sub>: Crystal oscillator frequency

ScClk: Switched capacitor filter clock, bits ScClk[4:0] (bit 0 has a mandatory value of '0').

For instance, for a crystal frequency of 16MHz and if the 6 bit divider divides the input frequency by 4, the cut-off frequency of the SC filter is  $16MHz/(40 \times 4) = 100kHz$ . A first-order RC low-pass filter removes clock frequency components from the signal at the switched-capacitor filter output.

The pre-filter and switched-capacitor filters in cascade must pass the full IF bandwidth of the received signal. In a zero-IF receiver such as the MICRF507 this bandwidth is as follows:

$$f_{BW} = f_{OFFSET} + f_{DEV} + \frac{r_b}{2}$$

where

$f_{BW}$ : Needed receiver bandwidth;  $f_{CUT}$  above should not be smaller than  $f_{BW}$  [Hz]

$f_{\mathsf{OFFSET}}$ : Total frequency offset between receiver and transmitter [Hz]

f<sub>DEV</sub>: Single-sided frequency deviation [Hz]

r<sub>b</sub>: The bit rate in bits/sec

#### **RSSI**

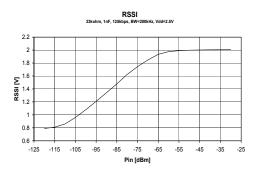

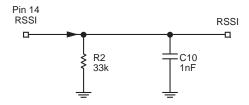

Figure 16. RSSI Voltage

Figure 17. RSSI Network

Figure 16 shows a typical plot of the RSSI voltage as a function of input power. The RSSI termination network is shown in Figure 17. The RSSI has a dynamic range of about 50dB from about -110dBm to -60dBm input power.

When an RF signal is received, the RSSI output increases and can serve as a signal presence indicator. It could be used to wake up external circuitry that conserves battery life while in a sleep mode. Note that RSSI only functions in Receive mode.

Another use for RSSI is to determine that transmit power can be reduced in a system. If the RSSI detects a strong signal, the transmitter could be alerted to reduce its transmit power and so reduce current consumption.

#### **FEE**

The Frequency Error Estimator (FEE) counts pulses from inside the demodulator to measure the frequency offset between it's receive frequency and the transmitter's frequency. The maximum offset that FEE can correctly report a frequency difference is about ±20ppm. The output of the FEE can be used to tune the XCO frequency, both for production calibration and to compensate for crystal temperature drift and aging.

The FEE is enabled when FEEC[1:0] = 11, and is off when FEEC[1:0] = 00 (do not use other values). It has two counters. One counter determines the measurement period by generating a trigger every time it has counted up the number of bit periods selected by the setting of FEEC[3:2] as given in Table 15. A second counter accumulates the net tally of UP and DN pulses from the demodulator. For each incoming '1' bit, UP carries an average number of pulses that is twice the modulation index ( $\beta$ ), and likewise for each incoming '0' bit and DN. The trigger transfers the contents of the second counter to the FEE register and clears it, after which it begins accumulating again.

| FEEC_1        | FEEC_0            | FEE Mode                                                                |

|---------------|-------------------|-------------------------------------------------------------------------|

| 0             | 0                 | Off                                                                     |

| 0             | 1                 | Do not use                                                              |

| 1             | 0                 | Do not use                                                              |

| 1             | 1                 | Counting UP and DN pulses. UP increments the counter, DN decrements it. |

|               |                   | acoromonia it.                                                          |

| FEEC_3        | FEEC_2            | No. of bits used for the measurement                                    |

| <b>FEEC_3</b> | <b>FEEC_2</b> 0   | No. of bits used for the                                                |

| 0<br>0        | <b>FEEC_2</b> 0 1 | No. of bits used for the measurement                                    |

| 0             | 0<br>1<br>0       | No. of bits used for the measurement                                    |

Table 15. FEEC (Frequency Error Estimator Control) Bits

The result of the measurement, read from the FEE register at address 22 (16 hex, 0010110 binary), is actually an eight-bit two's complement signed number, which can have values from -128 to 127. Reading FEE gives the most recently transferred value. The raw FEE value, treated as an unsigned number ranging from 0 to 255, can be converted into a signed integer as follows:

For a straightforward measurement of frequency offset, the incoming signal has to have an equal number of ones and zeros, such as a 1010... preamble. The frequency offset can then be calculated:

$$f_{OFFSET} = \frac{r_b}{4P} FEE_{SIGNED}$$