#### **MIC58P42**

#### 8-Bit Serial-Input Protected Latched Driver

#### **General Description**

The MIC58P42 serial-input latched driver is a high-voltage (80V), high-current (500mA) integrated circuit comprised of eight CMOS data latches, a bipolar Darlington transistor driver for each latch, and CMOS control circuitry for the common STROBE, CLOCK, SERIAL DATA INPUT, and OUTPUT ENABLE functions. Similar to the MIC5842, additional protection circuitry supplied on this device includes thermal shutdown, under voltage lockout (UVLO), and overcurrent shutdown.

The bipolar/CMOS combination provides an extremely low-power latch with maximum interface flexibility. The MIC58P42 has open-collector outputs capable of sinking 500 mA and integral diodes for inductive load transient suppression with a minimum output breakdown voltage rating of 80V (50V sustaining). The drivers can be operated with a split supply, where the negative supply is down to -20V and may be paralleled for higher load current capability.

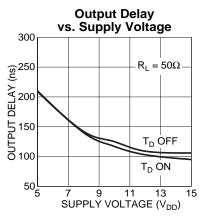

With a 5V logic supply, the MIC58P42 will typically operate at better than 5MHz. With a 12V logic supply, significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS, PMOS, and NMOS circuits. TTL circuits may require pull-up resistors. By using the serial data output, drivers may be cascaded for interface applications requiring additional drive lines.

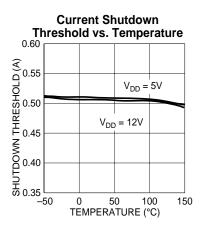

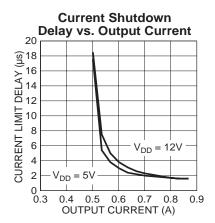

Each of these eight outputs has an independent over current shutdown of 500 mA. Upon over-current detection, the affected channel will turn OFF until  $\rm V_{DD}$  is cycled or the ENABLE/RESET pin is pulsed high. Current pulses less than 2µs will not activate current shutdown. Temperatures above 165°C will shut down the device. The UVLO circuit prevents operation at low  $\rm V_{DD}$ ; hysteresis of 0.5V is provided. See the MIC59P60 for a similar device that additionally provides an error flag output.

#### **Features**

- · 3.3 MHz Minimum Data-Input Rate

- CMOS, PMOS, NMOS, and TTL Compatible

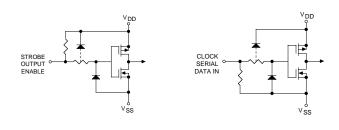

- Internal Pull-Up/Pull-Down Resistors

- Low Power CMOS Logic and Latches

- High Voltage (80V) Current-Sink Outputs

- Output Transient-Protection Diodes

- Single or Split Supply Operation

- Thermal Shutdown

- Under-Voltage Lockout

- Per-Output Over-Current Shutdown (500mA typical)

## **Ordering Information**

| Part Number | Temperature Range | Package            |  |  |  |

|-------------|-------------------|--------------------|--|--|--|

| MIC58P42BN  | -40°C to +85°C    | 18-Pin Plastic DIP |  |  |  |

| MIC58P42BV  | -40°C to +85°C    | 20-Pin PLCC        |  |  |  |

| MIC58P42BWM | -40°C to +85°C    | 18-Pin Wide SOIC   |  |  |  |

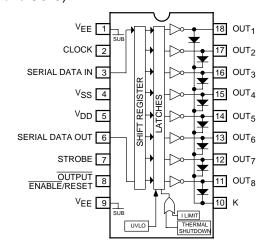

#### **Functional Diagram**

#

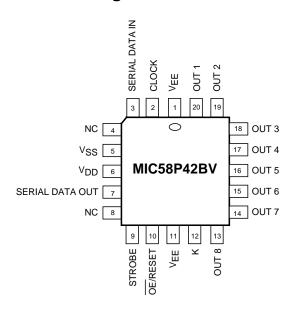

#### **Pin Configuration**

(DIP and SOIC)

MIC58P42 Micrel

## **PLCC Pin Configuration**

## **Absolute Maximum Ratings (Note 1, 2)**

at 25°C Free-Air Temperature and V<sub>SS</sub> = 0V

| Output Voltage                                     | 80V                        |

|----------------------------------------------------|----------------------------|

| Output Voltage, V <sub>CE(SUS)</sub> (Note 1)      | 50V                        |

| Logic Supply Voltage Range, VDD                    | 4.5V to 15V                |

| V <sub>DD</sub> with Reference to V <sub>EE</sub>  | 25V                        |

| Emitter Supply Voltage (Substrate), VEE            | -20V                       |

| Input Voltage Range, V <sub>IN</sub>               | $-0.3V$ to $V_{DD} + 0.3V$ |

| Package Power Dissipation, PD                      |                            |

| MIC58P42BN                                         | 1.82W                      |

| Derate above $T_{\Delta} = +25^{\circ}C$           | 18mW/°C                    |

| MIC58P42BV                                         | 1.4W                       |

| Derate above T <sub>A</sub> = +25°C<br>MIC58P42BWM | 14mW/°C                    |

| MIC58P42BWM                                        | 1.2W                       |

| Derate above T <sub>A</sub> = +25°C                | 12mW/°C                    |

| Operating Temperature Range, TA                    | -55°C to +125°C            |

| Storage Temperature Range, T <sub>S</sub>          | −65°C to +150°C            |

|                                                    |                            |

Note 1: For Inductive load applications.

Note 2: CMOS devices have input-static protection but are susceptible to damage when exposed to extremely high static electrical charges.

## **Typical Input Circuits**

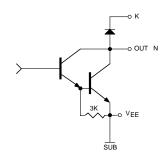

# **Typical Output Driver**

# **Pin Description**

| Pin          | Name                   | Description                                                                         |

|--------------|------------------------|-------------------------------------------------------------------------------------|

| (DIP & S.O.) |                        |                                                                                     |

| 1,9          | V <sub>EE</sub>        | Substrate. Most Negative voltage in the system connects here.                       |

| 2            | CLOCK                  | Serial Data Clock. A CLEAR input must also be clocked into the latches.             |

| 3            | SERIAL DATA IN         | Serial Data Input pin.                                                              |

| 4            | V <sub>SS</sub>        | Logic reference (Ground) pin.                                                       |

| 5            | V <sub>DD</sub>        | Logic Positive Supply voltage.                                                      |

| 6            | SERIAL DATA OUT        | Serial Data Output pin. (Flow-through).                                             |

| 7            | STROBE                 | Output Strobe pin. Loads output latches when high. Strobe is needed to clear latch. |

| 8            | OUTPUT<br>ENABLE/RESET | When Low, Outputs are active. When High, device is reset from a fault condition.    |

| 10           | K                      | Transient suppression diode's cathode common pin.                                   |

| 11—18        | OUTPUT N               | Open Collector outputs 8 through 1.                                                 |

# **Electrical Characteristics** at $T_A = +25$ °C, $V_{DD} = 5$ V, $V_{SS} = V_{EE} = 0$ V (unless otherwise noted)

|                                         |                        |                                                                                                                                                                     |                | Limits             |                    |      |  |  |

|-----------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|--------------------|------|--|--|

| Characteristic                          | Symbol                 | Test Conditions                                                                                                                                                     | Min.           | Тур.               | Max.               | Unit |  |  |

| Output Leakage Current                  | I <sub>CEX</sub>       | V <sub>OUT</sub> = 80V                                                                                                                                              |                |                    | 50                 | μΑ   |  |  |

|                                         |                        | V <sub>OUT</sub> = 80V, T <sub>A</sub> = +70°C                                                                                                                      |                |                    | 100                |      |  |  |

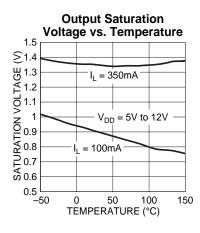

| Collector-Emitter<br>Saturation Voltage | V <sub>CE(SAT)</sub>   | I <sub>OUT</sub> = 100mA<br>I <sub>OUT</sub> = 200mA<br>I <sub>OUT</sub> = 350mA                                                                                    |                | 0.9<br>1.1<br>1.3  | 1.1<br>1.3<br>1.6  | V    |  |  |

| Collector-Emitter<br>Sustaining Voltage | V <sub>CE(SUS)</sub>   | I <sub>OUT</sub> = 350mA, L = 2mH                                                                                                                                   | 50             |                    |                    | V    |  |  |

| Input Voltage                           | V <sub>IN(0)</sub>     |                                                                                                                                                                     |                |                    | 1.0                | V    |  |  |

|                                         | V <sub>IN(1)</sub>     | $V_{DD} = 12V$<br>$V_{DD} = 10V$<br>$V_{DD} = 5.0V$ , <b>Note 1</b>                                                                                                 |                | 10.5<br>8.5<br>3.5 |                    |      |  |  |

| Input Resistance                        | R <sub>IN</sub>        | $V_{DD} = 12V$ $V_{DD} = 10V$ $V_{DD} = 5.0V$                                                                                                                       | 50<br>50<br>50 | 200<br>300<br>600  |                    | kΩ   |  |  |

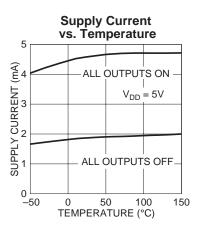

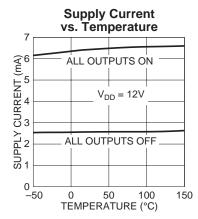

| Supply Current                          | I <sub>DD(ON)</sub>    | All Drivers ON, $V_{DD} = 12V$<br>All Drivers ON, $V_{DD} = 10V$<br>All Drivers ON, $V_{DD} = 5.0V$                                                                 |                | 6.4<br>6.0<br>4.6  | 10.0<br>9.0<br>7.5 | mA   |  |  |

|                                         | I <sub>DD (1 ON)</sub> | One Driver ON, All others OFF, V <sub>DD</sub> = 12V<br>One Driver ON, All others OFF, V <sub>DD</sub> = 10V<br>One Driver ON, All others OFF, V <sub>DD</sub> = 5V |                | 3.1<br>2.9<br>2.3  | 4.5<br>4.5<br>3.6  |      |  |  |

|                                         | I <sub>DD(OFF)</sub>   | All Drivers OFF, $V_{DD} = 12V$<br>All Drivers OFF, $V_{DD} = 10V$<br>All Drivers OFF, $V_{DD} = 5.0V$                                                              |                | 2.6<br>2.4<br>1.9  | 4.2<br>3.6<br>3.0  |      |  |  |

| Clamp Diode<br>Leakage Current          | I <sub>R</sub>         | V <sub>R</sub> = 80V                                                                                                                                                |                |                    | 50                 | μΑ   |  |  |

| Clamp Diode<br>Forward Voltage          | V <sub>F</sub>         | I <sub>F</sub> = 350mA                                                                                                                                              |                | 1.7                | 2.0                | V    |  |  |

| Output Current<br>Shutdown Threshold    | I <sub>LIM</sub>       |                                                                                                                                                                     |                | 500                |                    | mA   |  |  |

| Start Up Voltage                        | V <sub>SU</sub>        | Note 2                                                                                                                                                              | 3.5            | 4.0                | 4.5                | V    |  |  |

| Minimum Supply (V <sub>DD</sub> )       | V <sub>DD MIN</sub>    |                                                                                                                                                                     | 3.0            | 3.5                | 4.0                | V    |  |  |

| Thermal Shutdown                        |                        |                                                                                                                                                                     |                | 165                |                    | °C   |  |  |

| Thermal Shutdown Hysteresis             |                        |                                                                                                                                                                     |                | 10                 |                    | °C   |  |  |

Note 1: Operation of these devices with standard TTL or DTL may require the use of appropriate pull-up resistors to insure a minimum logic "1".

Note 2: Undervoltage Lockout is guaranteed to release device at no more than 4.5V, and disable the device at no less than 3.0V.

MIC58P42 Micrel

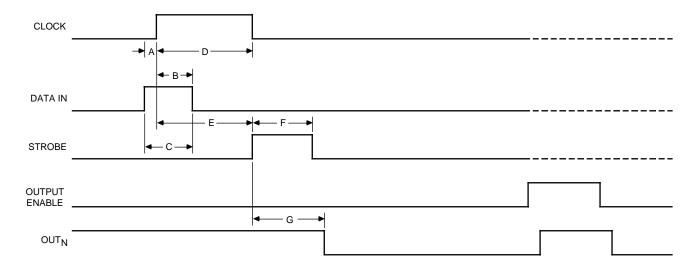

#### **Timing Conditions**

$(T_A = +25^{\circ}C, Logic Levels are V_{DD} and V_{SS}), V_{DD} = 5V$

| A. Typical Data Active Time Before Clock Pulse (Data Set-Up Time) | 75 ns  |

|-------------------------------------------------------------------|--------|

| B. Minimum Data Active Time After Clock Pulse (Data Hold Time)    |        |

| C. Minimum Data Pulse Width                                       | 150 ns |

| D. Minimum Clock Pulse Width                                      | 150 ns |

| E. Minimum Time Between Clock Activation and Strobe               | 300 ns |

| F. Minimum Strobe Pulse Width                                     | 100 ns |

| G. Typical Time Between Strobe Activation and Output Transition   | 500 ns |

SERIAL DATA present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.

Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the ENABLE input be high to prevent invalid output states.

When the ENABLE input is high, all of the output buffers are disabled (OFF) without affecting information <u>stored in the latches</u> or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches. A positive OUTPUT ENABLE/RESET pulse resets the output after a current shutdown fault. Thermal limit faults are not latched and require no reset pulse.

#### MIC58P42 Truth Table

|                      |                | Shift Register Contents |                | Serial         | Latch Contents |                |                 |                |                | Output Contents |  |                |                  |                |                |                |                |

|----------------------|----------------|-------------------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|-----------------|--|----------------|------------------|----------------|----------------|----------------|----------------|

| Serial Data<br>Input | Clock<br>Input | I <sub>1</sub>          | l <sub>2</sub> | l <sub>3</sub> | l <sub>8</sub> | Data<br>Output | Strobe<br>Input | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub>  |  | l <sub>8</sub> | Output<br>Enable | l <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | l <sub>8</sub> |

| Н                    |                | Н                       | R <sub>1</sub> | R <sub>2</sub> | R <sub>7</sub> | R <sub>7</sub> |                 |                |                |                 |  |                |                  |                |                |                |                |

| L                    |                | L                       | $R_1$          | R <sub>2</sub> | R <sub>7</sub> | R <sub>7</sub> |                 |                |                |                 |  |                |                  |                |                |                |                |

| Х                    |                | R1                      |                | R <sub>3</sub> |                | R <sub>8</sub> |                 |                |                |                 |  |                |                  |                |                |                |                |

|                      | 7              | 0                       | 0              | 0              | 0              | L              |                 |                |                |                 |  |                |                  |                |                |                |                |

|                      |                | Х                       | Х              | Χ              | Х              | Х              | L               | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub>  |  | R <sub>8</sub> |                  |                |                |                |                |

|                      |                | P <sub>1</sub>          | P <sub>2</sub> | P <sub>3</sub> | P <sub>8</sub> | P <sub>8</sub> | Н               | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub>  |  | P <sub>8</sub> | L                | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | P <sub>8</sub> |

|                      |                |                         |                |                |                |                |                 | Х              | Х              | Х               |  | Χ              | Н                | Н              | Н              | Н              | Н              |

L = Low Logic Level

H = High Logic Level

X = Irrelevant

P = Present State

R = Previous State

O = Output OFF

MIC58P42 Micrel

#### **Typical Characteristic Curves**

## Maximum Allowable Duty Cycle, Plastic DIP

V<sub>DD</sub> = 5.0V ┌

| Number of Outputs ON<br>(I <sub>OUT</sub> = 200mA | Max. | Allowable Duty | Cycle at Ambi | ent Temperat | ure of: |

|---------------------------------------------------|------|----------------|---------------|--------------|---------|

| $V_{DD} = 5.0V$ )                                 | 25°C | 40°C           | 50°C          | 60°C         | 70°C    |

| 8                                                 | 85%  | 72%            | 64%           | 55%          | 46%     |

| 7                                                 | 97%  | 82%            | 73%           | 63%          | 53%     |

| 6                                                 | 100% | 96%            | 85%           | 73%          | 62%     |

| 5                                                 | 100% | 100%           | 100%          | 88%          | 75%     |

| 4                                                 | 100% | 100%           | 100%          | 100%         | 93%     |

| 3                                                 | 100% | 100%           | 100%          | 100%         | 100%    |

| 2                                                 | 100% | 100%           | 100%          | 100%         | 100%    |

| 1                                                 | 100% | 100%           | 100%          | 100%         | 100%    |

$V_{DD} = 12V$

| Number of Outputs ON<br>(I <sub>OUT</sub> = 200mA | Max. Allowable Duty Cycle at Ambient Temperature of: |      |      |      |      |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------|------|------|------|------|--|--|--|--|

| V <sub>DD</sub> = 12V)                            | 25°C 40°C 50°C 60°C                                  |      |      |      |      |  |  |  |  |

| 8                                                 | 80%                                                  | 68%  | 60%  | 52%  | 44%  |  |  |  |  |

| 7                                                 | 91%                                                  | 77%  | 68%  | 59%  | 50%  |  |  |  |  |

| 6                                                 | 100%                                                 | 90%  | 79%  | 69%  | 58%  |  |  |  |  |

| 5                                                 | 100%                                                 | 100% | 95%  | 82%  | 69%  |  |  |  |  |

| 4                                                 | 100%                                                 | 100% | 100% | 100% | 86%  |  |  |  |  |

| 3                                                 | 100%                                                 | 100% | 100% | 100% | 100% |  |  |  |  |

| 2                                                 | 100%                                                 | 100% | 100% | 100% | 100% |  |  |  |  |

| 1                                                 | 100%                                                 | 100% | 100% | 100% | 100% |  |  |  |  |