# **MIC5013**

Protected High- or Low-Side MOSFET Driver

## **General Description**

The MIC5013 is an 8-pin MOSFET driver with over-current shutdown and a fault flag. It is designed to drive the gate of an N-channel power MOSFET above the supply rail high-side power switch applications. The MIC5013 is compatible with standard or current-sensing power MOSFETs in both high-and low-side driver topologies.

The MIC5013 charges a 1nF load in  $60\mu$ s typical and protects the MOSFET from over-current conditions. The current sense trip point is fully programmable and a dynamic threshold allows high in-rush current loads to be started. A fault pin indicates when the MIC5013 has turned off the FET due to excessive current.

Other members of the Micrel driver family include the MIC5011 minimum parts count driver and MIC5012 dual driver.

## Features

- 7V to 32V operation

- Less than 1µA standby current in the "OFF" state

- Available in small outline SOIC packages

- Internal charge pump to drive the gate of an N-channel power FET above supply

- Internal zener clamp for gate protection

- 60µs typical turn-on time to 50% gate overdrive

- Programmable over-current sensing

- · Dynamic current threshold for high in-rush loads

- · Fault output pin indicates current faults

- · Implements high- or low-side switches

## **Applications**

- · Lamp drivers

- Relay and solenoid drivers

- · Heater switching

- Power bus switching

- Motion control

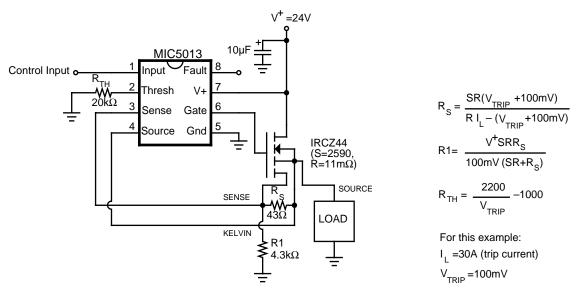

## **Typical Application**

#### **Ordering Information**

| Part Number | Temperature Range | Package           |  |  |

|-------------|-------------------|-------------------|--|--|

| MIC5013BN   | –40°C to +85°C    | 8-pin Plastic DIP |  |  |

| MIC5013BM   | –40°C to +85°C    | 8-pin SOIC        |  |  |

#### Figure 1. High-Side Driver with Current-Sensing MOSFET

Note: The MIC5013 is ESD sensitive.

Protected under one or more of the following Micrel patents: patent #4,951,101; patent #4,914,546

Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 • http://www.micrel.com

# Absolute Maximum Ratings (Note 1, 2)

| Input Voltage, Pin 1                    | -10 to V <sup>+</sup>  | Power Dissipation                       | 1.25W               |

|-----------------------------------------|------------------------|-----------------------------------------|---------------------|

| Threshold Voltage, Pin 2                | –0.5 to +5V            | $\theta_{IA}$ (Plastic DIP)             | 100°C/W             |

| Sense Voltage, Pin 3                    | -10V to V <sup>+</sup> | $\theta_{IA}$ (SOIC)                    | 170°C/W             |

| Source Voltage, Pin 4                   | -10V to V <sup>+</sup> | Ambient Temperature: B version          | –40°C to +85°C      |

| Current into Pin 4                      | 50mA                   | Storage Temperature                     | –65°C to +150°C     |

| Gate Voltage, Pin 6                     | -1V to 50V             | Lead Temperature                        | 260°C               |

| Supply Voltage (V <sup>+</sup> ), Pin 7 | -0.5V to 36V           | (Soldering, 10 seconds)                 |                     |

| Fault Output Current, Pin 8             | –1mA to +1mA           | Supply Voltage (V <sup>+</sup> ), Pin 7 | 7V to 32V high side |

| Junction Temperature                    | 150°C                  |                                         | 7V to 15V low side  |

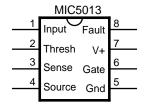

# Pin Description (Refer to Figures 1 and 2)

| Pin Number | Pin Name  | Pin Function                                                                                                                                                                                                                                       |  |  |  |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | Input     | Resets current sense latch and turns on power MOSFET when taken above threshold (3.5V typical). Pin 1 requires <1µA to switch.                                                                                                                     |  |  |  |

| 2          | Threshold | Sets current sense trip voltage according to:                                                                                                                                                                                                      |  |  |  |

|            |           | $V_{\text{TRIP}} = \frac{2200}{R_{\text{TH}} + 1000}$                                                                                                                                                                                              |  |  |  |

|            |           | where R <sub>TH</sub> to ground is 3.3k to $20k\Omega$ . Adding capacitor C <sub>TH</sub> increases the trip voltage at turn-on to 2V. Use C <sub>TH</sub> =10µF for a 10ms turn-on time constant.                                                 |  |  |  |

| 3          | Sense     | The sense pin causes the current sense to trip when $V_{SENSE}$ is $V_{TRIP}$ above $V_{SOURCE}$ . Pin 3 is used in conjunction with a current shunt in the source of a 3 lead FET or a resistor $R_S$ in the sense lead of a current sensing FET. |  |  |  |

| 4          | Source    | Reference for the current sense voltage on pin 3 and return for the gate clamp zener. Connect to the load side of current shunt or kelvin lead of current sensing FET. Pins 3 and 4 can safely swing to –10V when turning off inductive loads.     |  |  |  |

| 5          | Ground    |                                                                                                                                                                                                                                                    |  |  |  |

| 6          | Gate      | Drives and clamps the gate of the power FET. Pin 6 will be clamped to approximately –0.7V by an internal diode when turning off inductive loads.                                                                                                   |  |  |  |

| 7          | V+        | Supply pin; must be decoupled to isolate from large transients caused by the power FET drain. $10\mu$ F is recommended close to pins 7 and 5.                                                                                                      |  |  |  |

| 8          | Fault     | Outputs status of protection circuit when pin 1 is high. Fault low indicates normal operation; fault high indicates current sense tripped.                                                                                                         |  |  |  |

# **Pin Configuration**

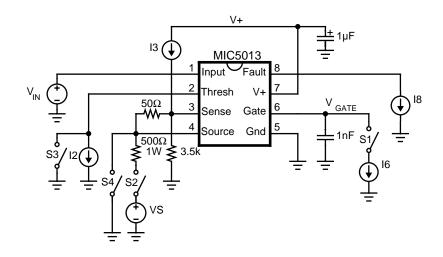

# **Electrical Characteristics** (Note 3) Test circuit. $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V^+ = 15V$ , all switches open, unless otherwise specified.

| Parameter                                                              | Conditions                                                                                |                                                   |                                 | Min | Typical | Max | Units |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------|-----|---------|-----|-------|

| Supply Current, I <sub>7</sub>                                         | V <sup>+</sup> = 32V                                                                      | V <sub>IN</sub> = 0V, S4 closed                   |                                 |     | 0.1     | 10  | μA    |

|                                                                        |                                                                                           | $V_{IN} = V_S = 32V$                              |                                 |     | 8       | 20  | mA    |

| Logic Input Voltage, V <sub>IN</sub>                                   | V <sup>+</sup> = 4.75V                                                                    | Adjust V <sub>IN</sub> for                        | V <sub>GATE</sub> low           |     |         | 2   | V     |

|                                                                        |                                                                                           | Adjust V <sub>IN</sub> for                        | V <sub>GATE</sub> high          | 4.5 |         |     | V     |

|                                                                        | V <sup>+</sup> =15V                                                                       | Adjust V <sub>IN</sub> for V <sub>GATE</sub> high |                                 | 5.0 |         |     | V     |

| Logic Input Current, I <sub>1</sub>                                    | V+ = 32V                                                                                  | $V_{IN} = 0V$                                     |                                 | -1  |         |     | μA    |

|                                                                        |                                                                                           | V <sub>IN</sub> = 32V                             |                                 |     |         | 1   | μA    |

| Input Capacitance                                                      | Pin 1                                                                                     |                                                   |                                 | 5   |         | pF  |       |

| Gate Drive, V <sub>GATE</sub>                                          | S1, S2 closed,                                                                            | $V^{+} = 7V, I_{6} = 0$                           |                                 | 13  | 15      |     | V     |

|                                                                        | $V_{S} = V+, V_{IN} = 5V$                                                                 | V <sup>+</sup> = 15V, I <sub>6</sub> =            | = 100 μA                        | 24  | 27      |     | V     |

| Zener Clamp,                                                           | S2 closed, V <sub>IN</sub> = 5V                                                           | V+ = 15V, V <sub>S</sub> = 15V                    |                                 | 11  | 12.5    | 15  | V     |

| V <sub>GATE</sub> – V <sub>SOURCE</sub>                                |                                                                                           | V <sup>+</sup> = 32V, V <sub>S</sub> = 32V        |                                 | 11  | 13      | 16  | V     |

| Gate Turn-on Time, t <sub>ON</sub><br>(Note 4)                         | V <sub>IN</sub> switched from 0 to 5V; measure time<br>for V <sub>GATE</sub> to reach 20V |                                                   |                                 |     | 60      | 200 | μs    |

| Gate Turn-off Time, t <sub>OFF</sub>                                   | V <sub>IN</sub> switched from 5 to 0V; measure time<br>for V <sub>GATE</sub> to reach 1V  |                                                   |                                 |     | 4       | 10  | μs    |

| Threshold Bias Voltage, V2                                             | l <sub>2</sub> = 200 μA                                                                   |                                                   |                                 | 1.7 | 2       | 2.2 | V     |

| Current Sense Trip Voltage,                                            | S2 closed, V <sub>IN</sub> = 5V,                                                          | V <sup>+</sup> = 7V,                              | S4 closed                       | 75  | 105     | 135 | mV    |

| V <sub>SENSE</sub> – V <sub>SOURCE</sub>                               | Increase I <sub>3</sub>                                                                   | I <sub>2</sub> = 100 μA                           | V <sub>S</sub> = 4.9V, S4 open  | 70  | 100     | 130 | mV    |

|                                                                        |                                                                                           | V <sup>+</sup> = 15V                              | S4 closed                       | 150 | 210     | 270 | mV    |

|                                                                        |                                                                                           | I <sub>2</sub> = 200 μA                           | V <sub>S</sub> = 11.8V, S4 open | 140 | 200     | 260 | mV    |

|                                                                        |                                                                                           | V <sup>+</sup> = 32V                              | V <sub>S</sub> = 0V, S4 open    | 360 | 520     | 680 | mV    |

|                                                                        |                                                                                           | I <sub>2</sub> = 500 μA                           | V <sub>S</sub> = 25.5V, S4 open | 350 | 500     | 650 | mV    |

| Peak Current Trip Voltage,<br>V <sub>SENSE</sub> – V <sub>SOURCE</sub> | S3, S4 closed,<br>$V^+ = 15V$ , $V_{IN} = 5V$                                             |                                                   | 1.6                             | 2.1 |         | V   |       |

| Fault Output Voltage, V <sub>8</sub>                                   | V <sub>IN</sub> = 0V, I <sub>8</sub> = -100 μA                                            | A                                                 |                                 |     | 0.4     | 1   | V     |

|                                                                        | $V_{IN} = 5V$ , $I_8 = 100 \mu$ A, current sense tripped                                  |                                                   |                                 | 14  | 14.6    |     | V     |

Note 1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device beyond its specified **Operating Ratings**.

Note 2 The MIC5010 is ESD sensitive.

**Note 3** Minimum and maximum **Electrical Characteristics** are 100% tested at  $T_A = 25^{\circ}C$  and  $T_A = 85^{\circ}C$ , and 100% guaranteed over the entire range. Typicals are characterized at 25°C and represent the most likely parametric norm.

Note 4 Test conditions reflect worst case high-side driver performance. Low-side and bootstrapped topologies are significantly faster—see Applications Information.

# **Test Circuit**

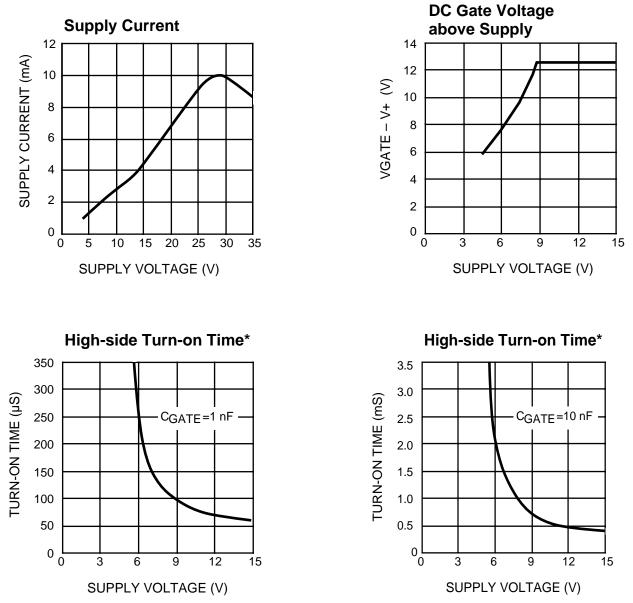

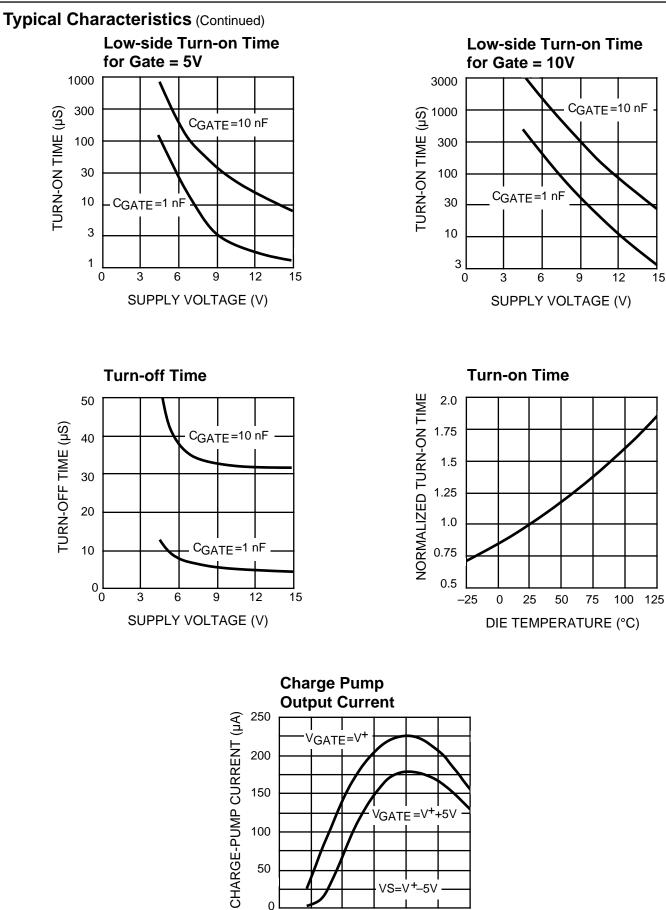

# **Typical Characteristics**

\* Time for gate to reach V<sup>+</sup> + 5V in test circuit with VS = V<sup>+</sup> - 5V (prevents gate clamp from interfering with measurement).

10

15

SUPPLY VOLTAGE (V)

25

20

30

0

5

Micrel

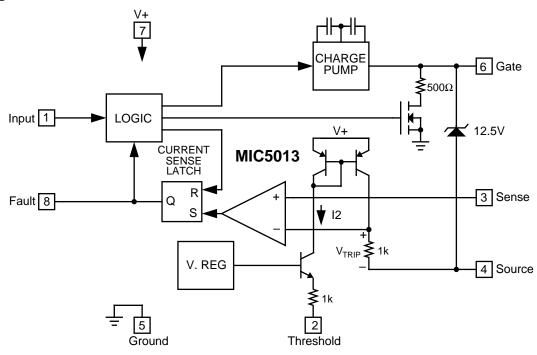

## **Block Diagram**

# **Applications Information**

#### Functional Description (refer to block diagram)

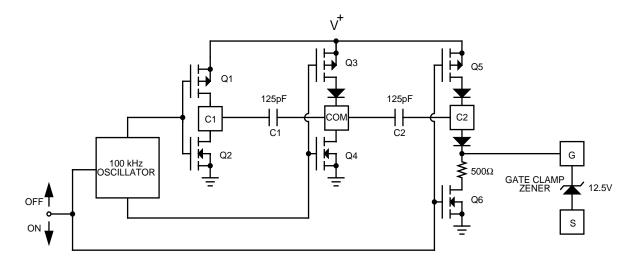

The various MIC5013 functions are controlled via a logic block connected to the input pin 1. When the input is low, all functions are turned off for low standby current and the gate of the power MOSFET is also held low through  $500\Omega$  to an N-channel switch. When the input is taken above the turn-on threshold (3.5V typical), the N-channel switch turns off and the charge pump is turned on to charge the gate of the power FET. A bandgap type voltage regulator is also turned on which biases the current sense circuitry.

The charge pump incorporates a 100kHz oscillator and onchip pump capacitors capable of charging 1nF to 5V above supply in 60 $\mu$ s typical. The charge pump is capable of pumping the gate up to over twice the supply voltage. For this reason, a zener clamp (12.5V typical) is provided between the gate pin 6 and source pin 4 to prevent exceeding the V<sub>GS</sub> rating of the MOSFET at high supplies.

The current sense operates by comparing the sense voltage at pin 3 to an offset version of the source voltage at pin 4. Current I2 flowing in threshold pin 2 is mirrored and returned to the source via a 1k $\Omega$  resistor to set the offset, or trip voltage. When (V<sub>SENSE</sub> – V<sub>SOURCE</sub>) exceeds V<sub>TRIP</sub>, the current sense trips and sets the current sense latch to turn off the power FET. An integrating comparator is used to reduce sensitivity to spikes on pin 3. The latch is reset to turn the FET back on by "recycling" the input pin 1 low and then high again.

A resistor R<sub>TH</sub> from pin 2 to ground sets I2, and hence V<sub>TRIP</sub>. An additional capacitor C<sub>TH</sub> from pin 2 to ground creates a higher trip voltage at turn-on, which is necessary to prevent high in-rush current loads such as lamps or capacitors from false-tripping the current sense. When the current sense has tripped, the fault pin 8 will be high as long as the input pin 1 remains high. However, when the input is low the fault pin will also be low.

#### **Construction Hints**

High current pulse circuits demand equipment and assembly techniques that are more stringent than normal low current lab practices. The following are the sources of pitfalls most often encountered during prototyping: Supplies: many bench power supplies have poor transient response. Circuits that are being pulse tested, or those that operate by pulse-width modulation will produce strange results when used with a supply that has poor ripple rejection, or a peaked transient response. Monitor the power supply voltage that appears at the drain of a highside driver (or the supply side of the load in a low-side driver) with an oscilloscope. It is not uncommon to find bench power supplies in the 1kW class that overshoot or undershoot by as much as 50% when pulse loaded. Not only will the load current and voltage measurements be affected, but it is possible to over-stress various components-especially electrolytic capacitors-with possibly catastrophic results. A 10µF supply bypass capacitor at the chip is recommended.

Residual Resistances: Resistances in circuit connections may also cause confusing results. For example, a circuit may employ a 50m $\Omega$  power MOSFET for low drop, but careless construction techniques could easily add 50 to 100m $\Omega$  resistance. Do not use a socket for the MOSFET. If the MOSFET is a TO-220 type package, make high-current drain connections to the tab. Wiring losses have a profound effect on high-current circuits. A floating millivoltmeter can identify connections that are contributing excess drop under load.

Figure 2. Low-Side Driver with Current Shunt

#### **Circuit Topologies**

The MIC5013 is suited for use in high- or low-side driver applications with over-current protection for both currentsensing and standard MOSFETs. In addition, the MIC5013 works well in applications where, for faster switching times, the supply is bootstrapped from the MOSFET source output. Low voltage, high-side drivers (such as shown in the Test Circuit) are the slowest; their speed is reflected in the gate turn-on time specifications. The fastest drivers are the low-side and bootstrapped high-side types. Load current switching times are often much faster than the time to full gate enhancement, depending on the circuit type, the MOSFET, and the load. Turn-off times are essentially the same for all circuits (less than  $10\mu$ s to V<sub>GS</sub> = 1V). The choice of one topology over another is based on a combination of considerations including speed, voltage, and desired system characteristics. Each topology is described in this section. Note that I<sub>1</sub>, as used in the design equations, is the load current that just trips the over-current comparator.

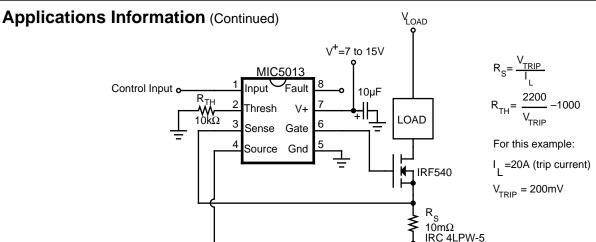

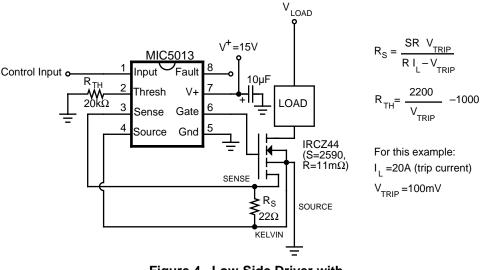

Low-Side Driver with Current Shunt (Figure 2). The over-

current comparator monitors RS and trips if  $I_L \times R_S$  exceeds  $V_{TRIP}$ . R is selected to produce the desired trip voltage.

(International Resistive Company)

As a guideline, keep  $V_{TRIP}$  within the limits of 100mV and 500mV ( $R_{TH} = 3.3k\Omega$  to 20k $\Omega$ ). Thresholds at the high end offer the best noise immunity, but also compromise switch drop (especially in low voltage applications) and power dissipation.

The trip current is set higher than the maximum expected load current—typically twice that value. Trip point accuracy is a function of resistor tolerances, comparator offset (only a few millivolts), and threshold bias voltage (V2). The values shown in Figure 2 are designed for a trip current of 20 amperes. It is important to ground pin 4 at the current shunt  $R_S$ , to eliminate the effects of ground resistance.

A key advantage of the low-side topology is that the load supply is limited only by the MOSFET BVDSS rating. Clamping may be required to protect the MOSFET drain terminal from inductive switching transients. The MIC5013

with Current Shunt

Figure 4. Low-Side Driver with Current-Sensing MOSFET

supply should be limited to 15V in low-side topologies; otherwise, a large current will be forced through the gate clamp zener.

Low-side drivers constructed with the MIC501X family are also fast; the MOSFET gate is driven to near supply immediately when commanded ON. Typical circuits achieve 10V enhancement in  $10\mu$ s or less on a 12 to 15V supply.

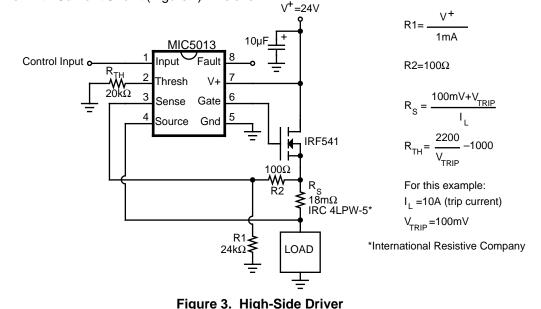

**High-Side Driver with Current Shunt** (Figure 3). The comparator input pins (source and sense) float with the current sensing resistor ( $R_S$ ) on top of the load. R1 and R2 add a small, additional potential to  $V_{TRIP}$  to prevent false-triggering of the over-current shutdown circuit with open or inductive loads. R1 is sized for a current flow of 1mA, while R2 contributes a drop of 100mV. The shunt voltage should be 200 to 500mV at the trip point. The example of Figure 3 gives a 10A trip current when the output is near supply. The trip point is somewhat reduced when the output is at ground as the voltage drop across R1 (and therefore R2) is zero.

High-side drivers implemented with MIC5013 drivers are self-protected against inductive switching transients. During turn-off an inductive load will force the MOSFET source 5V or more below ground, while the driver holds the gate at ground potential. The MOSFET is forced into conduction, and it dissipates the energy stored in the load inductance. The MIC5013 source and sense pins (3 and 4) are designed to withstand this negative excursion without damage. External clamp diodes are unnecessary.

Current Shunts (R<sub>S</sub>). Low-valued resistors are necessary for use at R<sub>S</sub>.Values for R<sub>S</sub> range from 5 to 50m $\Omega$ , at 2 to 10W. Worthy of special mention are Kelvin-sensed, "fourterminal" units supplied by a number of manufacturers<sup>†</sup> (see next page). Kelvin-sensed resistors eliminate errors caused by lead and terminal resistances, and simplify product assembly. 10% tolerance is normally adequate, and with shunt potentials of 200mV thermocouple effects are insignificant. Temperature coefficient is important; a linear, 500 ppm/°C change will contribute as much as 10% shift in the over-current trip point. Most power resistors designed for current shunt service drift less than 100 ppm/ °C.

Low-Side Driver with Current Sensing MOSFET (Figure 4). Several manufacturers now supply power MOSFETs in which a small sampling of the total load current is diverted to a "sense" pin. One additional pin, called "Kelvin source," is included to eliminate the effects of resistance in the source bond wires. Current-sensing MOSFETs are specified with a sensing ratio "S" which describes the relationship between the on-resistance of the sense connection and the body resistance "R" of the main source pin. Current sensing MOSFETs eliminate the current shunt required by standard MOSFETs.

The design equations for a low-side driver using a current sensing MOSFET are shown in Figure 4. "S" is specified on the MOSFET's datasheet, and "R" must be measured or estimated.  $V_{TRIP}$  must be less than  $R \times I_L$ , or else  $R_S$  will become negative. Substituting a MOSFET with higher on-resistance, or reducing  $V_{TRIP}$  fixes this problem.  $V_{TRIP}$  = 100 to 200mV is suggested. Although the load supply is limited only by MOSFET ratings, the MIC5013 supply should be limited to 15V to prevent damage to the gate clamp zener. Output clamping is necessary for inductive loads.

"R" is the body resistance of the MOSFET, excluding bond resistances.  $R_{DS(ON)}$  as specified on MOSFET data sheets

† Suppliers of Kelvin-sensed power resistors:

Dale Electronics, Inc., 2064 12th Ave., Columbus, NE 68601. Tel: (402) 564-3131 International Resistive Co., P.O. Box 1860, Boone, NC 28607-1860. Tel: (704) 264-8861 Kelvin, 14724 Ventura Blvd., Ste. 1003, Sherman Oaks, CA 91403-3501. Tel: (818) 990-1192 RCD Components, Inc., 520 E. Industrial Pk. Dr., Manchester, NH 03103. Tel: (603) 669-0054 Ultronix, Inc., P.O. Box 1090, Grand Junction, CO 81502. Tel: (303) 242-0810

7 to 15V 1N5817 1N4001 (2) MIC5013 Control Input Fault nput 10µF V-100nF 3 Gate Sense Gnd Source IRF540 100Ω R2 R κ<sub>s</sub> 18mΩ LOAD 1mA Ŧ Figure 6. Bootstrapped High-Side Driver

Micrel

includes bond resistances. A Kelvin-connected ohmmeter (using TAB and SOURCE for forcing, and SENSE and KELVIN for sensing) is the best method of evaluating "R." Alternatively, "R" can be estimated for large MOSFETs ( $R_{DS(ON)} \le 100m\Omega$ ) by simply halving the stated  $R_{DS(ON)}$ , or by subtracting 20 to 50m $\Omega$  from the stated  $R_{DS(ON)}$  for smaller MOSFETs.

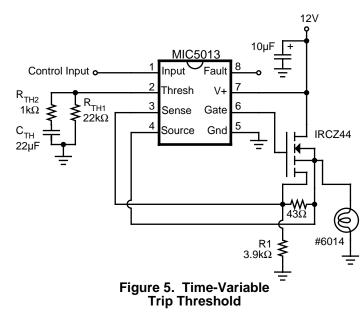

**High-Side Driver with Current Sensing MOSFET** (Figure 5). The design starts by determining the value of "S" and "R" for the MOSFET (use the guidelines described for the low-side version). Let  $V_{TRIP} = 100$ mV, and calculate  $R_S$  for a desired trip current. Next calculate  $R_{TH}$  and R1. The trip point is somewhat reduced when the output is at ground as the voltage drop across R1 is zero. No clamping is required for inductive loads, but may be added to reduce power dissipation in the MOSFET.

#### **Typical Applications**

Start-up into a Dead Short. If the MIC5013 attempts to turn on a MOSFET when the load is shorted, a very high current flows. The over-current shutdown will protect the MOSFET, but only after a time delay of 5 to 10 $\mu$ s. The MOSFET must be capable of handling the overload; consult the device's SOA curve. If a short circuit causes the MOSFET to exceed its 10 $\mu$ s SOA, a small inductance in series with the source can help limit di/dt to control the peak current during the 5 to 10 $\mu$ s delay.

When testing short-circuit behavior, use a current probe rated for both the peak current and the high di/dt.

The over-current shutdown delay varies with comparator overdrive, owing to noise filtering in the comparator. A delay of up to  $100\mu s$  can be observed at the threshold of shutdown. A 20% overdrive reduces the delay to near minimum.

**Incandescent Lamps**. The cold filament of an incandescent lamp exhibits less than one-tenth as much resistance as when the filament is hot. The initial turn-on current of a #6014 lamp is about 70A, tapering to 4.4A after a few

hundred milliseconds. It is unwise to set the over-current trip point to 70A to accommodate such a load. A "resistive" short that draws less than 70A could destroy the MOSFET by allowing sustained, excessive dissipation. If the over-current trip point is set to less than 70A, the MIC5013 will not start a cold filament. The solution is to start the lamp with a high trip point, but reduce this to a reasonable value after the lamp is hot.

The MIC5013 over-current shutdown circuit is designed to handle this situation by varying the trip point with time (see Figure 5).  $R_{TH1}$  functions in the conventional manner, providing a current limit of approximately twice that required by the lamp.  $R_{TH2}$  acts to increase the current limit at turn-on to approximately 10 times the steady-state lamp current. The high initial trip point decays away according to a 20ms time constant contributed by  $C_{TH}$ .  $R_{TH2}$  could be eliminated with  $C_{TH}$  working against the internal 1k $\Omega$  resistor, but this results in a very high over-current threshold. As a rule of thumb design the over-current circuitry in the conventional manner, then add the  $R_{TH2}/C_{TH}$  network to allow for lamp start-up. Let  $R_{TH2} = (R_{TH1} \div 10) - 1k\Omega$ , and choose a capacitor that provides the desired time constant working against  $R_{TH2}$  and the internal 1k $\Omega$  resistor.

When the MIC5013 is turned off, the threshold pin (2) appears as an open circuit, and  $C_{TH}$  is discharged through  $R_{TH1}$  and  $R_{TH2}$ . This is much slower than the turn-on time constant, and it simulates the thermal response of the filament. If the lamp is pulse-width modulated, the current limit will be reduced by the residual charge left in  $C_{TH}$ .

**Modifying Switching Times**. Do not add external capacitors to the gate to slow down the switching time. Add a resistor ( $1k\Omega$  to  $51k\Omega$ ) in series with the gate of the MOS-FET to achieve this result.

**Bootstrapped High-Side Driver** (Figure 6). The speed of a high-side driver can be increased to better than  $10\mu s$  by bootstrapping the supply off of the MOSFET source. This topology can be used where the load is pulse-width modu10mA Control Input

## Applications Information (Continued)

4N35

100kΩ

**≷**1kΩ

Figure 8. Improved

**Opto-Isolator Performance**

lated (100Hz to 20kHz), or where it is energized for only a short period of time ( $\leq$ 25ms). If the load is left energized for a long period of time (>25ms), the bootstrap capacitor will discharge and the MIC5013 supply pin will fall to V+ = V<sub>DD</sub> -1.4. Under this condition pins 3 and 4 will be held above V+ and may false trigger the over-current circuit. A larger capacitor will lengthen the maximum "on" time; 1000µF will hold the circuit up for 2.5 seconds, but requires more charge time when the circuit is turned off. The optional Schottky barrier diode improves turn-on time on supplies of less than 10V.

Since the supply current in the "OFF" state is only a small leakage, the 100nF bypass capacitor tends to remain charged for several seconds after the MIC5013 is turned off. In a PWM application the chip supply is actually much higher than the system supply, which improves switching time.

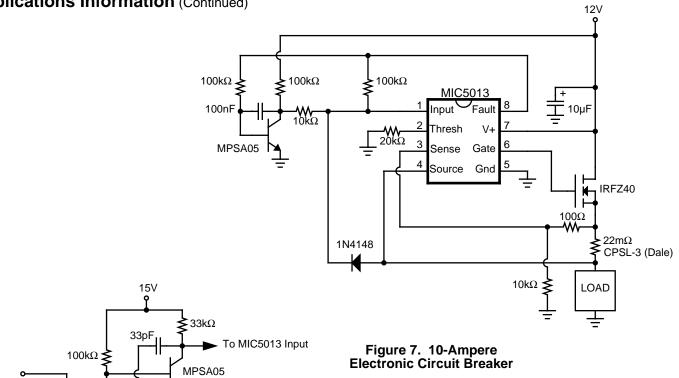

**Electronic Circuit Breaker** (Figure 7). The MIC5013 forms the basis of a high-performance, fast-acting circuit breaker. By adding feedback from FAULT to INPUT the breaker can be made to automatically reset. If an over-current condition occurs, the circuit breaker shuts off. The breaker tests the load every 18ms until the short is removed, at which time the circuit latches ON. No reset button is necessary.

**Opto-Isolated Interface** (Figure 8). Although the MIC5013 has no special input slew rate requirement, the lethargic transitions provided by an opto-isolator may cause oscillations on the rise and fall of the output. The circuit shown accelerates the input transitions from a 4N35 opto-isolator by adding hysteresis. Opto-isolators are used where the control circuitry cannot share a common ground with the MIC5013 and high-current power supply, or where the control circuitry is located remotely. This implementation is intrinsically safe; if the control line is severed the MIC5013 will turn OFF.

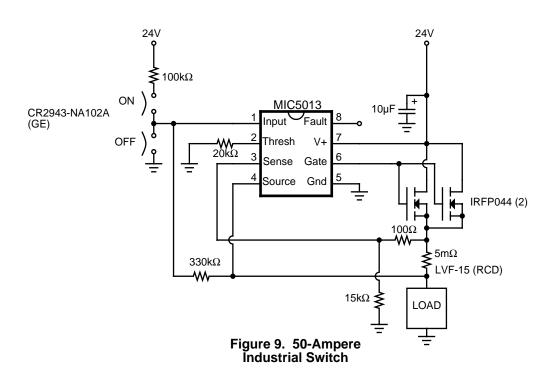

**Fault-Protected Industrial Switch** (Figure 9). The most common manual control for industrial loads is a push button on/off switch. The "on" button is physically arranged in a recess so that in a panic situation the "off" button, which extends out from the control box, is more easily pressed. This circuit is compatible with control boxes such as the CR2943 series (GE). The circuit is configured so that if both switches close simultaneously, the "off" button has precedence. If there is a fault condition the circuit will latch off, and it can be reset by pushing the "ON" button.

This application also illustrates how two (or more) MOSFETs can be paralleled. This reduces the switch drop, and distributes the switch dissipation into multiple packages.

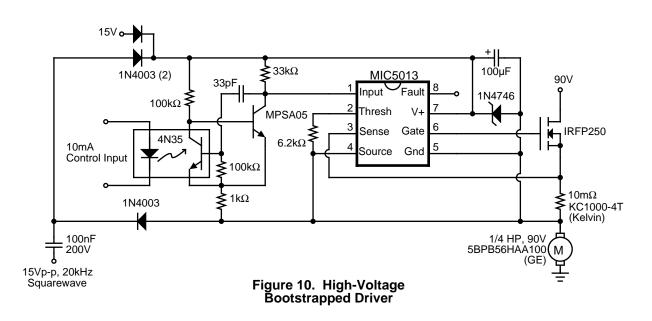

**High-Voltage Bootstrap** (Figure 10). Although the MIC5013 is limited to operation on 7 to 32V supplies, a floating bootstrap arrangement can be used to build a high-side switch that operates on much higher voltages. The MIC5013 and MOSFET are configured as a low-side driver, but the load is connected in series with ground. The high speed normally associated with low-side drivers is retained in this circuit.

Power for the MIC5013 is supplied by a charge pump. A 20kHz square wave (15Vp-p) drives the pump capacitor and delivers current to a  $100\mu$ F storage capacitor. A zener diode limits the supply to 18V. When the MIC5013 is off, power is supplied by a diode connected to a 15V supply. The circuit of Figure 8 is put to good use as a barrier between low voltage control circuitry and the 90V motor supply.

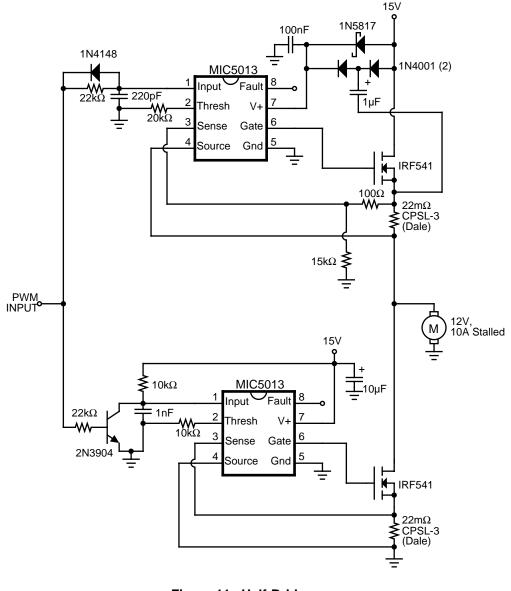

Half-Bridge Motor Driver (Figure 11). Closed loop control of motor speed requires a half-bridge driver. This topology presents an extra challenge since the two output devices should not cross conduct (shoot-through) when switching. Cross conduction increases output device power dissipation and, in the case of the MIC5013, could trip the overcurrent comparator. Speed is also important, since PWM control requires the outputs to switch in the 2 to 20kHz range.

The circuit of Figure 11 utilizes fast configurations for both the top- and bottom-side drivers. Delay networks at each input provide a 2 to  $3\mu$ s dead time effectively eliminating cross conduction. Both the top- and bottom-side drivers are protected, so the output can be shorted to either rail without damage.

The top-side driver is based on the bootstrapped circuit of Figure 6, and cannot be switched on indefinitely. The bootstrap capacitor (1 $\mu$ F) relies on being pulled to ground by the bottom-side output to recharge. This limits the maximum duty cycle to slightly less than 100%.

Two of these circuits can be connected together to form an H-bridge. If the H-bridge is used for locked antiphase control, no special considerations are necessary. In the case of sign/magnitude control, the "sign" leg of the Hbridge should be held low (PWM input held low) while the other leg is driven by the magnitude signal.

If current feedback is required for torque control, it is available in chopped form at the bottom-side driver's  $22 \text{ m}\Omega$  current-sensing resistor.

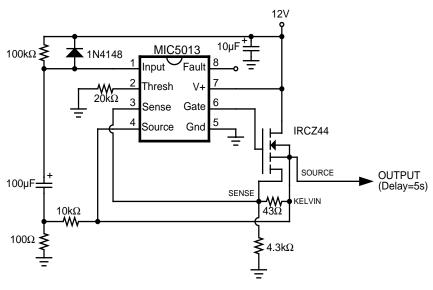

**Time-Delay Relay** (Figure 12). The MIC5013 forms the basis of a simple time-delay relay. As shown, the delay commences when power is applied, but the  $100 \text{ k}\Omega/1\text{N}4148$  could be independently driven from an external source such

as a switch or another high-side driver to give a delay relative to some other event in the system.

Hysteresis has been added to guarantee clean switching at turn-on. Note that an over-current condition latches the relay in a safe, OFF condition. Operation is restored by either cycling power or by momentarily shorting pin 1 to ground.

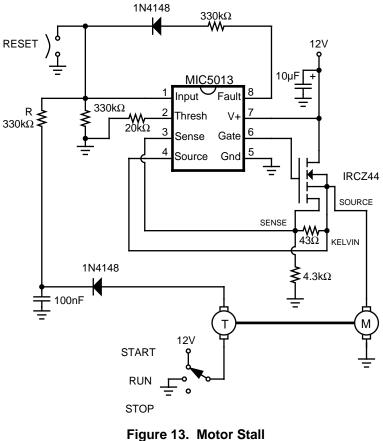

**Motor Driver with Stall Shutdown** (Figure 13). Tachometer feedback can be used to shut down a motor driver circuit when a stall condition occurs. The control switch is a 3-way type; the "START" position is momentary and forces the driver ON. When released, the switch returns to the "RUN" position, and the tachometer's output is used to hold the MIC5013 input ON. If the motor slows down, the tach output is reduced, and the MIC5013 switches OFF. Resistor "R" sets the shutdown threshold. If the output current exceeds 30A, the MIC5013 shuts down and remains in that condition until the momentary "RESET" button is pushed. Control is then returned to the START/RUN/STOP switch.

Figure 11. Half-Bridge Motor Driver

Shutdown

When applying the MIC5010, it is helpful to understand the operation of the gate control circuitry (see Figure 14). The gate circuitry can be divided into two sections: 1) charge pump (oscillator, Q1-Q5, and the capacitors) and 2) gate turn-off switch (Q6).

When the MIC5010 is in the OFF state, the oscillator is turned off, thereby disabling the charge pump. Q5 is also turned off, and Q6 is turned on. Q6 holds the gate pin (G) at ground potential which effectively turns the external MOS-FET off.

Q6 is turned off when the MIC5013 is commanded on. Q5 pulls the gate up to supply (through 2 diodes). Next, the charge pump begins supplying current to the gate. The gate accepts charge until the gate-source voltage reaches 12.5V and is clamped by the zener diode.

A 2-output, three-phase clock switches Q1-Q4, providing a quasi-tripling action. During the initial phase Q4 and Q2 are ON. C1 is discharged, and C2 is charged to supply through

Q5. For the second phase Q4 turns off and Q3 turns on, pushing pin C2 above supply (charge is dumped into the gate). Q3 also charges C1. On the third phase Q2 turns off and Q1 turns on, pushing the common point of the two capacitors above supply. Some of the charge in C1 makes its way to the gate. The sequence is repeated by turning Q2 and Q4 back on, and Q1 and Q3 off.

Micrel

In a low-side application operating on a 12 to 15V supply, the MOSFET is fully enhanced by the action of Q5 alone. On supplies of more than approximately 14V, current flows directly from Q5 through the zener diode to ground. To prevent excessive current flow, the MIC5010 supply should be limited to 15V in low-side applications.

The action of Q5 makes the MIC5013 operate quickly in low-side applications. In high-side applications Q5 precharges the MOSFET gate to supply, leaving the charge pump to carry the gate up to full enhancement 10V above supply. Bootstrapped high-side drivers are as fast as lowside drivers since the chip supply is boosted well above the drain at turn-on.

Figure 14. Gate Control Circuit Detail

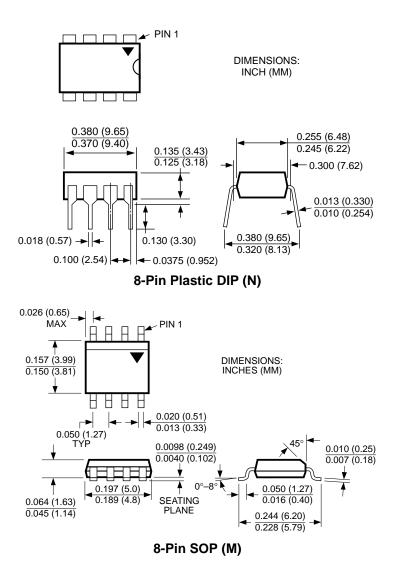

# **Package Information**

### MICREL INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 1998 Micrel Incorporated