# **Stream** 33 × 17, 1.5 Gbps Digital Crosspoint Switch

AD8150\*

#### **FEATURES**

**Low Cost**

33 imes 17, Fully Differential, Nonblocking Array

>1.5 Gbps per Port NRZ Data Rate

Wide Power Supply Range: +5 V, +3.3 V, -3.3 V, -5 V

**Low Power**

400 mA (Outputs Enabled)

30 mA (Outputs Disabled)

PECL and ECL Compatible

CMOS/TTL-Level Control Inputs: 3 V to 5 V

Low Jitter: <50 ps p-p

No Heat Sinks Required

Drives a Backplane Directly

Programmable Output Current

Optimize Termination Impedance

User-Controlled Voltage at the Load Minimize Power Dissipation

Individual Output Disable for Busing and Building

Larger Arrays

Double Row Latch

Buffered Inputs

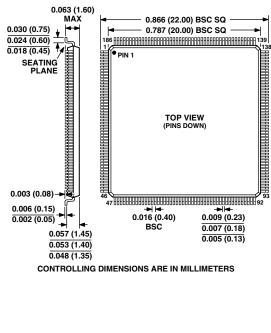

Available in 184-Lead LQFP

APPLICATIONS

HD and SD Digital Video

Fiber Optic Network Switching

#### PRODUCT DESCRIPTION

AD8150 is a member of the X stream line of products and is a breakthrough in digital switching, offering a large switch array  $(33 \times 17)$  on very little power, typically less than 1.5 W. Additionally, it operates at data rates in excess of 1.5 Gbps per port, making it suitable for HDTV applications. Further, the pricing of the AD8150 makes it affordable enough to be used for SD applications as well. The AD8150 is also useful for OC-24 optical network switching.

The AD8150's flexible supply voltages allow the user to operate with either PECL or ECL data levels and will operate down to 3.3~V for further power reduction. The control interface is CMOS/TTL compatible (3~V to 5~V).

Its fully differential signal path reduces jitter and crosstalk while allowing the use of smaller single-ended voltage swings.

The AD8150 is offered in a 184-lead LQFP package that operates over the industrial temperature range of 0°C to 85°C.

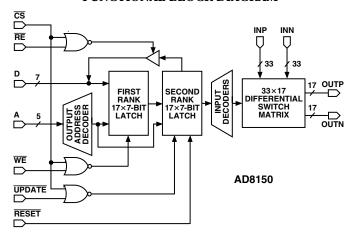

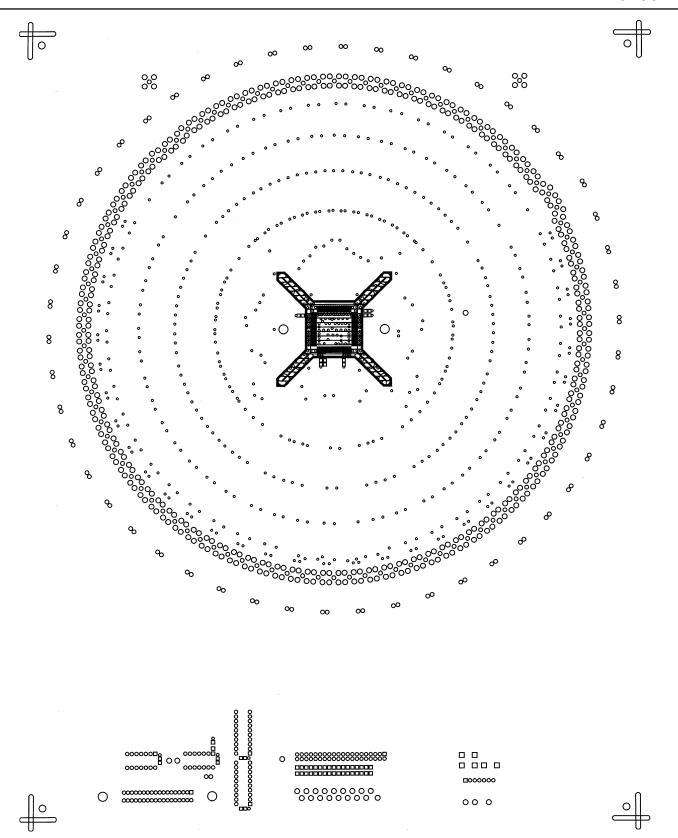

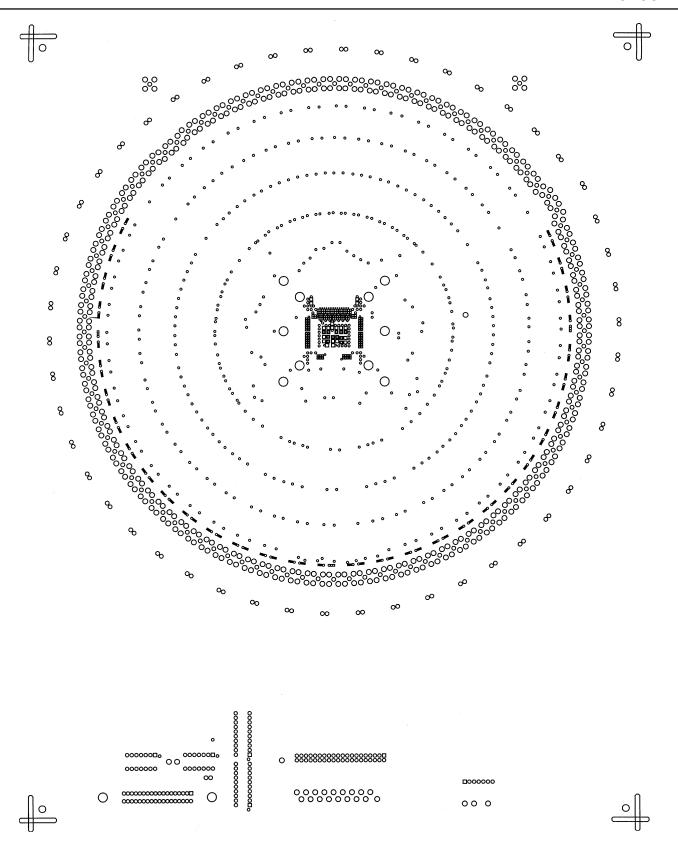

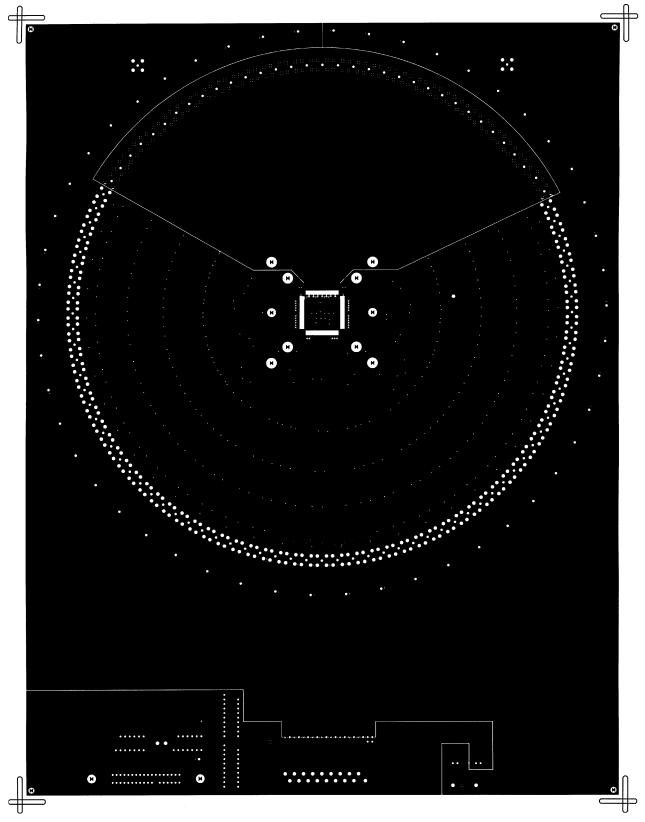

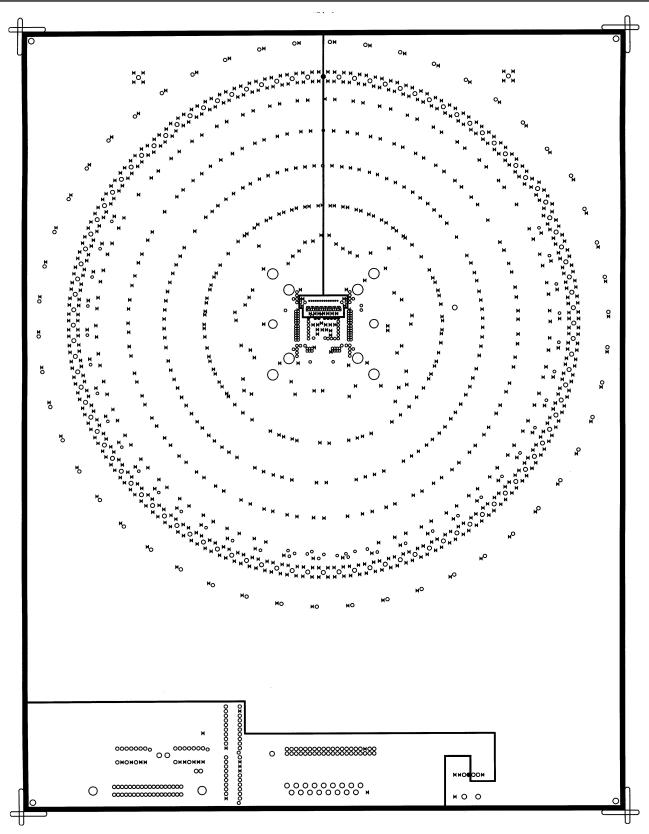

#### FUNCTIONAL BLOCK DIAGRAM

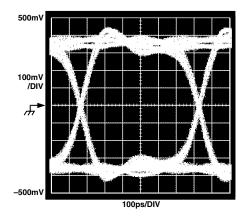

Figure 1. Output Eye Pattern, 1.5 Gbps

X stream is a trademark of Analog Devices, Inc.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

<sup>\*</sup>Patent Pending.

# $\textbf{AD8150-SPECIFICATIONS} \ \ ^{\text{(@ 25°C, V_{CC} = 3.3 V to 5 V, V_{EE} = 0 V, R_L = 50 } \Omega \ \ \text{(see Figure 22), I}_{\text{OUT}} = 16 \text{ mA, unless otherwise noted)}$

| Parameter                                                                                                                                               | Conditions                                                               | Min                                                                                    | Тур                          | Max                                                    | Unit                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------|------------------------------|

| DYNAMIC PERFORMANCE Max Data Rate/Channel (NRZ) Channel Jitter RMS Channel Jitter Propagation Delay Propagation Delay Match Output Rise/Fall Time       | Data Rate < 1.5 Gbps  V <sub>CC</sub> = 5 V  Input to Output  20% to 80% | 1.5                                                                                    | 50<br>10<br>650<br>50<br>100 | 100                                                    | Gbps ps p-p ps ps ps ps ps   |

| INPUT CHARACTERISTICS Input Voltage Swing Input Voltage Range Input Bias Current Input Capacitance Input V <sub>IN</sub> High Input V <sub>IN</sub> Low | Differential<br>Common-Mode                                              | $\begin{array}{c} 200 \\ V_{CC} - 2 \\ \\ V_{CC} - 1.2 \\ V_{CC} - 2.4 \\ \end{array}$ | 2 2                          | $1000 \\ V_{CC} \\ \\ V_{CC} - 0.2 \\ V_{CC} - 1.4 \\$ | mV p-p<br>V<br>μA<br>pF<br>V |

| OUTPUT CHARACTERISTICS Output Voltage Swing Output Voltage Range Output Current Output Capacitance                                                      | Differential (See Figure 22)                                             | V <sub>CC</sub> - 1.8                                                                  | 800                          | V <sub>CC</sub> 25                                     | mV p-p<br>V<br>mA<br>pF      |

| POWER SUPPLY Operating Range PECL, $V_{CC}$ ECL, $V_{EE}$ $V_{DD}$ $V_{SS}$ Quiescent Current $V_{DD}$ $V_{EE}$                                         | $V_{EE}$ = 0 V $V_{CC}$ = 0 V                                            | 3.3<br>-5<br>3                                                                         | 0<br>2<br>400                | 5<br>-3.3<br>5                                         | V<br>V<br>V<br>V<br>mA<br>mA |

| THERMAL CHARACTERISTICS Operating Temperature Range                                                                                                     | All Outputs Disabled                                                     | 0                                                                                      | 30                           | 85                                                     | mA<br>°C                     |

| $\frac{\theta_{JA}}{LOGIC\ INPUT\ CHARACTERISTICS}\\ Input\ V_{IN}\ High\\ Input\ V_{IN}\ Low$                                                          | $V_{DD}$ = 3 V dc to 5 V dc                                              | 1.9                                                                                    | 30                           | V <sub>DD</sub> 0.9                                    | °C/W<br>V<br>V               |

-2- REV. 0

#### ABSOLUTE MAXIMUM RATINGS1

Supply Waltage V

NOTES

| Supply voltage $v_{DD} - v_{EE}$ 10.5 v            |

|----------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>            |

| AD8150 184-Lead Plastic LQFP (ST) 4.2 W            |

| Differential Input Voltage $\dots V_{CC} - V_{EE}$ |

| Output Short Circuit Duration                      |

| Observe Power Derating Curves                      |

| Storage Temperature Range65°C to +125°C            |

| Lead Temperature Range (Soldering 10 sec) 300°C    |

|                                                    |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

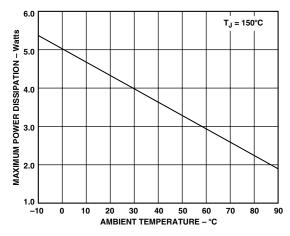

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8150 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8150 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves shown in Figure 2.

10 5 W

Figure 2. Maximum Power Dissipation vs. Temperature

#### **ORDERING GUIDE**

| Description           | Option |

|-----------------------|--------|

| 184-Lead Plastic LQFP | ST-184 |

| ` '                   |        |

|                       | •      |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8150 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

$<sup>^2</sup>$ Specification is for device in free air ( $T_A = 25^{\circ}C$ ):

<sup>184-</sup>lead plastic LQFP (ST):  $\theta_{JA} = 30^{\circ}$ C/W.

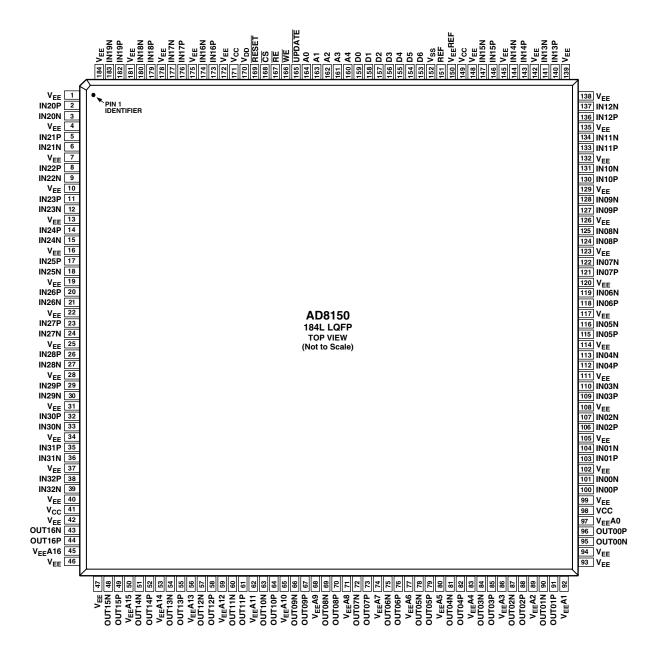

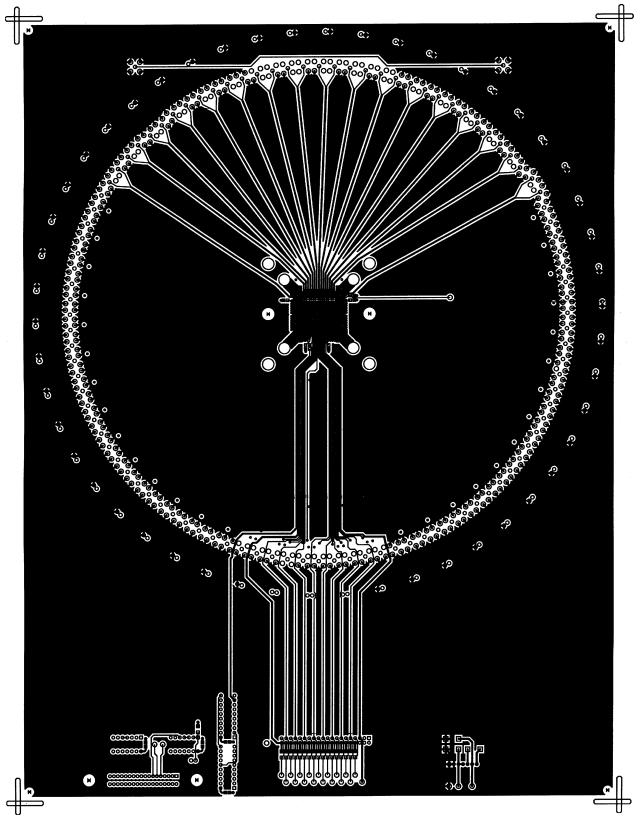

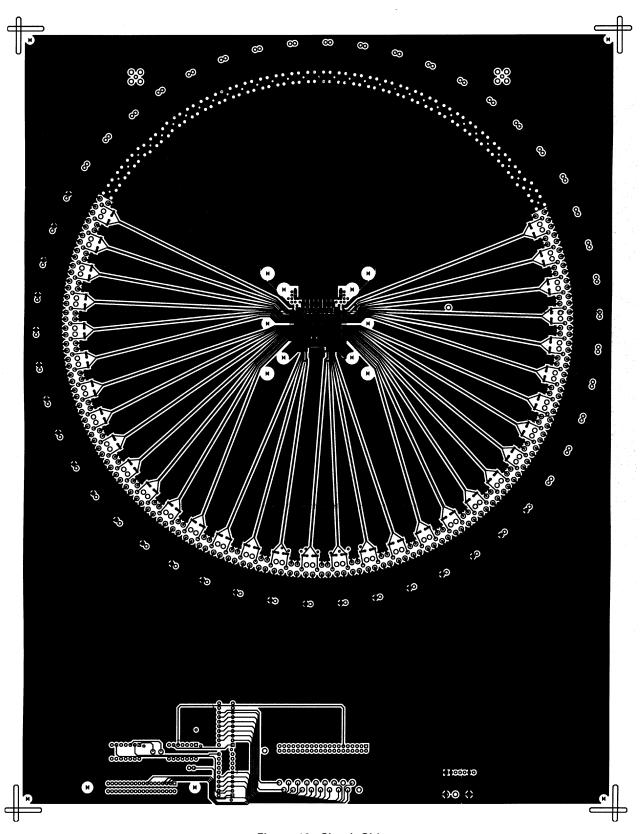

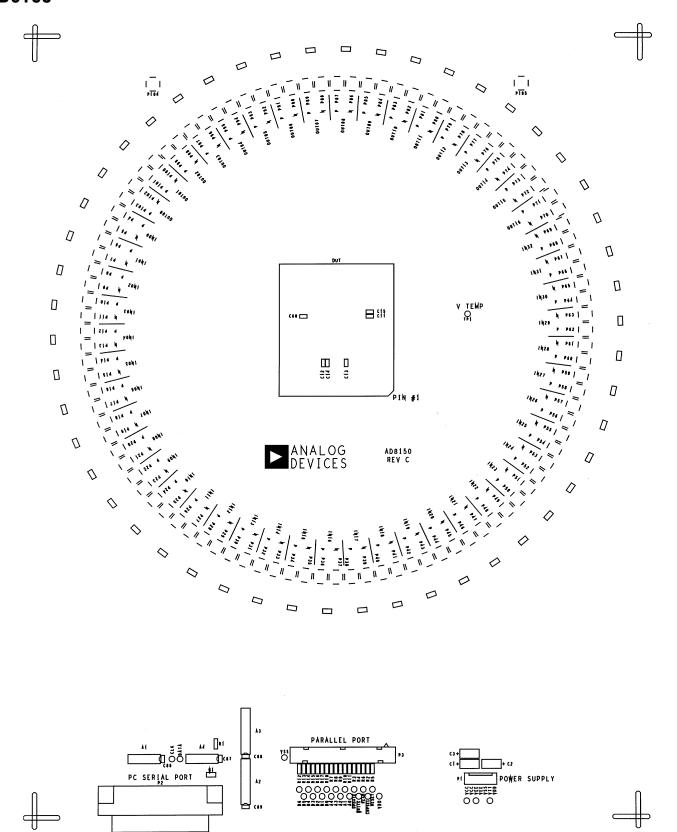

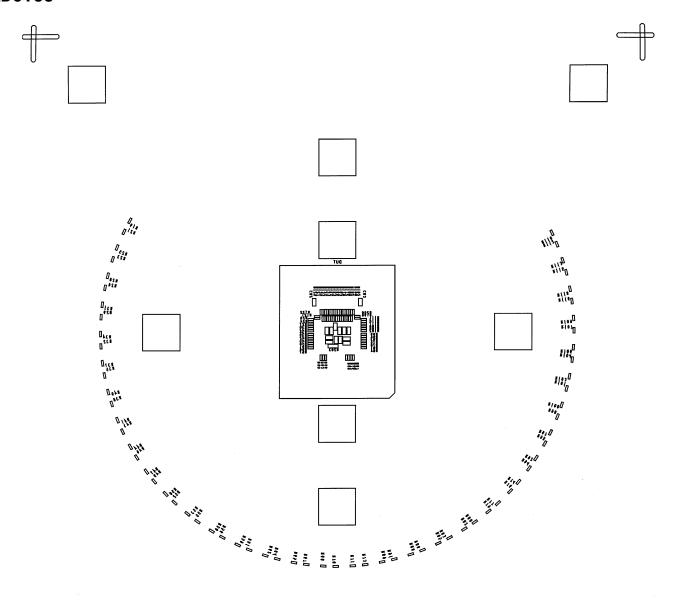

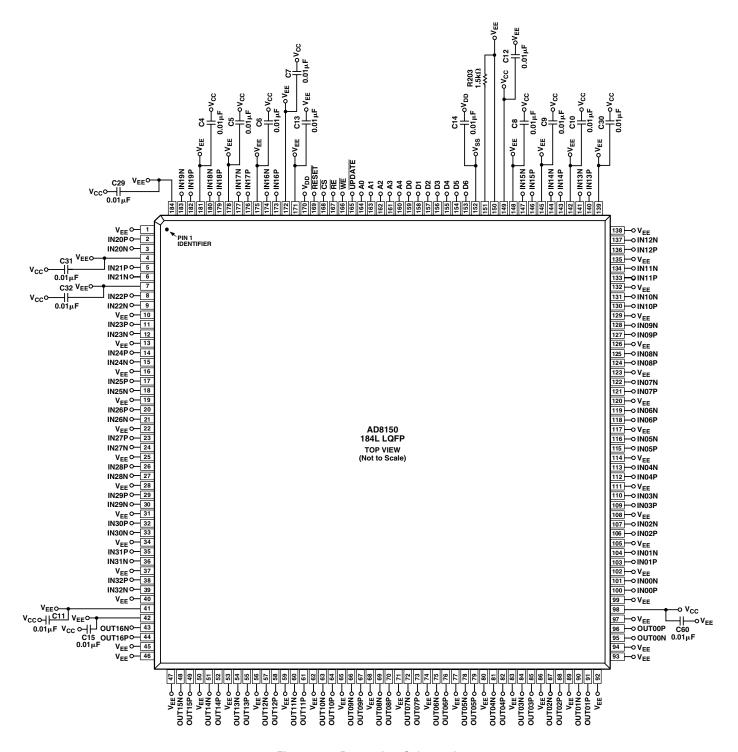

#### PIN CONFIGURATION

-4- REV. 0

#### PIN FUNCTION DESCRIPTIONS

| Pin No.                                                                                                                                                                                   | Signal              | Type         | Description                                                                   |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|-------------------------------------------------------------------------------|--|--|--|--|

| 1, 4, 7, 10, 13, 16, 19, 22, 25, 28, 31, 34, 37, 40, 42, 46, 47, 92, 93, 99, 102, 105, 108, 111, 114, 117, 120, 123, 126, 129, 132, 135, 138, 139, 142, 145, 148, 172, 175, 178, 181, 184 | $V_{\rm EE}$        | Power Supply | Most Negative PECL Supply (Common with Other Points Labeled $V_{\text{EE}}$ ) |  |  |  |  |

| 2                                                                                                                                                                                         | IN20P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 3                                                                                                                                                                                         | IN20N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 5                                                                                                                                                                                         | IN21P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 6                                                                                                                                                                                         | IN21N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 8                                                                                                                                                                                         | IN22P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 9                                                                                                                                                                                         | IN22N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 11                                                                                                                                                                                        | IN23P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 12                                                                                                                                                                                        | IN23N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 14                                                                                                                                                                                        | IN24P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 15                                                                                                                                                                                        | IN24N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 17                                                                                                                                                                                        | IN25P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 18                                                                                                                                                                                        | IN25N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 20                                                                                                                                                                                        | IN26P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 21                                                                                                                                                                                        | IN26N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 23                                                                                                                                                                                        | IN27P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 24                                                                                                                                                                                        | IN27N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 26                                                                                                                                                                                        | IN28P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 27                                                                                                                                                                                        | IN28N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 29                                                                                                                                                                                        | IN29P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 30                                                                                                                                                                                        | IN29N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 32                                                                                                                                                                                        | IN30P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 33                                                                                                                                                                                        | IN30N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 35                                                                                                                                                                                        | IN31P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 36                                                                                                                                                                                        | IN31N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 38                                                                                                                                                                                        | IN32P               | PECL         | High-Speed Input                                                              |  |  |  |  |

| 39                                                                                                                                                                                        | IN32N               | PECL         | High-Speed Input Complement                                                   |  |  |  |  |

| 41, 98, 149, 171                                                                                                                                                                          | $V_{CC}$            | Power Supply | Most Positive PECL Supply (Common with Other Points Labeled $V_{CC}$ )        |  |  |  |  |

| 43                                                                                                                                                                                        | OUT16N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 44                                                                                                                                                                                        | OUT16P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| 45                                                                                                                                                                                        | $V_{EE}A16$         | Power Supply | Most Negative PECL Supply (Unique to This Output)                             |  |  |  |  |

| 48                                                                                                                                                                                        | OUT15N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 49                                                                                                                                                                                        | OUT15P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| 50                                                                                                                                                                                        | $V_{EE}A15$         | Power Supply | Most Negative PECL Supply (Unique to this Output)                             |  |  |  |  |

| 51                                                                                                                                                                                        | OUT14N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 52                                                                                                                                                                                        | OUT14P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| 53                                                                                                                                                                                        | V <sub>EE</sub> A14 | Power Supply | Most Negative PECL Supply (Unique to this Output)                             |  |  |  |  |

| 54                                                                                                                                                                                        | OUT13N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 55                                                                                                                                                                                        | OUT13P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| 56                                                                                                                                                                                        | V <sub>EE</sub> A13 | Power Supply | Most Negative PECL Supply (Unique to this Output)                             |  |  |  |  |

| 57                                                                                                                                                                                        | OUT12N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 58                                                                                                                                                                                        | OUT12P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| 59                                                                                                                                                                                        | $V_{EE}A12$         | Power Supply | Most Negative PECL Supply (Unique to this Output)                             |  |  |  |  |

| 60                                                                                                                                                                                        | OUT11N              | PECL         | High-Speed Output Complement                                                  |  |  |  |  |

| 61                                                                                                                                                                                        | OUT11P              | PECL         | High-Speed Output                                                             |  |  |  |  |

| ·                                                                                                                                                                                         |                     |              | 9F                                                                            |  |  |  |  |

REV. 0 -5-

| Pin No. | Signal              | Type         | Description                                       |

|---------|---------------------|--------------|---------------------------------------------------|

| 62      | V <sub>EE</sub> A11 | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 63      | OUT10N              | PECL         | High-Speed Output Complement                      |

| 64      | OUT10P              | PECL         | High-Speed Output                                 |

| 65      | V <sub>EE</sub> A10 | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 66      | OUT09N              | PECL         | High-Speed Output Complement                      |

| 67      | OUT09P              | PECL         | High-Speed Output                                 |

| 68      | V <sub>EE</sub> A9  | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 69      | OUT08N              | PECL         | High-Speed Output Complement                      |

| 70      | OUT08P              | PECL         | High-Speed Output                                 |

| 71      | $V_{EE}A8$          | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 72      | OUT07N              | PECL         | High-Speed Output Complement                      |

| 73      | OUT07P              | PECL         | High-Speed Output                                 |

| 74      | $V_{EE}A7$          | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 75      | OUT06N              | PECL         | High-Speed Output Complement                      |

| 76      | OUT06P              | PECL         | High-Speed Output                                 |

| 77      | V <sub>EE</sub> A6  | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 78      | OUT05N              | PECL         | High-Speed Output Complement                      |

| 79      | OUT05P              | PECL         | High-Speed Output                                 |

| 80      | $V_{EE}A5$          | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 81      | OUT04N              | PECL         | High-Speed Output Complement                      |

| 82      | OUT04P              | PECL         | High-Speed Output                                 |

| 83      | $V_{EE}A4$          | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 84      | OUT03N              | PECL         | High-Speed Output Complement                      |

| 85      | OUT03P              | PECL         | High-Speed Output                                 |

| 86      | V <sub>EE</sub> A3  | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 87      | OUT02N              | PECL         | High-Speed Output Complement                      |

| 88      | OUT02P              | PECL         | High-Speed Output                                 |

| 89      | V <sub>EE</sub> A2  | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 90      | OUT01N              | PECL         | High-Speed Output Complement                      |

| 91      | OUT01P              | PECL         | High-Speed Output                                 |

| 94      | V <sub>EE</sub> A1  | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 95      | OUT00N              | PECL         | High-Speed Output Complement                      |

| 96      | OUT00P              | PECL         | High-Speed Output                                 |

| 97      | $V_{EE}A0$          | Power Supply | Most Negative PECL Supply (Unique to this Output) |

| 100     | IN00P               | PECL         | High-Speed Input                                  |

| 101     | IN00N               | PECL         | High-Speed Input Complement                       |

| 103     | IN01P               | PECL         | High-Speed Input                                  |

| 104     | IN01N               | PECL         | High-Speed Input Complement                       |

| 106     | IN02P               | PECL         | High-Speed Input                                  |

| 107     | IN02N               | PECL         | High-Speed Input Complement                       |

| 109     | IN03P               | PECL         | High-Speed Input                                  |

| 110     | IN03N               | PECL         | High-Speed Input Complement                       |

| 112     | IN04P               | PECL         | High-Speed Input                                  |

| 113     | IN04N               | PECL         | High-Speed Input Complement                       |

| 115     | IN05P               | PECL         | High-Speed Input                                  |

| 116     | IN05N               | PECL         | High-Speed Input Complement                       |

| 118     | IN06P               | PECL         | High-Speed Input                                  |

| 119     | IN06N               | PECL         | High-Speed Input Complement                       |

| 121     | IN07P               | PECL         | High-Speed Input  High-Speed Input                |

| 122     | IN07N               | PECL         | High-Speed Input Complement                       |

-6- REV. 0

| Pin No. | Signal        | Type         | Description                                                                                           |

|---------|---------------|--------------|-------------------------------------------------------------------------------------------------------|

| 124     | IN08P         | PECL         | High-Speed Input                                                                                      |

| 125     | IN08N         | PECL         | High-Speed Input Complement                                                                           |

| 127     | IN09P         | PECL         | High-Speed Input                                                                                      |

| 128     | IN09N         | PECL         | High-Speed Input Complement                                                                           |

| 130     | IN10P         | PECL         | High-Speed Input                                                                                      |

| 131     | IN10N         | PECL         | High-Speed Input Complement                                                                           |

| 133     | IN11P         | PECL         | High-Speed Input                                                                                      |

| 134     | IN11N         | PECL         | High-Speed Input Complement                                                                           |

| 136     | IN12P         | PECL         | High-Speed Input                                                                                      |

| 137     | IN12N         | PECL         | High-Speed Input Complement                                                                           |

| 140     | IN13P         | PECL         | High-Speed Input                                                                                      |

| 141     | IN13N         | PECL         | High-Speed Input Complement                                                                           |

| 143     | IN14P         | PECL         | High-Speed Input                                                                                      |

| 144     | IN14N         | PECL         | High-Speed Input Complement                                                                           |

| 146     | IN15P         | PECL         | High-Speed Input                                                                                      |

| 147     | IN15N         | PECL         | High-Speed Input Complement                                                                           |

| 150     | $V_{EE}REF$   | R-Program    | Connection Point for Output Logic Pull-Down Programming Resistor (Must be Connected to $V_{\rm EE}$ ) |

| 151     | REF           | R-Program    | Connection Point for Output Logic Pull-Down<br>Programming Resistor                                   |

| 152     | $V_{SS}$      | Power Supply | Most Negative Control Logic Supply                                                                    |

| 153     | D6            | TTL          | Enable/Disable Output                                                                                 |

| 154     | D5            | TTL          | (32) MSB Input Select                                                                                 |

| 155     | D4            | TTL          | (16)                                                                                                  |

| 156     | D3            | TTL          | (8)                                                                                                   |

| 157     | D2            | TTL          | (4)                                                                                                   |

| 158     | D1            | TTL          | (2)                                                                                                   |

| 159     | D0            | TTL          | (1) LSB Input Select                                                                                  |

| 160     | A4            | TTL          | (16) MSB Output Select                                                                                |

| 161     | A3            | TTL          | (8)                                                                                                   |

| 162     | A2            | TTL          | (4)                                                                                                   |

| 163     | A1            | TTL          | (2)                                                                                                   |

| 164     | A0            | TTL          | (1) LSB Output Select                                                                                 |

| 165     | <u>UPDATE</u> | TTL          | Second Rank Program                                                                                   |

| 166     | WE            | TTL          | First Rank Program                                                                                    |

| 167     | RE            | TTL          | Enable Readback                                                                                       |

| 168     | CS            | TTL          | Enable Chip to Accept Programming                                                                     |

| 169     | RESET         | TTL          | Disable All Outputs (Hi-Z)                                                                            |

| 170     | $ m V_{DD}$   | Power Supply | Most Positive Control Logic Supply                                                                    |

| 173     | IN16P         | PECL         | High-Speed Input                                                                                      |

| 174     | IN16N         | PECL         | High-Speed Input Complement                                                                           |

| 176     | IN17P         | PECL         | High-Speed Input                                                                                      |

| 177     | IN17N         | PECL         | High-Speed Input Complement                                                                           |

| 179     | IN18P         | PECL         | High-Speed Input                                                                                      |

| 180     | IN18N         | PECL         | High-Speed Input Complement                                                                           |

| 182     | IN19P         | PECL         | High-Speed Input                                                                                      |

| 183     | IN19N         | PECL         | High-Speed Input Complement                                                                           |

REV. 0 -7-

### **AD8150**—Typical Performance Characteristics

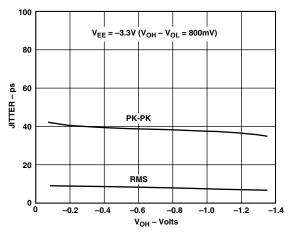

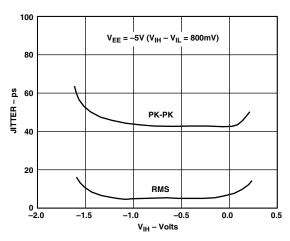

Figure 3. Jitter vs.  $V_{OH}$  1.5 Gbps, PRBS 23

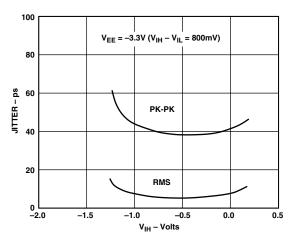

Figure 4. Jitter vs. V<sub>IH</sub> 1.5 Gbps, PRBS 23

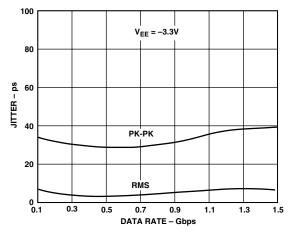

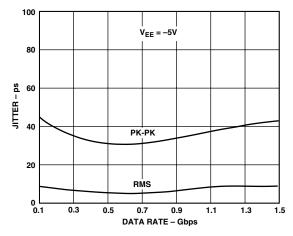

Figure 5. Jitter vs. Data Rate, PRBS 23

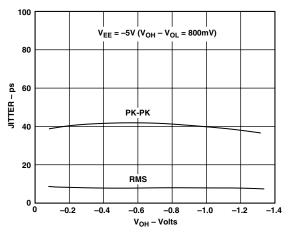

Figure 6. Jitter vs.  $V_{OH}$  1.5 Gbps, PRBS 23

Figure 7. Jitter vs. V<sub>IH</sub> 1.5 Gbps, PRBS 23

Figure 8. Jitter vs. Data Rate, PRBS 23

\_8\_ REV. 0

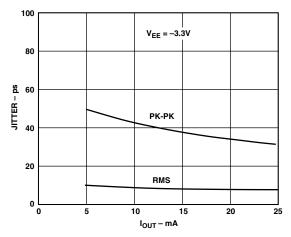

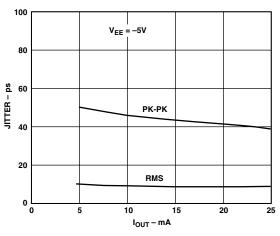

Figure 9. Jitter vs. I<sub>OUT</sub> 1.5 Gbps, PRBS 23

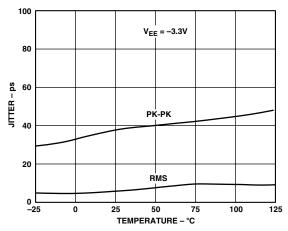

Figure 10. Jitter vs. Temperature 1.5 Gbps, PRBS 23

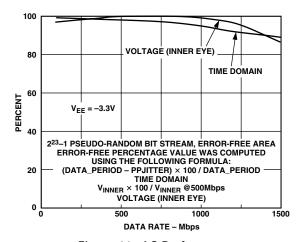

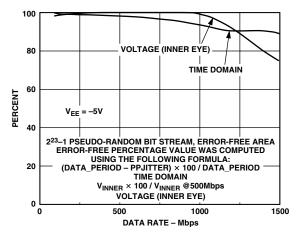

Figure 11. AC Performance

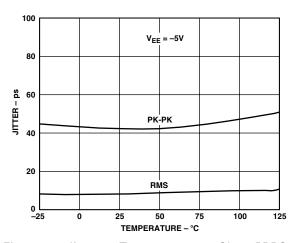

Figure 12. Jitter vs. I<sub>OUT</sub> 1.5 Gbps, PRBS 23

Figure 13. Jitter vs. Temperature 1.5 Gbps, PRBS 23

Figure 14. AC Performance

REV. 0 \_9\_

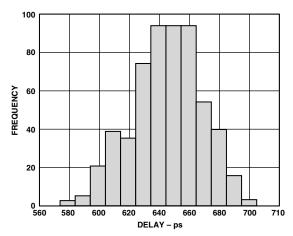

Figure 15. Variation in Channel-to-Channel Delay, All 561 Points

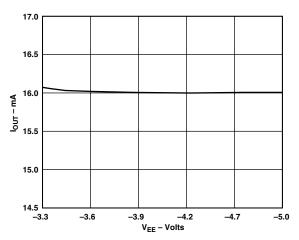

Figure 16.  $I_{OUT}$  vs. Supply,  $V_{EE}$

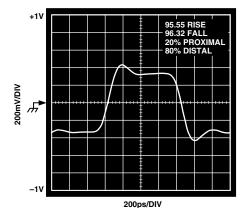

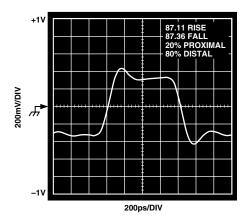

Figure 17. Rise/Fall Times,  $V_{EE} = -3.3 \text{ V}$

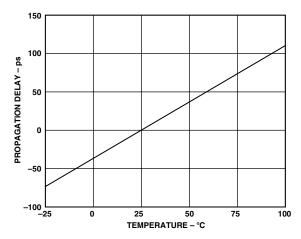

Figure 18. Propagation Delay, Normalized at 25°C vs. Temperature

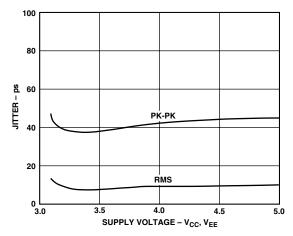

Figure 19. Jitter vs. Supply, 1.5 Gbps, PRBS 23

Figure 20. Rise/Fall Times,  $V_{EE} = -5 V$

-10- REV. 0

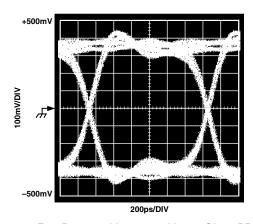

Figure 21. Eye Pattern,  $V_{EE} = -3.3 \text{ V}$ , 1.5 Gbps PRBS 23

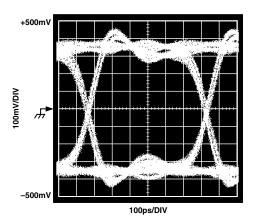

Figure 23. Eye Pattern,  $V_{EE} = -5 V$ , 1.5 Gbps PRBS 23

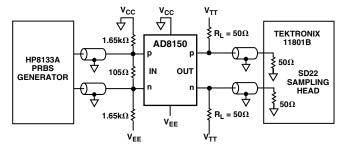

$V_{CC}=0V,~V_{EE}=-3.3V~OR-5V,~V_{TT}=-1.6V$   $R_{SET}=1.54k\Omega,~I_{OUT}=16mA,~V_{OH}=-0.8V,~V_{OL}=-1.8V$  INTRINSIC JITTER OF HP8133A AND TEKTRONIX 11801B = 3ps RMS, 17ps PK-PK

Figure 22. Eye Pattern Test Circuit

REV. 0 -11-

#### **Control Interface Truth Tables**

The following are truth tables for the control interface.

**Table I. Basic Control Functions**

|       |    | Conti | ol Pins |        |                                                                                                                                                                             |

|-------|----|-------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset | CS | WE    | RE      | Update | Function                                                                                                                                                                    |

| 0     | X  | X     | X       | X      | Global Reset. Reset all second rank enable bits to zero (disable all outputs).                                                                                              |

| 1     | 1  | X     | X       | X      | Control Disable. Ignore all logic (but the signal matrix still functions as programmed). D[6:0] are high-impedance.                                                         |

| 1     | 0  | 0     | X       | X      | Single Output Preprogram. Write input configuration data from data bus D[6:0]. into first rank of latches for the output selected by the output address bus A[4:0].         |

| 1     | 0  | X     | 0       | X      | Single Output Readback. Readback input configuration data from second rank of latches onto data bus D[6:0] for the single output selected by the output address bus A[4:0]. |

| 1     | 0  | X     | X       | 0      | Global Update. Copy input configuration data from all 17 first rank latches into second rank of latches, updating signal matrix connections for all outputs.                |

| 1     | 0  | 0     | 1       | 0      | Transparent Write and Update. It is possible to write data directly onto rank two. This simplifies logic when synchronous signal matrix updating is not necessary.          |

Table II. Address/Data Examples

| (                                                                                                                                                                                                              | •         | t Add<br>SB-LS | ress P<br>SB                         | ins  | Enable<br>Bit |                                                                                                                                                                           | •  | t Add<br>ASB-l |                                                                                                                                     | Pins |    |                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------------------------------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------|-------------------------------------------------------------------------------------------------------------------------------------|------|----|--------------------------------------------------------------------------------------------------------------------|

| <b>A</b> 4                                                                                                                                                                                                     | <b>A3</b> | A2             | A1                                   | A0   | D6/E          | D5                                                                                                                                                                        | D4 | <b>D</b> 3     | D2                                                                                                                                  | D1   | D0 | Function                                                                                                           |

| 0                                                                                                                                                                                                              | 0         | 0              | 0                                    | 0    | X             | 0                                                                                                                                                                         | 0  | 0              | 0                                                                                                                                   | 0    | 0  | Lower Address/Data Range. Connect Output #00 (A[4:0] = 00000) to Input #00 (D[5:0] = 000000).                      |

| 1                                                                                                                                                                                                              | 0         | 0              | 0                                    | 0    | X             | 1                                                                                                                                                                         | 0  | 0              | 0                                                                                                                                   | 0    | 0  | Upper Address/Data Range. Connect Output #16 (A[4:0] = 10000) to Input #32 (D[5:0] = 100000).                      |

| <binary number*="" output=""></binary>                                                                                                                                                                         |           | 1              | <binary input="" number=""></binary> |      |               |                                                                                                                                                                           |    |                | Enable Output. Connect Selected Output $(A[4:0] = 0$ to 16) to Designated Input $(D[5:0] = 0$ to 32) and Enable Output $(D6 = 1)$ . |      |    |                                                                                                                    |

| <bir< td=""><td>nary O</td><td>utput</td><td>Numl</td><td>er*&gt;</td><td>0</td><td>X</td><td>X</td><td>X</td><td>X</td><td>X</td><td>X</td><td>Disable Output. Disable Specified Output (D6 = 0).</td></bir<> | nary O    | utput          | Numl                                 | er*> | 0             | X                                                                                                                                                                         | X  | X              | X                                                                                                                                   | X    | X  | Disable Output. Disable Specified Output (D6 = 0).                                                                 |

| 1                                                                                                                                                                                                              | 0         | 0              | 0                                    |      |               | Broadcast Connection. Connect all 17 outputs to same designated input and set all 17 enable bits to the value of D6. Readback is not possible with the broadcast address. |    |                |                                                                                                                                     |      |    |                                                                                                                    |

| 1                                                                                                                                                                                                              | 0         | 0              | 1                                    | 0    | X             | 1                                                                                                                                                                         | 0  | 0              | 0                                                                                                                                   | 0    | 1  | Reserved. Any address or data code greater or equal to these are reserved for future expansion or factory testing. |

<sup>\*</sup>The binary output number may also be the broadcast connection designator, 10001X.

-12- REV. 0

#### **Control Interface Timing Diagrams**

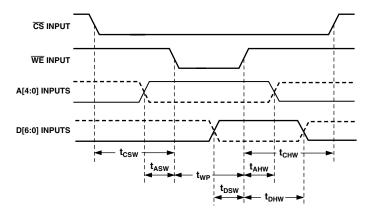

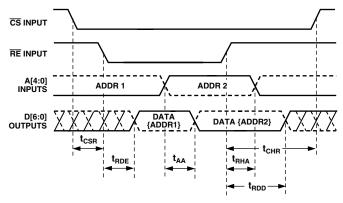

Figure 25. First Rank Write Cycle

Table III. First Rank Write Cycle

| Symbol                                                   | Paran             | Conditions                                                                           | Min                                               | Тур          | Max | Unit |                |

|----------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------|---------------------------------------------------|--------------|-----|------|----------------|

| t <sub>CSW</sub><br>t <sub>ASW</sub><br>t <sub>DSW</sub> | Setup Time        | Chip Select to Write Enable<br>Address to Write Enable<br>Data to Write Enable       | $T_A = 25^{\circ}C$ $V_{DD} = 5 V$ $V_{CC} = 5 V$ | 0<br>0<br>15 |     |      | ns<br>ns<br>ns |

| t <sub>CHW</sub><br>t <sub>AHW</sub><br>t <sub>DHW</sub> | Hold Time         | Chip Select from Write Enable<br>Address from Write Enable<br>Data from Write Enable |                                                   | 0<br>0<br>0  |     |      | ns<br>ns<br>ns |

| $t_{\mathrm{WP}}$                                        | Width of Write En | Width of Write Enable Pulse                                                          |                                                   |              |     |      | ns             |

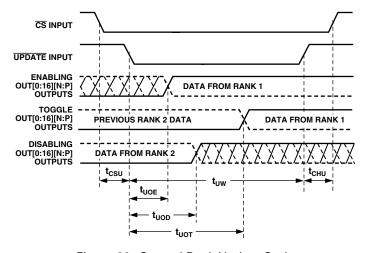

Figure 26. Second Rank Update Cycle

Table IV. Second Rank Update Cycle

| Symbol                                                                               | Para                                                                              | Conditions                                                                                                                 | Min                                                 | Typ | Max            | Unit           |                      |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|----------------|----------------|----------------------|

| t <sub>CSU</sub> t <sub>CHU</sub> t <sub>UOE</sub> t <sub>UOT</sub> t <sub>UOD</sub> | Setup Time Hold Time Output Enable Times Output Toggle Times Output Disable Times | Chip Select to Update Chip Select from Update Update to Output Enable Update to Output Reprogram Update to Output Disabled | $T_{A} = 25^{\circ}C$ $V_{DD} = 5 V$ $V_{CC} = 5 V$ | 0 0 | 25<br>25<br>25 | 40<br>40<br>30 | ns<br>ns<br>ns<br>ns |

| $t_{UW}$                                                                             | Width of Update Pulse                                                             |                                                                                                                            |                                                     | 15  |                |                | ns                   |

REV. 0 -13-

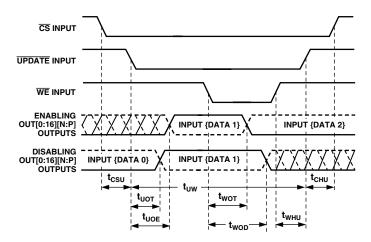

Figure 27. First Rank Write Cycle and Second Rank Update Cycle

Table V. First Rank Write Cycle and Second Rank Update Cycle

| Symbol             | Para                    | Conditions                                                     | Min                                   | Тур | Max      | Unit     |          |

|--------------------|-------------------------|----------------------------------------------------------------|---------------------------------------|-----|----------|----------|----------|

| t <sub>CSU</sub>   | Setup Time<br>Hold Time | Chip Select to Update<br>Chip Select from Update               | $T_A = 25^{\circ}C$<br>$V_{DD} = 5 V$ | 0 0 |          |          | ns<br>ns |

| t <sub>UOE</sub>   | Output Enable Times     | Update to Output Enable<br>Write Enable to Output Enable       | $V_{CC} = 5 \text{ V}$                |     | 25<br>25 | 40<br>40 | ns<br>ns |

| t <sub>UOT</sub>   | Output Toggle Times     | Update to Output Reprogram<br>Write Enable to Output Reprogram |                                       |     | 25<br>25 | 30<br>30 | ns<br>ns |

| t <sub>UOD</sub> * | Output Disable Times    | Update to Output Disabled<br>Write Enable to Output Disabled   |                                       |     | 25<br>25 | 30<br>30 | ns<br>ns |

| $t_{ m WHU}$       | Setup Time              | Write Enable to Update                                         |                                       | 10  |          |          | ns       |

| t <sub>UW</sub>    | Width of Update Pulse   |                                                                |                                       | 15  |          |          | ns       |

<sup>\*</sup>Not Shown.

Figure 28. Second Rank Readback Cycle

Table VI. Second Rank Readback Cycle

| Symbol                                                   | Parar                                      | Conditions                                                                             | Min                                                 | Тур         | Max            | Unit |                |

|----------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|----------------|------|----------------|

| t <sub>CSR</sub><br>t <sub>CHR</sub><br>t <sub>RHA</sub> | Setup Time<br>Hold Time                    | Chip Select to Read Enable<br>Chip Select from Read Enable<br>Address from Read Enable | $T_{A} = 25^{\circ}C$ $V_{DD} = 5 V$ $V_{CC} = 5 V$ | 0<br>0<br>5 |                |      | ns<br>ns<br>ns |

| t <sub>RDE</sub><br>t <sub>AA</sub><br>t <sub>RDD</sub>  | Enable Time<br>Access Time<br>Release Time | Data from Read Enable Data from Address Data from Read Enable                          | 10 kΩ<br>20 pF on D[6:0]<br>Bus                     |             | 15<br>15<br>15 | 30   | ns<br>ns<br>ns |

-14- REV. 0

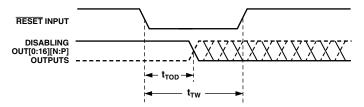

Figure 29. Asynchronous Reset

Table VII. Asynchronous Reset

| Symbol           | Paran                                                       | neter | Conditions                                        | Min | Typ | Max | Unit     |

|------------------|-------------------------------------------------------------|-------|---------------------------------------------------|-----|-----|-----|----------|

| t <sub>TOD</sub> | Disable Time Output Disable from Reset Width of Reset Pulse |       | $T_A = 25^{\circ}C$ $V_{DD} = 5 V$ $V_{CC} = 5 V$ | 15  | 25  | 30  | ns<br>ns |

#### **Control Interface Programming Example**

The following conservative pattern connects all outputs to input number 7, except output 16 which is connected to input number 32. The vector clock period,  $T_0$  is 15 ns. It is possible to accelerate the execution of this pattern by deleting vectors 1, 4, 7, and 9.

Table VIII. Basic Test Pattern

| Vector No. | Reset | CS | WE | RE | Update | A[4:0] | D[6:0]  | Comments                 |  |

|------------|-------|----|----|----|--------|--------|---------|--------------------------|--|

| 0          | 0     | 1  | 1  | 1  | 1      | xxxxx  | xxxxxxx | Disable All Outputs      |  |

| 1          | 1     | 1  | 1  | 1  | 1      | xxxxx  | xxxxxxx | _                        |  |

| 2          | 1     | 0  | 1  | 1  | 1      | 10001  | 1000111 | All Outputs to Input #07 |  |

| 3          | 1     | 0  | 0  | 1  | 1      | 10001  | 1000111 | Write to First Rank      |  |

| 4          | 1     | 0  | 1  | 1  | 1      | 10001  | 1000111 |                          |  |

| 5          | 1     | 0  | 1  | 1  | 1      | 10000  | 1100000 | Output #16 to Input #32  |  |

| 6          | 1     | 0  | 0  | 1  | 1      | 10000  | 1100000 | Write to First Rank      |  |

| 7          | 1     | 0  | 1  | 1  | 1      | 10000  | 1100000 |                          |  |

| 8          | 1     | 0  | 1  | 1  | 0      | xxxxx  | xxxxxxx | Transfer to Second Rank  |  |

| 9          | 1     | 0  | 1  | 1  | 1      | xxxxx  | xxxxxxx |                          |  |

| 10         | 1     | 1  | 1  | 1  | 1      | xxxxx  | xxxxxx  | Disable Interface        |  |

REV. 0 -15-

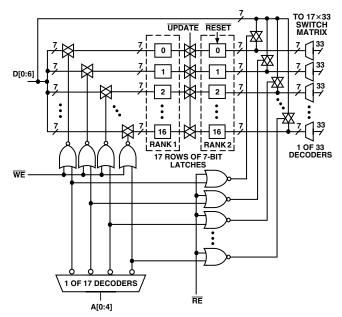

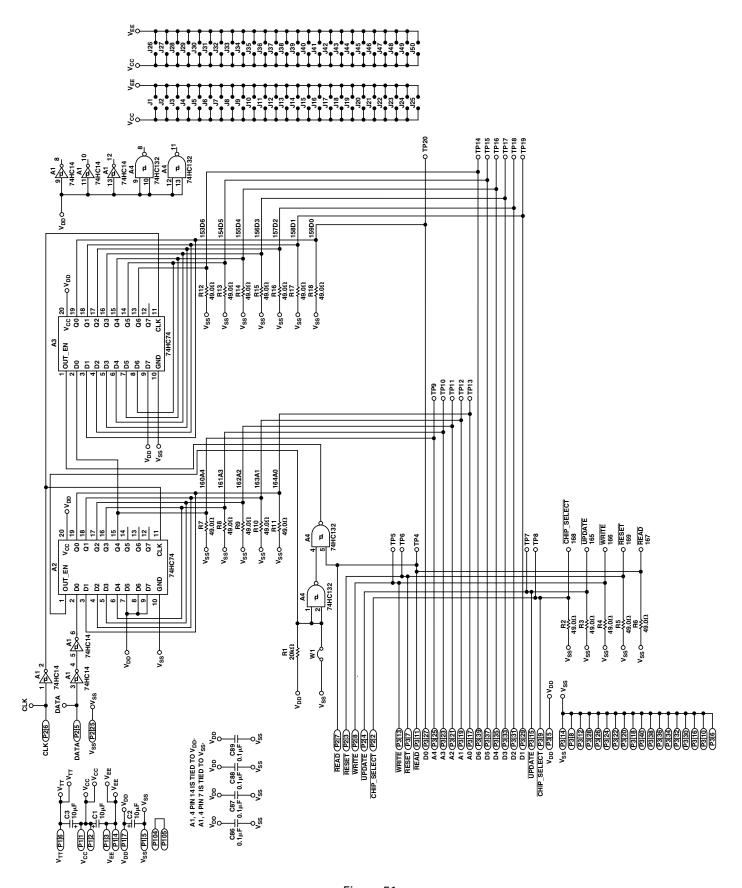

Figure 30. Control Interface (Simplified Schematic)

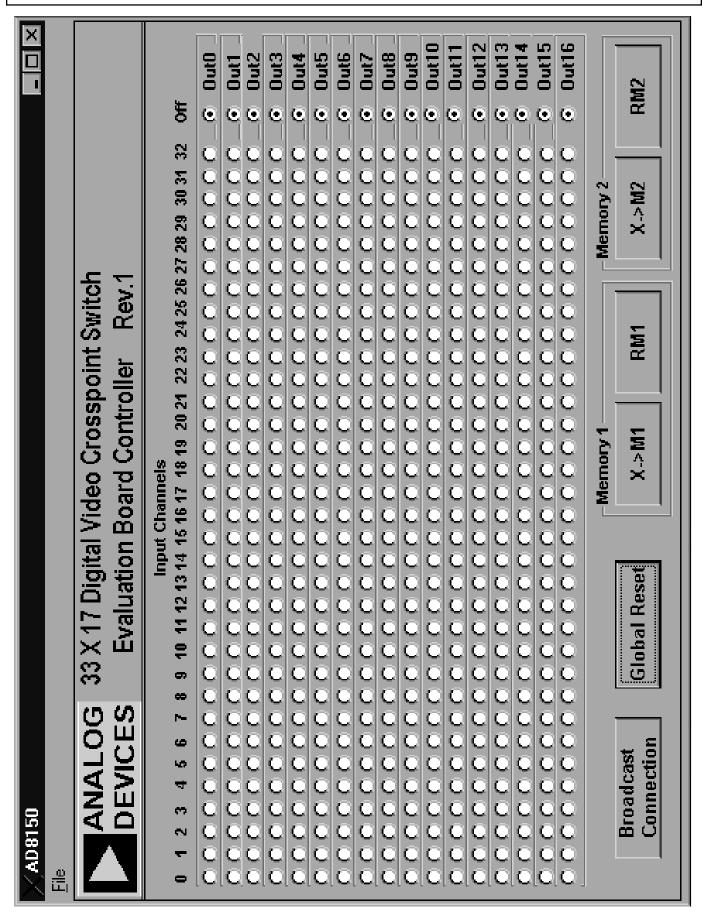

#### AD8150 CONTROL INTERFACE

The AD8150 control interface receives and stores the desired connection matrix for the 33 input and 17 output signal pairs. The interface consists of 17 rows of double-rank 7-bit latches, one row for each output. The 7-bit data word stored in each of these latches indicates to which (if any) of the 33 inputs the output will be connected.

One output at a time can be preprogrammed by addressing the output and writing the desired connection data into the first rank of latches. This process can be repeated until each of the desired output changes has been preprogrammed. All output connections can then be programmed at once by passing the data from the first rank of latches into the second rank. The output connections always reflect the data programmed into the second rank of latches, and do not change until the first rank of data is passed into the second rank.

If necessary for system verification, the data in the second rank of latches can be read back from the control interface.

At any time, a reset pulse can be applied to the control interface to globally reset the appropriate second rank data bits, disabling all 17 signal output pairs. This feature can be used to avoid output bus contention on system start-up. The contents of the first rank remain unchanged.

The control interface pins are connected via logic-level translators. These translators allow programming and readback of the control interface using logic levels different from those in the signal matrix.

In order to facilitate multiple chip address decoding, there is a chip-select pin. All logic signals except the reset pulse are ignored unless the chip select pin is active. The chip select pin disables only the control logic interface, and does not change the operation of the signal matrix. The chip select pin does not power down any of the latches, so any data programmed in the latches is preserved.

All control pins are level-sensitive, not edge-triggered.

#### CONTROL PIN DESCRIPTION

#### A[4:0] Inputs

Output address pins. The binary encoded address applied to these five input pins determines which one of the seventeen outputs is being programmed (or being read back). The most significant bit is A4.

#### D[6:0] Inputs/Outputs

Input configuration data pins. In write mode, the binary encoded data applied to pins D[6:0] determine which one of 33 inputs is to be connected to the output specified with the A[4:0] pins. The most significant bit is D5, and the least significant bit is D0. Bit D6 is the enable bit, setting the specified output signal pair to an enabled state if D6 is logic HIGH, or disabled to a high-impedance state if D6 is logic LOW.

In readback mode, pins D[6:0] are low-impedance outputs indicating the data word stored in the second rank for the output specified with the A[4:0] pins. The readback drivers were designed to drive high impedances only, so external drivers connected to the D[6:0] should be disabled during readback mode.

#### WE Input

First Rank Write Enable. Forcing this pin to logic LOW allows the data on pins D[6:0] to be stored in the first rank latch for the output specified by pins A[4:0]. The  $\overline{\text{WE}}$  pin must be returned to a logic HIGH state after a write cycle to avoid overwriting the first rank data.

#### **UPDATE** Input

Second Rank Write Enable. Forcing this pin to logic LOW allows the data stored in all 17 first rank latches to be transferred to the second rank latches. The signal connection matrix will be reprogrammed when the second rank data is changed. This is a global pin, transferring all 17 rows of data at once. It is not necessary to program the address pins. It should be noted that after initial power-up of the device, the first rank data is undefined. It may be desirable to preprogram all seventeen outputs before performing the first update cycle.

#### RE Input

Second Rank Read-Enable. Forcing this pin to logic LOW enables the output drivers on the bidirectional D[6:0] pins, entering the readback mode of operation. By selecting an output address with the A[4:0] pins and forcing  $\overline{RE}$  to logic LOW, the 7-bit data stored in the second rank latch for that output address will be written to D[6:0] pins. Data should not be written to the D[6:0] pins externally while in readback mode. The  $\overline{RE}$  and  $\overline{WE}$  pins are not exclusive, and may be used at the same time, but data should not be written to the D[6:0] pins from external sources while in readback mode.

#### **CS** Input

Chip-Select. This pin must be forced to logic LOW in order to program or receive data from the logic interface, with the exception of the RESET pin, described below. This pin has no effect on the signal pairs and does not alter any of the stored control data.

#### **RESET** Input

Global Output Disable Pin. Forcing the RESET pin to logic LOW will reset the enable bit, D6, in all 17 second rank latches, regardless of the state of any other pins. This has the effect of immediately disabling the 17 output signal pairs in the

-16- REV. 0

matrix. It is useful to momentarily hold RESET at a logic LOW state when powering up the AD8150 in a system that has multiple output signal pairs connected together. Failure to do this may result in several signal outputs contending after power-up. The reset pin is not gated by the state of the chip-select pin, CS. It should be noted that the RESET pin does not program the first rank, which will contain undefined data after power-up.

#### CONTROL INTERFACE TRANSLATORS

The AD8150 control interface has two supply pins,  $V_{\rm DD}$  and  $V_{\rm SS}$ . The potential between the positive logic supply  $V_{\rm DD}$  and the negative logic supply  $V_{\rm SS}$  must be at least 3 V and no more than 5 V. Regardless of supply, the logic threshold is approximately 1.6 V above  $V_{\rm SS}$ , allowing the interface to be used with most CMOS and TTL logic drivers.

The signal matrix supplies,  $V_{CC}$  and  $V_{EE}$ , can be set independent of the voltage on  $V_{DD}$  and  $V_{SS}$ , with the constraints that  $(V_{DD}-V_{EE}) \leq 10$  V. These constraints will allow operation of the control interface on 3 V or 5 V while the signal matrix is operated on 3.3 V or 5 V PECL, or –3.3 V or –5 V ECL.

#### CIRCUIT DESCRIPTION

The AD8150 is a high-speed 33 × 17 differential crosspoint switch designed for data rates up to 1.5 Gbps per channel. The AD8150 supports PECL-compatible input and output levels when operated from a 5 V supply ( $V_{CC} = 5 \text{ V}$ ,  $V_{EE} = \text{GND}$ ) or ECL-compatible levels when operated from a -5 V supply ( $V_{CC}$  = GND,  $V_{EE}$  = −5 V). To save power, the AD8150 can run from a 3.3 V supply to interface with low-voltage PECL circuits or a -3.3 V supply to interface with low-voltage ECL circuits. The AD8150 utilizes differential current mode outputs with individual disable control, which facilitates busing together the outputs of multiple AD8150s to assemble larger switch arrays. This feature also reduces system crosstalk and can greatly reduce power dissipation in a large switch array. A single external resistor programs the current for all enabled output stages, allowing for user control over output levels with different output termination schemes and transmission line characteristic impedances.

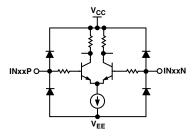

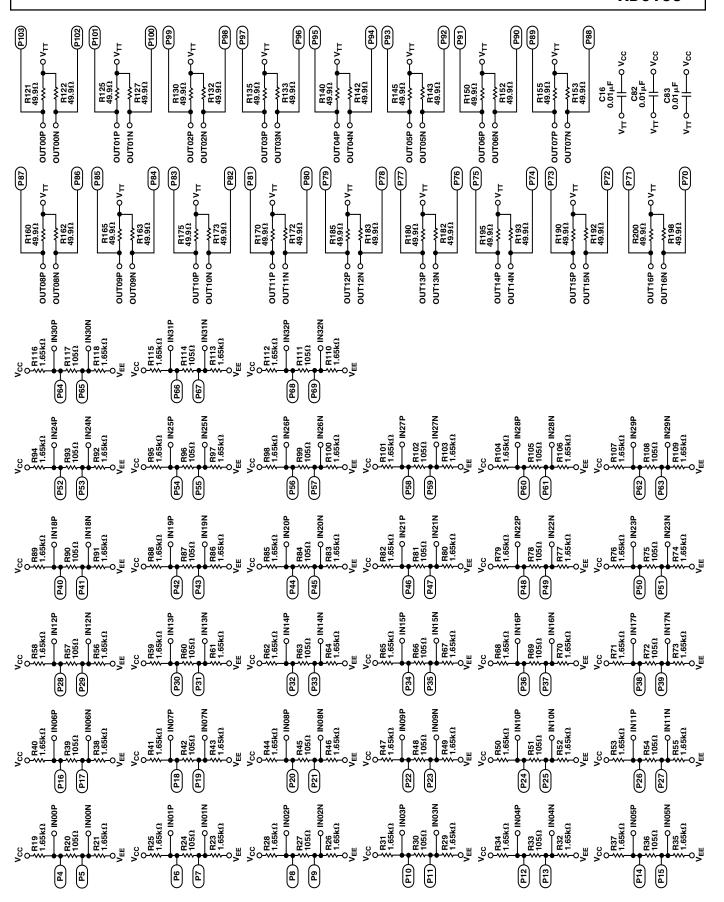

#### High-Speed Data Inputs (INxxP, INxxN)

The AD8150 has 33 pairs of differential voltage-mode inputs. The common-mode input range extends from the positive supply voltage ( $V_{CC}$ ) down to include standard ECL or PECL input levels ( $V_{CC}$  – 2 V). The minimum differential input voltage is less than 300 mV. Unused inputs may be connected directly to any level within the allowed common-mode input range. A simplified schematic of the input circuit is shown in Figure 31.

Figure 31. Simplified Input Circuit

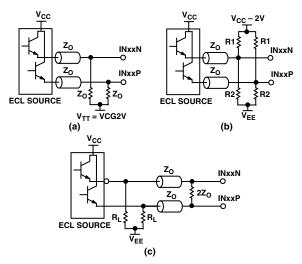

In order to maintain signal fidelity at the high data rates supported by the AD8150, the input transmission lines should be terminated as close to the input pins as possible. The preferred input termination structure will depend primarily on the application and the output circuit of the data source. Standard ECL components have open emitter outputs that require pull-down resistors. Three input termination networks suitable for this type of source are shown in Figure 32. The characteristic impedance of the transmission line is shown as  $Z_{\rm O}$ . The resistors, R1 and R2, in the Thevenin termination are chosen to synthesize a  $V_{\rm TT}$  source with an output resistance of  $Z_{\rm O}$  and an open-circuit output voltage equal to  $V_{\rm CC}-2$  V. The load resistors (R\_I) in the differential termination scheme are needed to bias the emitter followers of the ECL source.

Figure 32. AD8150 Input Termination from ECL/PECL Sources: a) Parallel Termination Using  $V_{TT}$  Supply, b) Thevenin Equivalent Termination, c) Differential Termination

If the AD8150 is driven from a current mode output stage such as another AD8150, the input termination should be chosen to accommodate that type of source, as explained in the following section.

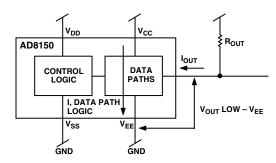

#### High-Speed Data Outputs (OUTyyP, OUTyyN)

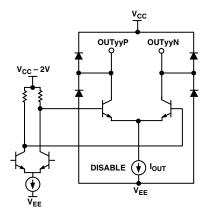

The AD8150 has 17 pairs of differential current-mode outputs. The output circuit, shown in Figure 33, is an open-collector NPN current switch with resistor-programmable tail current and output compliance extending from the positive supply voltage ( $V_{\rm CC}$ ) down to standard ECL or PECL output levels ( $V_{\rm CC}-2$  V). The outputs may be disabled individually to permit outputs from multiple AD8150's to be connected directly. Since the output currents of multiple enabled output stages connected in this way sum, care should be taken to ensure that the output compliance limit is not exceeded at any time; this can be achieved by disabling the active output driver before enabling any inactive driver.

REV. 0 -17-

Figure 33. Simplified Output Circuit

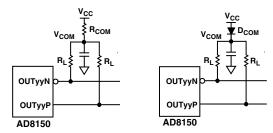

To ensure proper operation, all outputs (including unused output) must be pulled high using external pull-up networks to a level within the output compliance range. If outputs from multiple AD8150s are wired together, a single pull-up network may be used for each output bus. The pull-up network should be chosen to keep the output voltage levels within the output compliance range at all times. Recommended pull-up networks to produce PECL/ECL 100K and 10K compatible outputs are shown in Figure 34. Alternatively, a separate supply can be used to provide  $V_{\rm COM}$ ; making  $R_{\rm COM}$  and  $D_{\rm COM}$  unnecessary.

Figure 34. Output Pull-Up Networks: a) ECL 100K, b) ECL 10K

The output levels are simply:

$$\begin{split} V_{OH} &= V_{COM} \\ V_{OL} &= V_{COM} - I_{OUT}R_L \\ V_{SWING} &= V_{OH} - V_{OL} = I_{OUT}R_L \\ V_{COM} &= V_{CC} - I_{OUT}R_{COM} \ (100K\ Mode) \\ V_{COM} &= V_{CC} - V \ (D_{COM}) \ \ (10K\ Mode) \end{split}$$

The common-mode adjustment element ( $R_{COM}$  or  $D_{COM}$ ) may be omitted if the input range of the receiver includes the positive supply voltage. The bypass capacitors reduce common-mode perturbations by providing an ac short from the common nodes ( $V_{COM}$ ) to ground.

When busing together the outputs of multiple AD8150s or when running at high data rates, double termination of its outputs is recommended to mitigate the impact of reflections due to open transmission line stubs and the lumped capacitance of the AD8150 output pins. A possible connection is shown in Figure 35; the bypass capacitors provide an ac short from the common nodes of the termination resistors to ground. To maintain signal fidelity at high data rates, the stubs connecting the output pins to the output transmission lines or load resistors should be as short as possible.

Figure 35. Double Termination of AD8150 Outputs

In this case, the output levels are:

$$V_{OH} = V_{COM} - (1/4) I_{OUT}R_L$$

$$V_{OL} = V_{COM} - (3/4) I_{OUT}R_L$$

$$V_{SWING} = V_{OH} - V_{OL} = (1/2) I_{OUT}R_L$$

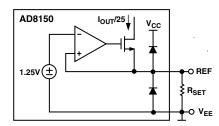

#### Output Current Set Pin (REF)

A simplified schematic of the reference circuit is shown in Figure 36. A single external resistor connected between the REF pin and  $V_{\rm EE}$  determines the output current for all output stages. This feature allows a choice of pull-up networks and transmission line characteristic impedances while still achieving a nominal output swing of 800 mV. At low data rates, substantial power savings can be achieved by using lower output swings and higher load resistances.

Figure 36. Simplified Reference Circuit

The resistor value current is given by the following expression:

$$R_{SET} = \frac{25}{I_{OUT}}$$

Example:

-18-

$$R_{SET} = 1.54 \ k\Omega$$

for  $I_{OUT} = 16.2 \ mA$

The minimum set resistor is  $R_{SET,min}=1~k\Omega$  resulting in  $I_{OUT,max}=25~mA$ . The maximum set resistor is  $R_{SET,max}=5~k\Omega$  resulting in  $I_{OUT,min}=5~mA$ . Nominal 800 mV output swings can be achieved in a 50  $\Omega$  load using  $R_{SET}=1.56~k\Omega$  ( $I_{OUT}=16.2~mA$ ) or in a doubly-terminated 75  $\Omega$  load using  $R_{SET}=1.17~k\Omega$  ( $I_{OUT}=21.3~mA$ ).

To minimize stray capacitance and avoid the pickup of unwanted signals, the external set resistor should be located close to the REF pin. Bypassing the set resistor is not recommended.

REV. 0

#### **Power Supplies**

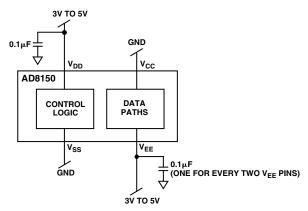

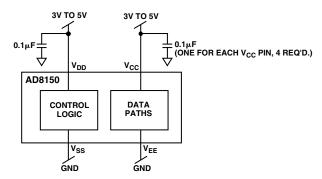

There are several options for the power supply voltages for the AD8150, as there are two separate sections of the chip that require power supplies. These are the control logic and the high-speed data paths. Depending on the system architecture, the voltage levels of these supplies can vary.

#### Logic Supplies

The control (programming) logic is CMOS and is designed to interface with any of the various standard single-ended logic families (CMOS or TTL). Its supply voltage pins are  $V_{\rm DD}$  (Pin 170, logic positive) and  $V_{\rm SS}$  (Pin 152, logic ground). In all cases the logic ground should be connected to the system digital ground.  $V_{\rm DD}$  should be supplied at between 3.3 V to 5 V to match the supply voltage of the logic family that is used to drive the logic inputs.  $V_{\rm DD}$  should be bypassed to ground with a 0.1  $\mu F$  ceramic capacitor. The absolute maximum voltage from  $V_{\rm DD}$  to  $V_{\rm SS}$  is 5.5 V.

#### **Data Path Supplies**

The data path supplies have more options for their voltage levels. The choices here will affect several other areas, like power dissipation, bypassing, and common mode levels of the inputs and outputs. The more positive voltage supply for the data paths is  $V_{\rm CC}$  (Pins 41, 98, 149 and 171). The more negative supply is  $V_{\rm EE}$ , which appears on many pins that will not be listed here. The maximum allowable voltage across these supplies is 5.5 V.

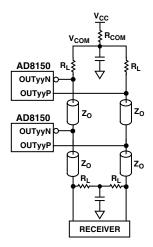

The first choice in the data path power supplies is to decide whether to run the device as ECL (Emitter-Coupled Logic) or PECL (Positive ECL). For ECL operation,  $V_{CC}$  will be at ground potential, while  $V_{EE}$  will be at a negative supply between -3.3~V to -5~V. This will make the common-mode voltage of the inputs and outputs at a negative voltage, see Figure 37.

Figure 37. Power Supplies and Bypassing for ECL Operation

If the data paths are to be dc-coupled to other ECL logic devices that run with ground as the most positive supply and a negative voltage for  $V_{\rm EE}$ , then this is the proper way to run. However, if

the part is to be ac coupled, it is not necessary to have the input/output common mode at the same level as the other system circuits, but it will probably be more convenient to use the same supply rails for all devices.

For PECL operation,  $V_{EE}$  will be at ground potential and  $V_{CC}$  will be a positive voltage from 3.3 V to 5 V. Thus, the common mode of the inputs and outputs will be at a positive voltage. These can then be dc coupled to other PECL operated devices. If the data paths are ac coupled, then the common-mode levels do not matter, see Figure 38.

Figure 38. Power Supplies and Bypassing for PECL Operation

#### POWER DISSIPATION

For analysis, the power dissipation of the AD8150 can be divided into three separate parts. These are the control logic, the data path circuits and the (ECL or PECL) outputs, which are part of the data path circuits, but can be dealt with separately. The first of these, the control logic, is CMOS technology and does not dissipate a significant amount of power. This power will, of course, be greater when the logic supply is 5 V rather than 3 V, but overall it is not a significant amount of power and can be ignored for thermal analysis.

Figure 39. Major Power Consumption Paths

The data path circuits operate between the supplies  $V_{\text{CC}}$  and  $V_{\text{EE}}$ . As described in the power supply section, this voltage can range from 3.3 V to 5 V. The current consumed by this section will be constant, so operating at a lower voltage can save about 40 percent in power dissipation.

REV. 0 –19–

The power dissipated in the data path outputs is affected by several factors. The first is whether the outputs are enabled or disabled. The worst case occurs when all of the outputs are enabled.

The current consumed by the data path logic can be approximated by:

$$I_{CC}$$

= 30 mA + [4.5 mA + ( $I_{OUT}$ /20 mA × 3 mA)]

× (# of outputs enabled)

This says that there will always be a minimum of 30 mA flowing.  $I_{CC}$  will increase by a factor that is proportional to both the number of enabled outputs and the programmed output current.

The power dissipated in this circuit section will simply be the voltage of this section ( $V_{CC} - V_{EE}$ ) times the current. For a worst case, assume that  $V_{CC} - V_{EE}$  is 5.0 V, all outputs are enabled and the programmed output current is 25 mA. The power dissipated by the data path logic will be:

$$P = 5.0 \ V \{25 \ mA + [4.5 \ mA + (25 \ mA/20 \ mA \times 3 \ mA)] \times 17\} = 826 \ mW$$

The power dissipated by the output current depends on several factors. These are the programmed output current, the voltage drop from a logic low output to  $V_{EE}$  and the number of enabled outputs. A simplifying assumption is that one of each (enabled) differential output pair will be low and draw the full output current (and dissipate most of the power for that output), while the complementary output of the pair will be high and draw insignificant current. Thus, its power dissipation of the high output can be ignored and the output power dissipation for each output can be assumed to occur in a single static low output that sinks the full output-programmed current.

The voltage across which this current flows can also vary, depending on the output circuit design and the supplies that are used for the data path circuitry. In general, however, there will be a voltage difference between a logic low signal and  $V_{\rm EE}$ . This is the drop across which the output current flows. For a worst case, this voltage can be as high as 3.5 V. Thus, for all outputs enabled and the programmed output current set to 25 mA, the power dissipated by the outputs:

$$P = 3.5 \ V (25 \ mA) \times 17 = 1.49 \ W$$

#### **HEAT SINKING**

Depending on several factors in its operation, the AD8150 can dissipate upwards of 2 W or more. The part is designed to operate without the need for an explicit external heatsink. However, the package design offers enhanced heat removal via some of the package pins to the PC board traces.

The  $V_{EE}$  pins on the input sides of the package (Pins 1 to 46 and Pins 93 to 138) have "finger" extensions inside the package that connect to the "paddle" upon which the IC chip is mounted. These pins provide a lower thermal resistance from the IC to the  $V_{EE}$  pins than other pins that just have a bond wire. As a result these pins can be used to enhance the heat removal process from the IC to the circuit board and ultimately to the ambient.

The  $V_{EE}$  pins described above should be connected to a large area of circuit board trace material in order to take most advantage their lower thermal resistance. If there is a large area available on an inner layer that is at  $V_{EE}$  potential, then vias can be provided from the package pin traces to this layer. There should be no thermal-relief pattern when connecting the vias to the inner layers for these  $V_{EE}$  pins. Additional vias in parallel and close to

the pin leads can provide an even lower thermal resistive path. If possible to use, 2 oz. copper foil will provide better heat removal than 1 oz.

The AD8150 package has a specified thermal impedance  $\theta_{JA}$  of 30°C/W. This is the worst case, still-air value that can be expected when the circuit board does not significantly enhance the heat removal from the package. By using the concept described above or by using forced-air circulation, the thermal impedance can be lowered.

For an extreme worst case analysis, the junction rise above the ambient can be calculated assuming 2 W of power dissipation and  $\theta_{JA}$  of 30°C/W to yield a 60°C rise above the ambient. There are many techniques described above that can mitigate this situation. Most actual circuits will not result in this high a rise of the junction temperature above the ambient.

#### **APPLICATIONS**

#### AD8150 INPUT AND OUTPUT BUSING

Although the AD8150 is a digital part, in any application that runs at high speed, analog design details will have to be given very careful consideration. At high data rates, the design of the signal channels will have a strong influence on the data integrity and its associated jitter and ultimately bit error rate (BER).

While it might be considered very helpful to have a suggested circuit board layout for any particular system configuration, this is not something that can be practically realized. Systems come in all shapes, sizes, speeds, performance criteria and cost constraints. Therefore, some general design guidelines will be presented that can be used for all systems and judiciously modified where appropriate.