Application Note

AN2491

Rev. 0, 9/2003

Simplified Mnemonics for PowerPC™ Instructions

Jerry Young, NCSD Applications

# Simplified Mnemonics for PowerPC<sup>TM</sup> Instructions

This document describes simplified mnemonics, which are provided for easier coding of assembly language programs. Simplified mnemonics are defined for the most frequently used forms of branch conditional, compare, trap, rotate and shift, and certain other instructions defined by the PowerPC<sup>TM</sup> architecture and by implementations of and extensions to the PowerPC architecture.

Most of this information is also provided in the appendixes of reference manuals and the *Programming Environments Manual for 32-Bit Implementations of the PowerPC Architecture* (referred to as the *Programming Environment Manual*). However, Section 12, "Comprehensive List of Simplified Mnemonics," provides an alphabetical listing of simplified mnemonics that are used by a variety of processors. Some assemblers may define additional simplified mnemonics not included here. The simplified mnemonics listed here should be supported by all compilers.

This document describes only simplified mnemonics for 32-bit instructions.

| Section                                                      | Page |

|--------------------------------------------------------------|------|

| Section 1, "Overview"                                        | 2    |

| Section 2, "Subtract Simplified Mnemonics"                   | 2    |

| Section 3, "Rotate and Shift Simplified Mnemonics"           | 3    |

| Section 4, "Branch Instruction Simplified Mnemonics"         | 4    |

| Section 5, "Compare Word Simplified Mnemonics"               | 18   |

| Section 6, "Condition Register Logical Simplified Mnemonics" | 19   |

| Section 7, "Trap Instructions Simplified Mnemonics"          | 19   |

| Section 8, "Simplified Mnemonics for Accessing SPRs"         | 21   |

| Section 9, "AltiVec Simplified Mnemonics"                    | 22   |

| Section 10, "Recommended Simplified Mnemonics"               | 23   |

| Section 11, "EIS-Specific Simplified Mnemonics"              | 24   |

| Section 12, "Comprehensive List of Simplified Mnemonics"     | 25   |

# 1 Overview

Simplified (or extended) mnemonics allow an assembly-language programmer to program using more intuitive mnemonics and symbols than the instructions and syntax defined by the instruction set architecture. For example, to code the conditional call "branch to an absolute target if CR4 specifies a greater than condition, setting the LR" without simplified mnemonics, the programmer would write the branch conditional instruction **bc 12,17**, target. The simplified mnemonic, branch if greater than, **bgt cr4**, target, incorporates the conditions. Not only is it easier to remember the symbols than the numbers when programming, it is also easier to interpret simplified mnemonics when reading existing code.

Although the original PowerPC architecture documents include a set of simplified mnemonics, these are not a formal part of the architecture, but rather a recommendation for assemblers that support the instruction set.

Many simplified mnemonics have been added to those originally included in the architecture documentation. Some assemblers created their own, and others have been added to support extensions to the instruction set (for example, AltiVec instructions and Book E auxiliary processing units (APUs)). Simplified mnemonics for new architecturally defined and new implementation-specific special-purpose registers (SPRs) are described here only in a very general way.

# 2 Subtract Simplified Mnemonics

This section describes simplified mnemonics for subtract instructions.

#### 2.1 Subtract Immediate

There is no subtract immediate instruction; however, its effect is achieved by negating the immediate operand of an Add Immediate instruction, **addi**. Simplified mnemonics include this negation, making the intent of the computation clearer. These are listed in Table 1.

**Table 1. Subtract Immediate Simplified Mnemonics**

| Simplified Mnemonic | Standard Mnemonic   |

|---------------------|---------------------|

| subi rD,rA,value    | addi rD,rA,-value   |

| subis rD,rA,value   | addis rD,rA,-value  |

| subic rD,rA,value   | addic rD,rA,-value  |

| subic. rD,rA,value  | addic. rD,rA,-value |

### 2.2 Subtract

Subtract from instructions subtract the second operand (**r**A) from the third (**r**B). The simplified mnemonics in Table 2 use the more common order in which the third operand is subtracted from the second.

**Table 2. Subtract Simplified Mnemonics**

| Simplified Mnemonic | Standard Mnemonic <sup>1</sup> |

|---------------------|--------------------------------|

| sub[o][.] rD,rA,rB  | subf[o][.] rD,rB,rA            |

| subc[o][.] rD,rA,rB | subfc[o][.] rD,rB,rA           |

<sup>&</sup>lt;sup>1</sup> rD,rB,rA is not the standard order for the operands. The order of rB and rA is reversed to show the equivalent behavior of the simplified mnemonic.

# 3 Rotate and Shift Simplified Mnemonics

Rotate and shift instructions provide powerful, general ways to manipulate register contents, but can be difficult to understand. Simplified mnemonics are provided for the following operations:

- Extract—Select a field of *n* bits starting at bit position *b* in the source register; left or right justify this field in the target register; clear all other bits of the target register.

- Insert—Select a left- or right-justified field of *n* bits in the source register; insert this field starting at bit position *b* of the target register; leave other bits of the target register unchanged.

- Rotate—Rotate the contents of a register right or left *n* bits without masking.

- Shift—Shift the contents of a register right or left *n* bits, clearing vacated bits (logical shift).

- Clear—Clear the leftmost or rightmost *n* bits of a register.

- Clear left and shift left—Clear the leftmost *b* bits of a register, then shift the register left by *n* bits. This operation can be used to scale a (known non-negative) array index by the width of an element.

# 3.1 Operations on Words

The simplified mnemonics in Table 3 can be coded with a dot (.) suffix to cause the Rc bit to be set in the underlying instruction.

**Table 3. Word Rotate and Shift Simplified Mnemonics**

| Operation                                | Simplified Mnemonic                                      | Equivalent to:                                              |

|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| Extract and left justify word immediate  | extlwi rA,rS, $n$ , $b$ ( $n > 0$ )                      | rlwinm rA,rS, <i>b</i> , <b>0</b> , <i>n</i> – 1            |

| Extract and right justify word immediate | <b>extrwi</b> rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0) | rlwinm rA,rS,b + n,32 - n, <b>31</b>                        |

| Insert from left word immediate          | inslwi rA,rS, $n$ , $b$ ( $n > 0$ )                      | rlwimi rA,rS,32 – <i>b,b</i> ,( <i>b</i> + <i>n</i> ) – 1   |

| Insert from right word immediate         | insrwi rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0)        | rlwimi rA,rS,32 – (b + n),b,(b + n) – 1                     |

| Rotate left word immediate               | rotlwi rA,rS,n                                           | rlwinm rA,rS,n,0,31                                         |

| Rotate right word immediate              | rotrwi rA,rS,n                                           | rlwinm rA,rS,32 – <i>n</i> , <b>0,31</b>                    |

| Rotate word left                         | rotlw rA,rS,rB                                           | rlwnm rA,rS,rB,0,31                                         |

| Shift left word immediate                | slwi rA,rS,n (n < 32)                                    | rlwinm rA,rS, <i>n</i> , <b>0</b> ,31 – <i>n</i>            |

| Shift right word immediate               | <b>srwi</b> rA,rS,n (n < 32)                             | rlwinm rA,rS,32 – <i>n</i> , <i>n</i> , <b>31</b>           |

| Clear left word immediate                | clrlwi rA,rS,n (n < 32)                                  | rlwinm rA,rS,0,n,31                                         |

| Clear right word immediate               | <b>clrrwi</b> rA,rS, <i>n</i> ( <i>n</i> < 32)           | rlwinm rA,rS, <b>0</b> , <b>0</b> ,31 – n                   |

| Clear left and shift left word immediate | cirlsiwi rA,rS, $b$ , $n$ ( $n \le b \le 31$ )           | rlwinm rA,rS, <i>n</i> , <i>b</i> – <i>n</i> ,31 – <i>n</i> |

Examples using word mnemonics follow:

| 1  | Destance of the | a: a.a. 1a:4 | (1-:4 A | \ _ C - C         |              | 14 1.4          | :                          |

|----|-----------------|--------------|---------|-------------------|--------------|-----------------|----------------------------|

| 1. | Extract the     | sign oit     | (DIL U  | ) 01 <b>r5</b> a1 | ia piace ine | e resuit right- | justified into <b>r</b> A. |

extrwi rA,rS,1,0 equivalent to rlwinm rA,rS,1,31,31

2. Insert the bit extracted in (1) into the sign bit (bit 0) of **r**B.

insrwi rB,rA,1,0 equivalent to rlwimi rB,rA,31,0,0

3. Shift the contents of **r**A left 8 bits.

slwi rA,rA,8 equivalent to rlwinm rA,rA,8,0,23

4. Clear the high-order 16 bits of **rS** and place the result into **rA**.

clrlwi rA,rS,16 equivalent to rlwinm rA,rS,0,16,31

# 4 Branch Instruction Simplified Mnemonics

Branch conditional instructions can be coded with the operations, a condition to be tested, and a prediction, as part of the instruction mnemonic rather than as numeric operands (the BO and BI operands). Table 4 shows the four general types of branch instructions. Simplified mnemonics are defined only for branch instructions that include BO and BI operands; there is no need to simplify unconditional branch mnemonics.

**Table 4. Branch Instructions**

| Instruction Name                     | Mnemonic          | Syntax            |

|--------------------------------------|-------------------|-------------------|

| Branch                               | b (ba bl bla)     | target_addr       |

| Branch Conditional                   | bc (bca bcl bcla) | BO,BI,target_addr |

| Branch Conditional to Link Register  | bcir (bciri)      | BO,BI             |

| Branch Conditional to Count Register | bcctr (bcctrl)    | BO,BI             |

The BO and BI operands correspond to two fields in the instruction opcode, as Figure 1 shows for Branch Conditional (**bc**, **bca**, **bcl**, and **bcla**) instructions.

| 0 |   |   |   |   | 5 | 6 | 10 | 11 | 15 | 16 29 30 | 0 3 | 1 |

|---|---|---|---|---|---|---|----|----|----|----------|-----|---|

| 0 | 0 | 1 | 0 | 0 | 0 | E | 30 | ВІ |    | BD AA    | AL  | K |

Figure 1. Branch Conditional (bc) Instruction Format

The BO operand specifies branch operations that involve decrementing CTR. It is also used to determine whether testing a CR bit causes a branch to occur if the condition is true or false.

The BI operand identifies a CR bit to test (whether a comparison is less than or greater than, for example). The simplified mnemonics avoid the need to memorize the numerical values for BO and BI.

For example, **bc** 16,0,target is a conditional branch that, as a BO value of 16 (0b1\_0000) indicates, decrements the CTR, then branches if the decremented CTR is not zero. The operation specified by BO is abbreviated as **d** (for decrement) and **nz** (for not zero), which replace the **c** in the original mnemonic; so the simplified mnemonic for **bc** becomes **bdnz**. The branch does not depend on a condition in the CR, so BI can be eliminated, reducing the expression to **bdnz** target.

In addition to CTR operations, the BO operand provides an optional prediction bit, and a true or false indicator can be added. For example, if the previous instruction should branch only on an equal condition in CR0, the instruction becomes **bc 8,2,**target. To incorporate a true condition, the BO value becomes 8 (as shown in Table 6); the CR0 equal field is indicated by a BI value of 2 (as shown in Table 7). Incorporating the branch-if-true condition adds a 't' to the simplified mnemonic, **bdnzt.** The BI value of 2 is replaced by the **eq** symbol. Using the simplified mnemonic and the **eq** operand, the expression becomes **bdnzt eq**,target.

This example tests CR0[EQ]; however, to test the equal condition in CR5 (CR bit 22), the expression becomes **bc 8,22**,*target*. The BI operand of 22 indicates CR[22] (CR5[2], or BI field 0b10110), as shown in Table 7. This can be expressed as the simplified mnemonic. **bdnzt 4 \* cr5 + eq**,*target*.

The notation, 4 \* cr5 + eq may at first seem awkward, but it eliminates computing the value of the CR bit. It can be seen that (4 \* 5) + 2 = 22. Note that although 32-bit registers in Book E processors are numbered 32-63, only values 0-31 are valid (or possible) for BI operands. As shown in Table 8, a Book E-compliant processor automatically translates the bit values; specifying a BI value of 22 selects bit 54 on a Book E processor, or CR5[2] = CR5[EQ].

# 4.1 Key Facts about Simplified Branch Mnemonics

The following key points are helpful in understanding how to use simplified branch mnemonics:

- All simplified branch mnemonics eliminate the BO operand, so if any operand is present in a branch simplified mnemonic, it is the BI operand (or a reduced form of it).

- If the CR is not involved in the branch, the BI operand can be deleted

- If the CR is involved in the branch, the BI operand can be treated in the following ways:

- It can be specified as a numeric value, just as it is in the architecturally defined instruction, or it can be indicated with an easier to remember formula,  $\mathbf{4} * \mathbf{cr} n + [\text{test bit symbol}]$ , where n indicates the CR field number.

- The condition of the test bit (eq, lt, gt, and so) can be incorporated into the mnemonic, leaving the need for an operand that defines only the CR field.

- If the test bit is in CR0, no operand is needed.

- If the test bit is in CR1-CR7, the BI operand can be replaced with a **crS** operand (that is, **cr1**, **cr2**, **cr3**, and so forth.

# 4.2 Eliminating the BO Operand

The 5-bit BO field, shown in Figure 2, encodes the following operations in conditional branch instructions:

- Decrement count register (CTR)

- And test if result is equal to zero

- And test if result is not equal to zero

- Test condition register (CR)

- Test condition true

- Test condition false

- Branch prediction (taken, fall through). If the prediction bit, y, is needed, it is signified by appending a plus or minus sign as described in Section 4.3, "Incorporating the BO Branch Prediction."

Figure 2. BO Field (Bits 6-10 of the Instruction Encoding)

BO bits can be interpreted individually as described in Table 5.

#### **Table 5. BO Bit Encodings**

| BO Bit | Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | If set, ignore the CR bit comparison.                                                                                                                                                                                                                                                                                                                                                  |

| 1      | If set, the CR bit comparison is against true; if not set the CR bit comparison is against false.                                                                                                                                                                                                                                                                                      |

| 2      | If set, the CTR is not decremented.                                                                                                                                                                                                                                                                                                                                                    |

| 3      | If BO[2] is set, this bit determines whether the CTR comparison is for equal to zero or not equal to zero.                                                                                                                                                                                                                                                                             |

| 4      | The <i>y</i> bit. If set, reverse the static prediction. Use of the this bit is optional and independent from the interpretation of the rest of the BO operand. Because simplified branch mnemonics eliminate the BO operand, this bit is programmed by adding a plus or minus sign to the simplified mnemonic, as described in Section 4.3, "Incorporating the BO Branch Prediction." |

#### **Branch Instruction Simplified Mnemonics**

Thus, a BO encoding of 10100 (decimal 20) means ignore the CR bit comparison and do not decrement the CTR—in other words, branch unconditionally. Encodings for the BO operand are shown in Table 6. A z bit indicates that the bit is ignored. However, these bits should be cleared, as they may be assigned a meaning in a future version of the architecture.

As shown in Table 6, the 'c' in the standard mnemonic is replaced with the operations otherwise specified in the BO field, (**d** for decrement, **z** for zero, **nz** for non-zero, **t** for true, and **f** for false).

**Table 6. BO Operand Encodings**

| BO Field                           | Value <sup>1</sup><br>(Decimal) | Description                                                                                      |                  |  |  |  |  |  |

|------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| 0000 <i>y</i>                      | 0                               | Decrement the CTR, then branch if the decremented CTR $\neq$ 0 and condition is FALSE.           | dnzf             |  |  |  |  |  |

| 0001 <i>y</i>                      | 2                               | Decrement the CTR, then branch if the decremented CTR = 0 and condition is FALSE.                | dzf              |  |  |  |  |  |

| 001 <i>z</i> <sup>2</sup> <i>y</i> | 4                               | Branch if the condition is FALSE. <sup>3</sup> Note that 'false' and 'four' both start with 'f'. | f                |  |  |  |  |  |

| 0100 <i>y</i>                      | 8                               | Decrement the CTR, then branch if the decremented CTR $\neq$ 0 and condition is TRUE.            | dnzt             |  |  |  |  |  |

| 0101 <i>y</i>                      | 10                              | Decrement the CTR, then branch if the decremented CTR = 0 and condition is TRUE.                 | dzt              |  |  |  |  |  |

| 011 <i>z</i> <sup>2</sup> <i>y</i> | 12                              | Branch if the condition is TRUE. <sup>3</sup> Note that 'true' and 'twelve' both start with 't'. | t                |  |  |  |  |  |

| $1z^200y^4$                        | 16                              | Decrement the CTR, then branch if the decremented CTR $\neq$ 0.                                  | dnz <sup>5</sup> |  |  |  |  |  |

| 1z <sup>2</sup> 01y <sup>4</sup>   | 18                              | Decrement the CTR, then branch if the decremented CTR = 0.                                       | dz <sup>5</sup>  |  |  |  |  |  |

| 1z <sup>2</sup> 1zz <sup>4</sup>   | 20                              | Branch always.                                                                                   | _                |  |  |  |  |  |

Assumes y = z = 0. Section 4.3, "Incorporating the BO Branch Prediction," describes how to use simplified mnemonics to program the y bit for static prediction.

# 4.3 Incorporating the BO Branch Prediction

As shown in Table 6, the low-order bit (y bit) of the BO field provides a hint about whether the branch is likely to be taken (static branch prediction). Assemblers should clear this bit unless otherwise directed. This default action indicates the following:

- A branch conditional with a negative displacement field is predicted to be taken.

- A branch conditional with a non-negative displacement field is predicted not to be taken (fall through).

- A branch conditional to an address in the LR or CTR is predicted not to be taken (fall through).

If the likely outcome (branch or fall through) of a given branch conditional instruction is known, a suffix can be added to the mnemonic that tells the assembler how to set the y bit. That is, '+' indicates that the branch is to be taken and '-' indicates that the branch is not to be taken. This suffix can be added to any branch conditional mnemonic, either standard or simplified.

<sup>&</sup>lt;sup>2</sup> A *z* bit indicates a bit that is ignored. However, these bits should be cleared, as they may be assigned a meaning in a future version of the architecture.

Instructions for which B0 is 12 (branch if condition true) or 4 (branch if condition false) do not depend on the CTR value and can be alternately coded by incorporating the condition specified by the BI field, as described in Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)."

<sup>&</sup>lt;sup>4</sup> Simplified mnemonics for branch instructions that do not test CR bits (BO = 16, 18, and 20) should specify only a target. Otherwise a programming error may occur.

Notice that these instructions do not use the branch if condition true or false operations. For that reason, simplified mnemonics for these should not specify a BI operand.

**Branch Instruction Simplified Mnemonics**

For relative and absolute branches (**bc[l][a]**), the setting of the *y* bit depends on whether the displacement field is negative or non-negative. For negative displacement fields, coding the suffix '+' causes the bit to be cleared, and coding the suffix '-' causes the bit to be set. For non-negative displacement fields, coding the suffix '+' causes the bit to be set, and coding the suffix '-' causes the bit to be cleared.

For branches to an address in the LR or CTR (**bclr**[l] or **bcctr**[l]), coding the suffix '+' causes the y bit to be set, and coding the suffix '-' causes the bit to be cleared.

Examples of branch prediction follow:

- 1. Branch if CR0 reflects less than condition, specifying that the branch should be predicted as taken. **blt**+ *target*

- 2. Same as (1), but target address is in the LR and the branch should be predicted as not taken. **bltlr**–

# 4.4 The BI Operand—CR Bit and Field Representations

With standard branch mnemonics, the BI operand is used when it is necessary to test a CR bit, as shown in the example in Section 4, "Branch Instruction Simplified Mnemonics,"

With simplified mnemonics, the BI operand is handled differently depending on whether the simplified mnemonic incorporates a CR condition to test, as follows:

- Some branch simplified mnemonics incorporate only the BO operand. These simplified mnemonics can use the architecturally defined BI operand to specify the CR bit, as follows:

- The BI operand can be presented exactly as it is with standard mnemonics—as a decimal number, 0–31.

- Symbols can be used to replace the decimal operand, as shown in the example in Section 4, "Branch Instruction Simplified Mnemonics," where bdnzt 4 \* cr5 + eq,target could be used instead of bdnzt 22,target. This is described in Section 4.4.1.1, "Specifying a CR Bit."

The simplified mnemonics in Section 4.5, "Simplified Mnemonics that Incorporate the BO Operand," use one of these two methods to specify a CR bit.

• Additional simplified mnemonics are specified that incorporate CR conditions that would otherwise be specified by the BI operand, so the BI operand is replaced by the **cr**S operand to specify the CR field, CR0–CR7. See Section 4.4.1, "BI Operand Instruction Encoding."

These mnemonics are described in Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)."

# 4.4.1 BI Operand Instruction Encoding

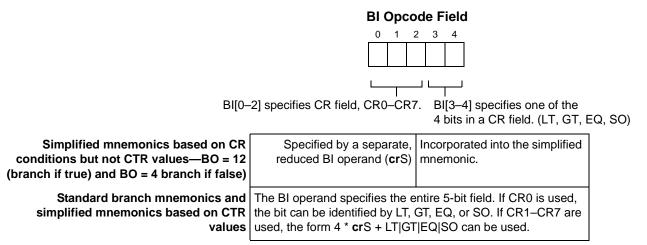

The entire 5-bit BI field, shown in Figure 3, represents the bit number for the CR bit to be tested. For standard branch mnemonics and for branch simplified mnemonics that do not incorporate a CR condition, the BI operand provides all 5 bits.

For simplified branch mnemonics described in Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)," the BI operand is replaced by a **cr**S operand. To understand this, it is useful to view the BI operand as comprised of two parts. As Figure 3 shows, BI[0–2] indicates the CR field and BI[3–4] represents the condition to test.

#### **Branch Instruction Simplified Mnemonics**

Figure 3. BI Field (Bits 11-14 of the Instruction Encoding)

Integer record-form instructions update CR0 and floating-point record-form instructions update CR1, as described in Table 7.

#### 4.4.1.1 Specifying a CR Bit

Note that the AIM version of the PowerPC architecture numbers CR bits 0–31 and Book E numbers them 32–63. However, no adjustment is necessary to the code; in Book E devices, 32 is automatically added to the BI value, as shown in Table 7 and Table 8.

Table 7. CR0 and CR1 Fields as Updated by Integer and Floating-Point Instructions

| CR <i>n</i> Bit | CR  | Bits   | Е   | BI  | Description                                                             |  |

|-----------------|-----|--------|-----|-----|-------------------------------------------------------------------------|--|

| OK// Bit        | AIM | Book E | 0–2 | 3–4 |                                                                         |  |

| CR0[0]          | 0   | 32     | 000 | 00  | Negative (LT)—Set when the result is negative.                          |  |

| CR0[1]          | 1   | 33     | 000 | 01  | Positive (GT)—Set when the result is positive (and not zero).           |  |

| CR0[2]          | 2   | 34     | 000 | 10  | Zero (EQ)—Set when the result is zero.                                  |  |

| CR0[3]          | 3   | 35     | 000 | 11  | Summary overflow (SO). Copy of XER[SO] at the instruction's completion. |  |

| CR1[0]          | 4   | 36     | 001 | 00  | Copy of FPSCR[FX] at the instruction's completion.                      |  |

| CR1[1]          | 5   | 37     | 001 | 01  | Copy of FPSCR[FEX] at the instruction's completion.                     |  |

| CR1[2]          | 6   | 38     | 001 | 10  | Copy of FPSCR[VX] at the instruction's completion.                      |  |

| CR1[3]          | 7   | 39     | 001 | 11  | Copy of FPSCR[OX] at the instruction's completion.                      |  |

Some simplified mnemonics incorporate only the BO field (as described Section 4.2, "Eliminating the BO Operand"). If one of these simplified mnemonics is used and the CR must be accessed, the BI operand can be specified either as a numeric value or by using the symbols in Table 8.

Compare word instructions (described in Section 5, "Compare Word Simplified Mnemonics"), floating-point compare instructions, move to CR instructions, and others can also modify CR fields, so CR0 and CR1 may hold values that do not adhere to the meanings described in Table 7. CR logical instructions, described in Section 6, "Condition Register Logical Simplified Mnemonics," can update individual CR bits.

**Branch Instruction Simplified Mnemonics**

Table 8. BI Operand Settings for CR Fields for Branch Comparisons

| CR <i>n</i>     |                                                                                                                                                                 | CR E                                       | ВІ                                           |                                                      |     |                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit             | Bit Expression                                                                                                                                                  | AIM (BI<br>Operand)                        | Book E                                       | 0–2                                                  | 3–4 | Description                                                                                                                                                                                                                 |

| CRn[0]          | 4 * cr0 + lt (or lt) 4 * cr1 + lt 4 * cr2 + lt 4 * cr3+ lt 4 * cr4 + lt 4 * cr5 + lt 4 * cr6 + lt 4 * cr7 + lt                                                  | 0<br>4<br>8<br>12<br>16<br>20<br>24<br>28  | 32<br>36<br>40<br>44<br>48<br>52<br>56<br>60 | 000<br>001<br>010<br>011<br>100<br>101<br>110        | 00  | Less than or floating-point less than (LT, FL). For integer compare instructions: rA < SIMM or rB (signed comparison) or rA < UIMM or rB (unsigned comparison). For floating-point compare instructions: frA < frB.         |

| CR <i>n</i> [1] | 4 * cr0 + gt (or gt) 4 * cr1 + gt 4 * cr2 + gt 4 * cr3 + gt 4 * cr3 + gt 4 * cr4 + gt 4 * cr5 + gt 4 * cr6 + gt 4 * cr7 + gt                                    | 1<br>5<br>9<br>13<br>17<br>21<br>25<br>29  | 33<br>37<br>41<br>45<br>49<br>53<br>57<br>61 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 01  | Greater than or floating-point greater than (GT, FG). For integer compare instructions: rA > SIMM or rB (signed comparison) or rA > UIMM or rB (unsigned comparison). For floating-point compare instructions: frA > frB.   |

| CRn[2]          | 4 * cr0 + eq (or eq) 4 * cr1 + eq 4 * cr2 + eq 4 * cr3+ eq 4 * cr4 + eq 4 * cr5 + eq 4 * cr6 + eq 4 * cr7 + eq                                                  | 2<br>6<br>10<br>14<br>18<br>22<br>26<br>30 | 34<br>38<br>42<br>46<br>50<br>54<br>58<br>62 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 10  | Equal or floating-point equal (EQ, FE). For integer compare instructions: rA = SIMM, UIMM, or rB. For floating-point compare instructions: frA = frB.                                                                       |

| CR <i>n</i> [3] | 4 * cr0 + so/un (or so/un)<br>4 * cr1 + so/un<br>4 * cr2 + so/un<br>4 * cr3 + so/un<br>4 * cr4 + so/un<br>4 * cr5 + so/un<br>4 * cr6 + so/un<br>4 * cr7 + so/un | 3<br>7<br>11<br>15<br>19<br>23<br>27<br>31 | 35<br>39<br>43<br>47<br>51<br>55<br>59<br>63 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 11  | Summary overflow or floating-point unordered (SO, FU). For integer compare instructions, this is a copy of XER[SO] at instruction completion. For floating-point compare instructions, one or both of frA and frB is a NaN. |

To provide simplified mnemonics for every possible combination of BO and BI (that is, including bits that identified the CR field) would require  $2^{10} = 1024$  mnemonics, most of which would be only marginally useful. The abbreviated set in Section 4.5, "Simplified Mnemonics that Incorporate the BO Operand," covers useful cases. Unusual cases can be coded using a standard branch conditional syntax.

### 4.4.1.2 The crS Operand

The **cr**S symbols are shown in Table 9. Note that either the symbol or the operand value can be used in the syntax used with the simplified mnemonic.

**Table 9. CR Field Identification Symbols**

| Symbol                                       | BI[0-2] | CR Bits |

|----------------------------------------------|---------|---------|

| cr0 (default, can be eliminated from syntax) | 000     | 32–35   |

| cr1                                          | 001     | 36–39   |

**Branch Instruction Simplified Mnemonics**

Table 9. CR Field Identification Symbols (continued)

| Symbol | BI[0-2] | CR Bits |

|--------|---------|---------|

| cr2    | 010     | 40–43   |

| cr3    | 011     | 44–47   |

| cr4    | 100     | 48–51   |

| cr5    | 101     | 52–55   |

| cr6    | 110     | 56–59   |

| cr7    | 111     | 60–63   |

To identify a CR bit, an expression in which a CR field symbol is multiplied by 4 and then added to a bit-number-within-CR-field symbol can be used, (for example,  $\mathbf{cr0} * \mathbf{4} + \mathbf{eq}$ ).

# 4.5 Simplified Mnemonics that Incorporate the BO Operand

The mnemonics in Table 10 allow common BO operand encodings to be specified as part of the mnemonic, along with the absolute address (AA) and set link register bits (LK). There are no simplified mnemonics for relative and absolute unconditional branches. For these, the basic mnemonics **b**, **ba**, **bl**, and **bla** are used.

**Table 10. Branch Simplified Mnemonics**

| Branch Semantics                                     | LR Update Not Enabled |        |         | LR Update Enabled |        |         |          |        |

|------------------------------------------------------|-----------------------|--------|---------|-------------------|--------|---------|----------|--------|

| Branch Semantics                                     | bc                    | bca    | bclr    | bcctr             | bcl    | bcla    | bclrl    | bcctrl |

| Branch unconditionally <sup>1</sup>                  | _                     | _      | blr     | bctr              | _      | _       | biri     | bctrl  |

| Branch if condition true                             | bt                    | bta    | btlr    | btctr             | btl    | btla    | btlrl    | btctrl |

| Branch if condition false                            | bf                    | bfa    | bflr    | bfctr             | bfl    | bfla    | bflrl    | bfctrl |

| Decrement CTR, branch if CTR ≠ 0 <sup>1</sup>        | bdnz                  | bdnza  | bdnzlr  | _                 | bdnzl  | bdnzla  | bdnziri  | _      |

| Decrement CTR, branch if CTR ≠ 0 and condition true  | bdnzt                 | bdnzta | bdnztlr | _                 | bdnztl | bdnztla | bdnztiri | _      |

| Decrement CTR, branch if CTR ≠ 0 and condition false | bdnzf                 | bdnzfa | bdnzflr | _                 | bdnzfl | bdnzfla | bdnzflrl | _      |

| Decrement CTR, branch if CTR = 0 <sup>1</sup>        | bdz                   | bdza   | bdzlr   | _                 | bdzl   | bdzla   | bdziri   | _      |

| Decrement CTR, branch if CTR = 0 and condition true  | bdzt                  | bdzta  | bdztlr  | _                 | bdztl  | bdztla  | bdztiri  | _      |

| Decrement CTR, branch if CTR = 0 and condition false | bdzf                  | bdzfa  | bdzflr  | _                 | bdzfl  | bdzfla  | bdzflrl  | _      |

Simplified mnemonics for branch instructions that do not test CR bits should specify only a target. Otherwise a programming error may occur.

**Branch Instruction Simplified Mnemonics**

Table 11 shows the syntax for basic simplified branch mnemonics

**Table 11. Branch Instructions**

| Instruction                          | Standard<br>Mnemonic | Syntax            | Simplified<br>Mnemonic                                                                                | Syntax                       |

|--------------------------------------|----------------------|-------------------|-------------------------------------------------------------------------------------------------------|------------------------------|

| Branch                               | b (ba bl bla)        | target_addr       | N/A, syntax does not include BO                                                                       |                              |

| Branch Conditional                   | bc (bca bcl bcla)    | BO,BI,target_addr | $\mathbf{b}x^1$ ( $\mathbf{b}x\mathbf{a}$ $\mathbf{b}x\mathbf{d}$ $\mathbf{b}x\mathbf{d}\mathbf{a}$ ) | BI <sup>2</sup> ,target_addr |

| Branch Conditional to Link Register  | bcir (bciri)         | BO,BI             | bxlr (bxlrl)                                                                                          | BI                           |

| Branch Conditional to Count Register | bcctr (bcctrl)       | BO,BI             | bxctr (bxctrl)                                                                                        | ВІ                           |

<sup>&</sup>lt;sup>1</sup> x stands for one of the symbols in Table 6, where applicable.

The simplified mnemonics in Table 10 that test a condition require a corresponding CR bit as the first operand (as the examples 2–5 in Section 4.5.1, "Examples that Eliminate the BO Operand," below illustrate). The symbols in Table 9 can be used in place of a numeric value.

### 4.5.1 Examples that Eliminate the BO Operand

The simplified mnemonics in Table 10 are used in the following examples:

1. Decrement CTR and branch if it is still nonzero (closure of a loop controlled by a count loaded into CTR) (note that no CR bits are tested).

**bdnz** target

equivalent to

**bc 16,0,***target*

Because this instruction does not test a CR bit, the simplified mnemonic should specify only a target operand. Specifying a CR (for example, **bdnz** 0, *target* or **bdnz** cr0, *target*) may be considered a programming error. Subsequent examples test conditions).

2. Same as (1) but branch only if CTR is nonzero and equal condition in CR0.

bdnzt eq,target

equivalent to

bc 8,2,target

Other equivalents include **bdnzt 2**, target or the unlikely **bdnzt 4 \* cr0** + **eq**, target

3. Same as (2), but equal condition is in CR5.

bdnzt 4 \* cr5 + eq,target

equivalent to

bc 8,22,target

**bdnzt 22,***target* would also work

4. Branch if bit 59 of CR is false.

bf 27,target

equivalent to

bc 4,27,target

**bf 4 \* cr6 + so,** target would also work

5. Same as (4), but set the link register. This is a form of conditional call.

bfl 27,target

equivalent to

bcl 4,27,target

Table 12 lists simplified mnemonics and syntax for **bc** and **bca** without LR updating.

Table 12. Simplified Mnemonics for bc and bca without LR Update

| Branch Semantics                      | bc              | Simplified<br>Mnemonic | bca              | Simplified<br>Mnemonic |  |

|---------------------------------------|-----------------|------------------------|------------------|------------------------|--|

| Branch unconditionally                | _               | _                      | _                | _                      |  |

| Branch if condition true <sup>1</sup> | bc 12,BI,target | bt BI,target           | bca 12,BI,target | bta BI,target          |  |

<sup>&</sup>lt;sup>2</sup> BI can be a numeric value or an expression as shown in Table 9.

#### **Branch Instruction Simplified Mnemonics**

Table 12. Simplified Mnemonics for bc and bca without LR Update (continued)

| Branch Semantics                                     | bc              | Simplified<br>Mnemonic          | bca              | Simplified<br>Mnemonic           |

|------------------------------------------------------|-----------------|---------------------------------|------------------|----------------------------------|

| Branch if condition false <sup>1</sup>               | bc 4,BI,target  | bf BI,target                    | bca 4,BI,target  | bfa BI,target                    |

| Decrement CTR, branch if CTR ≠ 0                     | bc 16,0,target  | <b>bdnz</b> target <sup>2</sup> | bca 16,0,target  | <b>bdnza</b> target <sup>2</sup> |

| Decrement CTR, branch if CTR ≠ 0 and condition true  | bc 8,BI,target  | bdnzt Bl,target                 | bca 8,BI,target  | bdnzta BI,target                 |

| Decrement CTR, branch if CTR ≠ 0 and condition false | bc 0,BI,target  | bdnzf Bl,target                 | bca 0,BI,target  | bdnzfa BI,target                 |

| Decrement CTR, branch if CTR = 0                     | bc 18,0,target  | <b>bdz</b> target <sup>2</sup>  | bca 18,0,target  | bdza target <sup>2</sup>         |

| Decrement CTR, branch if CTR = 0 and condition true  | bc 10,BI,target | bdzt BI,target                  | bca 10,BI,target | bdzta BI,target                  |

| Decrement CTR, branch if CTR = 0 and condition false | bc 2,BI,target  | bdzf Bl,target                  | bca 2,BI,target  | bdzfa Bl,target                  |

Instructions for which B0 is either 12 (branch if condition true) or 4 (branch if condition false) do not depend on the CTR value and can be alternately coded by incorporating the condition specified by the BI field, as described in Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)."

Table 13 lists simplified mnemonics and syntax for **bclr** and **bcctr** without LR updating.

Table 13. Simplified Mnemonics for bclr and bcctr without LR Update

| Branch Semantics                                     | bclr       | Simplified<br>Mnemonic | bcctr       | Simplified<br>Mnemonic |

|------------------------------------------------------|------------|------------------------|-------------|------------------------|

| Branch unconditionally                               | bclr 20,0  | blr <sup>1</sup>       | bcctr 20,0  | bctr <sup>1</sup>      |

| Branch if condition true <sup>2</sup>                | bclr 12,BI | btlr Bl                | bcctr 12,BI | btctr BI               |

| Branch if condition false <sup>2</sup>               | bclr 4,Bl  | bflr Bl                | bcctr 4,BI  | bfctr BI               |

| Decrement CTR, branch if CTR ≠ 0                     | bclr 16,BI | bdnzlr Bl              | _           | _                      |

| Decrement CTR, branch if CTR ≠ 0 and condition true  | bclr 8,BI  | bdnztlr Bl             | _           | _                      |

| Decrement CTR, branch if CTR ≠ 0 and condition false | bclr 0,Bl  | bdnzflr Bl             | _           | _                      |

| Decrement CTR, branch if CTR = 0                     | bclr 18,0  | bdzlr <sup>1</sup>     | _           | _                      |

| Decrement CTR, branch if CTR = 0 and condition true  | bclr 8,BI  | bdnztlr Bl             | _           | _                      |

| Decrement CTR, branch if CTR = 0 and condition false | bclr 2,BI  | bdzflr Bl              | _           | _                      |

Simplified mnemonics for branch instructions that do not test a CR bit should not specify one; a programming error may occur.

<sup>&</sup>lt;sup>2</sup> Simplified mnemonics for branch instructions that do not test CR bits should specify only a target. Otherwise a programming error may occur.

Instructions for which B0 is 12 (branch if condition true) or 4 (branch if condition false) do not depend on a CTR value and can be alternately coded by incorporating the condition specified by the BI field. See Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)."

**Branch Instruction Simplified Mnemonics**

Table 14 provides simplified mnemonics and syntax for **bcl** and **bcla**.

Table 14. Simplified Mnemonics for bcl and bcla with LR Update

| Branch Semantics                                     | bcl              | Simplified<br>Mnemonic           | bcla              | Simplified<br>Mnemonic           |

|------------------------------------------------------|------------------|----------------------------------|-------------------|----------------------------------|

| Branch unconditionally                               | _                | _                                | _                 | _                                |

| Branch if condition true <sup>1</sup>                | bcl 12,BI,target | btl Bl,target                    | bcla 12,BI,target | btla Bl,target                   |

| Branch if condition false 1                          | bcl 4,Bl,target  | bfl Bl,target                    | bcla 4,BI,target  | bfla Bl,target                   |

| Decrement CTR, branch if CTR ≠ 0                     | bcl 16,0,target  | <b>bdnzl</b> target <sup>2</sup> | bcla 16,0,target  | bdnzla target 2                  |

| Decrement CTR, branch if CTR ≠ 0 and condition true  | bcl 8,0,target   | bdnztl Bl,target                 | bcla 8,BI,target  | bdnztla BI,target                |

| Decrement CTR, branch if CTR ≠ 0 and condition false | bcl 0,Bl,target  | bdnzfl Bl,target                 | bcla 0,BI,target  | bdnzfla BI,target                |

| Decrement CTR, branch if CTR = 0                     | bcl 18,BI,target | <b>bdzl</b> target <sup>2</sup>  | bcla 18,BI,target | <b>bdzla</b> target <sup>2</sup> |

| Decrement CTR, branch if CTR = 0 and condition true  | bcl 10,Bl,target | bdztl BI,target                  | bcla 10,BI,target | bdztla BI,target                 |

| Decrement CTR, branch if CTR = 0 and condition false | bcl 2,Bl,target  | bdzfl Bl,target                  | bcla 2,BI,target  | bdzfla BI,target                 |

Instructions for which B0 is either 12 (branch if condition true) or 4 (branch if condition false) do not depend on the CTR value and can be alternately coded by incorporating the condition specified by the BI field. See Section 4.6, "Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)."

Table 15 provides simplified mnemonics and syntax for **bclrl** and **bcctrl** with LR updating.

Table 15. Simplified Mnemonics for bolrl and bootrl with LR Update

| Branch Semantics                                     | bclrl        | Simplified<br>Mnemonic | bcctrl       | Simplified<br>Mnemonic |

|------------------------------------------------------|--------------|------------------------|--------------|------------------------|

| Branch unconditionally                               | bclrl 20,0   | biri 1                 | bcctrl 20,0  | bctrl <sup>1</sup>     |

| Branch if condition true                             | bciri 12,Bi  | btlrl Bl               | bcctrl 12,BI | btctrl Bl              |

| Branch if condition false                            | bclrl 4,Bl   | bflrl Bl               | bcctrl 4,Bl  | bfctrl Bl              |

| Decrement CTR, branch if CTR ≠ 0                     | bclrl 16,0   | bdnziri <sup>1</sup>   | _            | _                      |

| Decrement CTR, branch if CTR ≠ 0 and condition true  | bclrl 8,Bl   | bdnztlrl Bl            | _            | _                      |

| Decrement CTR, branch if CTR ≠ 0 and condition false | bclrl 0,Bl   | bdnzflrl Bl            | _            | _                      |

| Decrement CTR, branch if CTR = 0                     | bclrl 18,0   | bdziri <sup>1</sup>    | _            | _                      |

| Decrement CTR, branch if CTR = 0 and condition true  | bciri 10, Bi | bdztlrl Bl             | _            | _                      |

| Decrement CTR, branch if CTR = 0 and condition false | bclrl 2,Bl   | bdzfiri Bi             | _            | _                      |

Simplified mnemonics for branch instructions that do not test a CR bit should not specify one. A programming error may occur.

<sup>&</sup>lt;sup>2</sup> Simplified mnemonics for branch instructions that do not test CR bits should specify only a target. A programming error may occur.

# 4.6 Simplified Mnemonics that Incorporate CR Conditions (Eliminates BO and Replaces BI with crS)

The mnemonics in Table 18 are variations of the branch-if-condition-true (BO = 12) and branch-if-condition-false (BO = 4) encodings. Because these instructions do not depend on the CTR, the true/false conditions specified by BO can be combined with the CR test bit specified by BI to create a different set of simplified mnemonics that eliminates the BO operand and the portion of the BI operand (BI[3–4]) that specifies one of the four possible test bits. However, the simplified mnemonic cannot specify in which of the eight CR fields the test bit falls, so the BI operand is replaced by a **crS** operand.

The standard codes shown in Table 16 are used for the most common combinations of branch conditions. Note that for ease of programming, these codes include synonyms; for example, less than or equal (**le**) and not greater than (**ng**) achieve the same result.

#### **NOTE**

A CR field symbol, **cr0–cr7**, is used as the first operand after the simplified mnemonic. If the default, CR0, is used, no **cr**S is necessary,

**Table 16. Standard Coding for Branch Conditions**

| Code | Description                                      | Equivalent | Bit Tested |

|------|--------------------------------------------------|------------|------------|

| lt   | Less than                                        | _          | LT         |

| le   | Less than or equal (equivalent to <b>ng</b> )    | ng         | GT         |

| eq   | Equal                                            | _          | EQ         |

| ge   | Greater than or equal (equivalent to <b>nl</b> ) | nl         | LT         |

| gt   | Greater than                                     | _          | GT         |

| nl   | Not less than (equivalent to <b>ge</b> )         | ge         | LT         |

| ne   | Not equal                                        | _          | EQ         |

| ng   | Not greater than (equivalent to <b>le</b> )      | le         | GT         |

| so   | Summary overflow                                 | _          | SO         |

| ns   | Not summary overflow                             | _          | SO         |

| un   | Unordered (after floating-point comparison)      | _          | SO         |

| nu   | Not unordered (after floating-point comparison)  | _          | SO         |

Table 17 shows the syntax for simplified branch mnemonics that incorporate CR conditions. Here, **cr**S replaces a BI operand to specify only a CR field (because the specific CR bit within the field is now part of the simplified mnemonic. Note that the default is CR0; if no **cr**S is specified, CR0 is used.

**Branch Instruction Simplified Mnemonics**

Table 17. Branch Instructions and Simplified Mnemonics that Incorporate CR Conditions

| Instruction                          | Standard<br>Mnemonic | Syntax            | Simplified<br>Mnemonic         | Syntax                                |

|--------------------------------------|----------------------|-------------------|--------------------------------|---------------------------------------|

| Branch                               | b (ba bl bla)        | target_addr       | _                              | _                                     |

| Branch Conditional                   | bc (bca bcl bcla)    | BO,BI,target_addr | bx <sup>1</sup> (bxa bxl bxla) | <b>cr</b> S <sup>2</sup> ,target_addr |

| Branch Conditional to Link Register  | bcir (bciri)         | BO,BI             | bxlr (bxlrl)                   | crS                                   |

| Branch Conditional to Count Register | bcctr (bcctrl)       | BO,BI             | bxctr (bxctrl)                 | <b>cr</b> S                           |

$<sup>^{1}</sup>$  x stands for one of the symbols in Table 16, where applicable.

Table 18 shows the simplified branch mnemonics incorporating conditions.

**Table 18. Simplified Mnemonics with Comparison Conditions**

| Branch Semantics                | LR Update Not Enabled |      |       | LR Update Enabled |      |       |        |         |

|---------------------------------|-----------------------|------|-------|-------------------|------|-------|--------|---------|

| Branch Semantics                | bc                    | bca  | bclr  | bcctr             | bcl  | bcla  | bclrl  | bcctrl  |

| Branch if less than             | blt                   | blta | bltlr | bltctr            | bltl | bltla | bltlrl | bltctrl |

| Branch if less than or equal    | ble                   | blea | blelr | blectr            | blel | blela | bleiri | blectrl |

| Branch if equal                 | beq                   | beqa | beqlr | beqctr            | beql | beqla | beqiri | beqctrl |

| Branch if greater than or equal | bge                   | bgea | bgelr | bgectr            | bgel | bgela | bgelrl | bgectrl |

| Branch if greater than          | bgt                   | bgta | bgtlr | bgtctr            | bgtl | bgtla | bgtlrl | bgtctrl |

| Branch if not less than         | bnl                   | bnla | bnllr | bnlctr            | bnll | bnlla | bnllrl | bnlctrl |

| Branch if not equal             | bne                   | bnea | bnelr | bnectr            | bnel | bnela | bnelrl | bnectrl |

| Branch if not greater than      | bng                   | bnga | bnglr | bngctr            | bngl | bngla | bnglrl | bngctrl |

| Branch if summary overflow      | bso                   | bsoa | bsolr | bsoctr            | bsol | bsola | bsolrl | bsoctrl |

| Branch if not summary overflow  | bns                   | bnsa | bnslr | bnsctr            | bnsl | bnsla | bnsiri | bnsctrl |

| Branch if unordered             | bun                   | buna | bunlr | bunctr            | bunl | bunla | buniri | bunctrl |

| Branch if not unordered         | bnu                   | bnua | bnulr | bnuctr            | bnul | bnula | bnulrl | bnuctrl |

Instructions using the mnemonics in Table 18 indicate the condition bit, but not the CR field. If no field is specified, CR0 is used. The CR field symbols defined in Table 9 (**cr0–cr7**) are used for this operand, as shown in examples 2–4 of Section 4.6.1, "Branch Simplified Mnemonics that Incorporate CR Conditions: Examples," below.

# 4.6.1 Branch Simplified Mnemonics that Incorporate CR Conditions: Examples

The following examples use the simplified mnemonics shown in Table 18:

1. Branch if CR0 reflects not-equal condition.

bne target equivalent to bc 4,2,target

2. Same as (1) but condition is in CR3.

bne cr3,target equivalent to bc 4,14,target

<sup>&</sup>lt;sup>2</sup> BI can be a numeric value or an expression as shown in Table 9.

#### **Branch Instruction Simplified Mnemonics**

3. Branch to an absolute target if CR4 specifies greater than condition, setting the LR. This is a form of conditional call.

**bgtla cr4**, target equivalent to **bcla 12**, 17, target

4. Same as (3), but target address is in the CTR.

bgtctrl cr4 equivalent to bcctrl 12,17

# 4.6.2 Branch Simplified Mnemonics that Incorporate CR Conditions: Listings

Table 19 shows simplified branch mnemonics and syntax for bc and bca without LR updating.

Table 19. Simplified Mnemonics for bc and bca without Comparison Conditions or LR Updating

| Branch Semantics                | bc                                    | Simplified Mnemonic | bca                                    | Simplified Mnemonic |

|---------------------------------|---------------------------------------|---------------------|----------------------------------------|---------------------|

| Branch if less than             | <b>bc 12,</b> Bl <sup>1</sup> ,target | blt crS,target      | <b>bca 12</b> ,Bl <sup>1</sup> ,target | blta crS,target     |

| Branch if less than or equal    | <b>bc 4,</b> Bl <sup>2</sup> ,target  | ble crS,target      | <b>bca 4</b> ,Bl <sup>2</sup> ,target  | blea crS,target     |

| Branch if not greater than      |                                       | bng crS,target      |                                        | bnga crS,target     |

| Branch if equal                 | <b>bc 12,</b> Bl <sup>3</sup> ,target | beq crS,target      | <b>bca 12,</b> Bl <sup>3</sup> ,target | beqa crS,target     |

| Branch if greater than or equal | <b>bc 4,</b> BI <sup>1</sup> ,target  | bge crS,target      | <b>bca 4</b> ,Bl <sup>1</sup> ,target  | bgea crS,target     |

| Branch if not less than         |                                       | bnl crS,target      |                                        | bnla crS,target     |

| Branch if greater than          | <b>bc 12,</b> Bl <sup>2</sup> ,target | bgt crS,target      | <b>bca 12,</b> Bl <sup>2</sup> ,target | bgta crS,target     |

| Branch if not equal             | <b>bc 4,</b> Bl <sup>3</sup> ,target  | bne crS,target      | <b>bca 4,</b> Bl <sup>3</sup> ,target  | bnea crS,target     |

| Branch if summary overflow      | <b>bc 12</b> ,Bl <sup>4</sup> ,target | bso crS,target      | <b>bca 12,</b> Bl <sup>4</sup> ,target | bsoa crS,target     |

| Branch if unordered             |                                       | bun crS,target      |                                        | buna crS,target     |

| Branch if not summary overflow  | <b>bc 4,</b> Bl <sup>4</sup> ,target  | bns crS,target      | <b>bca 4,</b> Bl <sup>4</sup> ,target  | bnsa crS,target     |

| Branch if not unordered         |                                       | bnu crS,target      |                                        | bnua crS,target     |

<sup>&</sup>lt;sup>1</sup> The value in the BI operand selects CR*n*[0], the LT bit.

Table 20 shows simplified branch mnemonics and syntax for **bclr** and **bcctr** without LR updating.

Table 20. Simplified Mnemonics for bclr and bcctr without Comparison Conditions and LR Updating

| Branch Semantics                | bclr                                   | Simplified<br>Mnemonic | bcctr                                    | Simplified<br>Mnemonic |

|---------------------------------|----------------------------------------|------------------------|------------------------------------------|------------------------|

| Branch if less than             | bclr 12,Bl <sup>1</sup> ,target        | bitir crS,target       | <b>bcctr 12,</b> Bl <sup>1</sup> ,target | bltctr crS,target      |

| Branch if less than or equal    | <b>bclr 4</b> ,Bl <sup>2</sup> ,target | blelr crS,target       | <b>bcctr 4,</b> Bl <sup>2</sup> ,target  | blectr crS,target      |

| Branch if not greater than      |                                        | bnglr crS,target       |                                          | bngctr crS,target      |

| Branch if equal                 | bclr 12,Bl <sup>3</sup> ,target        | beqlr crS,target       | <b>bcctr 12,</b> BI <sup>3</sup> ,target | beqctr crS,target      |

| Branch if greater than or equal | <b>bclr 4</b> ,Bl <sup>1</sup> ,target | bgelr crS,target       | <b>bcctr 4,</b> Bl <sup>1</sup> ,target  | bgectr crS,target      |

| Branch if not less than         |                                        | bnllr crS,target       |                                          | bnlctr crS,target      |

<sup>&</sup>lt;sup>2</sup> The value in the BI operand selects CR*n*[1], the GT bit.

<sup>&</sup>lt;sup>3</sup> The value in the BI operand selects CR*n*[2], the EQ bit.

<sup>&</sup>lt;sup>4</sup> The value in the BI operand selects CR*n*[3], the SO bit.

**Branch Instruction Simplified Mnemonics**

Table 20. Simplified Mnemonics for bclr and bcctr without Comparison Conditions and LR Updating (continued)

| Branch Semantics               | bcir                                    | Simplified<br>Mnemonic | bcctr                                    | Simplified<br>Mnemonic |

|--------------------------------|-----------------------------------------|------------------------|------------------------------------------|------------------------|

| Branch if greater than         | <b>bclr 12,</b> Bl <sup>2</sup> ,target | bgtlr crS,target       | <b>bcctr 12</b> ,Bl <sup>2</sup> ,target | bgtctr crS,target      |

| Branch if not equal            | <b>bclr 4,</b> Bl <sup>3</sup> ,target  | bnelr crS,target       | <b>bcctr 4,</b> Bl <sup>3</sup> ,target  | bnectr crS,target      |

| Branch if summary overflow     | bclr 12,Bl <sup>4</sup> ,target         | bsolr crS,target       | <b>bcctr 12</b> ,BI <sup>4</sup> ,target | bsoctr crS,target      |

| Branch if unordered            |                                         | bunlr crS,target       |                                          | bunctr crS,target      |

| Branch if not summary overflow | <b>bclr 4,</b> Bl <sup>4</sup> ,target  | bnslr crS,target       | <b>bcctr 4,</b> BI <sup>4</sup> ,target  | bnsctr crS,target      |

| Branch if not unordered        |                                         | bnulr crS,target       |                                          | bnuctr crS,target      |

<sup>&</sup>lt;sup>1</sup> The value in the BI operand selects CR*n*[0], the LT bit.

Table 21 shows simplified branch mnemonics and syntax for **bcl** and **bcla**.

Table 21. Simplified Mnemonics for bcl and bcla with Comparison Conditions and LR Updating

| Branch Semantics                | bcl                                    | Simplified<br>Mnemonic | bcla                                    | Simplified<br>Mnemonic |

|---------------------------------|----------------------------------------|------------------------|-----------------------------------------|------------------------|

| Branch if less than             | <b>bcl 12,</b> Bl <sup>1</sup> ,target | bltl crS,target        | <b>bcla 12</b> ,Bl <sup>1</sup> ,target | bltla crS,target       |

| Branch if less than or equal    | <b>bcl 4,</b> Bl <sup>2</sup> ,target  | blel crS,target        | <b>bcla 4,</b> Bl <sup>2</sup> ,target  | blela crS,target       |

| Branch if not greater than      |                                        | bngl crS,target        |                                         | bngla crS,target       |

| Branch if equal                 | <b>bcl 12,</b> Bl <sup>3</sup> ,target | beql crS,target        | <b>bcla 12</b> ,Bl <sup>3</sup> ,target | beqla crS,target       |

| Branch if greater than or equal | <b>bcl 4,</b> Bl <sup>1</sup> ,target  | bgel crS,target        | <b>bcla 4,</b> Bl <sup>1</sup> ,target  | bgela crS,target       |

| Branch if not less than         |                                        | bnll crS,target        |                                         | bnlla crS,target       |

| Branch if greater than          | <b>bcl 12,</b> Bl <sup>2</sup> ,target | bgtl crS,target        | <b>bcla 12,</b> Bl <sup>2</sup> ,target | bgtla crS,target       |

| Branch if not equal             | <b>bcl 4,</b> Bl <sup>3</sup> ,target  | bnel crS,target        | <b>bcla 4,</b> Bl <sup>3</sup> ,target  | bnela crS,target       |

| Branch if summary overflow      | bcl 12,Bl <sup>4</sup> ,target         | bsol crS,target        | <b>bcla 12</b> ,Bl <sup>4</sup> ,target | bsola crS,target       |

| Branch if unordered             |                                        | bunl crS,target        |                                         | bunla crS,target       |

| Branch if not summary overflow  | <b>bcl 4,</b> Bl <sup>4</sup> ,target  | bnsl crS,target        | <b>bcla 4,</b> Bl <sup>4</sup> ,target  | bnsla crS,target       |

| Branch if not unordered         |                                        | bnul crS,target        |                                         | bnula crS,target       |

The value in the BI operand selects CRn[0], the LT bit.

<sup>&</sup>lt;sup>2</sup> The value in the BI operand selects CR*n*[1], the GT bit.

<sup>&</sup>lt;sup>3</sup> The value in the BI operand selects CR*n*[2], the EQ bit.

<sup>&</sup>lt;sup>4</sup> The value in the BI operand selects CR*n*[3], the SO bit.

<sup>&</sup>lt;sup>2</sup> The value in the BI operand selects CR*n*[1], the GT bit.

<sup>&</sup>lt;sup>3</sup> The value in the BI operand selects CR*n*[2], the EQ bit.

<sup>&</sup>lt;sup>4</sup> The value in the BI operand selects CR*n*[3], the SO bit.

#### **Compare Word Simplified Mnemonics**

Table 22 shows the simplified branch mnemonics and syntax for **bclrl** and **bcctrl** with LR updating.

Table 22. Simplified Mnemonics for bclrl and bcctrl with Comparison Conditions and LR Update

| Branch Semantics                | bclrl                                    | Simplified<br>Mnemonic | bcctrl                                    | Simplified<br>Mnemonic |

|---------------------------------|------------------------------------------|------------------------|-------------------------------------------|------------------------|

| Branch if less than             | <b>bciri 12</b> ,Bl <sup>1</sup> ,target | bitiri crS,target      | <b>bcctrl 12</b> ,Bl <sup>1</sup> ,target | bltctrl crS,target     |

| Branch if less than or equal    | <b>bcirl 4,</b> Bl <sup>2</sup> ,target  | blelrl crS,target      | <b>bcctrl 4,</b> Bl <sup>2</sup> ,target  | blectrl crS,target     |

| Branch if not greater than      |                                          | bnglrl crS,target      |                                           | bngctrl crS,target     |

| Branch if equal                 | <b>bcIrI 12</b> ,BI <sup>3</sup> ,target | beqiri crS,target      | <b>bcctrl 12</b> ,Bl <sup>3</sup> ,target | beqctrl crS,target     |

| Branch if greater than or equal | <b>bcIrI 4,</b> BI <sup>1</sup> ,target  | bgelrl crS,target      | <b>bcctrl 4,</b> Bl <sup>1</sup> ,target  | bgectrl crS,target     |

| Branch if not less than         |                                          | bnllrl crS,target      |                                           | bnlctrl crS,target     |

| Branch if greater than          | bciri 12,BI2,target                      | bgtlrl crS,target      | <b>bcctrl 12</b> ,Bl <sup>2</sup> ,target | bgtctrl crS,target     |

| Branch if not equal             | <b>bcIrI 4,</b> BI <sup>3</sup> ,target  | bnelrl crS,target      | <b>bcctrl 4,</b> Bl <sup>3</sup> ,target  | bnectrl crS,target     |

| Branch if summary overflow      | bclrl 12,Bl <sup>4</sup> ,target         | bsolrl crS,target      | <b>bcctrl 12</b> ,Bl <sup>4</sup> ,target | bsoctrl crS,target     |

| Branch if unordered             |                                          | buniri crS,target      |                                           | bunctrl crS,target     |

| Branch if not summary overflow  | <b>bcIrl 4,</b> BI <sup>4</sup> ,target  | bnslrl crS,target      | <b>bcctrl 4,</b> Bl <sup>4</sup> ,target  | bnsctrl crS,target     |

| Branch if not unordered         |                                          | bnulrl crS,target      |                                           | bnuctrl crS,target     |

<sup>&</sup>lt;sup>1</sup> The value in the BI operand selects CR*n*[0], the LT bit.

# **5 Compare Word Simplified Mnemonics**

In compare word instructions, the L operand indicates a word (L=0) or double-word (L=1). Simplified mnemonics in Table 23 eliminate the L operand for word comparisons.

**Table 23. Word Compare Simplified Mnemonics**

| Operation                      | Simplified Mnemonic | Equivalent to:      |

|--------------------------------|---------------------|---------------------|

| Compare Word Immediate         | cmpwi crD,rA,SIMM   | cmpi crD,0,rA,SIMM  |

| Compare Word                   | cmpw crD,rA,rB      | cmp crD,0,rA,rB     |

| Compare Logical Word Immediate | cmplwi crD,rA,UIMM  | cmpli crD,0,rA,UIMM |

| Compare Logical Word           | cmplw crD,rA,rB     | cmpl crD,0,rA,rB    |

As with branch mnemonics, the **cr**D field of a compare instruction can be omitted if CR0 is used, as shown in examples 1 and 3 below. Otherwise, the target CR field must be specified as the first operand. The following examples use word compare mnemonics:

1. Compare rA with immediate value 100 as signed 32-bit integers and place result in CR0. cmpwi rA,100 equivalent to cmpi 0,0,rA,100

2. Same as (1), but place results in CR4.

cmpwi cr4,rA,100 equivalent to cmpi 4,0,rA,100

3. Compare **r**A and **r**B as unsigned 32-bit integers and place result in CR0. **cmplw r**A,**r**B equivalent to **cmpl 0,0,r**A,**r**B

<sup>&</sup>lt;sup>2</sup> The value in the BI operand selects CR*n*[1], the GT bit.

<sup>&</sup>lt;sup>3</sup> The value in the BI operand selects CR*n*[2], the EQ bit.

<sup>4</sup> The value in the BI operand selects CRn[3], the SO bit.

# 6 Condition Register Logical Simplified Mnemonics

The CR logical instructions, shown in Table 24, can be used to set, clear, copy, or invert a given CR bit. Simplified mnemonics allow these operations to be coded easily. Note that the symbols defined in Table 8 can be used to identify the CR bit.

**Table 24. Condition Register Logical Simplified Mnemonics**

| Operation                | Simplified Mnemonic | Equivalent to  |

|--------------------------|---------------------|----------------|

| Condition register set   | crset bx            | creqv bx,bx,bx |

| Condition register clear | crcir bx            | crxor bx,bx,bx |

| Condition register move  | crmove bx,by        | cror bx,by,by  |

| Condition register not   | crnot bx,by         | crnor bx,by,by |

Examples using the CR logical mnemonics follow:

1. Set CR[57].

crset 25 equivalent to creqv 25,25,25

2. Clear CR0[SO].

crclr so equivalent to crxor 3,3,3

3. Same as (2), but clear CR3[SO].

$\operatorname{crclr} 4 * \operatorname{cr} 3 + \operatorname{so}$  equivalent to  $\operatorname{crxor} 15,15,15$

4. Invert the CR0[EQ].

**crnot eq,eq** equivalent to **crnor 2,2,2**

5. Same as (4), but CR4[EQ] is inverted and the result is placed into CR5[EQ].

crnot 4 \* cr5 + eq.4 \* cr4 + eq equivalent to crnor 22,18,18

# 7 Trap Instructions Simplified Mnemonics

The codes in Table 25 have been adopted for the most common combinations of trap conditions.

**Table 25. Standard Codes for Trap Instructions**

| Code | Description                  | TO Encoding | ٧ | > | = | <u <sup="">1</u> | >U <sup>2</sup> |

|------|------------------------------|-------------|---|---|---|------------------|-----------------|

| lt   | Less than                    | 16          | 1 | 0 | 0 | 0                | 0               |

| le   | Less than or equal           | 20          | 1 | 0 | 1 | 0                | 0               |

| eq   | Equal                        | 4           | 0 | 0 | 1 | 0                | 0               |

| ge   | Greater than or equal        | 12          | 0 | 1 | 1 | 0                | 0               |

| gt   | Greater than                 | 8           | 0 | 1 | 0 | 0                | 0               |

| nl   | Not less than                | 12          | 0 | 1 | 1 | 0                | 0               |

| ne   | Not equal                    | 24          | 1 | 1 | 0 | 0                | 0               |

| ng   | Not greater than             | 20          | 1 | 0 | 1 | 0                | 0               |

| IIt  | Logically less than          | 2           | 0 | 0 | 0 | 1                | 0               |

| lle  | Logically less than or equal | 6           | 0 | 0 | 1 | 1                | 0               |

#### **Trap Instructions Simplified Mnemonics**

Table 25. Standard Codes for Trap Instructions (continued)

| Code | Description                     | TO Encoding | < | > | = | <u <sup="">1</u> | >U <sup>2</sup> |

|------|---------------------------------|-------------|---|---|---|------------------|-----------------|

| lge  | Logically greater than or equal | 5           | 0 | 0 | 1 | 0                | 1               |

| lgt  | Logically greater than          | 1           | 0 | 0 | 0 | 0                | 1               |

| Inl  | Logically not less than         | 5           | 0 | 0 | 1 | 0                | 1               |

| Ing  | Logically not greater than      | 6           | 0 | 0 | 1 | 1                | 0               |

| _    | Unconditional                   | 31          | 1 | 1 | 1 | 1                | 1               |

<sup>&</sup>lt;sup>1</sup> The symbol '<U' indicates an unsigned less-than evaluation is performed.

The mnemonics in Table 26 are variations of trap instructions, with the most useful TO values represented in the mnemonic rather than specified as a numeric operand.

**Table 26. Trap Simplified Mnemonics**

| Trap Semantics                          | 32-Bit Con    | nparison    |

|-----------------------------------------|---------------|-------------|

| Trap Semantics                          | twi Immediate | tw Register |

| Trap unconditionally                    | _             | trap        |

| Trap if less than                       | twlti         | twlt        |

| Trap if less than or equal              | twlei         | twle        |

| Trap if equal                           | tweqi         | tweq        |

| Trap if greater than or equal           | twgei         | twge        |

| Trap if greater than                    | twgti         | twgt        |

| Trap if not less than                   | twnli         | twnl        |

| Trap if not equal                       | twnei         | twne        |

| Trap if not greater than                | twngi         | twng        |

| Trap if logically less than             | twllti        | twllt       |

| Trap if logically less than or equal    | twllei        | twlle       |

| Trap if logically greater than or equal | twlgei        | twlge       |

| Trap if logically greater than          | twlgti        | twlgt       |

| Trap if logically not less than         | twlnli        | twini       |

| Trap if logically not greater than      | twlngi        | twing       |

The following examples use the trap mnemonics shown in Table 26:

1. Trap if **r**A is not zero.

twnei rA,0 equivalent to twi 24,rA,0

2. Trap if **r**A is not equal to **r**B.

twne rA,rB equivalent to tw 24,rA,rB

3. Trap if **r**A is logically greater than 0x7FF.

**twlgti rA,**0x7FF equivalent to **twi 1,rA,**0x7FF

<sup>&</sup>lt;sup>2</sup> The symbol '>U' indicates an unsigned greater-than evaluation is performed.

Simplified Mnemonics for Accessing SPRs

4. Trap unconditionally.

trap equivalent to tw 31,0,0

Trap instructions evaluate a trap condition as follows: The contents of  $\mathbf{r}A$  are compared with either the sign-extended SIMM field or the contents of  $\mathbf{r}B$ , depending on the trap instruction.

The comparison results in five conditions that are ANDed with operand TO. If the result is not 0, the trap exception handler is invoked. See Table 27 for these conditions.

Table 27. TO Operand Bit Encoding

| TO Bit | ANDed with Condition                    |  |  |

|--------|-----------------------------------------|--|--|

| 0      | Less than, using signed comparison      |  |  |

| 1      | Greater than, using signed comparison   |  |  |

| 2      | Equal                                   |  |  |

| 3      | Less than, using unsigned comparison    |  |  |

| 4      | Greater than, using unsigned comparison |  |  |

# 8 Simplified Mnemonics for Accessing SPRs

The **mtspr** and **mfspr** instructions specify a special-purpose register (SPR) as a numeric operand. Simplified mnemonics are provided that represent the SPR in the mnemonic rather than requiring it to be coded as a numeric operand. The pattern for **mtspr** and **mfspr** simplified mnemonics is straightforward: replace the **-spr** portion of the mnemonic with the abbreviation for the spr (for example XER, SRR0, or LR), eliminate the SPRN operand, leaving the source or destination GPR operand, **rS** or **rD**.

Following are examples using the SPR simplified mnemonics:

1. Copy the contents of **r**S to the XER.

mtxer rS equivalent to mtspr 1,rS

2. Copy the contents of the LR to **r**S.

mflr rD equivalent to mfspr rD,8

3. Copy the contents of **r**S to the CTR.

mtctr rS equivalent to mtspr 9,rS