# Freescale Semiconductor, Inc.

**Application Note**

AN2475/D 3/2003

Generating a PWM Signal Modulated by an Analog Input Using the MC68HC908QY4 Microcontroller

By: Alfredo Olmos

Andre Vilas Boas

Marcus Serra Espindola

Brazil Semiconductor Technology Center

Jaguariuna, S.P., Brazil

### Introduction

This document addresses the use of the internal timer and analog-to-digital converter (ADC) modules of the MC68HC908QY/QT Family of microcontrollers (MCUs). In the application, an analog signal is converted to a digital word through the ADC to set the duty cycle of a pulse-width modulated (PWM) signal. The PWM duty cycle varies from 0 to 100% in accordance with the voltage applied at the ADC input. Hence, the PWM signal corresponds to the digital conversion of the analog input. The PWM signal is fed back to build a close-loop system for providing voltage regulation in a simple, very flexible way.

# MC68HC908QY/QT Family of Microcontrollers

The MC68HC908QY/QT Family is a member of the low-cost, high-performance M68HC908 Family of 8-bit FLASH MCUs. The M68HC08 Family is a complex instruction set computer (CSIC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

Features of the MC68HC908QY4 include:

- 4 Kbytes of in-application programmable FLASH and 128 bytes of random-access memory (RAM)

- 2-channel 16-bit timer with selectable input capture, output compare, and PWM

- Easy to use high-performance HC08 CPU

- Trimmable internal oscillator with ±5% accuracy

- 4-channel 8-bit ADC

- Selectable trip point low-voltage inhibit (LVI)

- Computer operating properly (COP) timer

- Flexible high-current input/output (I/O) and keyboard interrupts

- 13 bidirectional

- 1 input only

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

- 8-pin dual flat no lead (DFN) package

## Analog-to-Digital Converter (ADC)

The 8-bit, 4-channel ADC module is only available on the MC68HC908QY2, MC68HC908QT2, MC68HC908QY4, and MC68HC908QT4. Features include:

- 4 channels with multiplexed input

- · Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

#### **Voltage Conversion**

When the input voltage to the ADC equals  $V_{DD}$ , the ADC converts the signal to \$FF (full scale). If the input voltage equals  $V_{SS}$ , the ADC converts it to \$00. Input voltages between  $V_{DD}$  and  $V_{SS}$  are a straight-line linear conversion. All other input voltages will result in \$FF if greater than  $V_{DD}$  and \$00 if less than  $V_{SS}$ .

### **Conversion Time**

Sixteen internal clock cycles are required to perform one conversion. The ADC starts a conversion on the first rising edge of the ADC internal clock immediately following a write to the ADC status and control register (ADSCR). If the internal clock is selected to run at 1 MHz, then one conversion will take 16 µs to complete. The highest sample rate at this frequency is 62.5 kHz.

# Continuous Conversion versus Single Conversion

In the continuous conversion mode, the ADC continuously converts the selected channel filling the ADC data register (ADR) with new data after each conversion. Data from the previous conversion will be overwritten whether that

AN2475/D Timer Interface Module (TIM)

data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit (ADSCR, \$003C) is set after each conversion and can be cleared by writing the ADSCR or reading of the ADR.

In the single conversion mode, once the conversion is completed the ADC puts the converted result in the ADR, sets a flag, and can generate an interrupt.

Please refer to the MC68HC908QY4, MC68HC908QT4, MC68HC908QY2, MC68HC908QT2, MC68HC908QY1, and MC68HC908QT1 Data Sheet (Motorola document order number MC68HC908QY4/D) for ADC features and electrical specification details.

# Timer Interface Module (TIM)

The timer interface module (TIM) is a 2-channel timer that provides a timing reference with input capture, output compare, and PWM functions. Software can read the TIM counter value at any time without affecting the counting sequence. The two TIM channels are programmable independently as either input capture or output compare.

#### Features of the TIM include:

- Two input capture/output compare channels:

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered PWM signal generation

- Programmable TIM clock input with 7-frequency internal bus clock prescaler selection

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

# Pulse-Width Modulation (PWM)

By using the toggle-on-overflow feature with an output compare channel, the TIM module can generate a PWM signal. The composed value stored in the TIM counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches that composed value. The time between overflows is the period of the PWM signal.

The composed value of the TIM counter modulo registers and the selected prescaler output determine the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM counter modulo registers produces a PWM period equal to 256 times the internal bus clock period if the prescaler select value is set to 000. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

# Unbuffered PWM Signal Generation

The PWM pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers. An unsynchronized write instruction to the TIM channel registers for changing the pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- 2. When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE:

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

# Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in the TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin (TCH1) is available as general-purpose I/O.

#### **NOTE:**

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently

AN2475/D Application Circuit

active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

Since in this application the PWM duty cycle varies from 0 to 100% in accordance with the voltage applied on the ADC, input buffered PWM allows eliminating potentially harmful glitches when the pulse width setting is changed. This is accomplished without requiring a synchronization method as in unbuffered PWM signal generation.

# **Application Circuit**

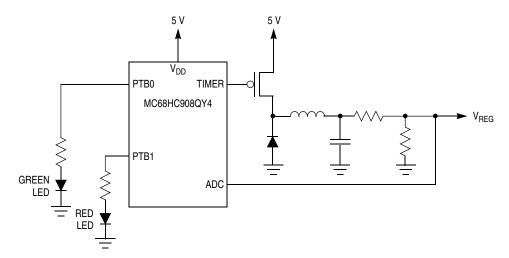

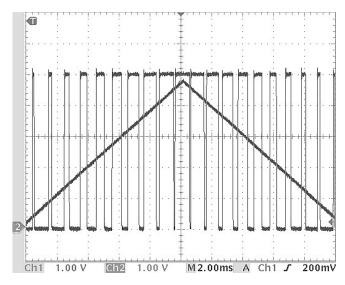

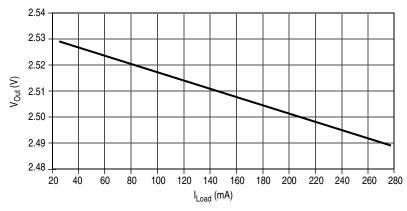

Figure 1 shows a typical application circuit involving the PWM feature. The MC68HC908QY4 outputs a PWM waveform used to control the PMOS switch and, therefore the effective DC regulated voltage applied on the load. The MCU reads the instantaneous regulated output voltage through the ADC and performs a comparison between the digital word obtained and an internal digital reference previously defined. The load voltage is acquired by the ADC through a feedback path cyclically thus, forcing the voltage regulation. If the load demands more current the regulator output voltage decreases. If the voltage input to the ADC is below the pre-set internal reference value the duty cycle is reduced (decremented), thus increasing the driver current of the converter compensating for the reduced voltage supplied to the load. On the other hand, if the load demands less current than the nominal value the MCU grows the duty cycle reducing the output voltage. When regulation is attained the green light emitting diode (LED) is turned on. Conversely, turning on the red LED indicates lack of regulation. Figure 2 illustrates the PWM waveform modulated by an analog voltage signal applied on the ADC input whereas, Figure 3 shows the regulated output voltage versus the load current for the application circuit.

#### NOTE:

It is possible to achieve a regulated voltage of 2.5 V with less than 30 mV variation driving a current load from 20 mA to 280 mA.

Regarding the application circuit in **Figure 1** the diode, inductor, and shunt capacitor create an energy storage reservoir to store enough energy to maintain load voltage during the off-time of the transistor. The transistor serves to replace lost energy during its off-time. Operation of the power switch can be broken down into two periods.

- When the power switch is on, load current passes through the inductor to the load and the diode will be reversed biased.

- When the power switch turns off, current must still pass through the inductor. The current path through the off transistor is now open. The diode will be forward biased, thus maintaining a closed current loop through the load.

Figure 1. Application Circuit

Figure 2. Duty Cycle Modulation versus Analog Input Voltage

Figure 3. Voltage Regulation versus Load Current

AN2475/D Software Description

# **Software Description**

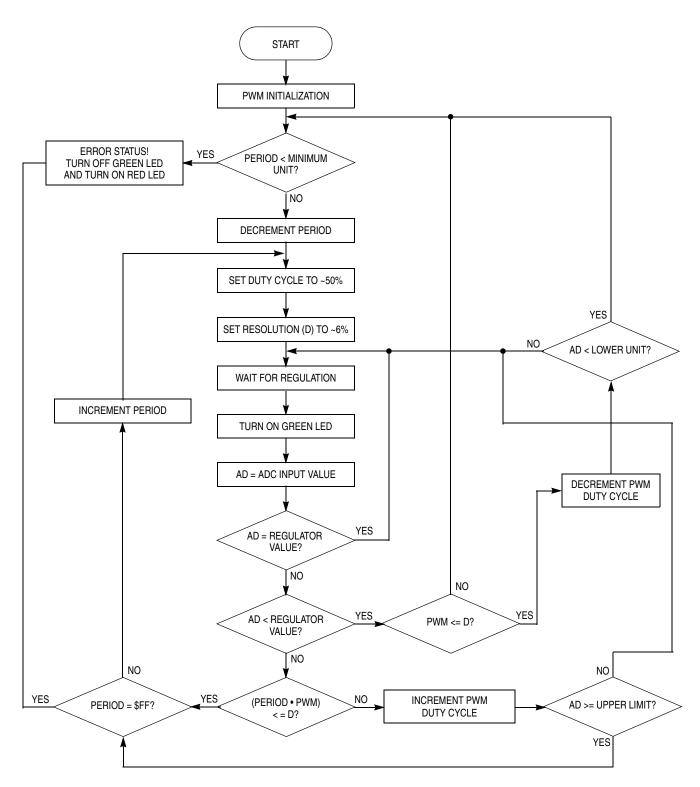

In this application the PWM duty cycle varies from 0 to 100% in accordance with the voltage applied on the ADC input. Actually PWM duty cycle varies from approximately 6% to 94% since it is needed to set a PWM resolution limit for proper operation of the close-loop system. User can redefine the PWM resolution limit as explained below. The PWM output of timer channel 0 is proportional to the analog converted value. When the input voltage increases, the PWM duty cycle increases and vice versa.

The ADC is configured for continuous conversion. The timer module is configured for buffered PWM signal generation. The software runs in a closed loop in which the analog input voltage is converted onto a digital data by the ADC and then compared to a target regulation value previously defined by the user. The system reaches regulation if the analog input reading is in between the upper and lower regulation limits also pre-defined by the user. The driver transistor is a PMOS device. If the ADC value approaches the upper target limit, the PWM duty cycle is increased (incremented). When the regulated output voltage is below the target value but above the lower limit the PWM duty cycle will be decremented. In case of the regulated output voltage being either over the upper limit or below the lower limit, the PWM period will be either enlarged or reduced, respectively. Therefore, the software will be seeking a combination of PWM period and duty cycle to provide a regulated voltage satisfying the pre-defined tolerances. PWM period checking range is from 256 to a minimum determined by the system resolution, as discussed below. A software flowchart is shown in Figure 4.

Every time the period value is changed, the PWM duty cycle is redefined to 50%. In this application a PWM resolution limit is set to approximately 6% (lower) and 94% (upper) of period. If the regulation is not reached varying PWM duty cycle between those limits, period value is altered again. This sequence is performed until regulation is attained.

The PWM resolution limits are obtained by shifting the period value four times to the right. Due to this shifting, the minimum possible period value is attained to guarantee that resolution is 17 (decimal). However, the user can redefine the PWM resolution limit altering the source by code taking into account the trade-off between system resolution and minimum period attainable.

**Figure 4. Software Flowchart**

## **Software Listing**

```

; * Title: LoadRegulation.asm

Copyright (c) Motorola 2002

;* Author: Alfredo Olmos - Motorola SPS/BSTC

Andre V. Boas - Motorola SPS/BSTC

; *

Marcus Espindola - Motorola SPS/BSTC

;* Description: Generating a PWM Signal Modulated by an Analog Input Using HC908QY4 MCU.

;* Documentation: HC908QY4 Data Sheet (MC68HC908QY4/D) for register and bit explanations

;* Include Files: MC68HC908QT4.equ, LoadRegulation.equ

;* Assembler: Metrowerks CodeWarrior - HIWARE HC08-Assembler

;* Revision History: not yet released

;* Rev \# Date Who Comments

;* 0.4 19-Mar-03 Espindola Included OSCTRIM setting;* 0.3 10-Feb-03 Espindola Included Period variation;* 0.2 17-Dec-02 Espindola Cleaned up to match new coding standard

;* 0.1

01-Oct-02 Espindola Initial data entry

;* Motorola reserves the right to make changes without further notice to any product

;* herein to improve reliability, function, or design. Motorola does not assume any

;* liability arising out of the application or use of any product, circuit, or software

;* described herein; neither does it convey any license under its patent rights nor the

;* rights of others. Motorola products are not designed, intended, or authorized for

; * use as components in systems intended for surgical implant into the body, or other

;* applications intended to support life, or for any other application in which the

;* failure of the Motorola product could create a situation where personal injury or

; ^{\star} death may occur. Should Buyer purchase or use Motorola products for any such

;* intended or unauthorized application, Buyer shall indemnify and hold Motorola and

;* its officers, employees, subsidiaries, affiliates, and distributors harmless against

;* all claims, costs, damages, and expenses, and reasonable attorney fees arising out

;* of, directly or indirectly, any claim of personal injury or death associated with

;* such unintended or unauthorized use, even if such claim alleges that Motorola was

; * negligent regarding the design or manufacture of the part.

;* Motorola is a registered trademark of Motorola, Inc.

;* Equates and Data Table Includes

include

"MC68HC908QT4.equ"

; * Constants and Variables for this file

```

include

"LoadRegulation.egu"

```

; * Code Starts Here

****************

org

FlashStart

Init:

#initCfg1,CONFIG1 ;Set config1 register

mov

; (LVI and COP disabled)

IntOsc:

lda

#initCfq2

CONFIG2

; set MCU to internal oscillator

sta

;* Configure oscillator trim value

;Load the factory oscillator trim value

TRIMLOC

lda

sta

OSCTRIM

;into the OSCTRIM register

;* Enable ADCH3 continuous convertion

mov

#initAD, ADSCR

;Start Convertion, CH3 selected

;* Optionally, select ADC ch 1 and 2 by using the instruction below

mov

#$21,adscr

;Start Convertion, CH1 selected

#$22,adscr

;Start Convertion, CH2 selected

mOv.

bclr

PTB0,PTB

; Initial value for PTB0

; Initial value for PTB1

bclr

PTB1, PTB

;PTB0 outputs regulation ok!

bset

DDRB0, DDRB

bset.

DDRB1, DDRB

;PTB1 outputs regulation error!

;* Program Timer Interface Module (TIM)

;* Initializing PWM

#initTim,TSC

; Reset & Stop Counter

mov

mov

#periodH, TMODH

; Set PWM period

mov

#periodL, TMODL

;T = periodL*16 int. bus*(1/bus clk)

#InitpwmH, TCHOH

mov

#InitpwmL, TCHOL

;initial value for output compare (50%)

mov

#tsc0Val,TSC0

; enable buffered PWM in channel 0

mov

#TimVal, TSC

; Disable interruption

mov

;clk = internal bus / 16

#ADclkval, ADICLK

;ADC clock, bus clock/ 16

DecPeriod:

#Permin

lda

cmp

TMODL

; Verify if Period is lower than Minimum Period

bmi

Error

;Go to Error status if so

lda

TMODL

deca

clrh

sta

TMODL

; Decrement period

ldx

#$02

div

tax

PWMLow

;Set PWM Duty Cycle to ~50%

stx

TCHOL

stx

```

|            | bra                             | RegRes                                          |                                                                                                                                                    |

|------------|---------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SetPwmDc:  | bset                            | PTB0,PTB                                        | ;PTB0 = 1, MCU is regulating or trying to do so                                                                                                    |

|            | lda<br>cmp<br>beq<br>bmi        | ADR<br>#RegVal<br>WaitReg<br>DecPwm             | ;Read ADC input value<br>;Compare ADC value with Target Reg. Value<br>;If ADC = RegVal -> wait for regulation<br>;If ADC < RegVal -> decrement PWM |

| IncPwm:    | ldx<br>lda<br>sub<br>cmp<br>bmi | PWMLow<br>TMODL<br>TCHOL<br>PWMLim<br>IncPeriod | ;Verify if PWM reached its resolution limit ;Increment Period if so                                                                                |

|            | incx<br>stx<br>stx              | PWMLow<br>TCH0L                                 | ;Increment PWM value                                                                                                                               |

|            | lda<br>cmp<br>bge               | ADR<br>#RegHLim<br>IncPeriod                    | ;Verify if ADC value is greater than or ;equal to Reg High Limit -> Inc Period if so                                                               |

|            | lda                             | #\$FF                                           |                                                                                                                                                    |

| WaitReg:   | nsa<br>nsa<br>deca<br>bne       | WaitReg                                         | ;Wait ~0.8ms or 2550 cycles to achieve accurate ;load regulation                                                                                   |

|            | bra                             | SetPwmDc                                        |                                                                                                                                                    |

| DecPwm:    | ldx<br>lda<br>cmp<br>bmi        | PWMLow<br>PWMLow<br>PWMLim<br>DecPeriod         | ;Verify if PWM reached its resolution limit ;Decrement Period if so                                                                                |

|            | decx<br>stx<br>stx              | PWMLow<br>TCH0L                                 | ;Decrement PWM value                                                                                                                               |

|            | lda<br>cmp<br>bmi               | ADR<br>#RegLLim<br>DecPeriod                    | ;Verify if ADC value is lower than ;Reg Low Limit -> Decrement Period if so                                                                        |

|            | lda<br>bra                      | #\$FF<br>WaitReg                                |                                                                                                                                                    |

| IncPeriod: | lda<br>cmp<br>beq               | TMODL<br>#\$FF<br>Error                         | ;Verify if Period is at high limit ;Go to Error Status if so                                                                                       |

|            | lda<br>inca                     | TMODL                                           |                                                                                                                                                    |

|            | clrh<br>sta<br>ldx<br>div       | TMODL<br>#\$02                                  | ;Increment period                                                                                                                                  |

|            | tax<br>stx                      | PWMLow                                          | ;Set PWM Duty Cycle to ~ 50%                                                                                                                       |

# AN2475/D

|                                        | stx                                        | TCH0L                         |                                                                                                    |  |  |

|----------------------------------------|--------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| RegRes:                                | lda<br>Lsra<br>lsra<br>lsra<br>lsra<br>sta | TMODL  PWMLim                 | ;Shift 4 times tmodl register value to the right ;in order to adjusted PWM resolution limit (or D) |  |  |

|                                        | Sea                                        |                               | ;to ~6%                                                                                            |  |  |

|                                        | lda<br>bra                                 | #\$FF<br>WaitReg              |                                                                                                    |  |  |

| Error:                                 | bclr<br>bset<br>bra                        | PTB0,PTB<br>PTB1,PTB<br>Error | ;Set ptb1 and clear ptb0 ;if MCU is not regulating                                                 |  |  |

| ;************************************* |                                            |                               |                                                                                                    |  |  |

| Dummy:                                 | rti                                        |                               |                                                                                                    |  |  |

| ;************************************* |                                            |                               |                                                                                                    |  |  |

|                                        | org<br>fdb                                 | \$FFDE<br>Dummy               | ;ADC conversion complete vector                                                                    |  |  |

|                                        | org<br>fdb                                 | \$FFE0<br>Dummy               | ;Keyboard vector                                                                                   |  |  |

|                                        | org<br>fdb                                 | \$FFF2<br>Dummy               | ;TIM overflow vector                                                                               |  |  |

|                                        | org<br>fdb                                 | \$FFF4<br>Dummy               | ;TIM Channel 1 vector                                                                              |  |  |

|                                        | org<br>fdb                                 | \$FFF6<br>Dummy               | ;TIM Channel 0 vector                                                                              |  |  |

|                                        | org<br>fdb                                 | \$FFFA<br>Dummy               | ;IRQ vector                                                                                        |  |  |

|                                        | org<br>fdb                                 | \$FFFC<br>Dummy               | ;SWI vector                                                                                        |  |  |

|                                        | org<br>fdb                                 | \$FFFE<br>Init                | ;Reset vector                                                                                      |  |  |

# Register and Bit Definitions for MC68HC908QY4

```

;* Title: HC908QY4.equ

Copyright (c) Motorola 2002

; * Author: Kazue Kikuchi

;* Description: Register and bit name definitions for MC68HC908QY4 and MC68HC908QT4

;* Documentation: MC68HC908QT4/D Advance Information

;* Include Files: none

; * Assembler: P&E Microcomputer Systems - CASM08Z (v3.16)

;* Revision History:

Who

; * Rev # Date

Comments

; * -----

;* ES 1.0 29-Apr-02

KK Initial release

;* ES 1.1 07-Jun-02 KK

Fixed OSCTRIM address and typos

; *

Motorola reserves the right to make changes without further notice to any product

herein to improve reliability, function, or design. Motorola does not assume any

liability arising out of the application or use of any product, circuit, or software

described herein; neither does it convey any license under its patent rights nor the

rights of others. Motorola products are not designed, intended, or authorized for

use as components in systems intended for surgical implant into the body, or other

applications intended to support life, or for any other application in which the

failure of the Motorola product could create a situation where personal injury or

death may occur. Should Buyer purchase or use Motorola products for any such

intended or unauthorized application, Buyer shall indemnify and hold Motorola and

its officers, employees, subsidiaries, affiliates, and distributors harmless against

all claims, costs, damages, and expenses, and reasonable attorney fees arising out

of, directly or indirectly, any claim of personal injury or death associated with

such unintended or unauthorized use, even if such claim alleges that Motorola was

negligent regarding the design or manufacture of the part.

Motorola and the Motorola logo are registered trademarks of Motorola, Inc.

***********************************

RamStart:

$0080

;Start of RAM

equ

RamLast:

equ

$00FF

;Last RAM location

FlashStart: equ $EE00

;Start of Flash

FlashLast: equ $FDFF

;Last Flash location

Vadc: equ

Vkbd: equ

Vtimov: equ

Vtimch1: equ

;ADC vector

$FFDE

;Keyboard vector

;Timer overflow vector

;Timer channel 1 vector

;Timer channel 0 vector

$FFE0

$FFF2

$FFF4

equ $FFF6

Vtimch0:

equ $FFFA

; IRQ vector

Vira:

equ $FFFC

Vswi:

;SWI vector

Vreset:

equ $FFFE

;Reset vector

```

```

Input/Output (I/O) Ports

; *

PTA:

$00

; Port A data register

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

;Auto wake-up latch data

AWUL

6

equ

PTA5:

5

;Port A data bit 5

eau

PTA4:

;Port A data bit 4

equ

;Port A data bit 3

PTA3:

3

2

PTA2:

;Port A data bit 2

equ

PTA1:

1

; Port A data bit 1

equ

;Port A data bit 0

equ

; bit position masks

mAWUL:

equ

%01000000

;Auto wake-up latch data

mPTA5:

%00100000

;Port A data bit 5

equ

mPTA4:

%00010000

; Port A data bit 4

equ

%00001000

mPTA3:

equ

; Port A data bit

mPTA2:

%0000100

;Port A data bit

equ

; Port A data bit 1

mPTA1:

equ

%0000010

mPTA0:

equ

%0000001

;Port A data bit 0

PTB:

$01

;Port B data register

equ

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

7

;Port B data bit 7

PTB7:

equ

6

; Port B data bit 6

PTB6:

equ

PTB5:

equ

5

;Port B data bit 5

PTB4:

;Port B data bit 4

equ

3

;Port B data bit 3

PTB3:

equ

2

;Port B data bit 2

PTB2:

equ

PTB1:

1

;Port B data bit 1

equ

equ

;Port B data bit 0

; bit position masks

%10000000

;Port B data bit 7

mPTB7:

equ

;Port B data bit 6

mPTB6:

%01000000

equ

;Port B data bit 5

mPTB5:

%00100000

equ

mPTB4:

equ

%00010000

; Port B data bit

mPTB3:

%00001000

; Port B data bit 3

equ

;Port B data bit 2

mPTB2:

equ

%00000100

%0000010

;Port B data bit 1

mPTB1:

equ

mPTB0:

%0000001

;Port B data bit 0

equ

$04

DDRA:

equ

; Port A data direction register

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

;Port A data direction bit 5

5

DDRA5:

equ

DDRA4:

equ

; Port A data direction bit 4

DDRA3:

3

; Port A data direction bit 3

equ

DDRA1:

equ

1

; Port A data direction bit 1

DDRA0:

;Port A data direction bit 0

0

equ

; bit position masks

%00100000

mDDRA5:

equ

;Port A data direction bit 5

mDDRA4:

%00010000

;Port A data direction bit 4

equ

%00001000

; Port A data direction bit 3

mDDRA3:

equ

mDDRA1:

equ

%0000010

; Port A data direction bit 1

mDDRA0:

%0000001

;Port A data direction bit 0

equ

DDRB:

equ

$05

; Port B data direction register

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

7

;Port B data direction bit 7

equ

DDRB6:

equ

6

; Port B data direction bit 6

DDRB5:

5

;Port B data direction bit 5

equ

4

DDRB4:

equ

; Port B data direction bit 4

```

```

DDRB3:

;Port B data direction bit 3

equ

DDRB2:

2

; Port B data direction bit 2

equ

DDRB1:

; Port B data direction bit 1

DDRB0:

0

;Port B data direction bit 0

; bit position masks

equ %10000000 ;Port B data direction bit 7

equ %01000000 ;Port B data direction bit 6

equ %00100000 ;Port B data direction bit 5

equ %00010000 ;Port B data direction bit 4

equ %00001000 ;Port B data direction bit 3

mDDRB7: equ %10000000

mDDRB6:

mDDRB5:

mDDRB4:

mDDRB3:

equ %00000100 ;Port B data direction bit 2 equ %00000100 ;Port B data direction bit 1

mDDRB2:

mDDRB1:

mDDRB0:

equ %0000001

;Port B data direction bit 0

equ $0B

PTAPUE:

; Port A input pullup enable register

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

;OSC2 pin enable

OSC2EN: equ 7

PTAPUE5:

equ

5

;Port A input pull up enable bit 5

4

PTAPUE4:

; Port A input pull up enable bit 4

equ

equ 3

PTAPUE3:

;Port A input pull up enable bit 3

equ 2

PTAPUE2:

;Port A input pull up enable bit 2

equ

PTAPUE1:

;Port A input pull up enable bit 1

equ

0

PTAPUE0:

;Port A input pull up enable bit 0

; bit position masks

mOSC2EN: equ %10000000 ;OSC2 pin enable

mPTAPUE5: equ %00100000 ;Port A input pull up enable bit 5

mPTAPUE4: equ %00010000 ;Port A input pull up enable bit 4

mPTAPUE3: equ %00001000 ;Port A input pull up enable bit 3

mPTAPUE2: equ %00000100 ;Port A input pull up enable bit 2

mPTAPUE1: equ %0000001 ;Port A input pull up enable bit 1

mPTAPUE0: equ %0000001

;Port A input pull up enable bit 0

PTBPUE:

equ $0C

; Port B input pullup enable register

; bit numbers for use in BLCR, BSET, BRCLR, and BRSET

;Port B input pull up enable bit 7

PTBPUE7: equ 7

PTBPUE6:

equ

6

; Port B input pull up enable bit 6

5

PTBPUE5:

equ

; Port B input pull up enable bit 5

equ 5

equ 4

equ 3

PTBPUE4:

; Port B input pull up enable bit 4

; Port B input pull up enable bit 3

PTBPUE3:

PTBPUE2:

equ 2

;Port B input pull up enable bit 2

PTBPUE1:

equ 1

;Port B input pull up enable bit 1

;Port B input pull up enable bit 0

0

PTBPUE0:

equ

; bit position masks

mPTBPUE7: equ %10000000 ;Port B input pull up enable bit 7

mPTBPUE6: equ %01000000 ;Port B input pull up enable bit 6

mPTBPUE5: equ %00100000 ;Port B input pull up enable bit 5

mPTBPUE4: equ %00010000 ;Port B input pull up enable bit 4

mPTBPUE3: equ %00001000 ;Port B input pull up enable bit 3

mPTBPUE2: equ %00001000 ;Port B input pull up enable bit 2

mPTBPUE1: equ

%00000010 ;Port B input pull up enable bit 1

mPTBPUE0: equ

%0000001

;Port B input pull up enable bit 0

; Keyboard status and control register

equ

$1A

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

;Keyboard flag

KEYF: equ

2

ACKK:

equ

; Keyboard acknowledge

IMASKK:

equ 1

; Keyboard interrupt mask

; Keyboard triggering sesitivity

MODEK:

equ

```

```

; bit position masks

mKEYF:

%00001000

; Keyboard flag

equ

mACKK:

; Keyboard acknowledge

mIMASKK:

%00000010

; Keyboard interrupt mask

mMODEK:

equ

%0000001

; Keyboard triggering sesitivity

KBIER:

equ

$1B

; Keyboard interrupt enable register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

equ

AWUIE:

;Auto wake-up interrupt enable

;Port A keyboard interrupt enable bit 5

KBIE5:

equ

;Port A keyboard interrupt enable bit 4

KBIE4:

equ

;Port A keyboard interrupt enable bit 3

KBIE3:

equ

KBIE2:

;Port A keyboard interrupt enable bit 2

equ

1

KBIE1:

equ

; Port A keyboard interrupt enable bit 1

KBIE0:

0

;Port A keyboard interrupt enable bit 0

equ

; bit position masks

;Auto wake-up interrupt enable

%01000000

mAWUIE equ

mKBIE5:

%00100000

;Port A keyboard interrupt enable bit 5

equ

%00010000

;Port A keyboard interrupt enable bit 4

mKBIE4:

equ

;Port A keyboard interrupt enable bit 3

mKBIE3:

equ

%00001000

mKBIE2:

%00000100

;Port A keyboard interrupt enable bit 2

equ

%00000010

;Port A keyboard interrupt enable bit 1

mKBIE1:

equ

mKBIE0:

equ

%0000001

;Port A keyboard interrupt enable bit 0

; *

INTSCR:

$1D

; IRQ status and control register

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

IRQF1: equ 3

;IRQ flag

ACK1:

; IRQ interrupt request acknowledge

2

equ

IMASK1:

eau

;IRQ interrupt mask

MODE1:

equ

; IRQ edge/level select

; bit position masks

mIRQF1: equ %00001000

;IRQ flag

mACK1:

%00000100

; IRQ interrupt request acknowledge

equ

mIMASK1:

equ

%0000010

; IRQ interrupt mask

mMODE1:

equ

%00000001

;IRQ edge/level select

$1E

;Configuration register 2

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

equ 7

IRQPUD:

; IRQ pin pullup control

IRQEN:

equ

6

; IRQ pin function selection

OSCOPT1:

; Selection bit 1 for oscillator option

equ

OSCOPT0:

3

;Selection bit 0 for oscillator option

equ

RSTEN:

equ

0

;RST pin function selection

; bit position masks

;IRQ pin pullup control

mIRQPUD: equ %1000000

%01000000 ;IRQ pin function selection

mIRQEN:

equ

;Selection bit 1 for oscillator option

mOSCOPT1: equ %00010000

mOSCOPT0: equ %00001000

;Selection bit 0 for oscillator option

mRSTEN:

equ

%00000001

;RST pin function selection

$1F

;Configuration register 1

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

;COP reset period selection

COPRS:

equ

;LVI enable in stop mode

LVISTOP:

6

equ

LVIRSTD:

equ

5

;LVI reset disable

LVIPWRD:

4

;LVI power disable

equ

LVI5OR3:

3

equ

;LVI 5V or 3V operating mode

```

```

SSREC:

equ

;Short stop recovery

;STOP instruction enable

STOP:

equ

1

equ

;COP disable

; bit position masks

mCOPRS: equ %1000000

;COP reset period selection

%01000000

mLVISTOP:

;LVI enable in stop mode

equ

;LVI reset disable

mLVIRSTD: equ

%00100000

;LVI power disable

%00010000

mLVIPWRD:

equ

;LVI 5V or 3V operating mode

mLVI5OR3:

equ

%00001000

%00000100

mSSREC:

;Short stop recovery

equ

%00000010

;STOP instruction enable

mSTOP:

equ

%0000001

mCOPD:

;COP disable

equ

; *

TSC:

$20

;Timer status and control register

eau

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

;TIM overflow flag

6

;TIM overflow interrupt enable

TOTE:

equ

TSTOP:

equ

5

;TIM Stop bit

TRST:

;TIM Reset bit

equ

equ 2

;Prescaler select bit 2

PS1:

equ 1

;Prescaler select bit 1

PS0:

equ 0

;Prescaler select bit 0

; bit position masks

;TIM overflow flag

;TIM overflow interrupt enable

;TIM Stop bit

equ %10000000

equ %01000000

mTOF:

mTOIE:

;TIM Stop bit

%00100000

mTSTOP:

equ

equ %00010000

mTRST:

;TIM Reset bit

equ %00000100 ;Prescaler select bit 2

mPS2:

egu %0000010

mPS1:

;Prescaler select bit 1

mPS0:

equ

%0000001

;Prescaler select bit 0

TSC0:

$25

;Timer channel 0 status and control register

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

equ

;Channel 0 flag

CH0IE:

equ

6

;Channel 0 interrupt enable

MS0B:

equ

5

; Mode select bit B

4

MS0A:

;Mode select bit A

equ

ELSOB:

3

;Edge/level select bit B

equ

;Edge/level select bit A

ELSOA:

equ

1

TOV0

eau

;Toggle on overflow

CH0MAX

0

;Channel 0 maximum duty cycle

equ

; bit position masks

equ %10000000 ;Channel 0 flag

equ %01000000 ;Channel 0 interrupt enable

equ %00100000 ;Mode select bit B

equ %00010000 ;Mode select bit A

mCH0F:

mCH0IE:

mMSOB:

mMSOA:

mELSOB:

equ %00001000

;Edge/level select bit B

mELSOA:

equ

%00000100

;Edge/level select bit A

mTOV0

%00000010

;Toggle on overflow

equ

mCH0MAX

%00000001

; Channel O maximum duty cycle

equ

TSC1:

equ

$28

;Timer channel 1 status and control register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

CH1F:

equ

;Channel 1 flag

;Channel 1 interrupt enable

CH1IE:

6

equ

5

;Mode select bit B

MS1B:

equ

MS1A:

equ

4

; Mode select bit A

ELS1B:

3

;Edge/level select bit B

equ

ELS1A:

equ

;Edge/level select bit A

```

```

TOV1

;Toggle on overflow

equ

CH1MAX

; Channel 1 maximum duty cycle

equ

; bit position masks

%10000000

;Channel 1 flag

mCH1IE:

equ

%01000000

;Channel 1 interrupt enable

%00100000

;Mode select bit B

mMS1B:

equ

mMS1A:

%00010000

; Mode select bit A

equ

%00001000

;Edge/level select bit B

mELS1B:

equ

; Edge/level select bit A

mELS1A:

equ

%00000100

%0000010

mTOV1

;Toggle on overflow

equ

%00000001

; Channel 1 maximum duty cycle

mCH1MAX

equ

TCNTH:

$21

;Timer counter register high

TCNTL:

equ

$22

;Timer counter register Low

TMODH:

$23

;Timer counter modulo register high

equ

TMODL:

$24

;Timer counter modulo register low

equ

$26

TCHOH:

equ

;Timer channel 0 register high

TCH0L:

$27

;Timer channel 0 register low

equ

TCH1H:

$29

;Timer channel 1 register high

equ

TCH1L:

equ

$2A

;Timer channel 1 register low

***********

;**** Oscillator Module (OSC)

; *

OSCSTAT:

$36

;Oscillator status register

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

1

;External clock generator on

equ

ECGON:

ECGST:

;External clock status

equ

; bit position masks

mECGON: equ %0000010

;External clock generator on

mECGST:

%0000001

;External clock status

eau

OSCTRIM:

equ

$38

;Oscillator trim register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

TRIM7: equ 7

;Internal oscillator trim factor bit 7

TRIM6:

equ

6

;Internal oscillator trim factor bit 6

TRIM5:

equ

5

;Internal oscillator trim factor bit 5

TRIM4:

4

;Internal oscillator trim factor bit 4

TRIM3:

equ

3

;Internal oscillator trim factor bit 3

2

;Internal oscillator trim factor bit 2

TRIM2:

equ

TRIM1:

;Internal oscillator trim factor bit 1

eau

0

;Internal oscillator trim factor bit 0

TRIM0:

equ

; bit position masks

;Internal oscillator trim factor bit 7

mTRIM7: equ %10000000

;Internal oscillator trim factor bit 6

%01000000

mTRIM6:

equ

equ

;Internal oscillator trim factor bit 5

mTRIM5:

%00100000

mTRIM4:

%00010000

;Internal oscillator trim factor bit 4

equ

mTRIM3:

equ

%00001000

;Internal oscillator trim factor bit 3

mTRIM2:

%00000100

;Internal oscillator trim factor bit 2

equ

mTRIM1:

%00000010

;Internal oscillator trim factor bit 1

equ

mTRIM0:

equ

%00000001

;Internal oscillator trim factor bit 0

TRIMLOC:

equ

$FFC0

;Internal oscillator trim value

;ADC status and control register

$3C

equ

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

coco:

equ

;Conversions complete

6

;ADC interrupt enable bit

AIEN:

equ

5

ADCO:

equ

;ADC continuous conversion

```

## AN2475/D Register and Bit Definitions for MC68HC908QY4

```

CH4:

;ADC channel select bit 4

equ

CH3:

;ADC channel select bit 3

equ

CH2:

;ADC channel select bit 2

1

CH1:

;ADC channel select bit 1

Ω

CHO:

equ

;ADC channel select bit 0

; bit position masks

equ %10000000 ;Conversions complete

equ %01000000 ;ADC interrupt enable bit

equ %00100000 ;ADC continuous conversion

equ %00010000 ;ADC channel select bit 4

equ %00001000 ;ADC channel select bit 3

equ %0000100 ;ADC channel select bit 2

mCOCO:

mAIEN:

mADCO:

mCH4:

mCH3:

mCH2:

mCH1:

equ %00000010 ;ADC channel select bit 1

mCH0:

equ %0000001

;ADC channel select bit 0

ADR:

equ

$3E

;ADC data register

ADICLK:

equ

$3F

;ADC input clock register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

equ 7 ;ADC clock prescaler bit 2

ADIV1:

6

;ADC clock prescaler bit 1

equ

ADIV0:

5

;ADC clock prescaler bit 0

equ

; bit position masks

mADIV2: equ %10000000 ;ADC clock prescaler bit 2

%01000000 ;ADC clock prescaler bit 1 %00100000 ;ADC clock prescaler bit 0

mADIV1:

equ

equ

mADIV0:

; *

BSR:

$FE00

equ

;SIM break status register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

SBSW equ 1

;SIM break stop/wait

; bit position masks

mSBSW: equ %0000010

;SIM break stop/wait

equ

$FE01

;SIM reset status register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

POR:

;Power-on reset

equ

6

PIN:

;External reset

equ

COP:

equ 5

;COP reset

equ 4

; Illegal opcode reset

ILOP:

ILAD:

equ 3

;Illegal address reset

equ 2

MODRST:

; Monitor mode entry module reset

LVI:

equ

1

;LVI reset

; bit position masks

mPOR: equ %10000000 mPIN: equ %01000000

;Power-on reset

;External reset

;COP reset

equ %00100000

mCOP:

equ %00010000

mILOP:

;Illegal opcode reset

%00001000

mILAD:

equ

; Illegal address reset

mMODRST: equ

%00000100

;Monitor mode entry module reset

equ %0000010

;LVI reset

mLVI:

$FE02

BRKAR:

equ

;Break auxiliary register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

BDCOP: equ

0

;Break disable COP

; bit position masks

equ %0000001

;Break disable COP

mBDCOP:

BFCR:

equ

$FE03

;Break flag control register

```

```

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

7

;Break clear flag enable

BCFE: equ

; bit position masks

equ %1000000

;Break clear flag enable

mBCFE:

equ

$FE04

INT1:

;Interrupt status register 1

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

equ

;Interrupt flag 5

IF4:

equ

5

; Interrupt flag 4

;Interrupt flag 3

IF3:

equ

4

IF1:

equ

; Interrupt flag 1

equ $FE05

;Interrupt status register 2

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

IF14: equ

;Interrupt flag 14

$FE06

equ

;Interrupt status register 3

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

;Interrupt flag 15

IF15:

equ

; *

FLCR:

equ

$FE08

;Flash control register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

HVEN: equ 3

;High-voltage enable bit mask

; Mass erase control bit mask

MASS:

eau

2

equ

ERASE:

1

;Erase control bit mask

0

PGM:

;Program control bit mask

equ

; bit position masks

;High-voltage enable bit mask ;Mass erase control bit mask

mHVEN: equ %00001000

%00000100

mMASS:

eau

equ

mERASE:

%0000010

;Erase control bit mask

equ %0000001

mPGM:

;Program control bit mask

FLBPR:

$FFBE

equ

;Flash block protect register

BRKH:

$FE09

equ

;Break address register high

BRKL:

$FE0A

;Break address register low

equ

BRKSCR: equ $FE0B ;Break status and control register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

7

;Break enable

BRKE: equ

BRKA:

equ

6

;Break active

; bit position masks

mBRKE: equ %10000000

;Break enable

%01000000

mBRKA:

;Break active

eau

; *

equ $FE0C

LVISR:

;LVI status register

; bit numbers for use in BCLR, BSET, BRCLR, and BRSET

LVIOUT:

equ

;LVI output bit

; bit position masks

mLVIOUT:

equ

%10000000

;LVI output bit

COPCTL:

$FFFF

;COP control register

equ

```

AN2475/D Constants and variables definitions

#### Constants and variables definitions

```

; * Title: LoadRegulation.equ

Copyright (c) Motorola 2002

; * Author: Alfredo Olmos - Motorola SPS/BSTC

Andre V. Boas - Motorola SPS/BSTC

; *

Marcus Espindola - Motorola SPS/BSTC

;* Description: Constants and variables definitions for MC68HC908QY4 and MC68HC908QT4.

;* Documentation: HC908QY4 Data Sheet (MC68HC908QY4/D) for register and bit explanations

;* Include Files:

;* Assembler: P&E Microcomputer Systems - CASM for HC08

;* Revision History: not yet released

Comments

;* Rev # Date Who

19-Mar-03 Espindola Initial data entry

;* Motorola reserves the right to make changes without further notice to any product

;* herein to improve reliability, function, or design. Motorola does not assume any

; ^\star liability arising out of the application or use of any product, circuit, or software

; ^{\star} described herein; neither does it convey any license under its patent rights nor the

;* rights of others. Motorola products are not designed, intended, or authorized for

; * use as components in systems intended for surgical implant into the body, or other

; ^{\star} applications intended to support life, or for any other application in which the

;* failure of the Motorola product could create a situation where personal injury or

;* death may occur. Should Buyer purchase or use Motorola products for any such

;* intended or unauthorized application, Buyer shall indemnify and hold Motorola and

;* its officers, employees, subsidiaries, affiliates, and distributors harmless against

;* all claims, costs, damages, and expenses, and reasonable attorney fees arising out

;* of, directly or indirectly, any claim of personal injury or death associated with

;* such unintended or unauthorized use, even if such claim alleges that Motorola was

;* negligent regarding the design or manufacture of the part.

; * Motorola is a registered trademark of Motorola, Inc.

;* Constants and Variables for this file

**********************************

org

RamStart

initCfg1: equ

;initCfg1: equ %00010001

;Config1 Register value

|||||| CONFIG1 is a write once register

||||||+-COPD - 1 disable COP Watchdog

|||||+--STOP

- 0 disable STOP instruction

|||||+---SSREC - 0 4096 cycle STOP recovery

||||+---LVI5OR3 - 0 set LVI for 3V system

|||+----LVIPWRD - 1 disable power to LVI system

||+----LVIRSTD - 0 enable reset on LVI trip

|+-----LVISTOP - 0 disable LVI in STOP mode

+-----COPRS - 0 long COP timeout

```

```

initCfg2: equ

%0000000

;Config2 Register value

CONFIG2 is a write once register

||||||+-RSTEN

- 0 Reset function inactive in pin

|||||+--R

- 0 Reserved bit

||||+---R

- 0 Reserved bit

| \ | \ | \ | \ | +---OSCOPT0 - 0 Set oscillator option as internal

|||+----OSCOPT1 - 0 Set oscillator option as internal

| | +---R

- 0 Reserved bit

|+----IRQEN - 0 disable IRQ function

+----IRQPUD - 0 Internal pullup conecte IRQ and VDD

initAD: equ

%00100011

;AD configuration value

ADC Status and Control Register

||||+-CHO

- 1 Mux to select ADC channel

;

|||||+--CH1

- 1 Mux to select ADC channel

||||+---CH2

- 0 Mux to select ADC channel

|||+----CH3

- 0 Mux to select ADC channel

|||+----CH4

- 0 Channel 3 selected

| | +----ADCO

- 1 Set ADC as continuous conversion

|+----AIEN - 0 disable ADC interrupt

+----COCO

- 0 Conversions Complete Bit

initTim: equ

%00110000

;Timer Status and control Reg. value

TIM Status and Control Register

|||||+-PS0

- 0 Prescaler select bit

- 0 Prescaler select bit

||||+--PS1

||||+---PS2

- 0 Tim clock source int. bus / 8

| | | | +---0

- 0

|||+---TRST

- 1 TIM reset bit

||+----TSTOP - 1 TIM counter stopped

|+----TOIE

- 0 disable TIM overflow interrupts

+----TOF

- 0 TIM overflow flag bit

periodH: equ

80000000

;TIM Counter Modulo Registers

;Set period high register value

periodL: equ

%11111111

; Initial Period value

;Set period to 256

InitpwmH: equ

%00000000

; Initial PWM duty cycle value

%10000000

InitpwmL: equ

;Set PWM duty cycle to 50%

ADclkval: equ

%10000000

;AD clock configuration

;ADC Clock prescaler bit

tsc0Val: equ

%00101010

;TSC0 Initial Value

TIM Channel Status and Control Register

||||||+-CHOMAX - O Channel O Maximum Duty Cycle bit

||||||+--TOV0

- 1 Channel 0 toggle on overflow

||||+---ELSOA

- 0 I

||||+---ELSOB

- 1

|||+----MSOA

- 0 |

| |+----MS0B

- 1 |-> Config TIM as buffered PWM

|+----CH0IE - 0 disable Channel 0 CPU interrupt

+----CH0F

- 0 No input capture or output compare

```

```

TimVal: equ

%00000100

;Timer Register configuration value

TIM Status and Control Register

|||||+-PSO

- 0 Prescaler select bit

|||||+--PS1

- 0 Prescaler select bit

||||+---PS2

- 1 Tim clock source int. bus / 16

| | | | +---0

- 0

|||+---TRST

- 0 TIM reset bit

| |+----TSTOP

- 0 TIM counter active

|+----TOIE

- 0 disable TIM overflow interrupts

+----TOF

- 0 TIM overflow flag bit

RegHLim: equ

%10000101

;Upper Limit Period value set

;by user

RegLLim: equ

%01111011

;Lower Limit Period value set

;by user

RegVal: equ

%10000000

; Target Reg. Value set by user

Permin: equ

%00010001

; Minimum Period Value set by user

; PWM Duty Cycle resolution limit (or D)

PWMLim: rmb

PWMLow: rmb

; PWM Duty Cycle

```

### Conclusion

In this application a PWM modulator is implemented using the MC68HC908QY4 microcontroller. Typical PWM applications include motor speed control, battery chargers, and switching voltage regulators, all of them easily implemented using the 68HC08-based MCU's. This low-cost, low pin count family of microcontrollers brings to designers flexibility in the system development process helping to reduce overall system costs and speed up time-to-market. In addition, a variety of features and benefits make MC68HC908QYx microcontrollers versatile for a wide range of systems like home applications, computer peripherals, and automotive electronics.

# Freescale Semiconductor, Inc.

# AN2475/D

#### **HOW TO REACH US:**

#### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu Minato-ku, Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

#### **TECHNICAL INFORMATION CENTER:**

1-800-521-6274

HOME PAGE:

http://motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. digital dna is a trademark of Motorola, Inc. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2003