# Freescale Semiconductor Application Note

AN2405/D Rev. 1.1, 11/2004

# i.MX Supplemental Information for LCD Interfacing

MC9328MX1 & MC9328MXL

This application note provides supplementary information to the MC9328MX1 and MC9328MXL (i.MX) Integrated Portable System Processor Reference Manuals (order numbers: MC9328MX1RM/D and MC9328MXL/D), LCD Controller chapters:

- Features and supported panel types

- LCD pins and signals

- LCD interface clock settings

- Timings

- Interfacing to Sharp TFT panels

- Other considerations

For the latest errata and addenda to the i.MX reference manual please reference the web site: www.freescale.com/semiconductors.

# 1 Features and Supported Panels

Table 1 on page 2 summarizes the panels supported by the i.MX processor with the ARM® core based system.

## Contents

| Features and Supported Panels 1 |

|---------------------------------|

| LCDC Pins and Signals 2         |

| LCD Interface Clock Settings 3  |

| Timing 5                        |

| Interfacing to Sharp TFT Panels |

| Other Considerations            |

| Revision History 18             |

|                                 |

© Freescale Semiconductor, Inc., 2004. All rights reserved.

## **LCDC Pins and Signals**

| Panel Type     | BPP | Panel<br>Interface<br>(bits) | Number of Levels        | Max. Panel<br>Size<br>(pixels)            | Palette Ram Usage                                                                                                                                                                                             |

|----------------|-----|------------------------------|-------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mono<br>chrome | 1   | 1,2,4,8                      | 2 level black and white | 640 x 480*<br>640 x 480**                 | 1. Palette RAM is not used.                                                                                                                                                                                   |

|                | 2   | 1,2,4,8                      | 4 gray scale levels     | 640 x 480*<br>640 x 480**                 | <ol> <li>Palette RAM is not used.</li> <li>Black is one shade, white is one shade, two<br/>remaining shades are programmable in LGPMR<br/>LCD Gray Palette Mapping Register.</li> </ol>                       |

|                | 4   | 1,2,4,8                      | 16 gray scale levels    | 640 x 480*<br>320 x 240 or<br>240 x 320** | <ol> <li>Palette RAM is used.</li> <li>16 four-bit values are programmed into the first 16<br/>entries of the palette RAM.</li> </ol>                                                                         |

| CSTN           | 4   | 8                            | 16 color levels         | 320 x 240 or<br>240 x 320**               | <ol> <li>Palette RAM is used.</li> <li>16 colors can be selected out of a palette of 4096 different colors.</li> <li>16 twelve-bit values are programmed into first 16 entries of the palette RAM.</li> </ol> |

|                | 8   | 8                            | 256 color levels        | 320 x 240 or<br>240 x 320**               | <ol> <li>Palette RAM is used.</li> <li>256 colors can be selected out of a palette of<br/>4096 different colors.</li> <li>256 twelve-bit values are programmed into the<br/>palette RAM.</li> </ol>           |

|                | 12  | 8                            | 4096 color levels       | 320 x 240 or<br>240 x 320**               | 1. Palette RAM is not used.                                                                                                                                                                                   |

| TFT            | 4   | 12                           | 16 color levels         | 640 x 480*<br>320 x 240 or<br>240 x 320** | <ol> <li>Palette RAM is used.</li> <li>16 colors can be selected out of a palette of 4096 different colors.</li> <li>16 twelve-bit values are programmed into first 16 entries of the palette RAM.</li> </ol> |

|                | 8   | 12                           | 256 color levels        | 640 x 480*<br>320 x 240 or<br>240 x 320** | <ol> <li>Palette RAM is used.</li> <li>256 colors can be selected out of a palette of<br/>4096 different colors.</li> <li>256 twelve-bit values are programmed into the<br/>palette RAM.</li> </ol>           |

|                | 12  | 12                           | 4096 color levels       | 640 x 480*<br>240 x 160 or<br>160 x 240** | 1. Palette RAM is not used.                                                                                                                                                                                   |

|                | 16  | 16                           | 65,536 color levels     | 640 x 480*<br>240 x 160 or<br>160 x 240** | 1. Palette RAM is not used.                                                                                                                                                                                   |

## Table 1. i.MX Processor Panel Support

# 2 LCDC Pins and Signals

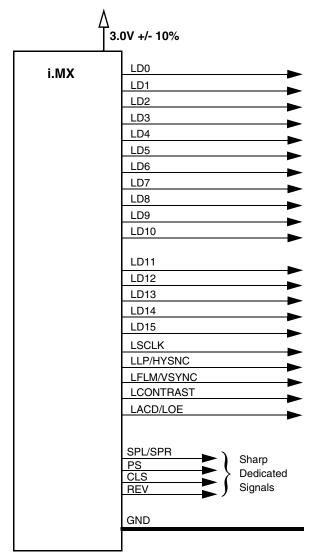

The i.MX interface pins for the LCDC are  $3.0V \pm 10\%$  capable. Refer to the i.MX reference manual and your panel's specifications regarding electrical compatibility with the i.MX processor's interface pins. The Figure 1 shows the i.MX processor's LCD pins and signal name assignments.

Figure 1. LCDC Pins and Signals

# 3 LCD Interface Clock Settings

The frequency setting of the interface clock, LSCLK, is determined by the panel specifications. To avoid flicker on the screen set LSCLK to be within the panel specifications. Use an oscilloscope to probe LSCLK to ensure that the clock frequency is set correctly. If flicker problems occur, visually inspect the interface clock by probing even when the clock settings have been programmed correctly.

LCD Interface Clock Settings

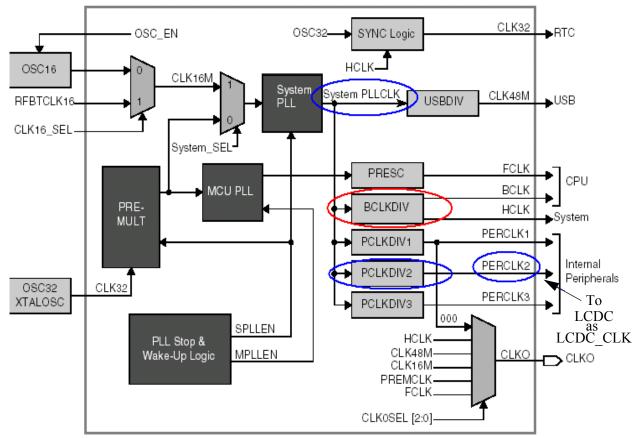

Figure 2. i.MX Clock Controller Module

Figure 2 shows that the LCD controller's clock input is PERCLK2. PERCLK2, with respect to the LCDC, is known as LCDC\_CLK. Therefore, LCDC\_CLK and HCLK are derived from the same clock source, the output of the System PLL (System PLLCLK).

## WARNING:

HCLK and LCDC\_CLK must follow the following relationship for the LCDC to work properly:

LCDC\_CLK = PERCLK2 = (System PLLCLK) / (PCLKDIV2)

HCLK = (System PLLCLK) / (BCLKDIV)

However, when BCLKDIV = 1 (for example  $BCLK_DIV$  setting = 0x0) then HCLK = (System PLLCLK). In this case the divider PCLKDIV2 can be any value.

Also, when BCLK\_DIV = 2 (for example BCLK\_DIV setting = 0x1) then HCLK = (System PLLCLK) / 2. In this case, the divider PCLK\_DIV2 must be 3, 7, or 15 and so on.

This method ensures the rising clock edge of LCDC\_CLK is synchronized with the rising edge of HCLK, otherwise timing problems occur. Consequently, the output of the LCDC is unpredictable.

Please refer to the i.MX reference manual for PCLKDIV2 and BCLKDIV divider settings and programming.

# 4 Timing

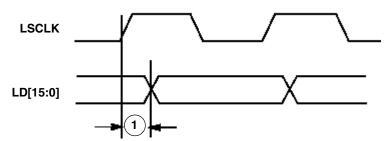

The LCDC supports both non-TFT passive matrix panels as well as TFT active matrix panels. Timing for both panel types are discussed in this section. Figure 3 and Table 1 depict the LSCLK-to-display data (LD) relationship.

Figure 3. LSCLK to LD Timing Diagram

| Table 2. | LSCLK to I | LD Timing | Parameters |

|----------|------------|-----------|------------|

|----------|------------|-----------|------------|

| Number | ber Characteristic 3.0 V +/- 10% |         | - 10%   | Unit |

|--------|----------------------------------|---------|---------|------|

| Number | Characteristic                   | Minimum | Maximum | Unit |

| 1      | SCLK to LD valid                 | _       | 3       | ns   |

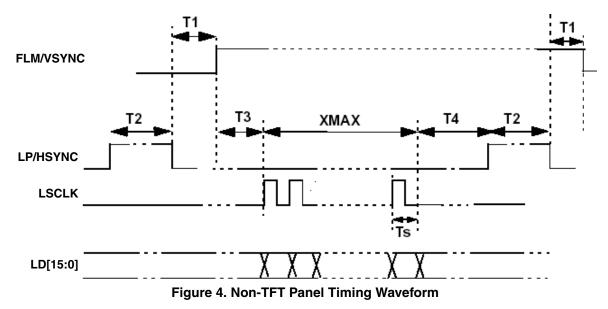

# 4.1 Non-TFT Panel Timing (Passive Matrix)

The LCDC supports non-TFT panel interfaces for passive matrix LCD panels.

### Timing

| Symbol                                                                                                                                                                                                                                                          | Parameter            | Allowed Register<br>Minimum Value | Actual Value | Unit |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|--------------|------|--|

| T1                                                                                                                                                                                                                                                              | HSYNC to VSYNC delay | 0                                 | HWAIT2+2     | Тріх |  |

| T2                                                                                                                                                                                                                                                              | HSYNC pulse width    | 0                                 | HWIDTH+1     | Тріх |  |

| T3                                                                                                                                                                                                                                                              | VSYNC to SCLK        | _                                 | 0≤T3≤Ts      |      |  |

| T4                                                                                                                                                                                                                                                              | SCLK to HSYN         | 0                                 | HWAIT1+1     | Тріх |  |

| <ul> <li>VSYNC, HSYNC, and LSCLK can be programmed as active high or active low. In the timing diagram above, all 3 signals are active high.</li> <li>Ts is the shift clock period.</li> <li>Ts = Tpix * (panel data bus width).</li> </ul>                     |                      |                                   |              |      |  |

| • Tpix is the Pixel Clock Period (LSCLK) which equals $\frac{1}{8 \times (PCD+1)} \times LCDC\_CLK$ .                                                                                                                                                           |                      |                                   |              |      |  |

| <ul> <li>To calculate the maximum frequency required for the LSCLK to operate on a passive LCD panel so that the LD output is correct, use the following formulas:</li> <li>LSCLK (12 bpp) &lt; 1/9 HCLK</li> <li>LSCLK (8 bpp/4 bpp) &lt; 1/15 HCLK</li> </ul> |                      |                                   |              |      |  |

Table 3. Non-TFT Panel Timing

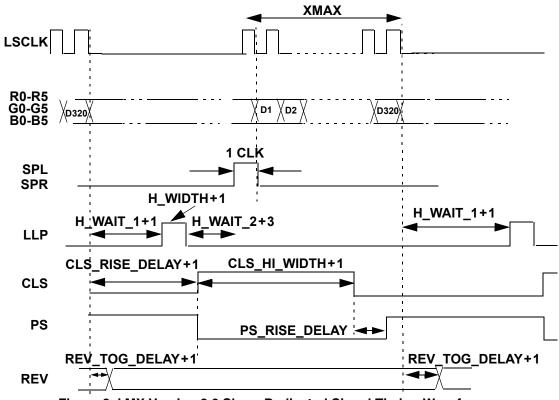

# 4.2 TFT Panel Timing

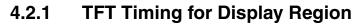

The LCDC supports TFT panel interfaces for active matrix LCD panels. The i.MX processor supports two types of TFT panels: the Sharp TFT panels that require the special timing signals SPL/SPR, CLS, PS, and REV and standard TFT interface panels. This sections discusses the latter type of panels.

Figure 5. TFT Panel Timing Waveform for Display Region

| Symbol | Parameter                                                  | Allowed Register<br>Minimum Value | Actual Value     | Unit |

|--------|------------------------------------------------------------|-----------------------------------|------------------|------|

| T1     | Idle HSYNC period between last line and beginning of VSYNC | 0                                 | VWAIT1           | T2   |

| T2     | HSYNC period                                               | -                                 | XMAX+T5+T6+T7+T8 | Ts   |

| Т3     | VSYNC pulse width                                          | 1                                 | VWIDTH           | T2   |

| T4     | Idle HSYNC period between End of<br>VSYNC to first line    | 0                                 | VWAIT2           | T2   |

| T5     | HSYNC pulse width                                          | 0                                 | HWIDTH+1         | Ts   |

| Т6     | End of HSYNC to T8                                         | 0                                 | HWAIT2+1         | Ts   |

| T7     | End of OE to beginning of HSYNC                            | 0                                 | HWAIT1+1         | Ts   |

| Т8     | Dummy idle state (Sharp = 0)                               | _                                 | 2                | Ts   |

Table 4. TFT Panel Timing for Display Region

### Timing

Table 4. TFT Panel Timing for Display Region (continued)

| Symbol                                                     | Parameter                                                                                                                                                                                                                                                                                                              | Allowed Register<br>Minimum Value | Actual Value | Unit |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------|------|

| Т8                                                         | Dummy idle state (Sharp = 1)                                                                                                                                                                                                                                                                                           | -                                 | 3            | Ts   |

| signals a<br>The pola<br>By defau<br>If registe<br>dummy s | HSYNC and LOE can be programmed as active high<br>are active low.<br>Inity of LSCLK and LD[15:0] can also be programmed.<br>It, LSCLK is idle when LOE is non-active.<br>It sclk_idle equals 1, LSCLK is active when LOE is<br>state, for example T5, T6, T7, and T8.<br>It sclk_sel equals 1, LSCLK is always active. |                                   |              |      |

• XMAX is defined in unit of pixel.

• Formula for period of VSYNC = T2 \* YMAX + T1+T3+T4

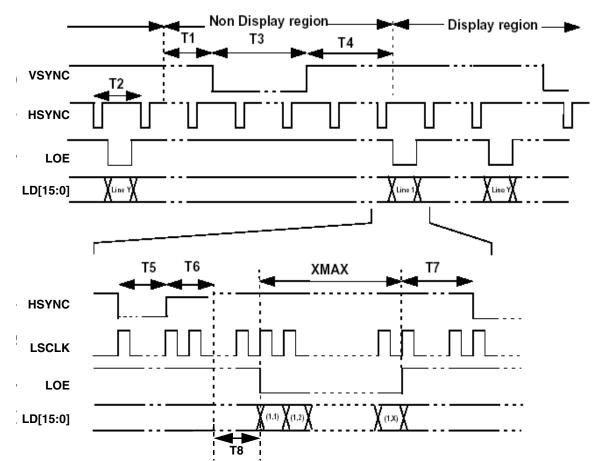

# 4.2.2 TFT Timing for Non-Display Region

Within the non-display period, the position of VSYNC relative to the HSYNC is the same in each HSYNC period. This applies for both positive and negative going edge of VSYNC.

# 5 Interfacing to Sharp TFT Panels

The i.MX processor's LCDC can directly interface with Sharp HR-TFT panels that require Sharp dedicated signals. Figure 7 shows how to connect the LCDC interface signals to a 18 bpp TFT panel. The two LSBs of the blue (B0) and red (R0) component are tied to B1 and R1, respectively. The diagram shows a panel that does not require Sharp dedicated signals, therefore, they are shown not connected (nc).

#### 3.0V i.MX 18 bpp TFT Panel B0 Not Requiring LD0 B0 B1 Sharp Dedicated LD1 B1 B2 Signals LD2 B2 В3 LD3 B3 B4 LD4 B4 B5 LD5 G0 G0 LD6 G1 G1 LD7 G2 G2 LD8 G3 G3 LD9 G4 G4 LD10 G5 G5 R0 LD11 R1 R0 LD12 R2 R1 LD13 R3 R2 LD14 R4 R3 LD15 R5 R4 LSCLK SCLK СК LP/HSYNC HSYNC Hsync FLM/VSYNC VSYNC Vsync LCONTRAST nc LACD/LOE ENAB SPL/SPR nc Sharp PS nc Dedicated CLS nc Signals REV nc VSS GND GND

# 5.1 Connections and Signals

Figure 7. TFT Panel Interface Not Requiring Sharp Dedicated Signals

If the panel illustrated in Figure 7 required Sharp dedicated signals—that is, it was a Sharp panel and the timing ASIC for the dedicated signals was not provided—the i.MX processor could be used to directly drive the panel by making direct connections to those signals. The four signals dedicated to Sharp panels are identified in Table 5 on page 10.

### Interfacing to Sharp TFT Panels

| Signal Name      | Description                  |

|------------------|------------------------------|

| SPL/SPR          | Sampling Start Signal        |

| CLS <sup>1</sup> | Clock Signal for Gate Driver |

| PS               | Power Save Signal            |

| REV <sup>1</sup> | Reverse Control              |

## **Table 5. Sharp Dedicated Signals**

<sup>1</sup>Both the rising and falling edge of CLS and transition edge of REV are programmable.

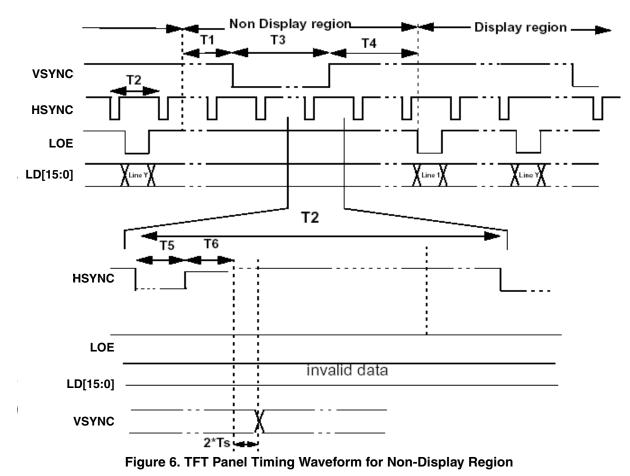

# 5.2 Sharp Dedicated Signal Timing

Figure 8. i.MX Version 2.0 Sharp Dedicated Signal Timing Waveform

Additional information regarding Figure 8 follows:

- Falling edge of PS aligns with rising edge of CLS.

- Delay of rising edge of PS is programmed by PS\_RISE\_DELAY.

- SPL/SPR pulse width is fixed and aligned to the first data of the line.

- REV toggles every LLP period.

- CLS\_HI\_WIDTH is programmable, PWMR [24:16].

# 6.1 LCDC DMA Setting

For SDRAM access, a fixed burst length of 8 is preferred.

## Table 6. Fixed Burst Length Settings

| Item               | DMA Register Setting |

|--------------------|----------------------|

| Fixed burst length | 1                    |

| High mark          | 8                    |

| Low mark           | 4                    |

For a heavily loaded bus and SDRAM access, a dynamic burst length is recommended.

| Item               | DMA Register Setting |

|--------------------|----------------------|

| Fixed burst length | 0                    |

| High mark          | 3                    |

| Low mark           | 8                    |

## Table 7. Dynamic Burst Length Settings

# 6.2 Bandwidth and Detection of LCDC Under-Run

The LCDC output data rate is determined by:

- bit per pixel

- panel size

**Refresh Rate**—The refresh rate is determined by the panel specification. For a TFT panel typical refresh rates are around 60 frames/sec.

For example:

- $240 \times 320$  TFT panel 16 bpp color

- refresh rate at 60 Frame/sec.

The required data output rate:

$240 \times 320 \times 16 \times 60 = 73$  M bit/sec (approximately)

If HCLK (DMA CLOCK) is running at 96 MHz, then the maximum data rate is:

$32 \times 96$  M = 3072 M bit /sec.

Therefore, the theoretic bandwidth used by the LCDC = 73 / 3072 = 0.023

In a customer's application data under-run may occur due to heavy bus loading as well as a priority issue with the memory controller. To detect a data under-run event, the user can perform the following:

- Read the Under-Run bit in the LCDC status register to see if it is set.

- Monitor the period of HSYNC/VSYNC to see if it is changing intermittently.

When an Under-Run occurs, the data output will be incorrect. When normal data service—that is, no more Under-Run, is restored the LCDC outputs data correctly. However, the LCD panel is a sequential device with no error checking protocol. Even though the LCDC returns to correct operation, the LCD panel will return to normal operation only after a VSYNC signal. This is to fully synchronize the data between LCDC and the LCD panel. Under-run errors will be more prone to occur on higher resolution panels such as VGA (640x480). Tests on the overall system must take place to make sure the usage of system bus does not trigger under-run errors.

# 6.3 Example Initializations

### Code Example 1. Sharp TFT VGA Panel Not Requiring Dedicated Signals

comment ### Select CLKO mux to output HCLK(BCLK) ### setmem 0x21B000 0x2F00AC03, 32 comment ### Change BCLK (CPUCLK) to 16MHz comment setmem 0x21B000 0x2F009403, 32 comment ### Change BCLK (CPUCLK) to 24MHz comment setmem 0x21B000 0x2F008C03, 32 comment ### Change BCLK (CPUCLK) to 32MHz comment setmem 0x21B000 0x2F008803, 32 comment ### Change BCLK (CPUCLK) to 48MHz comment setmem 0x21B000 0x2F008403, 32 comment ### Change BCLK (CPUCLK) to 96MHz setmem 0x21B000 0x2F008003, 32 comment ### Change PerCLK2 (LCDCLK) to 96MHz comment setmem 0x21B020 0x000B000B, 32 comment ### Change PerCLK2 (LCDCLK) to 48MHz setmem 0x21B020 0x000B001B, 32 comment ### Change PerCLK2 (LCDCLK) to 32MHz comment setmem 0x21B020 0x000B002B, 32 comment ### Change PerCLK2 (LCDCLK) to 16MHz comment setmem 0x21B020 0x000B005B, 32 comment ### Change PerCLK2 (LCDCLK) to 8MHz comment setmem 0x21B020 0x000B00BB, 32 comment ### CSO - boot flash, 32 wait states, 8-bit ### setmem 0x220000 0x00002000, 32 setmem 0x220004 0x11110301, 32 comment ### CS1 - SRAM, wait states, 32-bit ### setmem 0x220008 0x00000300, 32 setmem 0x22000C 0x11110601, 32 comment ### CS4 - External UART, 10 wait states, 8-bit ### setmem 0x220020 0x00000A00, 32 setmem 0x220024 0x11110301, 32 INIT FILE FOR SHARP 640X480 LCD DISPLAY comment comment LCD buffer point to external SRAM setmem 0x00205000 0x12000000, 32 comment LCD buffer point to eSRAM comment setmem 0x00205000 0x00300000, 32 comment set LCD display size 640x480 setmem 0x00205004 0x028001E0, 32

comment vpwC480(dec) for 8bpp 40 for 4bpp comment set vpw to  $640/2=320 \Rightarrow 0x140$ setmem 0x00205008 0x00000140, 32 comment set cursor position & attributes setmem 0x0020500C 0x40010001, 32 setmem 0x00205010 0x1F1F0000, 32 setmem 0x00205014 0x0000F800, 32 comment 16 bpp , tft , color, div by 2 setmem 0x00205018 0xF8E00081, 32 comment h width, h wait1, h wait2 setmem 0x0020501C 0x04001066, 32 comment v width, v wait1, v wait2 setmem 0x00205020 0x04000022, 32 comment panning offset setmem 0x00205034 0x0000000, 32 comment. IO PORT INIT FOR LCD config PC16 to output port for LCD ON comment config PD to functional use for LCD signals comment comment PORT D GIUS comment clear PORT D for LCD signal setmem 0x0021C320 0x0000000, 32 comment PORT D GPR setmem 0x0021C338 0x0000000, 32 comment PORT C GIUS setmem 0x0021C220 0x00010000, 32 comment PORT C OCR2 setmem 0x0021C208 0x0000003, 32 comment PORT C DDIR setmem 0x0021C200 0x00010000, 32 comment PORT C GPR setmem 0x0021C238 0x00010000, 32 comment PORT C DR (data register) comment set PC16 will turn off LCD setmem 0x0021C21C 0x00010000, 32 comment LCD ON comment PORT C DR (data register) comment set PC16 will turn off LCD setmem 0x0021C21C 0x00010000, 32 comment LCD enabled setmem 0x00205034 0x0F000002, 32

# NOTE:

Code Example 2 provides a way to configure the internal clocks of the i.MX chip, however depending on the application and system requirements the clocks could be different.

Code Example 2. Sharp 320x480 TFT Requiring Dedicated Signals comment ### Select CLKO mux to output HCLK(BCLK) ### setmem 0x21B000 0x2F00AC03, 32 comment ### Change BCLK (CPUCLK) to 16MHz comment setmem 0x21B000 0x2F009403, 32 comment ### Change BCLK (CPUCLK) to 24MHz comment setmem 0x21B000 0x2F008C03, 32 comment ### Change BCLK (CPUCLK) to 32MHz comment setmem 0x21B000 0x2F008803, 32 comment ### Change BCLK (CPUCLK) to 48MHz comment setmem 0x21B000 0x2F008403, 32 comment ### Change BCLK (CPUCLK) to 96MHz setmem 0x21B000 0x2F008003, 32 comment ### Change PerCLK2 (LCDCLK) to 96MHz comment setmem 0x21B020 0x000B000B, 32 comment ### Change PerCLK2 (LCDCLK) to 48MHz comment setmem 0x21B020 0x000B001B, 32 comment ### Change PerCLK2 (LCDCLK) to 32MHz setmem 0x21B020 0x000B002B, 32 comment ### Change PerCLK2 (LCDCLK) to 16MHz comment setmem 0x21B020 0x000B005B, 32 comment ### Change PerCLK2 (LCDCLK) to 8MHz comment setmem 0x21B020 0x000B00BB, 32 comment ### CSO - boot flash, 32 wait states, 8-bit ### setmem 0x220000 0x00002000, 32 setmem 0x220004 0x11110301, 32 comment ### CS1 - SRAM, 10 wait states, 32-bit ### setmem 0x220008 0x00000A00, 32 setmem 0x22000C 0x11110601, 32 comment ### CS4 - External UART, 10 wait states, 8-bit ### setmem 0x220020 0x00000A00, 32 setmem 0x220024 0x11110301, 32 INIT FILE FOR SHARP 320X480 LCD DISPLAY comment comment LCD buffer point to external SRAM setmem 0x00205000 0x12000000, 32 comment LCD buffer point to eSRAM comment setmem 0x00205000 0x00300000, 32 comment set XMAX to 336 (0x150), YMAX to 480 (0x1E0) setmem 0x00205004 0x015001E0, 32 comment vpw=336/32=168 (0xA8) word where word = 32 bit and 16bpp setmem 0x00205008 0x000000A8, 32 setmem 0x0020500C 0x40050001, 32 setmem 0x00205010 0x1F1F0000, 32

setmem 0x00205014 0x0000f800, 32 comment 16 bp , tft ,color, pos edge clock pol, LLP active high, LFLM active low setmem 0x00205018 0xF8040042, 32 comment Sharp Configuration 1 Register setmem 0x00205028 0x00090300, 32 comment hsyn width = 2 CLK hsyn wait 1 = 8 CLK (0x7) hsyn wait2 = 4 CLK (0x1)setmem 0x0020501C 0x4000701, 32 comment vsyn width = 2 lines vsyn\_wait 1 = 7 lines (0x7) vsyn\_wait2 = 6 lines (0x6)setmem 0x00205020 0x08000706, 32 comment setmem 0x00205034 0x0000000, 32 IO PORT INIT FOR LCD comment config PC16 to output port for LCD ON comment. config PD to functional use for LCD signals comment. comment PORT D GIUS comment clear PORT D for LCD signal setmem 0x0021C320 0x0000000, 32 comment PORT D GPR setmem 0x0021C338 0x0000000, 32 comment PORT C GIUS setmem 0x0021C220 0x00010000, 32 comment PORT C OCR2 setmem 0x0021C208 0x0000003, 32 comment PORT C DDIR setmem 0x0021C200 0x00010000, 32 comment PORT C GPR setmem 0x0021C238 0x00010000, 32 comment PORT C DR (data register) comment set PC16 will turn off LCD setmem 0x0021C21C 0x00010000, 32 comment LCD ON comment PORT C DR (data register) comment set PC16 will turn off LCD setmem 0x0021C21C 0x00010000, 32 comment set SPL/SPR to CLS delay 316 clk (256 + 0x21) setmem 0x0020502C 0x00A9033C, 32 comment Enable the LCD display setmem 0x00205034 0x0F000002, 32

# 6.4 Testing the Display

The application note, *MC9328MX1 Reference Design for High Resolution Software Development*, (order number AN2309/D) provides details to test the display and create a proper test image (See Section 3.4).

**Revision History**

# 7 Revision History

The changes from Revision 1 to revision 1.1 of this document follows:

• Updated URL from Motorola to Freescale Semiconductor.

NOTES

#### How to Reach Us:

#### USA/Europe/Locations Not Listed:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong 852-26668334

#### Home Page: www.freescale.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Learn More: For more information about Freescale products, please visit www.freescale.com.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. ARM and the ARM Powered logo are registered trademarks of ARM Ltd. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004. All rights reserved.