## **Application Note**

AN2329/D Rev. 0, 9/2002

Interfacing the MSC8101 to SDRAM on the MSC8101ADS

by Marwan Younis Al-saiegh

## CONTENTS

- SDRAM Machine Basics 1

MT48LC2M32B2TG

- SDRAM Device...... 4 2.1 SDRAM Main Interface

- Commands...... 5

- 2.2 SDRAM Operations..... 6

- 2.3 SDRAM Row and Column Addressing..... 6

- 2.4 SDRAM Timing

1

- MSC8101 SDRAM Machine.....11

- 3.1 Selecting the SDRAM

- Machine.....11

- 3.2 Page Hit Checking .... 11

- 3.3 Partitioning the System Bus...... 11

- 3.4 Memory Controller

- Bank Registers...... 15 3.5 SDRAM Machine Initialization on the

- MSC8101ADS ...... 23

- 4 Related Reading ...... 25

# Synchronous DRAM (SDRAM) is one of the most cost effective read/write memories on the market, offering high-performance throughput with the cost benefits of a commodity item. In synchronous DRAM, all the memory signal timing relates to a single clock that allows SDRAM to provide significantly faster access time than DRAM.

This application note discusses the interface between the Motorola MSC8101 memory controller (SDRAM machine) and an example JEDEC-compatible MICRON SDRAM device, which is referred to as the MT48LC2M32B2TG device. It begins with an overview of SDRAM basics, including the signals for interfacing an SDRAM device to the MSC8101 device, and then discusses the MSC8101 (DSP side) SDRAM machine. Finally, the application note shows how to initialize SDRAM using the MSC8101 SDRAM machine.

# SDRAM Machine Basics

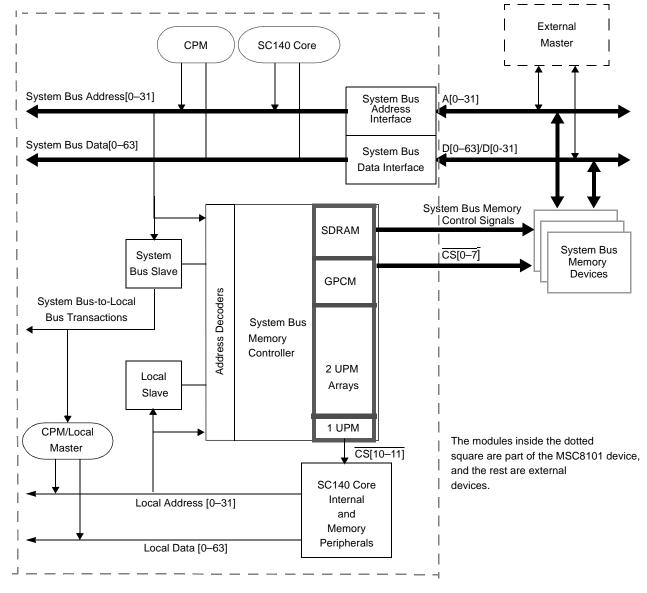

**Figure 1** shows the MSC8101 memory controller (MEMC), which consists of three user-programmable machines (UPMs), one general-purpose chip-select machine (GPCM), and one SDRAM machine. The SDRAM machine is available only on the system bus, which can assign memory banks to the SDRAM machine. Features of the SDRAM machine include:

- · Control functions and signals for a glueless connection to JEDEC-compliant SDRAM devices

- Two types of page mode, each selectable per memory bank: back-to-back page mode for consecutive and back-to-back accesses and page mode for intermittent accesses

- 2-, 4-, and 8-way bank interleaving

- An SDRAM port size of 64 bits, 32 bits, 16 bits, or 8 bits

- · External address and/or command line buffering

The SDRAM machine operates in one of two bus modes, Single-Master Bus mode and Multi-Master Bus mode. In Single-Master Bus mode, the MSC8101 device is the only master on the system bus, and the MSC8101 device interfaces directly to memory and slave peripherals. It sends address and control signals for a direct, glueless interface to the SDRAM. There is no need for external address latching because the MSC8101 MEMC handles address multiplexing.

**Freescale Semiconductor, Inc.**

**MOTOROLA** intelligence everywhere<sup>\*\*</sup>

digitaldna

Figure 1. MSC8101 Memory Controller

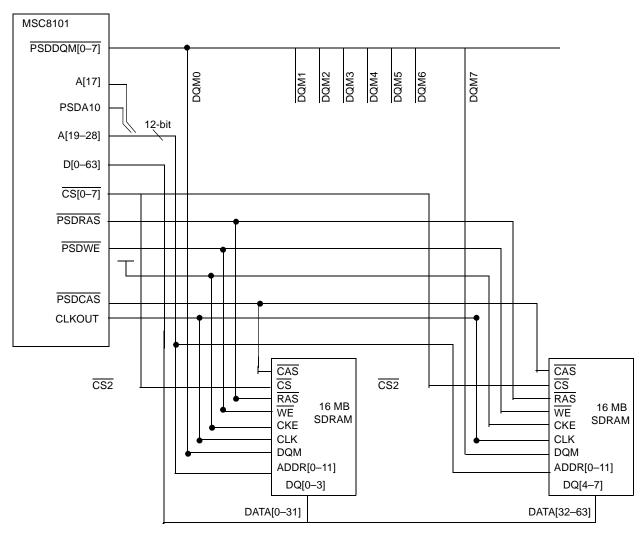

**Figure 2** depicts Single-Master Bus mode. In system bus Multi-Master Bus mode, there are separate address and data tenure phases during which the address is not driven for the entire bus transaction, so internal address multiplexing is not used. Furthermore, external logic must latch the address and multiplex the columns and row addresses to the SDRAM device at the appropriate time.Thus, the MSC8101 uses the Address Latch Enable (ALE) and Select Pin (SDMUX) signals to control the interface between the MSC8101 and SDRAM devices. This application note focuses on the SDRAM hardware interconnect for Single-Master Bus mode.

Figure 2. Single-Bus Mode SDRAM Hardware Interconnect to MSC8101 SDRAM Machine<sup>1</sup>

**Table 1** lists the key components of the SDRAM architecture of the SDRAM device that connects to the MSC8101 memory controller SDRAM machine.

Table 1. SDRAM Architecture

| Component         | Description                                                                                                                                                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock             | The clock is an oscillator that toggles between 0 volts and $V_{CC}$ ( $V_{CC}$ = 3.3 volts in this case). The period of the clock is the time to complete one cycle and is the inverse of the frequency. For the MSC8101, SDRAM read and write operations are synchronized to the system bus clock. |

| Command Control   | The MT48LC2M32B2TG SDRAM device uses 4-bit long command words. These command control signals are inputs that control the SDRAM device. The command decoder monitors CS, RAS, CAS, and WE to determine which command to execute                                                                       |

| Bank Architecture | The SDRAM memory array is divided into two or more banks so that one bank of the memory array can precharge while the other bank is accessed. This scheme eliminates precharge latency and effectively increases the bandwidth.                                                                      |

<sup>&</sup>lt;sup>1</sup> On the MSC8101ADS, the CKE signal of one SDRAM module is tied low for a 32-bit wide bus.

| Component                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pipelined Operation            | The MT48LC2M32B2TG SDRAM device employs a three-stage pipeline that allows<br>new memory accesses to be initiated before the preceding access completes. When<br>the pipeline is full, data can be accessed on every clock cycle. Along with burst<br>mode access, this feature significantly improves data transfer performance.                                                                                                                                      |

| A10/Auto Precharge             | During ACTIVE operation, A[0–10] provide row address information. During read and write operations, A10 pulled high enables the auto precharge feature, and A10 pulled low disables it. BA[0–1] determine which bank is being read from or written to.                                                                                                                                                                                                                 |

| Refresh and Refresh<br>Counter | During the refresh operation the SDRAM auto refreshes if Clock Enable (CKE) is high; it self refreshes if CKE is low. A refresh counter controls row addressing and tracks the next row number to be refreshed in preparation for the next refresh command. When the MSC8101ADS board is configured for a 32-bit bus mode, one SDRAM CKE signal is tied low. When the CKE signal is tied low, the SDRAM device can retain its values while it is in self refresh mode. |

| CAS Latency                    | The MSC8101 SDRAM machine accesses a row of the memory matrix by putting an address on the memory address pins and activating the RAS signal. After a defined number of clock cycles (known as RAS-to-CAS delay), the column address is put on the address pins, and the CAS signal is activated to access the correct column of the memory matrix. Finally, after another defined number of clock cycles (CAS latency), the data appears on the pins of the RAM.      |

Table 1. SDRAM Architecture (Continued)

# MT48LC2M32B2TG SDRAM Device

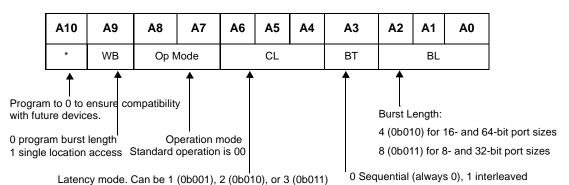

The MT48LC2M32B2TG SDRAM device contains a mode register that is initialized at power-up (see **Figure 3**). This register configures basic SDRAM device operation, such as the following:

- **CAS** latency (1, 2, or 3)

- Burst length (4 beats for 64-bit and 16-bit port sizes, 8 beats for 32-bit and 8-bit port sizes)

- Burst type (sequential or interleaved)

The burst operation uses an on-chip burst counter that increments the column addresses, yielding very fast burst accesses.

Figure 3. Mode Register Definition

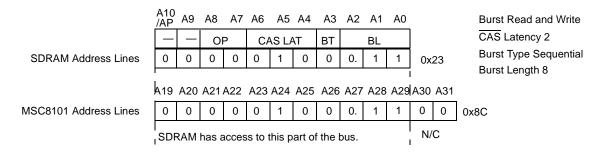

When the Mode Register Set (MRS) command is issued during SDRAM initialization, the MSC8101 PSDMR[2–4]:OP field must contain a value of 011 to initialize the SDRAM (see **Table 22** for details). To program the SDRAM device for a CAS latency of 2- and 8-beat bursts in Single-Master Bus mode with a 32-bit port size, the bits in the MSC8101 PSDMR register must be configured as follows:

- PSDMR[23]:BL = 1

- PSDMR[30–31]:CL = 010

#### For More Information On This Product, Go to: www.freescale.com

2

When WB (shown in **Figure 3**) is cleared, the burst length programmed via BL applies to both read and write bursts. When WB is set to 1, the programmed burst length applies to read bursts, but write bursts are single location (non burst) access. To select the Normal operating mode, assign the SDRAM mode register OP mode bits (8 and 7) a value of 00. Other combinations of values are reserved for future use.

To program the SDRAM device for a  $\overline{CAS}$  latency of 2 and burst lengths of 8 beats in Multi-Master Bus mode, these settings must be also be in effect. Also, the value in the SDRAM register is 0x23, which requires a write to the mode register at address 0x20000000 + 0x8C. The port size is 32 bits because the SDRAM Mode Register is shifted by two bits (A[30–31]) to account for the port size settings (see **Figure 4**).

Figure 4. SDRAM Mode Register Programming Example for 32-Bit Port Size

# 2.1 SDRAM Main Interface Commands

The MSC8101 device performs all accesses to SDRAM in compliance with JEDEC-standard SDRAM interface commands. The SDRAM device samples command and data inputs on the rising edge of the MSC8101 bus clock. Data at the output of the SDRAM device must also be sampled on the rising edge of the MSC8101 bus clock. A successful read/write transaction proceeds as follows:

- ACTIVATE. Occurs when a new row in the bank is accessed. The row is transferred to the page data register. The ACTIVATE command opens (or activates) a row in a particular bank for a subsequent access.

- READ. Occurs when data is transferred from the SDRAM page data register to the data bus. The READ command initiates a burst read access to an active row. The value on the BA[0–1] inputs selects the bank, and the address on inputs A[0–7] selects the starting column location.

- WRITE. Occurs when data is transferred from the data bus to the SDRAM page data register. The WRITE command initiates a burst write access to an active row. The value on the BA[0–1] inputs selects the bank, and the address provided on inputs A[0–7] selects the starting column location.

- PRECHARGE. Deactivates the open row in a particular bank or the open row in all banks. This operation occurs when data is written back to SDRAM from the page data register. The row in SDRAM must be precharged before the data is written. A10 determines whether auto precharge is used. If auto precharge is selected, the accessed row is precharged at the end of the read or write burst; if auto precharge is not selected, the row remains open for subsequent accesses.

- AUTO REFERESH. Used during normal operation of the SDRAM. The internal refresh controller generates the addressing, so the address bits have a value of "Don't Care" when an auto refresh command executes. The SDRAM memory requires 4,096 auto refresh cycles every 64 μs, regardless of the width option selected. Providing a distributed AUTO REFRESH command every 15.625 μs meets the refresh requirement and ensures that each row is refreshed.

# 2.2 SDRAM Operations

Table 2 shows the functions of the SDRAM device and the pins associated with them.

| Command                                                      | CS | RAS | CAS | WE | ADDR     | DQM    | DQs    |

|--------------------------------------------------------------|----|-----|-----|----|----------|--------|--------|

| Command Inhibit (NOP)                                        | Н  | Х   | Х   | Х  | Х        | Х      | Х      |

| No Operation (NOP)                                           | L  | Н   | Н   | Н  | Х        | Х      | Х      |

| Active<br>(Select bank and activate Row)                     | L  | L   | Н   | L  | Bank/Row | Х      | Х      |

| READ (Select bank and column, and start READ burst)          | L  | Н   | L   | Н  | Bank/Col | Х      | Х      |

| WRITE (Select bank and column, and start WRITE burst)        | L  | н   | L   | L  | Bank/Col | H/L    | Valid  |

| Burst terminate                                              | L  | н   | L   | н  | Code     | Х      | ACTIVE |

| PRECHARGE (Deactivate row in bank or banks)                  | L  | Н   | L   | L  | Х        | Code   | Х      |

| AUTO REFRESH or SELF<br>REFRESH<br>(Enter self refresh mode) | L  | L   | L   | Н  | х        | Х      | Х      |

| LOAD MODE REGISTER                                           | L  | L   | L   | L  | Х        | OPCODE | Х      |

| Write Enable/Output Enable                                   |    |     |     |    |          | L      | High Z |

| Write Inhibit/Output High-Z                                  |    |     |     |    |          | н      | ACTIVE |

| Table 2. | SDRAM    | Truth  | Table  |

|----------|----------|--------|--------|

|          | 0010.001 | 110001 | i abio |

Following are important points about these commands to keep in mind:

- CKE is high for all SDRAM commands except SELF REFRESH.

- During load mode register operation, A[0–10] define the opcode written to the SDRAM Mode Register.

- During active operation, A[0–10] provide the row address, and BA[0–1] determine which bank is active.

- During read and write operation, A[0–7] provide the column address. A10 sampled high enables the auto precharge feature, and A10 sampled low disables it. BA[0–1] determine which bank is read or written.

- During precharge operation, A10 LOW: BA0 and BA1 determine which bank is precharged. A10 HIGH: All banks are precharged, and BA0 and BA1 are "Don't care."

- During a refresh operation, auto refreshes occur if CKE is held high, and self refreshes occur if CKE is held low.

- During refresh operation, an internal refresh counter controls row addressing; all inputs and I/Os are "Don't care" except for CKE.

- During write inhibit/output high Z operations, the DQ signals s are activated or deactivated during writes (zero-clock delay) and reads (two-clock delay). DQM0 controls DQ[0-7]; DQM1 controls DQ[8-15]; DQM2 controls DQ[16-23]; and DQM3 controls DQ[24-31].

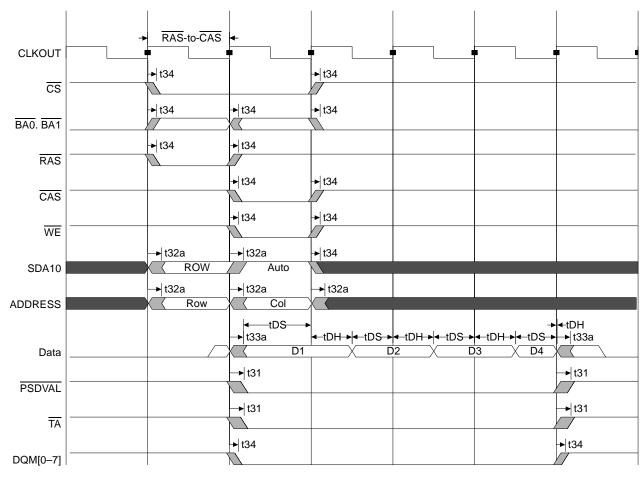

# 2.3 SDRAM Row and Column Addressing

SDRAM is usually based on a 2-, 4-, or 8-bank architecture. The Micron MT48LC2M32B2TG consists of 4 banks. BA[0–1] are bank address inputs that define the bank to which the ACTIVE, READ, WRITE, or PRECHARGE command is applied. Bank select lines are controlled using the Bus Configuration Register (BCR). When BCR[EAV] is cleared, bank select signals are driven on system bus address lines. There is

no full address visibility. When BCR[EAV] is set, bank select signals are not driven on the address bus. Bank select lines are used to drive the BA[0–1] signals. You can use the address lines or BNKSEL to drive the BA[0–1] signals. BNKSEL signals can be used to drive bank select signals in single or multi-master environments.

The row address lines are used to activate a specific bank for commands such as READ, WRITE, or PRECHARGE. MT48LC2M32B2TG uses address inputs A[0–10] as row address lines to activate a specific bank. The column address lines are used to issue a READ or WRITE command based on the status of the  $\overline{WE}$  signal. If  $\overline{WE}$  is high, a read operation is applied on the bank, and if  $\overline{WE}$  is low, a write operation is applied instead. MT48LC2M32B2TG uses address inputs A[0–7] as column address lines to fetch data during a read or write operation to a specific area in memory when a READ/WRITE command executes.

# 2.4 SDRAM Timing Diagrams

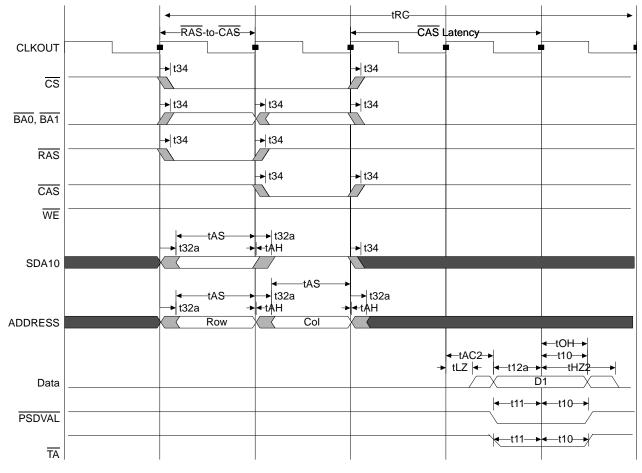

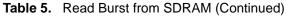

This section covers the timing diagrams of the MSC8101's SDRAM machine interface to SDRAM during read, write, read burst and write burst operations.

Figure 5. Single Read Transaction

| Name | Min  | Max | Comment                                                              |

|------|------|-----|----------------------------------------------------------------------|

| tAC2 |      | 8   | Access time from CLK (positive edge) with latency of 2               |

| tLZ  | 1    |     | Data-out low-impedance time                                          |

| t32a | 0.5  | 8.5 | Address bus/Address attributes/GBL delay from CLKIN rising edge      |

| t12a | 4.55 |     | Data bus setup time before CLKIN rising edge - normal mode           |

| t11  | 5    |     | AACK/ARTRY/TA/TEA/DBG/BG/BR set-up time before the CLKIN rising edge |

| tOH  | 2.5  |     | Data-out hold time                                                   |

| tHZ2 |      | 8   | Data-out high-impedance time                                         |

| t10  | 0.5  |     | Hold time for all signals after the CLKIN rising edge                |

| tAS  | 2    |     | Address set-up time                                                  |

| tAH  | 1    |     | Address hold time                                                    |

Table 3. Single Read Transaction

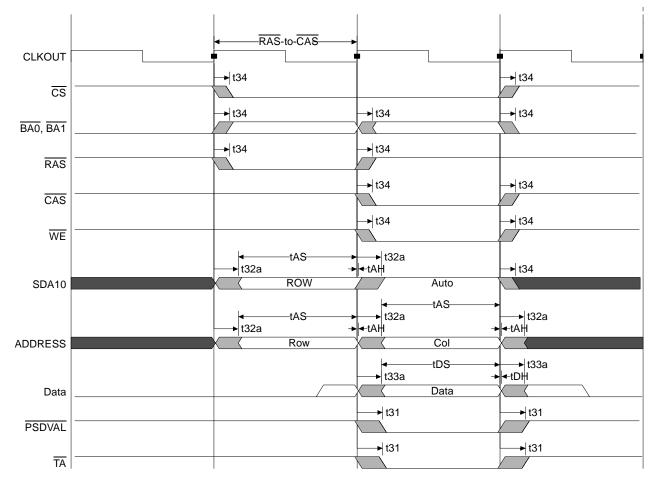

Figure 6. Write Transaction

| Name | Min | Max | Comment                                                         |

|------|-----|-----|-----------------------------------------------------------------|

| t34  | 0.5 | 5.5 | Memory controller signals/ALE delay from CLKIN rising edge      |

| t32a | 0.5 | 8.5 | Address bus/Address attributes/GBL delay from CLKIN rising edge |

| t31  | 0.5 | 9   | PSDVAL/TEA/TA delay from CLKIN rising edge.                     |

| t33a | 0.5 | 8.5 | Data bus delay from CLKIN rising edge                           |

| tDS  | 2   |     | Data-in set-up time                                             |

| tDH  | 1   |     | Data-in hold time                                               |

| tAS  | 2   |     | Address set-up time                                             |

| tAH  | 1   |     | Address hold time                                               |

Table 4. Write Transaction to SDRAM

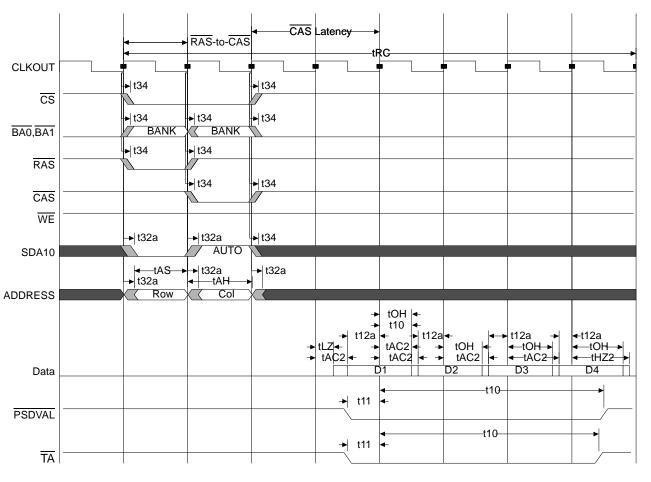

Table 5. Read Burst from SDRAM

| Name | Min | Max | Comment                                                    |

|------|-----|-----|------------------------------------------------------------|

| tAC2 |     | 8   | Access time from CLK (positive edge) with latency of 2     |

| tLZ  | 1   |     | Data-out low-impedance time                                |

| tOH  | 2.5 |     | Data-out hold time                                         |

| t34  | 0.5 | 5.5 | Memory controller signals/ALE delay from CLKIN rising edge |

| Name | Min  | Мах | Comment                                                              |

|------|------|-----|----------------------------------------------------------------------|

| t32a | 0.5  | 8.5 | Address bus/Address attributes/GBL delay from CLKIN rising edge      |

| t12a | 4.55 |     | Data bus set-up time before CLKIN rising edge, normal mode           |

| t10  | 0.5  |     | Hold time for all signals after CLKIN rising edge                    |

| t11  | 5    |     | AACK/ARTRY/TA/TEA/DBG/BG/BR set-up time before the CLKIN rising edge |

| tHZ2 |      | 8   | Data-out high-impedance time                                         |

| tAS  | 2    |     | Address set-up time                                                  |

| tAH  | 1    |     | Address hold time                                                    |

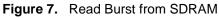

## Figure 8. Write Burst to SDRAM

## Table 6. Write Burst to SDRAM

| Name | Min | Max | Comment                                                         |  |

|------|-----|-----|-----------------------------------------------------------------|--|

| t34  | 0.5 | 5.5 | Memory controller signals/ALE delay from CLKIN rising edge      |  |

| t32a | 0.5 | 8.5 | Address bus/Address attributes/GBL delay from CLKIN rising edge |  |

| t34  | 0.5 | 5.5 | Memory controller signals/ALE delay from CLKIN rising edge      |  |

| t33a | 0.5 | 8.5 | Data bus delay from CLKIN rising edge                           |  |

| Name | Min | Max | Comment                                     |

|------|-----|-----|---------------------------------------------|

| t31  | 0.5 | 9   | PSDVAL/TEA/TA delay from CLKIN rising edge. |

| tDS  | 2   |     | Data-in set-up time                         |

| tDH  | 1   |     | Data-in hold time                           |

| Table 6. | Write Burst to SDRAM | (Continued) |

|----------|----------------------|-------------|

|----------|----------------------|-------------|

# 3 Programming the MSC8101 SDRAM Machine

This section discusses how to interface the MICRON MT48LC2M32B2 SDRAM to the MSC8101 SDRAM machine. To program the SDRAM machine to communicate with the SDRAM correctly, complete the following steps:

1. Issue a precharge command to all banks.

2. Issue eight auto refreshes.

3. Program the SDRAM device mode register.

# 3.1 Selecting the SDRAM Machine

The MT48LC2M32B2 has 11 row address lines and 8 column address lines. The defined SDRAM base address is written to the MSC8101 BRn (Base register 0–7). The SDRAM bank size is written to the MSC8101 ORn (Option register 0–7). Each time a bus cycle access is requested on the system bus, the access address is compared with the addresses of all memory controller banks. If a match occurs, for example, on memory controller bank 2, BR2 and OR2 are selected (since BR2[MSEL] is set to the SDRAM machine), and the attributes defined in BR2 and OR2 are used to control the memory access.

# 3.2 Page Hit Checking

The SDRAM machine supports page mode operation. Each time a page is activated on the SDRAM device, the SDRAM machine stores its address in a page register. The page information, which the user writes to the ORn register, is used along with the bank size to compare page bits of the address to the page register each time a bus cycle access is requested. If a match occurs together with a bank match, the bus cycle is defined as a page hit. The SDRAM machine automatically closes an open page if the bus becomes idle, unless ORn [PMSEL] is set.

# 3.3 Partitioning the System Bus

This section discusses two types of interleaving, page-based and bank-based.

## 3.3.1 Page-Based Interleaving

Page-based interleaving yields the best performance and is the preferred interleaving method. Page-based interleaving supports consecutive back-to-back accesses. It uses low address bits as the bank select for the SDRAM, thus allowing interleaving on every page boundary. Paged-based interleaving is activated by setting PSDMR[PBI]. This section covers two topics:

- Partitioning the system bus address bus based on the port size settings of 32 bits or 64 bits (see **Table 7** and **Table 8**).

- Partitioning the SDRAM device address port from the SDRAM device executing a bank ACTIVATE command and read/write commands using 32- and 64-bit port size settings (see **Table 9** through **Table 12**).

## Programming the MSC8101 SDRAM Machine

| A[0-7]               | A[8–18] | A[19–20]    | A[21–28] | A[29–31] |

|----------------------|---------|-------------|----------|----------|

| MSB of start address | Row     | Bank Select | Column   | LSB      |

**Table 7.** System Bus Address Bus Partition for a 64-Bit Port Size

Table 8. System Bus Address Bus Partition for a 32-Bit Port Size

| A[0-8]               | A[0–8] A[9–19] |             | A[22–29] | A[30–31] |  |

|----------------------|----------------|-------------|----------|----------|--|

| MSB of start address | Row            | Bank Select | Column   | LSB      |  |

When the system bus address bus is partitioned for page-based interleaving, the LSB vary between a 32-bit and a 64-bit port size because address lines 31–29 are ignored for the 64-bit port size and address lines 31–30 are ignored for a 32-bit port size. The 8-bit and 16-bit port sizes are not covered because the minimum access for the MSC8101ADS SDRAM is 32 bits. That is, there are 32 data lines for each SDRAM device, so each device has a 32-bit port size. Since there are two devices, the total number of data lines is 64, for a 64-bit port size. Therefore, this application note focuses on the 32-bit and 64-bit port sizes. These configurations are based on the MSC8101ADS and are subject to change if an SDRAM with a different size and bank architecture is used.

The column address lines are A[21–28] for a 64-bit port size and A[22–29] for a 32-bit port size. The SDRAM on the MSC8101ADS board contains 11 row address lines and 8 column address lines. The row address lines are A[8–18] for a 64-bit port size and A[9-19] for a 32-bit port size. There are two bits for bank select lines because the SDRAM adapted on the MSC8101ADS has 4 banks.

Table 9.

SDRAM Device Address Port During ACTIVATE Command for a 64-Bit Port Size

| Driven<br>Signals           | A[0–15] | A[16–17]                           | A[18–28]                 | A[29–31] |  |

|-----------------------------|---------|------------------------------------|--------------------------|----------|--|

| System bus<br>Bus partition | —       | A[19–20]<br>(Internal bank select) | A[8–18]<br>(Row address) | _        |  |

Note: Driven signals are signals driven on external pins when address multiplexing is enabled.

Table 10.

SDRAM device Address Port During ACTIVATE Command for 32-Bit Port size

| Driven<br>Signals       | A[0–16] | A[17–18]                           | A[19–29]                 | A[30–31] |  |

|-------------------------|---------|------------------------------------|--------------------------|----------|--|

| System<br>Bus partition | _       | A[20–21]<br>(Internal bank select) | A[9–19]<br>(Row Address) | _        |  |

During the ACTIVATE command period, the MSC8101 sends the row address lines to the SDRAM to activate the specified bank. The MSC8101 device must choose a bank before attempting to read or write from the activated bank.

Table 11. SDRAM Device Address Port During READ/WRITE Command for 64-Bit Port Size

| Driven Signals              | A[16–17]             | A[18]      | A[19]      | A[20]      | A[21–28] | A[29–31] |

|-----------------------------|----------------------|------------|------------|------------|----------|----------|

| System bus<br>Bus partition | Internal bank select | Don't care | Don't care | Don't care | Column   |          |

| Driven Signals              | A[17–18]             | A[19]      | A[20]      | A[21]      | A[22–29] | A[30–31] |

|-----------------------------|----------------------|------------|------------|------------|----------|----------|

| System bus<br>Bus partition | Internal bank select | Don't care | Don't care | Don't care | Column   | _        |

Table 12. SDRAM Device Address Port During READ/WRITE Command for 32-Bit Port Size

The READ/WRITE command follows the ACTIVATE command. After the MSC8101 device sends the row address lines to activate the bank, the MSC8101 must either read or write to that specific bank. At this point, the MSC8101 sends the column address lines to the SDRAM to specify the starting column in the SDRAM for read or write operations. A  $\overline{CAS}$  latency occurs during reads from the SDRAM; there is no latency during writes to the SDRAM. It is important to specify auto precharge, which precharges all SDRAM banks, or single precharge, which precharges only the selected bank during execution of the ACTIVATE command.

**Table 13** shows the SDAM[5–7] bits in the PSDMR for 32-bit and 64-bit port sizes in page mode interleaving. The cells highlighted in italics apply to the 32-bit port size, and the cells highlighted in bold (red) apply to the 64-bit port size. Note the overlap.

| SDAM | External<br>System Bus<br>Address<br>Pins | A16 | A17 | A18 | A19 | A20 | A21 | A22 | A23 | A24 | A25 | A26 | A27 | A28 | A29 | A30 | A31 |

|------|-------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 000  | Signal driven                             | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 | A21 | A22 | A23 |

| 001  | on external<br>pins when                  | A7  | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 | A21 | A22 |

| 010  | address                                   | A6  | A7  | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 | A21 |

| 011  | multiplexing is                           | A5  | A6  | A7  | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 |

| 100  | enabled                                   | A4  | A5  | A6  | A7  | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 |

| 101  |                                           | _   |     | A5  | A6  | A7  | A8  | A9  | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 | A18 |

Table 13.

SDRAM Address Multiplexing for 64- and 32-Bit Port Sizes

Following are the PSDMR settings for SDRAM page mode interleaving, as listed in Table 22:

- SDAM[5–7]. The A[8–18] signals are driven on the external pins when address multiplexing is enabled. For the 64-bit port size, these signals match the A[18–28] external system bus address pins. For the 32-bit port size, the A[9–19] signals are driven on the external pins when address multiplexing is enabled. These signals match the A[19–29] external system bus address pins. Thus, SDAM is set to 010. Therefore, bits 5–7 in the PSDMR are the same for both 32-bit and 64-bit port sizes.

- BSMA[8–10]. Since the row address lines start at A8 for 64-bit port size and at A9 for 32-bit port size, the range of bank select lines ends at A17 for the 64-bit port size and A18 for the 32-bit port size Thus, the PSDMR[BSMA] bits [8–10] are set to 011 for the 64-bit port size and to 100 for the 32-bit port size, respectively. This configuration applies only when the MT48LC2M32B2 is used on the MSC8101ADS. These configurations vary depending on SDRAM bank architecture (that is, 2 or 4 banks), and the number of row and column addresses.

- SDA10 [11–13]. The starting row address for the 64-bit port size is A8, and the starting row address for the 32-bit port size is A9. Thus, SDA10 [11–13] is set to 010 for the 64-bit port size and to 001 for the 32-bit port size.

Figure 9 summarizes the address multiplexing for a 32-bit port size.

Figure 9. MSC8101 SDRAM Address Multiplexing.

**Note:** Partitioning is affected if a different SDRAM is used. Usually the number of row and column address lines varies according to the size of the SDRAM. As long as the SDRAM device address port and the system bus address bus is partitioned according to the correct number of row and columns address lines, BR, OR, and PSDMR are programmed correctly.

# 3.3.2 Bank-Based Interleaving

Bank-based interleaving uses the most significant address bits as the bank select for the SDRAM, thus allowing interleaving only on bank boundaries. It is activated by clearing PSDMR[PBI]. See **Table 14** through **Table 19**.

**Table 14.** System Bus Address Bus Partition for 64-Bit Port Size

| A[0-7]               | A[8–9]                | A[10–20] | A[21–28] | A[29–31] |  |

|----------------------|-----------------------|----------|----------|----------|--|

| MSB of start address | Internal bank address | Row      | Column   | LSB      |  |

Table 15. System Bus Address Bus Partition for 32-Bit Port Size

| A[0–8]               | A[9–10]               | A[11–21] | A[22–29] | A[30–31] |

|----------------------|-----------------------|----------|----------|----------|

| MSB of start address | Internal bank address | Row      | Column   | LSB      |

Table 16. SDRAM Address Port During ACTIVATE for 64-Bit Port Size

| Driven<br>Signals       | A[0–15] | A[16–17]                         | A[18–28]                  | A[29–31] |

|-------------------------|---------|----------------------------------|---------------------------|----------|

| System bus<br>partition | —       | A[8-9]<br>(Internal bank select) | A[10-20]<br>(Row address) | _        |

Table 17.

SDRAM Address Port During ACTIVATE for 32-Bit Port Size

| Driven<br>Signals       | A[0–16] | A[17–18]                          | A[19–29]                  | A[30–31] |

|-------------------------|---------|-----------------------------------|---------------------------|----------|

| System bus<br>partition |         | A[9-10]<br>(Internal bank select) | A[11-21]<br>(Row address) |          |

| Driven Signals          | A[16–17]             | A18        | A19        | A20        | A[21–28] | A[29–31] |  |  |  |  |

|-------------------------|----------------------|------------|------------|------------|----------|----------|--|--|--|--|

| System bus<br>partition | Internal bank select | Don't care | Don't care | Don't care | Column   | —        |  |  |  |  |

Table 18.

SDRAM Device Address Port During READ/WRITE for 64-Bit Port Size

Table 19. SDRAM Device Address Port During READ/WRITE for 32-Bit Port Size

| Driven Signals          | A[17–18]             | A19        | A20        | A21        | A[22–29] | A[30–31] |

|-------------------------|----------------------|------------|------------|------------|----------|----------|

| System bus<br>partition | Internal bank select | Don't care | Don't care | Don't care | Column   | —        |

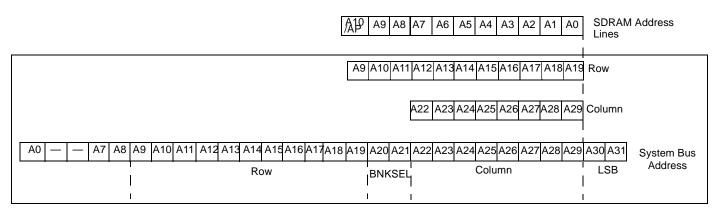

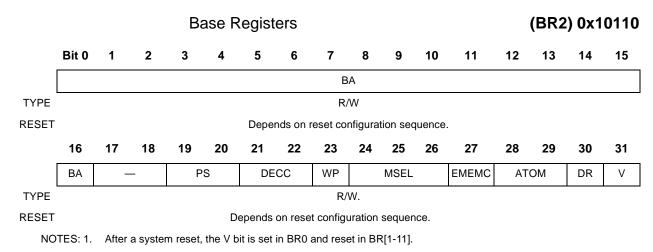

# 3.4 Memory Controller Bank Registers

This section shows the MSC8101 registers and bit settings necessary to program the SDRAM machine properly for page-based interleaving both the 32-bit and 64-bit port sizes. The MSC8101 is connected to the MT48LC2M32B2 SDRAM device. The interface timings, bursts, and interleaving are easily programmed in the SDRAM machine registers. The MSC8101 registers to be programmed are as follows:

- Base Registers (BRx)

- Option Registers (ORx)

- 60x SDRAM Mode Register (PSDMR)

- 60x Bus-Assigned SDRAM Refresh Timer (PSRT)

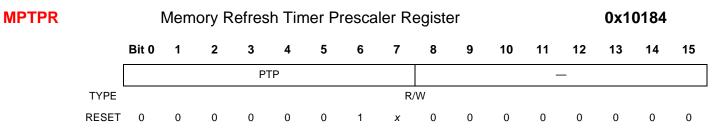

- Memory Refresh Timer Prescaler Register (MPTPR)

All possible bit settings are shown for each register, and, for each bit, the selected setting for this application is highlighted in bold.

NO

The base registers contain the base address and address type that the memory controller uses to compare the address bus value with the current address accessed.

BRx

## Programming the MSC8101 SDRAM Machine

## Table 20. BRx Bit Settings

| Name                 | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             | Settings                                                                                                                                                                               |

|----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>BA</b><br>0–16    | 1     | <b>Base Address</b><br>The upper 17 bits of each base address register are compared to the address on the address bus to determine if the bus master is accessing a memory bank controlled by the memory controller.<br>BRx[BA] is used with OR <i>x</i> [AM].                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |                                                                                                                                                                                        |

| <br>17–18            | 0     | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |                                                                                                                                                                                        |

| <b>PS</b><br>19–20   | 0     | Port Size<br>Specifies the port size of this memory region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>00</b><br><b>11</b><br>10<br>01                          | <b>64-bit.</b><br><b>32-bit.</b><br>16-bit.<br>8-bit.                                                                                                                                  |

| <b>DECC</b> 21–22    | 0     | Data Error Correction and Checking<br>Specifies the method for data error checking and correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00<br>01<br>10<br>11                                        | Data errors checking disabled.<br>Normal parity checking.<br>Read-modify-write parity checking.<br>ECC correction and checking.                                                        |

| <b>WP</b><br>23      | 0     | Write Protect<br>Can restrict write accesses within the address range of a BR. An<br>attempt to write to this address range while WP = 1 can cause TEA<br>to be asserted by the bus monitor logic (if enabled) which terminates<br>the cycle. When WP is set, the memory controller does not assert CSx<br>and PSDVAL on write cycles to this memory bank. TESCR1[WP] or<br>L_TESCR1[WP] is set if a write to this memory bank is attempted                                                                                                                                                                                                                            | <b>0</b><br>1                                               | Read and write accesses are allowed.<br>Only read access is allowed.                                                                                                                   |

| <b>MSEL</b><br>24–26 | 0     | Machine Select<br>Specifies machine select for the memory operations handling and<br>assigns the bank to the system bus if GPCM or SDRAM are selected.<br>If UPMx is selected, the bus assignment is determined by<br>MxMR[BSEL].                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000<br>001<br><b>010</b><br>011<br>100<br>101<br>110<br>111 | GPCM— system bus (reset value).<br>GPCM— local bus.<br><b>SDRAM— system bus.</b><br>Reserved.<br>UPMA.<br>UPMB.<br>UPMC.<br>Reserved.                                                  |

| <b>EMEMC</b> 27      | 0     | <b>External MEMC Enable</b><br>Overrides MSEL and assigns the bank to the system bus. However,<br>other BRx fields remain in effect. When this bit is set, the external<br>memory controller is expected to assert AACK, TA, and PSDVAL.                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>0</b><br>1                                               | Accesses are handled by the memory<br>controller according to MSEL.<br>Accesses are handled by an external<br>memory controller (or other slave) on the<br>system bus.                 |

| <b>ATOM</b> 28–29    | 0     | Atomic Operation<br>Note that If the device fails to release the bus, the lock is released<br>after 256 clock cycles. Writes to the address space handled by the<br>memory controller bank cause the MSC8101 to lock the bus for the<br>exclusive use of the master. The lock is released when the master<br>performs a read operation from this address space. This feature is<br>intended for CAM operations.<br>Reads from the address space handled by the memory controller<br>bank cause the MSC8101 to lock the bus for the exclusive use of the<br>accessing device. The lock is released when the device performs a<br>write operation to this address space. | 00<br>01<br>10<br>11                                        | The address space controlled by the<br>memory controller bank is not used for<br>atomic operations.<br>Read-after-write-atomic (RAWA).<br>Write-after-read-atomic (WARA).<br>Reserved. |

| <b>DR</b><br>30      | 0     | Data Pipelining           This feature is for memory regions that use ECC or parity checks and need to improve data set-up time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>0</b><br>1                                               | No data pipelining.<br>Data beats of accesses to the address space<br>controlled by the memory controller bank are<br>delayed by one cycle.                                            |

#### Table 20. BRx Bit Settings

| Name           | Reset          | Description                                                                                                                                                                                                                                           |        | Settings                                            |

|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------|

| <b>V</b><br>31 | 0 <sup>2</sup> | Valid Bit<br>Indicates that the contents of the BRx and ORx pair are valid. The $\overline{CS}$ signal does not assert until V is set. An access to a region with no V bit set may cause a bus monitor time-out. After a system reset, BR0[V] is set. | 0<br>1 | This bank is invalid.<br><b>This bank is valid.</b> |

| NOT            |                | epends on reset configuration sequence.<br>fter a system reset, the V bit is set in BR0 and reset in BR[1–11].                                                                                                                                        |        |                                                     |

ORx

|       | Option Registers—SDRAM Mode |    |    |    |    |     |    |    |      | (  | (OR2) | ) 0x1 | 0114  |    |    |    |  |

|-------|-----------------------------|----|----|----|----|-----|----|----|------|----|-------|-------|-------|----|----|----|--|

|       | Bit 0                       | 1  | 2  | 3  | 4  | 5   | 6  | 7  | 8    | 9  | 10    | 11    | 12    | 13 | 14 | 15 |  |

|       |                             |    |    |    |    | SDA | M  |    |      |    |       |       | LSDAM |    |    |    |  |

| TYPE  |                             |    |    |    |    |     |    | R/ | W    |    |       |       |       |    |    |    |  |

| RESET | 0                           | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0    | 0  | 0     | 0     | 0     | 0  | 0  | 0  |  |

|       | 16                          | 17 | 18 | 19 | 20 | 21  | 22 | 23 | 24   | 25 | 26    | 27    | 28    | 29 | 30 | 31 |  |

|       | LSDAM                       | BF | PD |    | RO | WST |    |    | NUMR |    | PMSEL | IBID  |       | -  | _  |    |  |

| TYPE  |                             |    |    |    |    |     |    | R/ | W    |    |       |       |       |    |    |    |  |

| RESET | 0                           | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0    | 0  | 0     | 0     | 0     | 0  | 0  | 0  |  |

OR defines the size of memory banks and address attributes. All possible bit settings are shown, and, for each bit, the selected setting for this application is highlighted in bold.

| Name                  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Settings                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>SDAM</b><br>0-11   | 0     | SDRAM Address Mask<br>Masks corresponding BRx bits. Masking address bits<br>independently allows SDRAM devices of different size<br>address ranges to be used. Clearing bits masks the<br>corresponding address bit. Setting bits causes the<br>corresponding address bit to be compared with the address<br>pins. Address mask bits can be set or cleared in any order,<br>allowing a resource to reside in more than one area of the<br>address map. SDAM can be read or written at any time.<br>NOTE: If PSDMR[PBI]=0, the maximum size of the memory<br>bank should not exceed 128 MB. | 0000_0000_00004 GB<br>1000_0000_00002 GB<br>1100_0000_00001 GB<br>1110_0000_0000512 MB<br>1111_0000_0000256 MB<br>1111_100_000064 MB<br>1111_1100_000064 MB<br>1111_1110_000032 MB<br>1111_1111_000016 MB (for 64-bit port size)<br>1111_1111_1000 8 MB (for 32-bit port size)<br>1111_1111_1000 8 MB<br>1111_1111_1110 2 MB<br>1111_1111_1111 MB |

| <b>LSDAM</b><br>12–16 | 0     | Lower SDRAM Address Mask<br>Reset LSDAM to 0x0 to implement a minimum size of 1 MB<br>when SDRAM is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                   |

Table 21. ORx Bit Settings (SDRAM Mode)

| Name                | Reset                                                      | Description                                                                                                                                                           | Settings                                                                                                                        |  |  |

|---------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     |                                                            | SDRAM Page Informat                                                                                                                                                   | ion                                                                                                                             |  |  |

| <b>BPD</b><br>17–18 | 0                                                          | Banks Per Device<br>Sets the number of internal banks per SDRAM device. Note                                                                                          | <ul><li>00 2 internal banks per device.</li><li>01 4 internal banks per device (settings are common</li></ul>                   |  |  |

|                     | that for 128-MB SDRAMs, BPD must have a value of 00 or 01. |                                                                                                                                                                       | <ul> <li>for both 32-bit and 64-bit port sizes).</li> <li>8 internal banks per device (not valid for 128-MB SDRAMs).</li> </ul> |  |  |

|                     |                                                            |                                                                                                                                                                       | 11 Reserved.                                                                                                                    |  |  |

| ROWST               | 0                                                          | Row Start Address Bit                                                                                                                                                 | For PSDMR[PBI] = 0:                                                                                                             |  |  |

| 19–22               |                                                            | Sets the demultiplexed row start address bit. The value of                                                                                                            | 0010 A7.                                                                                                                        |  |  |

|                     |                                                            | ROWST depends on PSDMR[PBI].                                                                                                                                          | 0100 A8.                                                                                                                        |  |  |

|                     |                                                            |                                                                                                                                                                       | 0110 A9.                                                                                                                        |  |  |

|                     |                                                            |                                                                                                                                                                       | 1000 A10.                                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 1010 A11.                                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 1100 A12.                                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 1110 A13.                                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | Other values are reserved.                                                                                                      |  |  |

|                     |                                                            |                                                                                                                                                                       | For PSDMR[PBI] = 1:                                                                                                             |  |  |

|                     |                                                            |                                                                                                                                                                       | 0000 A0.                                                                                                                        |  |  |

|                     |                                                            |                                                                                                                                                                       | 0001 A1.                                                                                                                        |  |  |

|                     |                                                            |                                                                                                                                                                       | 0010 A2.                                                                                                                        |  |  |

|                     |                                                            |                                                                                                                                                                       |                                                                                                                                 |  |  |

|                     |                                                            |                                                                                                                                                                       | 1000 A8 (for 64-bit port size).                                                                                                 |  |  |

|                     |                                                            |                                                                                                                                                                       | 1001 A9 (for 32-bit port size).                                                                                                 |  |  |

|                     |                                                            |                                                                                                                                                                       | 1101–1111 Reserved.                                                                                                             |  |  |

| NUMR                | 0                                                          | Number of Row Address Lines                                                                                                                                           | 000 9 row address lines.                                                                                                        |  |  |

| 23–25               |                                                            | Sets the number of row address lines in the SDRAM device.                                                                                                             | 001 10 row address lines.                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 010 11 row address lines (settings are common for both 32-bit and 64-bit port sizes).                                           |  |  |

|                     |                                                            |                                                                                                                                                                       | 011 12 row address lines.                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 100 13 row address lines.                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 101 14 row address lines.                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 110 15 row address lines.                                                                                                       |  |  |

|                     |                                                            |                                                                                                                                                                       | 111 16 row address lines.                                                                                                       |  |  |

| PMSEL<br>26         | 0                                                          | Page Mode Select<br>Selects page mode for the SDRAM connected to the                                                                                                  | 0 Back-to-back page mode (normal operation). Page is closed when the bus becomes idle.                                          |  |  |

|                     |                                                            | memory controller bank.                                                                                                                                               | <ol> <li>Page is kept open until a page miss or refresh<br/>occurs.</li> </ol>                                                  |  |  |

| IBID<br>27          | 0                                                          | Internal Bank Interleaving Within Same Device Disable<br>Setting this bit disables bank interleaving between internal                                                 | 0 Enables bank interleaving (setting is common for both 32-bit and 64-bit port sizes).                                          |  |  |

|                     |                                                            | banks of a SDRAM device connected to the chip-select line.<br>IBID should be set in multi-master bus mode if the SDRAM<br>device is not connected to the BNKSEL pins. | 1 Disables bank interleaving.                                                                                                   |  |  |

| <br>28–31           | 0                                                          | Reserved. Write to zero for future compatibility.                                                                                                                     |                                                                                                                                 |  |  |

| Table 21. | ORx Bit Settings (SDRAM Mode) |

|-----------|-------------------------------|

|-----------|-------------------------------|

| R |       |       |      | 60   | )x SD | RAM | Mod   | le Reç | gister |      |      |    |    |       | 0x101  | 90  |    |

|---|-------|-------|------|------|-------|-----|-------|--------|--------|------|------|----|----|-------|--------|-----|----|

|   |       | Bit 0 | 1    | 2    | 3     | 4   | 5     | 6      | 7      | 8    | 9    | 10 | 11 | 12    | 13     | 14  | 15 |

|   |       | PBI   | RFEN |      | OP    |     |       | SDAM   |        |      | BSMA |    |    | SDA10 | )      | RFI | RC |

|   | TYPE  |       |      |      |       |     |       |        | R      | z/W  |      |    |    |       |        |     |    |

|   | RESET | 0     | 0    | 0    | 0     | 0   | 0     | 0      | 0      | 0    | 0    | 0  | 0  | 0     | 0      | 0   | 0  |

|   |       | 16    | 17   | 18   | 19    | 20  | 21    | 22     | 23     | 24   | 25   | 26 | 27 | 28    | 29     | 30  | 31 |

|   |       | RFRC  | PR   | ETOA | СТ    | A   | CTTOR | W      | BL     | LDOT | OPRE | W  | RC | EAMUX | BUFCMD | С   | L  |

|   | TYPE  |       |      |      |       |     |       |        | R      | ./W  |      |    |    |       |        |     |    |

|   | RESET | 0     | 0    | 0    | 0     | 0   | 0     | 0      | 0      | 0    | 0    | 0  | 0  | 0     | 0      | 0   | 0  |

PSDMR configures operations pertaining to the SDRAM machine on the system bus. All possible bit settings are shown, and, for each bit, the selected setting for this application is highlighted in bold.

| Name             | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | Settings                                                                                                                                                                                                                                                                                                                               |

|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>PBI</b><br>0  | 0     | Page-Based Interleaving<br>Selects the address multiplexing method. PBI<br>works in conjunction with PSDMR[SDA10].                                                                                                                                                                                                                                                                                                                                                                        | 0<br>1                                               | Bank-based interleaving.<br>Page-based interleaving (normal operation).                                                                                                                                                                                                                                                                |

| RFEN<br>1        | 0     | <b>Refresh Enable</b><br>Indicates that the SDRAM needs refresh<br>services.                                                                                                                                                                                                                                                                                                                                                                                                              | 0<br>1                                               | Refresh services are not required.<br>Refresh services are required.                                                                                                                                                                                                                                                                   |

| <b>ОР</b><br>2–4 | 0     | SDRAM Operation<br>Determines which operation occurs when the<br>SDRAM device is accessed. If Multi-Master<br>Bus mode is in effect on the system bus or<br>the SDRAM port size is 8-/16-bit or the<br>SDRAM is connected to the BADDR lines<br>(not needed for 64-/32-bit port size), the bus<br>master must supply the mode register data<br>on the low bits of the address during the<br>access.<br>NOTE: The selection of OP depends on the<br>operation during SDRAM initialization. | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Normal operation.<br>CBR refresh, used in SDRAM initialization.<br>Self refresh (for debug purpose).<br>Mode Register write, used in SDRAM<br>initialization.<br>Precharge bank (for debug purpose).<br>Precharge all banks, used in SDRAM<br>initialization.<br>Activate bank (for debug purpose).<br>Read/write (for debug purpose). |

| Table 22. | PSDMR Settings |

|-----------|----------------|

|-----------|----------------|

**Freescale Semiconductor, Inc.**

## Programming the MSC8101 SDRAM Machine

| Name                  | Reset                                           | Description                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                       |                                       | Settings                                   |         |  |  |  |

|-----------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------|---------|--|--|--|

| <b>SDAM</b> 0<br>5–7  |                                                 | Determines how the address of the current                                                                                                                                                                      |                                                                                                                                                                                                                                                                       |                                       |                                            |         |  |  |  |

|                       | memory cycle can be output on the address pins. |                                                                                                                                                                                                                | АМ                                                                                                                                                                                                                                                                    | External<br>System Bus<br>Address Pin | Signal Driver<br>on External<br>Pin        |         |  |  |  |

|                       |                                                 |                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                    | 00                                    | A[13–31]                                   | A[5–23] |  |  |  |

|                       |                                                 |                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                    | 01                                    | A[14–31]                                   | A[5–22] |  |  |  |

|                       |                                                 |                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                     | 10                                    | A[15–31]                                   | A[5–21] |  |  |  |

|                       |                                                 |                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                     | 11                                    | A[16–31]                                   | A[5–20] |  |  |  |