# RTL8181 Wireless LAN Access Point/Gateway Controller

### **DATA SHEET**

**ISSUE 4: June 10, 2003**

# Revision History

| Issue   | Revision | Details of Change                                                                                                                                                                                                                                | Originator   | Issue Date |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|

| Issue 1 | 0.1      | First Release                                                                                                                                                                                                                                    | David Hsu    | 11/29/2002 |

| Issue 2 | 0.2      | <ol> <li>Add a section about system configuration.</li> <li>Add some descriptions about register usages.</li> </ol>                                                                                                                              | David Hsu    | 12/9/2002  |

| Issue 3 | 0.3      | <ol> <li>Add Pin number</li> <li>Add System config register</li> </ol>                                                                                                                                                                           | Victor Hsu   | 03/03/2003 |

| Issue 4 | 1.0      | <ol> <li>Add a memory map.</li> <li>Modify some register definitions and function descriptions.</li> <li>Add package information.</li> <li>Remove 32 bits flash interface support</li> <li>Add pin definitions for Maxim RF interface</li> </ol> | Victor/David | 2003/06/10 |

# **Table of Contents**

| 1. OVERVIEW                 | 4  |

|-----------------------------|----|

| 2. PIN DESCRIPTION          | 5  |

| 3. ADDRESS MAPPING          | 12 |

| 4. REGISTER MAPPING         | 13 |

| 5. SYSTEM CONFIGURATION     | 16 |

| 6. INTERRUPT CONTROLLER     | 17 |

| 7. MEMORY CONTROLLER        | 18 |

| 8. ETHERNET CONTROLLER      | 21 |

| 9. UART CONTROLLER          | 30 |

| 10. TIMER & WATCHDOG        | 33 |

| 11. GPIO CONTROL            | 35 |

| 12. 802.11B WLAN CONTROLLER | 37 |

| 13. PACKAGE INFORMATION     | 48 |

#### w1.₽:Overview

RTL8181 is a highly integrated SoC, embedded with a high-performance 32-bit RISC microcontroller, Ethernet and WLAN controller. It is a cost-effective and high-performance solution for the system of wireless LAN Access Point, wireless SOHO router, wireless Internet gateway, etc.

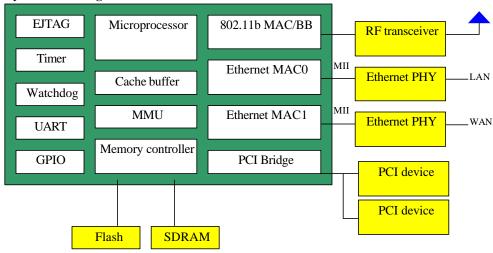

#### System block diagram:

The embedded processor of RTL8181 is Lexra LX5280 32bit RISC CPU, with 8K separate instruction and data caches. A protection unit (MMU) allows the memory be segmented and protected, and this unit is required in the modern operation system (e.g., Linux).

The processor pipeline is a dual issues and 6 stage architecture. The dual issue CPU fetches two instructions per cycle, and which could allow two instructions are executed concurrently in two pipes via some instructions. Thus, its performance will achieve up to 30% improvement over uni-scalar architecture.

Besides, it includes two fast Ethernet MACs, one could be used for LAN interface and the other one could connect to WAN port. An IEEE 802.11b WLAN MAC+Baseband processor is embedded as well. By this build-in wireless controller, it could save a lot of costs and space comparing with the system designed with an external 802.11b adapter.

The RTL8181 also integrates with memory controller, which allows customers use external SDRAM and Flash memory in glueless.

A PCI interface is supported as well, which enables customers to plug in a PCI device seamlessly. For example, an IEEE 802.11a device could be connected through this PCI interface to provide the WLAN dual mode service.

#### **Features**

#### **Core Processor**

- ∠ LX5280 32-bit RISC architecture.

- Superscalar architecture, containing 2 execution pipelines with better performance

- Embedded with 8K I-Cache, 8K D-Cache and 4K D-RAM.

- MMU supported

- ∠ Up to 200MHZ operating frequency

#### WLAN Controller

- Support Tx data rate in 11M, 5.5M, 2M and 1M

- Support long and short preamble

- Support antenna diversity and AGC.

www.DataSheet4U.com

#### **Fast Ethernet Controller**

- ≤ Fully compliant with IEEE 802.3/802.3u

- Support IP, TCP and UDP checksum offload

- Support IEEE 802.1Q VLAN tagging and 802.1P priority queue.

- Support full duplex flow control (IEEE 802.3X)

#### **UART**

- ∠ 16 bytes FIFO size

- ∠

✓

Auto CTS/RTS flow control

#### **Memory Controller**

- Support external 16/32-bit SDRAM with 2 banks access, up to 32M bytes

- Support external 16-bit Flash memory, up to 16M bytes

#### **PCI Bridge**

- Support two external PCI devices, complied with PCI 2.2

#### **GPIO**

- ✓ 16 programmable I/O ports and more 16 port when memory interface is 16 bit mode.

- ✓ Individually configurable to input, output and edge transition

#### Watchdog/Timer/Counter

- ∠ 4 sets of general timers/counters

#### **EJTAG**

Standard P1149.1 JTAG interface for testing and debugging

### 2. Pin Description

| Symbol    | Tvn   | Pin No(208) | Pin No(292)   | Description                             |

|-----------|-------|-------------|---------------|-----------------------------------------|

| Symbol    | e     | 11111(200)  | 1 m 1 (0(2)2) | 2 coci puoi                             |

| Memory In | terfa | ce          |               |                                         |

| MD[31-0]  | I/O   | 198,197,195 | P1,P2,N3,N    | Data for SDRAM, Flash                   |

|           |       | ,194,193,19 | 2,N1,M3,M     |                                         |

|           |       | 2,191,190,1 | 2,M1,L2,L3,   |                                         |

|           |       | 88,187,185, | L1,K2,K3,K    |                                         |

|           |       | 184,182,181 | 1,J2,J1,H2,   |                                         |

|           |       | ,180,179,17 | H1,G2,F1,G    |                                         |

|           |       | 7,176,174,1 | 3,F2,E1,F3,   |                                         |

|           |       | 73,171,170, | E2,D1,D2,E    |                                         |

|           |       | 169,168,166 | 3,A1,B1,B2,   |                                         |

|           |       | ,165,163,16 | C3            |                                         |

|           |       | 2,161,160,1 |               |                                         |

|           |       | 59,158      |               |                                         |

| MA[21-0]/ | O     | 115,116,118 | B14,A15,D1    | Address for SDRAM, Flash                |

| DQM[3-0]  |       | ,119,121,12 | 4,C14,A14,    | MA[15-18] mapping to DQM[3-0] for SDRAM |

|           |       | 2,124,125,1 | C13,B13,C1    |                                         |

|           |       | 27,128,130, | 2,A12,C11,    |                                         |

|           |       | 131,133,134 | B11,C10,A1    |                                         |

|           |       | ,135,136,13 | 1,B10,A10,    |                                         |

| ww.DataShee      | t4U.co | 8,139,141,1  | C9,A9,B9,A              |                                             |

|------------------|--------|--------------|-------------------------|---------------------------------------------|

|                  |        | 42,144       | 7,C7,B7,A6              |                                             |

| M_CLK            | O      | 152          | A5                      | SDRAM clock                                 |

| MCS0B            | O      | 150          | C5                      | Bank 0 chip select FLASH chip select        |

| MCS1B            | О      | 149          | B5,                     | Bank 1 chip select FLASH chip select        |

| RASB/OE          | О      | 157          | D4                      | Raw address strobe for SDRAM;               |

| В                |        |              |                         | Output enable for Flash                     |

| CASB             | O      | 156          | A2                      | Column address strobe                       |

| MWENB            | O      | 154          | B4                      | Write enable for SDRAM and Flash            |

| MCKE             | O      | 153          | A4                      | SDRAM Clock enable                          |

| MCS2B            | O      | 147          | D5                      | Bank 0 chip select for SDRAM                |

| MCS3B            | О      | 146          | B6                      | Bank 1 chip select for SDRAM                |

| <b>UART Inte</b> | rface  | I .          |                         | 1                                           |

| URTSB            | О      | 16           | Y8                      | UART Request to send                        |

| UCTSB            | Ī      | 14           | W7                      | UART Clear to send.                         |

| USIN             | Ī      | 15           | Y7                      | UART data receive serial input              |

| USOUT            | 0      | 17           | V8                      | UART data transmit serial output            |

| Power & G        | _      | 17           | V 0                     | JOAN Cata transmit scharoutput              |

| PP[11-1]         | P      | 208 178 164  | K4 G4 F4 F              | I/O power 3.3V (Digital),                   |

| 11[11-1]         | 1      | ,151,137,12  |                         | 170 power 3.3 v (Digital),                  |

|                  |        | 3,83,58,52,3 |                         |                                             |

|                  |        | 0,4          | 7,A19,A18,              |                                             |

|                  |        | 0,4          | K17,P4,P17,             |                                             |

|                  |        |              | R17,U7,U8,              |                                             |

|                  |        |              | U14,U15                 |                                             |

| GP[11-1]         | P      | 204 189 167  | ,                       | I/O 3.3V GND (Digital)                      |

| Of [11-1]        | 1      | ,155,140,12  |                         | 1/0 3.3 V GIVD (Digital)                    |

|                  |        | 6,80,63,42,2 |                         |                                             |

|                  |        | 0,00,03,42,2 | ,H11,H10,K              |                                             |

|                  |        | 0,1          | 13,L8,L9,L1             |                                             |

|                  |        |              | 0,L11,L12,L             |                                             |

|                  |        |              | 13,M9,M10,              |                                             |

|                  |        |              | M11,N10,N               |                                             |

|                  |        |              | 11                      |                                             |

| PD[7:5],PS       | D      | 183 175 132  |                         | Core logic power 1.8V (Digital)             |

| [5:3]            | 1      |              | N4,U10,U1               | Core logic power 1.0 v (Digital)            |

| [5.5]            |        | ,190,146,74  | 1                       |                                             |

| GD[7-5],G        | D      | 186 172 120  | MQ 112 IQ D             | Core logic 1.8Ground (Digital)              |

| S[5-3]           | 1      | ,199,145,77  |                         | Core logic 1.0010tilit (Digital)            |

|                  | D      |              |                         | Wireless LAN power 3.3V(Analog)             |

| I A[0-1]         | 1      |              | 5,C17,D20,              | Wheless LAIN power 5.5 V (Androg)           |

|                  |        | 13,76,67     | G19                     |                                             |

| GA[6-1],G        | D      | 108,107,95,  | G17,F17,E1              | Wireless LAN Ground (Analog), GA7 VSUB      |

| A7               | Г      |              | 7,C16,D19,              | Wheless LAIN Glound (Analog), GA7 VSGB      |

| A                |        | 114,100,80,  | G20,A20                 |                                             |

| PD[4-1]          | P      |              | J4,H4,D10,              | Core logic 1.8V power(Digital)              |

| FD[4-1]          | Г      | 8            | D9                      | Core logic 1.8 v power(Digital)             |

| GD[4-1]          | P      |              | H13,H12,H               | Core logic LAN Ground(Digital)              |

| 00[41]           | 1      | 5            | 9,H8,M12,               | Core rogic LAIN Ground(Digital)             |

|                  |        |              | 9,H8,M12,<br>M13,N8,N9, |                                             |

|                  |        |              | N12,N13                 |                                             |

| PS[2:1]          | P      | 36,7         |                         | Core logic power 1.8V(Digital)              |

| 1.5[2.1]         |        | 50,7         | 5,U12,L17,              | Cole logic power 1.0 v(Digital)             |

|                  |        |              | M17                     |                                             |

| GS[2:1]          | P      | 39,10        |                         | Core logic 1.8V GND                         |

| US[2.1]          | Г      | 37,10        |                         | Cole logic 1.0 v GIND                       |

| TATE A NUMBER    | .ce. T | ED C4        | 6,U13                   |                                             |

|                  |        | ED Control   | T10                     | WILANITE (D. C.C. L. L. LEAC)               |

| WLTXRX           | U      | 65           | T19                     | WLAN Tx/Rx traffic indicator or JTAG reset. |

| LED0B            |        |              |                         |                                             |

| WLTXRX          |          | 64              | T10        | WILAN Try/Dry traffic indicator on ITAC CLV                                       |

|-----------------|----------|-----------------|------------|-----------------------------------------------------------------------------------|

| LED1B           | ŒU.C¢    | )O <del>4</del> | T18        | WLAN Tx/Rx traffic indicator or JTAG CLK                                          |

| RF Interfac     | ce for   | Intersil        | <u> </u>   |                                                                                   |

| RIFSCK          | 0        | 66              | R20        | 3-wire Bus Clock                                                                  |

| RIFSD           | O        | 67              | P19        | 3-wire Bus Data                                                                   |

| RFLE            | O        | 68              | P18        | 3-wire Bus Enable                                                                 |

| IFLE/AGC        | O        | 70              | N18        | IF_LE of the Intersil Chipset: PLL Synthesizer Serial Interface Latch Enable      |

| SET             | _        |                 |            | Control. CMOS output.                                                             |

| CALEN/          | O        | 71              | P20        | CAL_EN of the Intersil Chipset: CMOS output for activation of DC offset adjust    |

| AGCRESE         |          |                 |            | circuit. A rising edge activates the calibration cycle, which completes within a  |

| T               |          |                 |            | programmable time and holds the calibration while this pin is held high. In       |

|                 |          |                 |            | applications where the synthesizer is not used, this pin needs to be grounded.    |

| LNA_HL          | O        | 73              | M19        | Drive to the RF AGC Stage Attenuator: CMOS digital.                               |

| ANTSELP         | O        | 75              | M20        | Antenna Select +: The antenna selects signal changes state as the receiver        |

|                 |          |                 |            | switches from antenna to antenna during the acquisition process in the antenna    |

|                 |          |                 |            | diversity mode. This is a complement for ANTSELN for differential drive of        |

|                 |          |                 |            | ant enna switches.                                                                |

| ANTSELN         | O        | 76              | L18        | Antenna Select -: The antenna selects signal changes state as the receiver        |

|                 |          |                 |            | switches from antenna to antenna during the acquisition process in the antenna    |

|                 |          |                 |            | diversity mode. This is a complement for ANTSELP for differential drive of        |

|                 |          |                 |            | antenna switches.                                                                 |

| TRSWP           | O        | 78              | L19        | Transmit/Receive Control                                                          |

| TRSWN           | O        | 79              | L20        |                                                                                   |

| VCOPDN/         | O        | 81              | K20        | Output Pin as VCO VCC Power Enable/Disable.                                       |

| PHITXI          | _        |                 |            |                                                                                   |

| PAPE            | 0        | 82              | K19        | Transmit PA Power Enable                                                          |

| 2 227 2 2 2 2 2 | O        | 84              | K18        | The combination of PE1 and PE2 are as follows:                                    |

| XQ              |          |                 |            | 00: Power Down State, PLL Registers in Save Mode, Inactive PLL, Active Serial     |

|                 |          |                 |            | 11: Receive State, Active PLL                                                     |

|                 |          |                 |            | 10: Transmit State, Active PLL                                                    |

| DE2             | 0        | 0.5             | 120        | 01: Inactive Transmit and Receive States, Active PLL, Active Serial Interface     |

| PE2<br>RXIP     | O        | 85              | J20<br>B19 | Output Pin as PE2: Refer to PE1 description.                                      |

| RXIN            | AI<br>AI | 110<br>109      | B19<br>B20 | Receive (Rx) In-phase Differential Analog Data                                    |

| RXQP            | AI       | 106             | C18,C19    | Receive (Rx) Quadrature Differential Analog Data                                  |

| RXQN            | AI       | 100             | C16,C19    | Receive (Kx) Quadrature Differential Affaiog Data                                 |

| RSSI            | AI       | 105             | D17        | Analog Input to the Receive Power A/D Converter for AGC Control                   |

| TXDET           | AI       | 103             | D17        | Input to the Transmit Power A/D Converter for Transmit AGC Control                |

| VREFI           | AI       | 101             | C20        | Voltage Reference for ADC and DAC                                                 |

| TXIP            | AO       | 97              | E19,F18    | Transmit (TX) In-phase Differential Analog Data                                   |

| TXIN            |          | 96              | L17,1 10   | Transmit (171) in phase Differential Analog Data                                  |

| TXQP            |          | 94              | E20,F20    | Trans mit (TX) Quadrature Differential Analog Data                                |

| TXQN            |          | 93              | 220,1 20   | Than the (171) Quadrature Differential Analog Data                                |

| TXAGC           | AO       | 91              | F19        | Analog Drive to the Transmit IF Power Control                                     |

| RXAGC           |          | 90              | G18        | Analog Drive to the Receive IF AGC Control                                        |

| RF Interfac     |          |                 | 1000       | <u></u>                                                                           |

|                 | 0        | 66              | R20        | 3-wire Bus Clock: The serial clock output, with resistive dividers on board to    |

|                 |          |                 |            | allow programming from +5V levels.                                                |

| RIFSD           | О        | 67              | P19        | 3-wire Bus Data: Serial data output, with resistive dividers on board to allow    |

|                 |          |                 |            | programming from +5V levels.                                                      |

| RFLE            | О        | 68              | P18        | 3-wire Bus Enable: Enable serial port output, with resistive dividers on board to |

|                 |          |                 |            | allow programming from +5V levels.                                                |

| IFLE/AGC        | X*       | 70              | N18        | Not used in the RFMD RF chipset.                                                  |

| SET             |          |                 |            |                                                                                   |

| CALEN/          | X        | 71              | P20        | Not used in the RFMD RF chipset.                                                  |

| AGCRESE         |          |                 |            |                                                                                   |

| T               |          |                 |            |                                                                                   |

| LNA_HL          | O        | 73              | M19        | RF2494 Gain Select: Digital output.                                               |

|                   | F _           | T . | 1      | T                                                                                                         |

|-------------------|---------------|-----|--------|-----------------------------------------------------------------------------------------------------------|

| ANTSELP           | <b>O</b> J.co | 75  | M20    | Antenna Select +: The antenna selects signal changes state as the receiver                                |

|                   |               |     |        | switches from antenna to antenna during the acquisition process in the antenna                            |

|                   |               |     |        | diversity mode. This is a complement for ANTSEL- for differential drive of                                |

| ANTEGELAL         | 37            | 7.6 | T 10   | antenna switches.                                                                                         |

| ANTSELN           |               | 76  | L18    | Not used in the RFMD RF chipset.                                                                          |

| TRSWP             | X             | 78  | L19    | Not used in the RFMD RF chipset.                                                                          |

| TRSWN             | X             | 79  | L20    | Not used in the RFMD RF chipset.                                                                          |

| VCOPDN/<br>PHITXI | O/I           | 81  | K20    | Output Pin as VCO VCC Power Enable/Disable.                                                               |

| PAPE              | О             | 82  | K19    | Power Control Output for RF2189 PA: 0V to +3.3V.                                                          |

| PE1/PHIT          | O             | 84  | K18    | This pin is the shutdown control output on board regulator when the RF Module                             |

| XQ                |               |     |        | enters either power-saving or standby mode.                                                               |

| PE2               | O             | 85  | J20    | Output pin as RF2948 RX EN/ TX EN, RF2494 OE and CE:                                                      |

|                   |               |     |        | Refer to the RF2948 and RF2494 datasheets.                                                                |

| RXIP              | AI*           | 110 | B19    | Receive (Rx) In-phase Analog Data in Single Ended                                                         |

| RXIN              | X             | 109 | B20    | Not used in RFMD RF chipset.                                                                              |

| RXQP              | ΑI            | 106 | C18    | Receive (Rx) Quadrature-phase Analog Data in Single Ended                                                 |

| RXQN              | X             | 105 | C19    | Not used in RFMD RF chipset.                                                                              |

| RSSI              | X             | 103 | D17    | Not used in RFMD RF chipset.                                                                              |

| TXDET             | ΑI            | 102 | D18    | To internal ADC which detects transmit power.                                                             |

| VREFI             | ΑI            | 101 | C20    | Reference voltage for ADC, DAC from VREF1 of RF2948B.                                                     |

| TXIP              | AO            | 97  | E19    | Transmit (TX) In phase Digital Data: Combining before connecting to TX_I of                               |

| TXIN              | AO            | 96  | F18    | RF2948B.                                                                                                  |

| TXQP              | AO            | 94  | E20    | Transmit (TX) Quadrature Digital Data: Combining before connecting to TX_Q                                |

|                   |               |     |        | of RF2948B.                                                                                               |

| TXQN              | AO            | 93  | F20    |                                                                                                           |

| TXAGC             |               | 91  | F19    | Transmit gain control output to RF2948.                                                                   |

| RXAGC             |               | 90  | G18    | RF2948 VGC receiver gain control analog output.                                                           |

| RF Interfa        | ce tor        |     | R20    | 3-wire Bus Clock: The pin RIFSCK is the "shift clock" output. If the 3-wire bus                           |

| KIFSCK            | U             | 66  | R20    |                                                                                                           |

|                   |               |     |        | is enabled, address or data bits will be clocked out from the RIFSD pin with                              |

| RIFSD             | О             | 67  | P19    | rising edges of RIFSCK.  3-wire Bus Data: The pin RIFSD is the output "data" pin. The detail timing is on |

| KIFSD             | U             | 07  | F 19   | 11.3.3.                                                                                                   |

| RFLE              | О             | 68  | P18    | 3-wire Bus Enable: The pin RFLE is an "enable" signal. It is level sensitive: If                          |

|                   |               |     |        | RFLE is of LOW value, the 3-wire bus interface on the SA2400 is enabled. This                             |

|                   |               |     |        | means that each rising edge on the RIFSCK pin will be taken as a shift cycle,                             |

|                   |               |     |        | and address/data bits are expected on RIFSD. If RFLE is HIGH, the 3-wire bus                              |

|                   |               |     |        | interface is disabled. No register settings will change regardless activity on                            |

|                   |               |     |        | RIFSCK and RIFSD.                                                                                         |

| IFLE/AGC          | I             | 70  | N18    | AGCSET of the Philips Chipset: On the digital output pin AGCRESET, a $0 \Rightarrow 1$                    |

| SET               |               |     |        | transition clears AGCSET of SA2400 to logic 0 and SA2400 starts the AGC                                   |

|                   |               |     |        | cycle. At end of AGC cycle, the AGCSET of SA2400 is asserted to logic 1. Then,                            |

|                   |               |     | 700    | AGCRESET will return to logic low.                                                                        |

| CALEN/            | О             | 71  | P20    | AGCRESET of the Philips Chipset: Please refer to the AGCSET description and                               |

| AGCRESE           |               |     |        | Philips SA2400 datasheet.                                                                                 |

| T                 |               |     | 2.54.0 |                                                                                                           |

| LNA_HL            | X*            | 73  | M19    | Not used in Philips RF chipset.                                                                           |

| ANTSELP           | O             | 75  | M20    | Antenna Select +: The artenna selects signal changes state as the receiver                                |

|                   |               |     |        | switches from antenna to antenna during the acquisition process in the antenna                            |

|                   |               |     |        | diversity mode. This is a complement for ANTSEL- for differential drive of antenna switches.              |

| ANTSELN           | 0             | 76  | L18    | Antenna Select -: The antenna selects signal changes state as the receiver                                |

| ANISELIN          |               | 70  | L10    | switches from antenna to antenna during the acquisition process in the antenna                            |

|                   |               |     |        | diversity mode. This is a complement for ANTSEL+ for differential drive of                                |

|                   |               |     |        | antenna switches.                                                                                         |

| TRSWP             | O             | 78  | L19    | Transmit and Receive Switch Control: This is a complement for TRSW                                        |

| 1100 111          |               | , 0 | 117    | 1:TX                                                                                                      |

|                   |               |     |        | 0:RX                                                                                                      |

| L                 | 1             | l   | I      | 0.14.1                                                                                                    |

| TRSWN              | <b>(0</b> J.cc | 79  | L20   | Transmit and Receive Switch Control: This is a complement for TRSW+.  1:RX  0:TX                                                                                                                                                                       |  |

|--------------------|----------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCOPDN/<br>PHITXI/ | O/I            | 81  | K20   | Output Pin as Transmit (TX) In-phase Digital Data of the Philips Chipset. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer                                                                                              |  |

| D + DE             | _              | 0.2 | 17.10 | program).                                                                                                                                                                                                                                              |  |

| PAPE               | O              | 82  | K19   | Transmit PA Power Enable: Assert high when starting transmission.                                                                                                                                                                                      |  |

| XQ                 | О              | 84  | K18   | Transmit (TX) Quadrature Digital Data of Philips Chipset. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer program).                                                                                                    |  |

| PE2                | О              | 85  | J20   | Output Pin as TX/RX Control: 1:RX 0:TX                                                                                                                                                                                                                 |  |

| RXIP               | AI*            | 110 | B19   | Receive (Rx) In-phase Analog Data: Positive path of differential pair.                                                                                                                                                                                 |  |

| RXIN               | ΑI             | 109 | B20   | Receive (Rx) In-phase Analog Data: Negative path of differential pair.                                                                                                                                                                                 |  |

| RXQP               | AI             | 106 | C18   | Receive (Rx) Quadrature-phase Analog Data: Positive path of the differential pair.                                                                                                                                                                     |  |

| RXQN               | AI             | 105 | C19   | Receive (Rx) Quadrature-phase Analog Data: Negative path of the differential pair.                                                                                                                                                                     |  |

| RSSI               | ΑI             | 103 | D17   | Received Signal Strength Indication: To internal ADC.                                                                                                                                                                                                  |  |

| TXDET              | ΑI             | 102 | D18   | Transmit Power Detect: To internal ADC which detects transmit power.                                                                                                                                                                                   |  |

| VREFI              | ΑI             | 101 | C20   | Reference Voltage for ADC & DAC                                                                                                                                                                                                                        |  |

| TXIP               | AO             | 97  | E19   | Transmit (Tx) In-phase Analog Data: Positive path of differential pair. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer program).                                                                                      |  |

| TXIN               | AO             | 96  | F18   | Transmit (Tx) In-phase Analog Data: Negative path of differential pair. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer program).                                                                                      |  |

| TXQP               | AO             | 94  | E20   | Transmit (Tx) Quadrature-phase Analog Data: Positive path of the differential pair. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer program).                                                                          |  |

| TXQN               | AO             | 93  | F20   | Transmit (Tx) Quadrature-phase Analog Data: Negative path of the differential pair. This function is valid on Tx digital mode (AnalogPhy = Digital on EEPROM writer program).                                                                          |  |

| TXAGC              | X              | 91  | F19   | Not used in Philips RF chipset                                                                                                                                                                                                                         |  |

| RXAGC              | X              | 90  | G18   | Not used in Philips RF chipset                                                                                                                                                                                                                         |  |

| RF Interfac        |                |     | 1010  | The about in Time but the book                                                                                                                                                                                                                         |  |

| RIFSCK             | 0              | 66  | R20   | 3-wire Bus Clock: The serial clock output                                                                                                                                                                                                              |  |

| RIFSD              | O              | 67  | P19   | 3-wire Bus Data: Serial data output                                                                                                                                                                                                                    |  |

| RFLE               | О              | 68  | P18   | 3-wire Bus Enable: Enable serial port output                                                                                                                                                                                                           |  |

| IFLE/AGC<br>SET    |                | 70  | N18   | Not used in the Maxim RF chipset.                                                                                                                                                                                                                      |  |

|                    | X              | 71  | P20   | Not used in the Maxim RF chipset.                                                                                                                                                                                                                      |  |

|                    | О              | 73  | M19   | LNA Gain Select Logic Output: Logic high for LNA high-gain mode, logic low for LNA low-gain mode.                                                                                                                                                      |  |

| ANTSELP            | О              | 75  | M20   | Antenna Select +: The antenna selects signal changes state as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode. This is a complement for ANTSEL- for differential drive of antenna switches. |  |

| ANTSELN            | X              | 76  | L18   | Antenna Select -: The antenna selects signal changes state as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode. This is a complement for ANTSEL+ for differential drive of antenna switches. |  |

| TRSWP              | X              | 78  | L19   | Not used in the Maxim RF chipset.                                                                                                                                                                                                                      |  |

| TRSWN              | X              | 79  | L20   | Not used in the Maxim RF chipset.                                                                                                                                                                                                                      |  |

| VCOPDN/<br>PHITXI  |                | 81  | K20   | Output Pin as VCO VCC Power Enable/Disable.                                                                                                                                                                                                            |  |

| D + DE        | 10           | 102 | 17.10                                                              | lm the part of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|--------------|-----|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAPE Shee     | <b>Q</b> ,co | 82  | K19                                                                | Transmit PA Power Enable: Assert high when starting transmission.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               | O            | 84  | K18                                                                | Not used in the Maxim RF chipset.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XQ            | _            | 0.5 | 120                                                                | N I' d M ' DE I'                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PE2           | O            | 85  | J20                                                                | Not used in the Maxim RF chipset now.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXIP          | AI*          | 110 | B19                                                                | Receive (Rx) In-phase Analog Data: Positive path of differential pair.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXIN          | X            | 109 | B20                                                                | Receive (Rx) In-phase Analog Data: Negative path of differential pair.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXQP          | ΑI           | 106 | C18                                                                | Receive (Rx) Quadrature-phase Analog Data: Positive path of differential pair.                                                                                                                                                                                                                                                                                                                                                                                                         |

| RXQN          | X            | 105 | C19                                                                | Receive (Rx) Quadrature-phase Analog Data: negative path of differential pair.                                                                                                                                                                                                                                                                                                                                                                                                         |

| RSSI          | X            | 103 | D17                                                                | Not used in Maxim RF chipset.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXDET         | ΑI           | 102 | D18                                                                | To internal ADC which detects transmit power.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VREFI         | ΑI           | 101 | C20                                                                | Not used in Maxim RF chipset.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXIP          | AO           | 97  | E19                                                                | Transmit (TX) In-phase Digital Data: Combining before connecting to TX_I of                                                                                                                                                                                                                                                                                                                                                                                                            |

| TXIN          | AO           | 96  | F18                                                                | RF2948B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TXQP          | AO           | 94  | E20                                                                | Transmit (TX) Quadrature Digital Data: Combining before connecting to TX_Q                                                                                                                                                                                                                                                                                                                                                                                                             |

|               |              | 93  |                                                                    | of RF2948B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TXQN<br>TXAGC | AO<br>AO     | 91  | F20<br>F19                                                         | Transmit gain control output to RF2948.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXAGC         | AO           | 90  | G18                                                                | Analog Drive to the Receiver AGC Control.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |              | 90  | GI8                                                                | Analog Drive to the Receiver AGC Control.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Miscellaneo   |              | 100 | E10                                                                | TTI ' (1 11 11 1 10T/O ')                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R10K          | I/O          | 99  | E18                                                                | This pin must be pulled low by a 10K O resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XO            | O            | 87  | H18                                                                | Crystal Feedback Output: This output is reserved for crystal connection. It should                                                                                                                                                                                                                                                                                                                                                                                                     |

| 371           | -            | 0.0 | 1110                                                               | be left open when XI is driven with an external 44 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XI            | 1            | 88  | H19                                                                | 44 MHz OSC Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PCI Interfa   |              | 1   | 1.10.010.10                                                        | Dor II                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AD31-0        | T/S          | *X  | ,C8,B8,C4,<br>B3,A3,C2,D<br>3,C1,G1,H3,<br>J3,V2,V1,V<br>3,W2,V4,w | PCI address and data multiplexed pins. The address phase is the first clock cycle in which FRAMEB is asserted. During the address phase, AD31-0 contains a physical address (32 bits). For I/O, this is a byte address, and for configuration and memory, it is a double-word address. Write data is stable and valid when IRDYB is asserted. Read data is stable and valid when TRDYB is asserted. Data I is transferred during those clocks where both IRDYB and TRDYB are asserted. |

|               |              |     | 3,Y3,W6,Y<br>6,V7,Y14,<br>W14,Y15,Y<br>19,U16,R18<br>,T20,R19      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C/BE3-0       | T/S          | *X  | W20,V19,U<br>17,V20                                                | PCI bus command and byte enables multiplexed pins. During the address phase of a transaction, C/BE3-0 define the bus command. During the data phase, C/BE3-0 are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE0 applies to byte 0, and C/BE3 applies to byte 3.                                                                                                                                |

| CLK           | О            | *X  | N19                                                                | PCI clock: This clock input provides timing for all PCI transactions and is input to the PCI device.                                                                                                                                                                                                                                                                                                                                                                                   |

| DEVSELB       | S/T/<br>S    | *X  | Р3                                                                 | Device Select: As a bus master, the RTL8181 samples this signal to insure that a PCI target recognizes the destination address for the data transfer.                                                                                                                                                                                                                                                                                                                                  |

| FRAMEB        | S/T/<br>S    | *X  | N20                                                                | Cycle Frame: As a bus master, this pin indicates the beginning and duration of an access. FRAMEB is asserted low to indicate the start of a bus transaction. While FRAMEB is asserted, data transfer continues. When FRAMEB is deasserted, the transaction is in the final data phase.  As a target, the device monitors this signal before decoding the address to check                                                                                                              |

| CNED          | TI/C         | *** | 1120                                                               | if the current transaction is addressed to it.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GNTB          | T/S          | *X  | H20                                                                | Grant:Grant indicate to the agent that access to the bus has been granted.                                                                                                                                                                                                                                                                                                                                                                                                             |

| REQB          | T/S          | *X  | J18                                                                | Request: Request indicates to the arbiter that this agent desires use of the bus.                                                                                                                                                                                                                                                                                                                                                                                                      |

| IDSEL         | O            | *X  | A16                                                                | Initialization Device Select: This pin is used as a chip select during configuration read and write transactions                                                                                                                                                                                                                                                                                                                                                                       |

| INTAB         | O/D          | *X  | A17                                                                | Interrupt A: Used to request an interrupt. It is asserted low when an interrupt condition occurs, as defined by the Interrupt Status, Interrupt Mask.                                                                                                                                                                                                                                                                                                                                  |

| IRDYB         | S/T/<br>S    | *X  | M18                                                                | Initiator Ready: This indicates the initiating agent's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                                                  |

|               |              |     |                                                                    | As a bus master, this signal will be asserted low when the RTL8181 is ready to                                                                                                                                                                                                                                                                                                                                                                                                         |

| ww.DataShee                  | et4U.c    | om                            |                                             | complete the current data phase transaction. This signal is used in conjunction with the TRDYB signal. Data transaction takes place at the rising edge of CLK                                                                                                                                                                       |

|------------------------------|-----------|-------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |           |                               |                                             | when both IRDYB and TRDYB are asserted low. As a target, this signal indicates that the master has put data on the bus.                                                                                                                                                                                                             |

| TRDYB                        | S/T/      | *X                            | J19                                         | Target Ready: This indicates the target agent's ability to complete the current phase of the transaction.                                                                                                                                                                                                                           |

|                              |           |                               |                                             | As a bus master, this signal indicates that the target is ready for the data during                                                                                                                                                                                                                                                 |

|                              |           |                               |                                             | write operations and with the data during read operations. As a target, this signal                                                                                                                                                                                                                                                 |

|                              |           |                               |                                             | will be asserted low when the (slave) device is ready to complete the current data phase transaction. This signal is used in conjunction with the IRDYB signal. Data transaction takes place at the rising edge of CLK when both IRDYB and TRDYB are asserted low.                                                                  |

| PAR                          | T/S       | *X                            | R2                                          | Parity: This signal indicates even parity across AD31-0 and C/BE3-0 including                                                                                                                                                                                                                                                       |

|                              |           |                               |                                             | the PAR pin. PAR is stable and valid one clock after each address phase. For data phase, PAR is stable and valid one clock after either IRDYB is asserted on a write transaction or TRDYB is asserted on a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase. As |

|                              |           |                               |                                             | a bus master, PAR is asserted during address and write data phases. As a target,                                                                                                                                                                                                                                                    |

| STOPB                        | S/T/      | *X                            | B16                                         | PAR is asserted during read data phases.  Stop: Indicates that the current target is requesting the master to stop the current                                                                                                                                                                                                      |

| STOPB                        | S/1/<br>S | "A                            | B10                                         | transaction.                                                                                                                                                                                                                                                                                                                        |

| RSTB                         | О         | *X                            | B15                                         | Reset: Active low signal to reset the PCI device.                                                                                                                                                                                                                                                                                   |

| MII Interfa                  | ace       |                               |                                             |                                                                                                                                                                                                                                                                                                                                     |

| LTXC,<br>WTXC                | Ι         | 53,31                         | Y20<br>W11                                  | TXC is a continuous clock that provides a timing reference for the transfer of TXD[3:0], TXE. In MII mode, it uses the 25 MHz or 2.5 MHz supplied by the external PMD device.                                                                                                                                                       |

| LTXEN,<br>WTXEN              | О         | 59,37                         | T17                                         | Indicates the presence of valid nibble data on TXD[3:0].                                                                                                                                                                                                                                                                            |

| LTXD[3-0]<br>, WTXD<br>[3-0] | О         | 57,56,55,54<br>35,34,33,32    | V18,V17,W<br>19,W18<br>V12,Y13,W<br>12,Y12  | Four parallel transmit data lines which are driven synchronous to the TXC for transmission by the external physical layer chip.                                                                                                                                                                                                     |

| LRXC,<br>WRXC                | I         | 51,29                         | W17,V11                                     | This is a continuous clock that is recovered from the incoming data. MRXC is 25MHz in 100Mbps and 2.5Mhz in 10Mbs.                                                                                                                                                                                                                  |

| LCOL,<br>WCOL                | Ι         | 60,38                         | U18,V13                                     | This signal is asserted high synchronously by the external physical unit upon detection of a collision on the medium. It will remain asserted as long as the collision condition persists.                                                                                                                                          |

| LRXDV,<br>WRXDV              | I         | 43,44                         | W16,W9                                      | Data valid is asserted by an external PHY when receive data is present on the RXD[3:0] lines, and it is deasserted at the end of the packet. This signal is valid on the rising of the RXC.                                                                                                                                         |

| LRXD[3-0],<br>WRXD[3-<br>0]  | I         | 50,49,47,46<br>27,26,24,23    | V15,V16,Y<br>18,Y17,Y11<br>,W10,V10,<br>Y10 | This is a group of 4 data signals aligned on nibble boundaries which are driven synchronous to the RXC by the external physical unit                                                                                                                                                                                                |

| LRXER,<br>WRXER              | Ι         | 44,22                         | V14,V9                                      | This pin is asserted to indicate that invalid symbol has been detected in 100Mbps MII mode. This signal is synchronized to RXC and can be asserted for a minimum of one receive clock.                                                                                                                                              |

| LMDC,<br>WMDC                | О         | 40,18                         | W15,W8                                      | Management Data Clock: This pin provides a clock synchronous to MDIO, which may be asynchronous to the transmit TXC and receive RXC clocks.                                                                                                                                                                                         |

| LMDIO,<br>WMDIO              | I/O       | 41,19                         | Y16,Y9                                      | Management Data Input/Output: This pin provides the bi-directional signal used to transfer management information.                                                                                                                                                                                                                  |

| GPIO                         | II/0      | 205 206 205                   | 111 110 110                                 | Consultation 1/O single and P. 114 O ICIOPOIS 43                                                                                                                                                                                                                                                                                    |

| GPIOB[11-<br>0]              | 1/0       | 205,206,207,<br>2,3,5,6,8,9,1 | U1,U2,U3,<br>W1,Y1,Y2,                      | General purpose I/O pins group B pins 11 to 0. If ICFG[5-4] power on latch =[1-0]. GPIO[5-2] mapping to JTAG_TDO(JTAG test data                                                                                                                                                                                                     |

| OJ                           |           | 1,12,13                       | W4,V5,Y4,                                   | output),JTAG_TRSTN(JTAG reset),JTAG_TMS(JTAG test mode                                                                                                                                                                                                                                                                              |

| CDICDII                      | 1/0       | 200 201 202                   | W5,V6,Y5                                    | select),JTAG_TDI(JTAG test data input).                                                                                                                                                                                                                                                                                             |

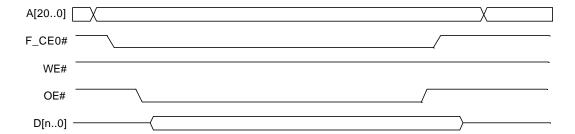

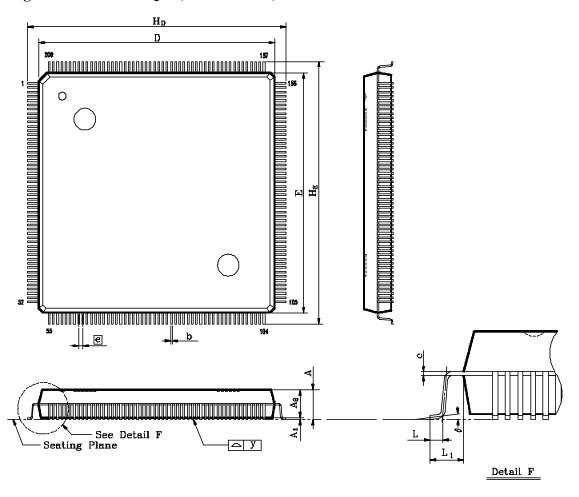

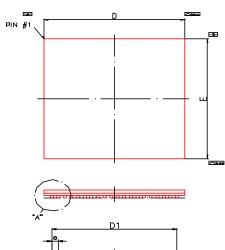

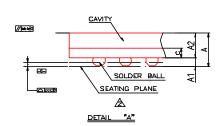

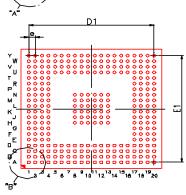

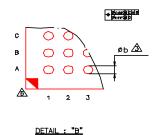

| GPIOB[15<br>-12]             | 1/0       | 200,201,202,<br>203           | R1,T1,T2,T                                  | General purpose I/O pins group B pin 15 to 12.                                                                                                                                                                                                                                                                                      |