# **Analog and Interface Guide – Volume 2**

A Compilation of Technical Articles and Design Notes

# **Contents**

| Techniques To Minimize Noise                                                       |    |

|------------------------------------------------------------------------------------|----|

| Looking Forward To Technology Migration                                            | 1  |

| Bypass Capacitors: No Black Magic Here                                             | 2  |

| The Debounce Debacle                                                               | 3  |

| ETP-248: Managing Power, Ground And Noise In Microcontroller/Analog Applications   |    |

| Charging Lithium Batteries                                                         |    |

| Charging High Capacity Lithium Batteries                                           | 8  |

| Charging Lithium-Ion Batteries: Not All Charging Systems Are Created Equal         | 10 |

| Operational Amplifiers                                                             |    |

| Working Your Amplifier Inside The Single-supply Voltage Box                        | 14 |

| Every Amplifier Is Waiting To Oscillate And Every Oscillator Is Waiting To Amplify | 18 |

| Amplifiers And The SPICE Of Life                                                   | 22 |

| Analog-to-Digital Converters                                                       |    |

| The Number Of Bits vs LSB Errors                                                   | 24 |

| Is Your Converter Accurate – Part 2                                                | 25 |

| Sometimes Noise Can Be Good                                                        | 26 |

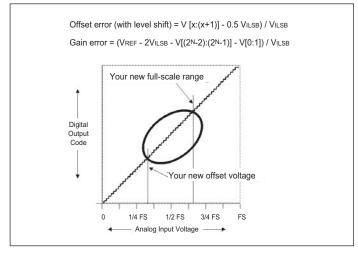

| Using The Basics For ACD Range Control                                             | 27 |

| Turning Nyquist Upside Down By Undersampling                                       | 28 |

| Miscellaneous                                                                      |    |

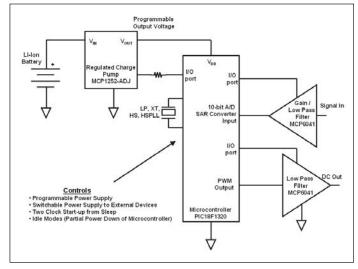

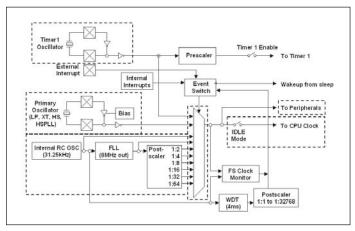

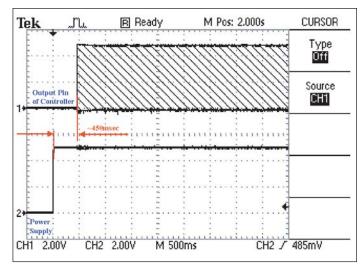

| Arming Yourself With nanoWatt Technology Techniques                                | 29 |

| Muxing Your Micro With Style                                                       | 32 |

| Riding The Crest Factor Wave                                                       | 33 |

| Designing With Low Dropout Regulators In Embedded Applications                     | 34 |

# **Looking Forward To Technology Migration**

By Bonnie C. Baker, Microchip Technology Inc.

The industry is laying the groundwork as we speak. The geometries of digital and analog integrated circuit silicon processes are shrinking. As a consequent, IC devices continue to have lower power-supply voltage requirements, silicon areas and prices. I personally have witnessed geometry migration from 1.2 microns all the way down to 0.25 microns. I am finding that a device function manufactured with a 0.7 micron process may not work as well if I change to a 0.25 micron process.

What is that all about?! I theoretically haven't changed anything,

but it appears that my circuits present an argument to the contrary. Of course, I have the option of not selecting devices that have migrated to smaller geometries, which is a very bad idea for a forward-thinking engineer. By not participating in this industry trend. I turn down the added benefits of lower powersupply voltages, faster speeds and lower cost. Not very smart! My only line of defense is to design with the expectation that geometries are going to continue to get smaller. I know that smaller geometry devices are able to support lower power-supply voltages. This helps me with my power consumption issues, but ESD (electrostatic discharge) is less than optimum. Not only are smaller geometry devices less able to absorb high-voltage transients, but they lack robustness around high currents. The manufacture's standards are as high as ever with a 2000 Vrms to 4000 Vrms ESD tolerance (Human Body Model). However, their tests look for catastrophic failures while the end user can experience RAM contamination because of EMI (electromagnetic interference) and EFT (electrical fast transients) signals.

However, there are several areas that I can focus on, such as protection circuits (MOVs, transient suppressors), microcontroller or processor pin protection (I/O, interrupt, reset pins), or firmware recovery techniques (WDT, register refresh), etc. All of these techniques help produce a robust design, but I get the biggest bang-for-the-buck when I optimize my layout.

If you want to join this smaller-geometry migration wave, look for places in your layout where spikes and glitches can enter your, soon to be, sensitive circuits. A great place is to look at the power-supply traces. In a typical circuit, buck or boost converters generate the power-supply signals. On top of this type of noisy supply, your can receive EFT on top of the power voltages. This EFT will manifest itself as voltage or current spikes. Remember, with higher order geometry designs the circuit works just fine in your current layout. A general rule of thumb going forward is to minimize these effects by managing your power and ground traces (or planes). Finally, your circuit has always required decouple or bypass capacitors, but now the proper selection is critical.

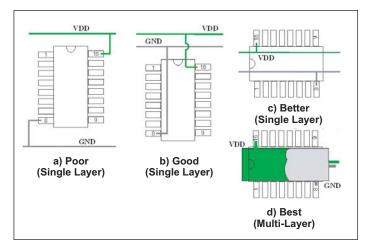

Figure 1 illustrates a few examples of what to do and not do.

**Figure 1:** Connecting several devices with one ground and VDD trace, (a) can became a candidate for ground and power-supply loops. This topology also enhances power-supply glitches. Having ground or VDD jumper (b) is a better solution but not great. Creating a ground and VDD trace from device to device is a better solution (c) between the three. However, the best solution is to have separate ground and power-supply planes (d) in a multi-layer board.

You have probably heard all of these suggestions before and a multitude of other useful hints beyond this short column. If so, that is a good sign. Since you're a descent engineer, you probably have discovered what you need and don't need in your circuit. I congratulate you. But, change is in the wind. As you move into new silicon geometries, you need to implement those seemingly ancient layout rules. Optimize your layout with power glitches in mind. Add protection circuits such as MOVs and transient suppressors. Protect the I/O, interrupt and reset pins of your controller or processor. Use firmware recovery techniques such as WDT or register refresh so they contain the correct values. All of these techniques will foster the production of a robust design.

# **Bypass Capacitors: No Black Magic Here**

By Bonnie C. Baker, Microchip Technology Inc.

A basic requirement for all electronic circuits is the inclusion of bypass capacitors (also know as decoupling capacitors). These devices reside across the positive supply to ground, as close to the supply pin of the active device as possible. You may get away with excluding these capacitors in low-frequency circuits, but more than not, low-frequency circuits actually have high-frequency entities inside the active devices. An example of a supposed "low-frequency device" is a microcontroller that uses a low-frequency system clock. Granted, the frequency of the clock is slow, but the transition of the internal and I/O gates can occur in nanoseconds. Without proper power-supply filtering, these rising and falling glitches will traverse the circuit. The first step to proper supply filtering is to include a proper-valued, bypass capacitor.

Circuits containing digital devices are not the only systems that require bypass capacitors. Analog devices also benefit from the inclusion of bypass capacitors, but in another way. While bypass capacitors in digital systems control fast rising- and falling-time glitches from the device, bypass capacitors in analog systems assist in preventing power-supply noise from entering the analog device. Typically, analog devices have preventative power-supply filtering built-in, primarily known as power-supply or line-rejection capability. These power-supply rejection (PSR), noise-rejection mechanisms are effective at reducing low-frequency power-supply noise, but this is not the case at higher frequencies.

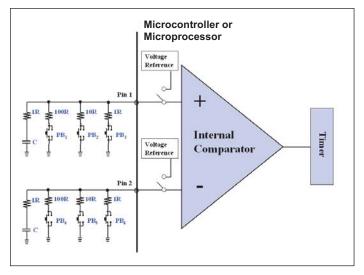

Once you resign to your fate of including bypass capacitors in your circuit, the re-aiming task is to select the right capacitor value for the various devices in your circuit. Typically, manufacturers will include suggested bypass capacitor values in their data sheets. If the manufacturer does not supply that information, you can determine the proper value on your own.

For instance, with microcontrollers or microprocessors you can calculate the bypass capacitor value when you know the typical rise and fall times of signals from your device (trise). You also need the average current while the microcontroller or microprocessor is operating (IAVE). These two quantities are in the microcontroller/microprocessor product data sheet tables. You finally need to define the maximum voltage ripple-noise that you can tolerate on your power-supply trace (VRIPPLE).

Using these values, the appropriate value for the bypass capacitor is:

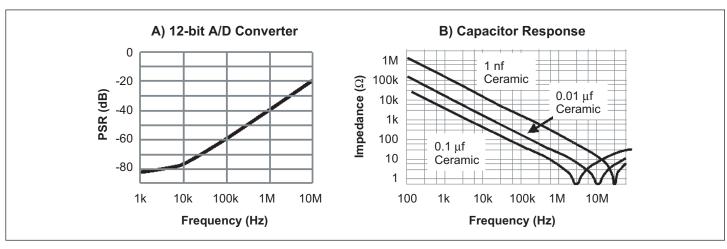

Analog devices are a benefit in another way. With these kinds of circuits, you need to find the frequency where power-supply noise will affect your circuit. The best place to look to find this information is with the PSR or line-rejection performance over frequency graphs in the product data sheet. Additionally, you need to determine the minimum, acceptable noise that you can tolerate. For instance, with a 12-bit A/D converter you can tolerate un-rejected power-supply noise of approximately  $\pm\,^{1}\!\!/_{4}$  Least Significant Bytes (LSB), for true 12-bit performance. You also need to take a stab at estimating the power-supply, noise-voltage magnitude. With these two parameters, you can refer to the typical PSR versus frequency curve in the manufacturer's data sheet.

For example, Figure 1A provides the PSR over frequency curve of a 12-bit A/D converter. The PSR of this converter is equal to:

PSR = 20 log (Vpower-supply-ripple / Vadc-error)

If you determine that the noise level riding on top of your converter power supply is  $\pm 20$  mV (or 40 mV peak) and the allowed error is  $\pm$   $^{1}\!\!\!/ \Delta$  LSB or 0.61 mV peak (implying 5V full scale range), the noise from the power supply will show up in the output code of the converter as noise as –36.33 dB. This occurs per Figure 1A at approximately 5 MHz. Referring to Figure 1B, the appropriate bypass, ceramic capacitor value for this converter would be between 0.1  $\mu F$  and 0.01  $\mu F$ .

It is advantageous to note that these calculations use typical values instead of the minimum or maximum numbers. This is important to understand, because selecting the correct bypass capacitor is not an exact science. Not only will devices vary slightly from part to part, the capacitors that you use in your circuit will also vary from part to part as well as over temperature. But, don't let this deter you from using bypass capacitors. The worst of all cases is when you use none.

**Figure 1:** Using the PSR versus over temperature of an analog part (A) in combination with the ceramic capacitor impedance versus frequency (B) determines the best bypass capacitor for analog parts.

# The Debounce Debacle

By Bonnie C. Baker, Microchip Technology Inc.

Mechanical switches play an important role in many microcontroller and microprocessor applications. These types of switches are simple, inexpensive and easy to install. But, the perceived simplicity of mechanical switches can be deceiving if you intend to keep your user happy. For instance, an annoying, poor switch implementation is a TV button that advances the channel two or three channels higher instead of the intended one-channel advance. More critically, a switch sensor could determine the status of a door. An open door trips an alarm or motivates an attendant to go to the site. False alarms can be disruptive and expensive. Some switches reside in time-critical environments, like in keyboards where a quick, accurate determination of the switch position is critical.

It is easy to blame these problems on the switch, instead of the electronics that sense the switch position. An alternative approach is to examine the dynamic characteristics of your switch and assess its environmental influences. All switches demonstrate a switch contact, "bouncing" action as the switch opens or closes. The switch contacts actually bounce off of each other several times before the contacts settle to their final position. If the switch position is sensitive to the touch, a person who had too much coffee could cause a bouncing action to occur as a result of human touch. Switch manufacturers call this "playing" with the switch. You also need to look at environmental interference, such as vibrations or electromagnetic interference (EMI). Once you've evaluated these system dynamics, you are ready to design the electronics in your circuit.

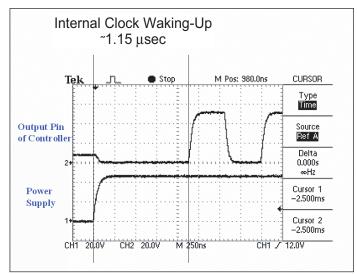

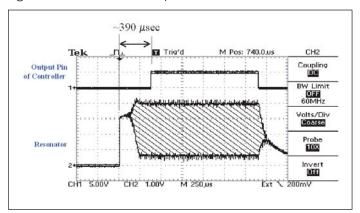

You can implement the switch-interface electronics using an analog or digital solution. The analog solution uses an R/C filter to control the bouncing signal. A digital gate, with hysteresis, takes the output of the R/C filter and sends the switch-position signal into the microcontroller or microprocessor. In this type of system, the bounce time is assumed slower than the R/C time constant. You are probably safe if you design with a 500 ms switch closure time. But, don't hesitate to verify this timing with your switch on the bench. You will find that switches bounce less as they open as compared to when they close. In this configuration, the microcontroller or microprocessor receives the switch position after the fact.

An alternative to the analog solution is a purely digital one. A digital solution is "almost" free because you no longer need your external components. The analog option has the additional cost of materials, installation and board real estate. The pure digital solution can immediately determine if the switch has changed. The microcontroller or microprocessor can then filter the switch bounce digitally. This debounce circuit can be thought of as a low-pass/decimation filter. The "brute-force debounce" digital solution uses a programmed delay time in firmware to replace the analog R/C time constant.

As an alternative, it is possible to adjust this programmed delay time by using clever programming techniques. This type of algorithm increments a counter when the switch output signal is high and decrements the same counter when the switch output is low. By taking multiple samples, the counter will over range either high or low, which identifies the switch state. The programmer determines the number of and timing between samples. The timing of the samples should not correlate to the main frequency of microcontroller or microprocessor clocks.

Some say the attention to issues surrounding a switch's open and closure action is a lost art. If this is so, evaluating all the elements of your system is a lost art as well. Electronic systems in the real world usually have a switch somewhere in the circuit. The opening or closing of a switch seldom demonstrates a clean transition. The connection consists of a series of "breaks" and "makes" before the final "make" (or "break"). This bouncing-phenomena can occur several to hundreds of times before things settle. The best, cost-effective solution comes from using the microcontroller/microprocessor approach. You can change your design as you experiment, or on the fly at next to no cost.

### References

"My Favorite Software Debouncers", Jack Ganssle, Embedded Systems Programming Magazine, 6-16-04.

"PICkit™ 1 Flash Starter Kit, User's Guide", Microchip Technology Inc., DS40051.

"Examining Switch-Debounce Circuits", Ron Mancini, EDN, Feb. 21, 2002.

# ETP-248: Managing Power, Ground And Noise In Microcontroller/Analog Applications

By Bonnie C. Baker and Keith Curtis, Microchip Technology Inc.

Microcontroller applications often have low-level sensor signals and moderate power-drive circuitry, in addition to the microcontrollers. A peaceful coexistence with these three extremes requires a careful power and ground distribution design. This paper will discuss sources of noise and the paths by which the noise travels. We will cover the theory behind good layout practices and their impact on noise. We will also discuss the proper selection and placement of noise isolating and limiting components. Any designer who struggles to keep digital and power noise out of sensitive input circuits will find this paper useful.

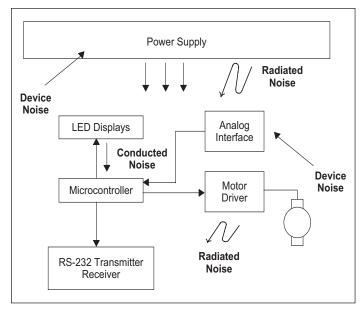

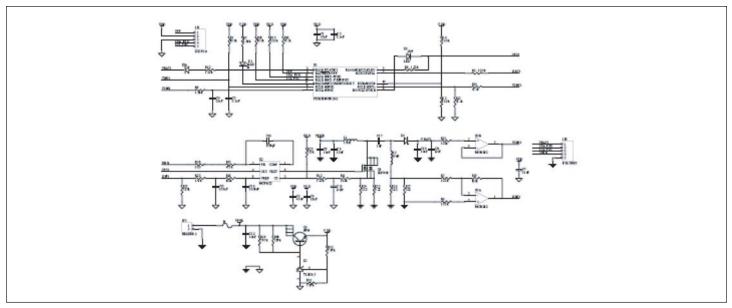

Figure 1 shows a block diagram of the example system that we will use to the discuss concepts in this paper. The overall function of this system is to acquire weight and display the results in an LED array, as well as on a laptop computer. Additionally, a fan controller cools the board temperature as needed.

In the example design, there is an analog and digital section. One of the difficulties in this design is the segregation of these two domains. Starting with the analog input to the circuit, the design is capable of measuring weight. The analog interface block in Figure 1 includes a load cell, gain block, anti-aliasing filter and a 12-bit analog-to-digital converter (ADC). The load cell is a weatstone bridge, as shown in Figure 2.

**Figure 1:** This block diagram models the circuit, along with noise sources, of the system in this paper. The analog interface circuitry measures weight with a load-cell sensor. The interface then transmits those results to a microcontroller. The microcontroller sends the sensor results to an LED display and laptop computer. There is also circuitry for a fan-motor driver.

In the digital section, the microcontroller produces the digital representation of the load-cell value. One of the activities of the microcontroller is to display the measurement results in the LED array. The microcontroller also uses an RS-232 interface port to communicate the data to a desktop computer. The desktop computer takes analog measurements from the microcontroller and displays that data in a histogram chart. Finally, the digital section also includes a PWM driver output for the fan.

This design includes sensitive analog circuitry, a high-power LED display and a potentially noisy digital interface to a laptop computer. The challenge is to design a circuit and layout that allows the coexistence of all of these conflicting elements. We will start by designing the analog section of this circuit and then move on to layout concerns.

## **Analog Circuit Design**

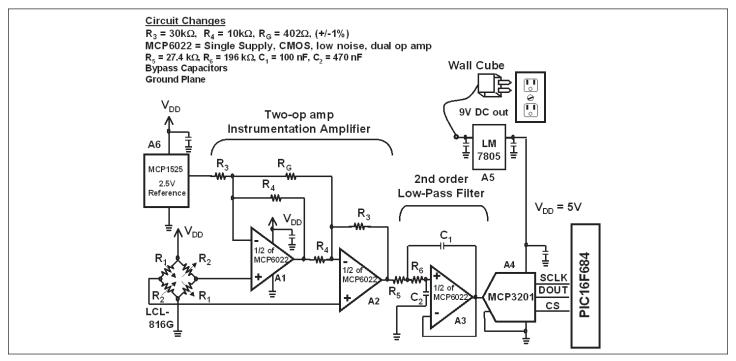

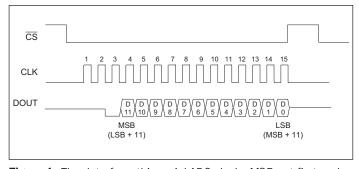

The analog portion of this circuit has a load-cell sensor, dual operational amplifier (MCP6022, Microchip Technology Incorporated) configured as an instrumentation amplifier, a 12-bit 100 kHz SAR ADC (MCP3201, Microchip) and one voltage reference. The ADC's SPI™ port connects directly to a microcontroller (see Figure 2).

The load-cell sensor has a full-scale output range of  $\pm 10$  mV. The gain of the instrumentation amplifier (A1 and A2) is 153 V/V. This gain matches the full-scale output swing of the instrumentation amplifier block to the full-scale input range of the ADC. The SAR ADC has an internal input sampling mechanism. With this function, each conversion uses a single sample. The microcontroller acquires the data from the converter and translates the data into a usable format for tasks such as the LED display or the PC interface.

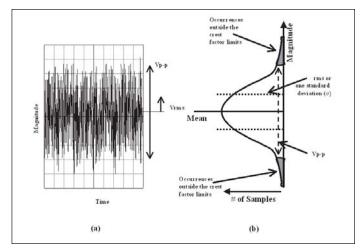

If the implementation of the circuit and layout design of this system is poor (no ground plane, no bypass capacitors and no anti-aliasing filter), it will be an excellent candidate for noise problems. The symptom of a poor implementation is an intolerable level of uncertainty about the digital output results from the ADC. It is easy to assume that this type of symptom indicates that the last device in the signal chain generates the noise problem. But, in fact, the root cause of poor conversion results originates with the PCB layout.

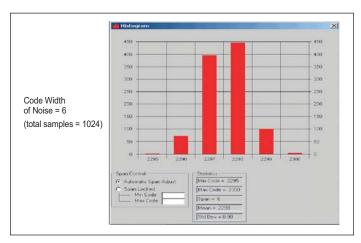

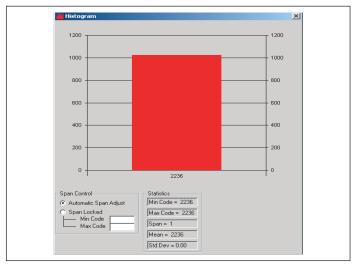

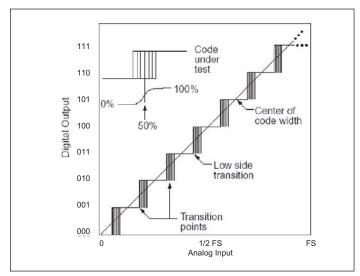

In the worst of circumstances, when noise reduction layout precautions are not taken, the 12-bit system in Figure 2 will output a large distribution of code for a DC input signal. Figure 3 shows data from the output of the converter.

The data in Figure 3 is far from optimum. Six bits of peak-to-peak error changes the 12-bit converter system into a noise-free 9.3-bit system. One can average this data in the digital domain to recapture the full 12-bits, but this will ideally require the averaging of 4  $^{(12-9.3)}$  or 36 samples. In a non-ideal environment, it will be more.

**Figure 2:** This is the analog portion of the block diagram in Figure 1. The amplifiers and voltage reference tie into the ADC, and the ADC ties to the microcontroller. Building a 2nd order, low-pass filter (A3) requires two resistors, two capacitors and the MCP6022 (Microchip) operational amplifier. The other amplifiers form an instrumentation amplifier circuit. Bypass capacitors are included. For testing, this portion of the circuit is powered from a 110 VAC to 9 VDC wall cube. A linear regulator converts the 9V output of the wall-cube to 5 VDC.

**Figure 3:** A poor implementation of the 12-bit data acquisition system shown in Figure 2 could easily have an output range of six different codes with a 1024 sample size.

## **Analog Layout Guidelines**

Ground and Power-Supply Strategy: The implementation for the layout of the ground plane is critical when designing low-noise solutions. It is a dangerous practice to omit a ground plane with analog and/or mixed signal devices. Ground planes solve problems such as offset errors, gain errors and noisy circuits. These errors are more prevalent when the layout lacks a ground plane because analog signals typically refer to ground.

When determining the grounding strategy of a board, one should determine if the circuit needs one or more ground planes. If the circuit has a "minimum" amount of digital circuitry onboard, a single ground plane and triple-wide power supply traces may be appropriate. The danger of connecting the digital and analog ground planes together is that the analog circuitry picks-up the noise from the digital return currents. In either case, one should connect the analog grounds, digital grounds and power supplies together at one or more points on the circuit board. The inclusion of a ground plane in a 12-bit system is critical.

ADC Layout Strategies: ADC layout techniques vary with converter technology. When SAR ADCs are used, the entire device should reside on the analog power and ground planes. ADC vendors often supply analog and digital ground pins. If high-resolution SAR converters are used, a digital buffer should be used to isolate the converter from bus activity on the digital side of the circuit. This is the correct strategy to use for delta-sigma ADCs as well.

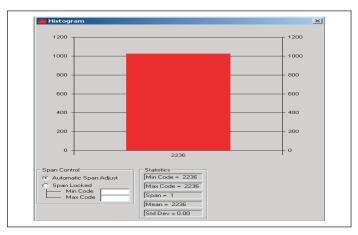

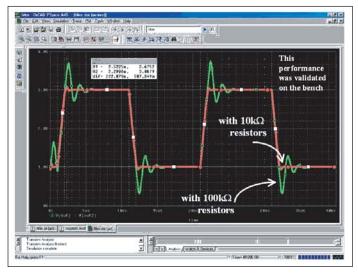

Figure 4 shows the performance of a board laid out with these considerations. This data shows that the analog section of this circuit works extremely well.

**Figure 4:** This figure shows the data results from the circuit design in Figure 2. The improvement indicates that our low-noise layout strategies are effective.

## **Analog Design Conclusion**

Concluding this first section, it is important from the beginning of the design to verify that the circuit devices are low noise. In this example, the key elements are the resistors and amplifiers. Following the device selection, make sure that the signal path is properly filtered. This includes the signal path as well as the power-supply train. An uninterrupted ground plane is a critical element in all analog designs. You will eliminate noise that you might otherwise have problems tracking down. Finally, bypass capacitors are critical in analog designs. When you install them, place the capacitors with short leads as close to the power pins as possible.

At this point, the analog design is deemed "good". However, you will see that the addition of the LED array and fan controller will cause the performance of the analog section to become worse.

### **Digital Design**

We will start with the first-pass digital/analog design integration. In the first pass, we will add the digital section arbitrarily using normal rules of thumb for a layout strategy. This portion of the design adds the LEDs, motor driver, RS-232 transmitter/receiver and microcontroller.

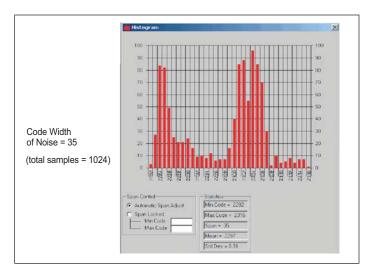

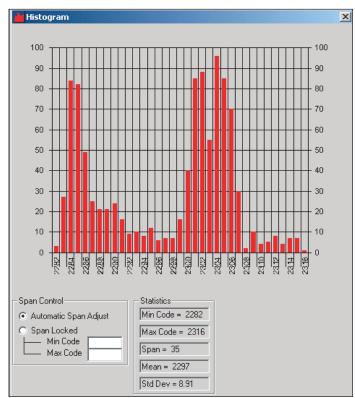

The design uses bypass capacitors and a flyback diode on the motor drive. Bypass capacitors are kept near the IC power, and the ground traces are short. This is done without changing the analog circuit layout. Figure 5 shows the first-pass histogram results from digital/analog layout.

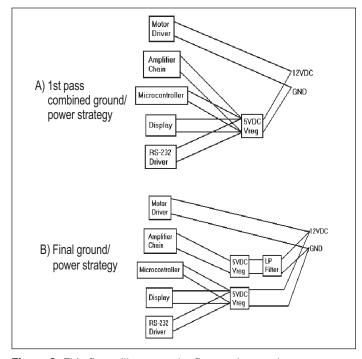

The results of the ADC output from this new board are worse than the first try at the analog section. We are going to recover the original analog behavior by reworking the power and ground strategy. The first corrective action is to separate the digital portions of the power train from the analog portion. Figure 6A shows the first attempt with the analog/digital combination. Figure 6B reflects the second, more successful version.

**Figure 5:** The digital circuit corrupts the analog section, causing a code width of 35 codes from 1024 samples. This data (the output of the ADC) indicates that there are noise sources on the board because of the two features in the data. The results from this data would be difficult to digitally filter to one final ADC code.

**Figure 6:** This figure illustrates the first- and second-pass strategies for power and ground. Note that the second pass separates noisy and sensitive circuitry as much as possible.

The first analog/digital layout routed the digital 5V and ground connections through the analog section. In this configuration, the LED high currents, motor switching and digital controller noise is overlaid onto the sensitive analog power and ground paths (Figure 6A). The pathways for noise in the PCB traces are the power and ground currents interacting with trace resistance and inductance. This produces AC offsets in both the power and ground of the analog portion of the circuit. A quick solution to this problem is to reroute the power and ground traces so that the analog and digital lines are independent, up to a central location. At this central location, they are connected (Figure 6B). This strategy takes advantage of trace resistance, inductance and bypass capacitors to create RC and LC low-pass filters on the power and ground traces. This further isolates noisy and sensitive sections of the design.

Key candidates for radiated noise are the LED traces (that carry high currents), the charge pump in the RS-232 interface (which can pull moderate currents) and the I/Os from the microcontroller (which have fast rise times). The LED and RS-232 driver traces inductively couple noise to adjacent traces in close proximity on the board. This action manifests itself as voltage noise. Fast rise-time signals from the microcontroller capacitively couple into high-impedance, sensitive traces. This coupling activity manifests itself as current noise if traces are in close proximity.

If these factors are considered in the circuit layout, the noise coupled from the noisy digital to the sensitive analog is reduced. The new layout for analog circuitry remains unchanged, as does most of the digital. The difference is that the LED traces now go around the analog block rather than through it. The RS-232 interface's power supply and ground are also kept separate from the sensitive analog and digital functions on the board. And, the power and ground strategy from Figure 6B is used to guide the layout.

**Figure 7:** Testing the new layout shows that the changes are effective. 1024 samples where collected. The board exhibits true 12-bit operation.

### Conclusion

The first step to analog noise reduction is to choose low-noise analog parts. One can remove signal and power noise with filters. Use an anti-aliasing filter as appropriate. In the power bus, use bypass capacitors and inductive chokes as needed. Also, implement the PCB solution with a ground plane.

When you add digital circuitry, develop a ground and power strategy for the entire circuit. In the plan, consider the resistance and inductance of the traces in conjunction with the current density traveling through those paths. The objective in the composite layout is to minimize noise pathways, such as capacitive and inductive coupling between traces, and to use the inductance and resistance of the trace, together with the bypass capacitors, to reduce and isolate noise.

### References

"High-Speed Digital Design: A Handbook of Black Magic", Howard Johnson, Martin Graham, Prentice Hall, 1993.

"Noise Reduction Techniques in Electronic Systems", Henry Ott, John Wiley, N.Y., 1998.

"The RF Capacitor Handbook", American Technical Ceramics Inc.

"The Circuit Designer's Companion", Tim Williams.

"Reference Data for Engineers", 7th edition, Edward C. Jordan, Editor-in-chief.

"ABC's of Transformers & Coils", Edward J. Bukstein.

"Techniques that Reduce System Noise in ADC Circuits", Bonnie C. Baker, ADNO07, Microchip Technology Inc.

Anti-Aliasing, Analog Filters for Data Acquisition Systems", Bonnie C. Baker, AN699, Microchip Technology Inc.p

"Interfacing Pressure Sensors to Microchip's Analog Peripherals", Bonnie C. Baker, AN695, Microchip Technology Inc.

"Layout Tips for 12-Bit A/D Converter Applications", Bonnie C. Baker, AN688, Microchip Technology Inc.

"Analog Design in a Digital World using Mixed-Signal Controllers", Keith Curtis, AN823, Microchip Technology Inc.

FilterLab® Active Filter Design Software, www.microchip.com

# **Charging High Capacity Lithium Batteries**

By George Paparrizos, Microchip Technology Inc.

New portable electronic designs are continuously improving system performance. Designers are adding new features, and the power requirements of these systems are increasing along with their performance. This trend has resulted in the development of Lithium Ion (Li-Ion) battery packs with significantly higher capacities that can provide adequate system run times. Li-Ion batteries have emerged to be the power source of choice for most portable consumer applications. They provide many advantages over other battery types, such as higher energy density and cell voltages. However, as the available battery capacity increases to address today's growing power demands, consumer requirements for shorter battery-charge cycles and smaller physical size are also increasing. Meeting those requirements becomes a major design challenge.

The preferred charging rate for a Li-Ion or Li-Polymer battery pack is 1C, which means that a 1000 mAh battery pack has a preferred fast-charge current of 1A. Charging at this rate provides the shortest charge-cycle times without degradation to the battery-pack performance or its life. To achieve the preferred charging rate while utilizing battery cells with increasingly higher capacity, a higher charge-current level is inevitable. This leads to major design challenges, the most important of which is the heat generated in the charge-management controller IC as well as on the system board. To address these issues, a more careful thermal design is necessary. As shown below, integrating the pass transistor, which dissipates most of the heat, on the charge management IC, becomes, in many cases, a limiting factor for the design performance and operating range.

The power dissipation of a linear-battery charger, the most popular type for 1- and 2-cell Lithium-based applications, can be calculated as follows:

PD = (VDD - VBATTERY) x ICHARGE

With:

PD: power dissipation

VDD: input (adapter) voltage

VBATTERY: battery voltage

ICHARGE: fast charge current

The above formula indicates that a worst-case scenario exists when the input-voltage to battery-voltage differential and the charge current are high. We calculate the power dissipation for a typical scenario, in which the car or wall adapter provides a 5V  $\pm 10$  percent supply voltage, the battery voltage is 3.0V and the fast-charge current is 1A. (i.e., 1C charging rate for a 1000 mAh battery) In this case, the power dissipation is calculated to:

$$PD = (5.5V - 3.0V) \times 1A = 2.5W$$

Table 1 shows the maximum operating ambient temperature assuming a 2.5W power-dissipation scenario, and a maximum junction temperature of 125°C, for some of the most popular package options in the industry.

| Package<br>Type | Thermal Resistance (°C/W)* | Max. Ambient<br>Temperature (°C) |

|-----------------|----------------------------|----------------------------------|

| MSOP-8          | 206                        | -391                             |

| SOIC-8          | 163                        | -283                             |

| MSOP-10         | 113                        | -158                             |

| SOT-23-6        | 96                         | -114                             |

| 3x3 DFN-8       | 52                         | -5                               |

| Power SOIC-8    | 43                         | 18                               |

| 4x4 QFN-16      | 38                         | 30                               |

| 5x6 DFN-8       | 36                         | 35                               |

**Table 1:** Max. Operating Ambient Temperature (2.5W Power-Dissipation, Max. Junction Temperature 125°C)

It is apparent from these results that the maximum allowable ambient temperature for most of the package types puts significant limitations on the thermal design. Furthermore, achieving some of these operating conditions is not feasible in a real-world situation. The assumptions for conducting these calculations do not take into account worst-case conditions. For example, the battery might have just been preconditioned (i.e. deeply depleted cells) in which case the battery voltage during the beginning of current regulation could be as low as 2.7V. Additionally, after-market adapters that provide a less tight regulation might be utilized, such that the battery charger would accept input voltages significantly higher than 5V. Lastly, as new applications require more power, battery packs with capacities greater than 1000 mAh are becoming increasingly popular.

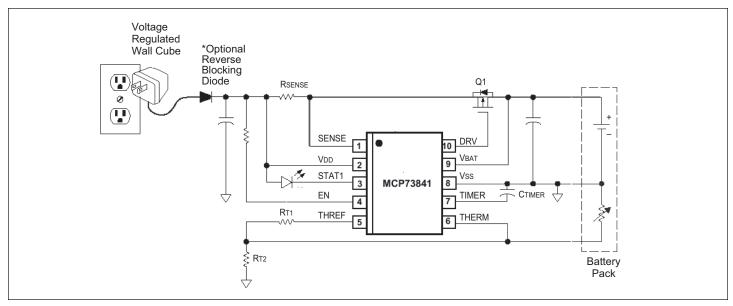

Some battery chargers, like Microchip Technology's MCP7384X, provide the ability to use an external P-channel MOSFET. Discrete MOSFETs can run hotter without reliability concerns. They are offered in a variety of heat-dissipating packages that enable higher allowable power dissipation as well as higher maximum operating ambient temperature. The flexibility of selecting a MOSFET that meets the application's power dissipation and electrical requirements allows for higher system performance and cost optimization. Figure 1 demonstrates a typical circuit for this battery-charger family.

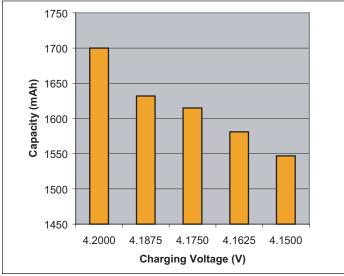

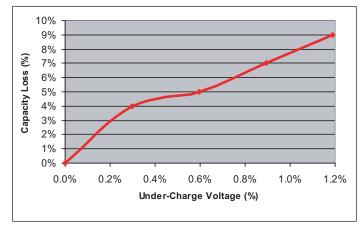

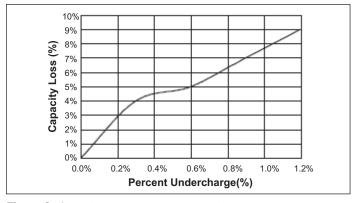

The MCP7384X also offers a  $\pm 0.5$  percent voltage regulation accuracy (max). Since both over- and under-charging the battery reduces its performance and life, it is essential for the charge management controller IC to provide a high-precision voltage to the battery. Exceeding the termination voltage allows for a short-term gain in available battery energy. However, continuous overcharging can result in a significant reduction in cycle life or safety issues. On the other hand, undercharging reduces the battery cell's available capacity, thereby shortening usable battery time; thus, providing a precise regulation voltage maximizes cell capacity utilization and ensures safe operation. Figures 2 and 3 illustrate that a small decrease in voltage accuracy results in a large decrease in battery capacity.

Figure 1: Typical Charging Circuit for High-Capacity Battery Packs.

Figure 2: Battery Capacity vs. Charging Voltage.

When the battery voltage falls below a recharge threshold, the MCP7384X products automatically initiate a new charge cycle. This allows the battery to be kept at near-full charge at all times, making it readily available for utilization at any point of time. The operation also allows for higher reliability, since "trickle-charging" Li-lon batteries for extended periods results in life degradation.

The number of available portable equipment types are expected to increase in the years to come. Extending usable battery life and reducing charge-cycle time are essential for ensuring a positive user experience. Battery manufacturers are already offering new, space-saving Li-lon battery packs with high capacity to meet today's power demands. While high-capacity batteries are able to extend operating life, they also introduce significant design challenges. Addressing both issues requires accurate voltage regulation and the utilization of external-pass transistors that are capable of providing high charge current while ensuring thermal stability.

Figure 3: Battery Capacity Loss vs. Under-Charge Voltage.

# Charging Lithium-Ion Batteries: Not All Charging Systems Are Created Equal

By Scott Dearborn, Microchip Technology Inc.

### Introduction

Powering today's portable world poses many challenges for system designers. The use of batteries as a prime power source is on the rise. As a result, a burden has been placed on the system designer to create sophisticated systems utilizing the battery's full potential.

Each application is unique, but one common theme rings through: *maximize battery capacity usage*. This theme directly relates to how energy is properly restored to rechargeable batteries. No single method is ideal for all applications. An understanding of the charging characteristics of the battery and the application's requirements is essential in order to design an appropriate and reliable battery charging system. Each method has its associated advantages and disadvantages. It is the particular application with its individual requirements that determines which method will be the best to use.

Far too often, the charging system is given low priority, especially in cost-sensitive applications. The quality of the charging system, however, plays a key role in the life and reliability of the battery. In this article, the fundamentals of charging Lithium-Ion (Li-Ion) batteries are explored. In particular, linear charging solutions and a microcontroller-based, switch-mode solution shall be explored. Microchip's MCP73843 and MCP73861 linear charge management controllers and PIC16F684 microcontroller along with a MCP1630 pulse width modulator (PWM), shall be used as examples.

### Li-lon Charging

The rate of charge or discharge is often expressed in relation to the capacity of the battery. This rate is known as the C-Rate. The C-Rate equates to a charge or discharge current and is defined as:

$I = M \times Cn$

where:

I = charge or discharge current, A

M = multiple or fraction of C

C = numerical value of rated capacity, Ah

n = time in hours at which C is declared.

A battery discharging at a C-rate of 1 will deliver its nominal rated capacity in one hour. For example, if the rated capacity is 1000 mAhr, a discharge rate of 1C corresponds to a discharge current of 1000 mA. A rate of C/10 corresponds to a discharge current of 100 mA.

Typically, manufacturers specify the capacity of a battery at a 5 hour rate, n=5. For example, the above-mentioned battery would provide 5 hours of operating time when discharged at a constant current of 200 mA. In theory, the battery would provide 1 hour of operating time when discharged at a constant current of 1000 mA. In practice, however, the operating time will be less than 1 hour due to inefficiencies in the discharge cycle.

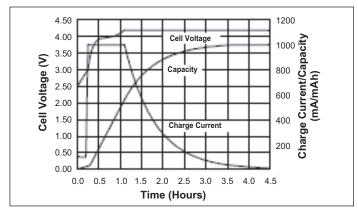

So how is energy properly restored to a Li-Ion battery? The preferred charge algorithm for Li-Ion battery chemistries is a constant, or controlled, current – constant voltage algorithm that can be broken up into four stages: trickle charge, constant current charge, constant voltage charge and charge termination. Refer to Figure 1.

Figure 1: Li-lon Charge Profile.

Stage 1: Trickle Charge – Trickle charge is employed to restore charge to deeply depleted cells. When the cell voltage is below approximately 3V, the cell is charged with a constant current of 0.1C maximum.

Stage 2: Constant Current Charge – After the cell voltage has risen above the trickle charge threshold, the charge current is raised to perform constant current charging. The constant current charge should be in the 0.2C to 1.0C range. The constant current does not need to be precise and semi-constant current is allowed. Often, in linear chargers, the current is ramped-up as the cell voltage rises in order to minimize heat dissipation in the pass transistor.

Charging at constant current rates above 1C does not reduce the overall charge cycle time and should be avoided. When charging at higher currents, the cell voltage rises more rapidly due to over-voltage in the electrode reactions and the increased voltage across the internal resistance of the cell. The constant current stage becomes shorter, but the overall charge cycle time is not reduced because the percentage of time in the constant voltage stage increases proportionately.

Stage 3: Constant Voltage – Constant current charge ends and the constant voltage stage is invoked when the cell voltage reaches 4.2V. In order to maximize performance, the voltage regulation tolerance should be better than +1%.

Stage 4: Charge Termination – Unlike nickel-based batteries, it is not recommended to continue to trickle charge Li-lon batteries. Continuing to trickle charge can cause plating of metallic lithium, a condition that makes the battery unstable. The result can be sudden, automatic and rapid disassembly.

Charging is typically terminated by one of two methods: minimum charge current or a timer (or a combination of the two). The minimum current approach monitors the charge current during the constant voltage stage and terminates the charge when the charge current diminishes in the range of 0.02C to 0.07C. The second method determines when the constant voltage stage is invoked. Charging continues for an additional two hours, and then the charge is terminated.

Charging in this manner replenishes a deeply depleted battery in roughly 2.5 to 3 hours.

Advanced chargers employ additional safety features. For example the charge is suspended if the cell temperature is outside a specified window, typically 0°C to 45°C.

### **Li-ion Charging - System Considerations**

A high-performance charging system is required to recharge any battery quickly and reliably. The following system parameters should be considered in order to ensure a reliable, cost-effective solution.

### **Input Source**

Many applications use very inexpensive wall cubes for the input supply. The output voltage is highly dependent on the AC input voltage and the load current being drawn from the wall cube.

In the US, the AC mains input voltage can vary from 90 VRMS to 132 VRMS for a standard wall outlet. Assuming a nominal input voltage of 120 VRMS, the tolerance is +10%, -25%. The charger must provide proper regulation to the battery independent of its input voltage. The input voltage to the charger will scale in accordance to the AC mains voltage and the charge current:

$$Vo = \sqrt{2} \times Vin \times a - 10 (ReQ + Rptc) - 2 \times Vfd$$

REQ is the resistance of the secondary winding plus the reflected resistance of the primary winding (RP/ a2).

RPTC is the resistance of the PTC, and VFD is the forward drop of the bridge rectifiers. In addition, transformer core loss will slightly reduce the output voltage.

Applications that charge from a car adapter can experience a similar problem. The output voltage of car adapter will have a typical range of 9V to 18V.

### **Constant Current Charge Rate and Accuracy**

The choice of topology for a given application may be determined by the desired constant current. Many high constant current, or multiple cell applications rely on a switch-mode charging solution for improved efficiency and less heat generation.

Linear solutions are desirable in low to moderate fast charge current applications for their superior size and cost considerations. However, a linear solution purposely dissipates excess power in the form of heat.

The tolerance on the constant current charge becomes extremely important to a linear system. If the regulation tolerance is loose, pass transistors and other components will need to be oversized adding size and cost. In addition, if the constant current charge is low, the complete charge cycle will be extended.

Figure 2: Capacity Loss vs. Undercharge Voltage.

### **Output Voltage Regulation Accuracy**

The output voltage regulation accuracy is critical in order to obtain the desired goal: maximize battery capacity usage. A small decrease in output voltage accuracy results in a large decrease in capacity. However, the output voltage can not be set arbitrarily high because of safety and reliability concerns.

Figure 2 depicts the importance of output voltage regulation accuracy.

### **Charge Termination Method**

It can not be stressed enough that over charging is the Achilles' heal of Li-Ion cells. Accurate charge termination methods are essential for a safe, reliable, charging system.

### **Cell Temperature Monitoring**

The temperature range over which a Li-Ion battery should be charged is 0°C to 45°C, typically. Charging the battery at temperatures outside of this range may cause the battery to become hot. During a charge cycle, the pressure inside the battery increases causing the battery to swell. Temperature and pressure are directly related. As the temperature rises, the pressure can become excessive. This can lead to a mechanical breakdown inside the battery or venting. Charging the battery outside of this temperature range may also harm the performance of the battery or reduce the battery's life expectance.

Generally, thermistors are included in Lithium-Ion battery packs in order to accurately measure the battery temperature. The charger measures the resistance value of the thermistor between the thermistor terminal and the negative terminal. Charging is inhibited when the resistance, and therefore the temperature, is outside the specified operating range.

### **Battery Discharge Current Or Reverse Leakage Current**

In many applications, the charging system remains connected to the battery in the absence of input power. The charging system should minimize the current drain from the battery when input power is not present. The maximum current drain should be below a few microamperes and, typically, should be below one microampere.

### **Li-ion Charging – Application Examples**

Taking the above system considerations into account, an appropriate charge management system can be developed.

### **Linear Solutions**

Linear charging solutions are generally employed when a well-regulated input source is available. Linear solutions, in these applications, offer advantages of ease of use, size and cost.

Due to the low efficiency of a linear charging solution, the most important factor is the thermal design. The thermal design is a direct function of the input voltage, charge current and thermal impedance between the pass transistor and the ambient cooling air. The worst-case situation is when the device transitions from the trickle charge stage to the constant current stage. In this situation, the pass transistor has to dissipate the maximum power. A trade-off must be made between the charge current, size, cost and thermal requirements of the charging system.

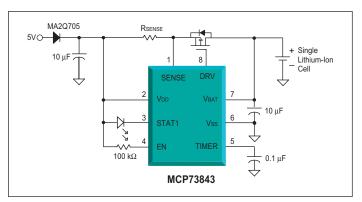

Take, for example, an application required to charge a 1000 mAh, single Li-lon cell from a 5V  $\pm$ 5% input at a constant current charge rate of 0.5C or 1C. Figure 3 depicts Microchip's MCP73843 used to produce a low cost, stand-alone solution. With a few external components, the preferred charge algorithm is implemented.

The MCP73843 combines high accuracy constant current, constant voltage regulation with automatic charge termination.

Figure 3: Typical Linear Solution.

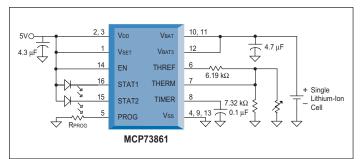

In an effort to further reduce size, cost and complexity of linear solutions, many of the external components can be integrated into the charge management controller. Advanced packaging and reduced flexibility come along with higher integration. These packages require advanced equipment for manufacturing, and, in many instances, preclude rework. Typically, integration encompasses charge current sensing, the pass transistor and reverse discharge protection. In addition, these charge management controllers typically employ some type of thermal regulation. Thermal regulation optimizes the charge cycle time while maintaining device reliability by limiting the charge current based on the device die temperature. Thermal regulation greatly reduces the thermal design effort.

Figure 4 depicts a fully integrated, linear solution utilizing Microchip's MCP73861. The MCP73861 incorporates all the features of the MCP73843 along with charge current sensing, the pass transistor, reverse discharge protection and cell temperature monitoring.

Figure 4: Typical, Fully Integrated, Linear Solution.

### **Charge Cycle Waveforms**

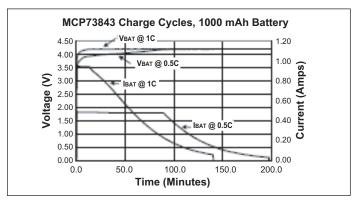

Figure 5 depicts complete charge cycles utilizing the MCP73843 with constant current charge rates of 1C ad 0.5C. Charging at a rate of 0.5C instead of 1C, it takes about 1 hour longer for the end of charge to be reached. The MCP73843 scales the charge termination current proportionately with the fast charge current. The result is an increase of 36% in charge time with the benefit of a 2% gain in capacity and reduced power dissipation. The change in termination current from 0.07C to 0.035C results in an increase in final capacity from ~98% to ~100%. The system designer has to make a trade-off between charge time, power dissipation and available capacity.

Figure 5: MCP73843 Charge Cycle Waveforms.

### **Switch Mode Charging Solutions**

Switch mode charging solutions are generally employed in applications that have a wide ranging input or a high input to output voltage differential. In these applications, switch mode solutions have the advantage of improved efficiency. The disadvantage is system complexity, size and cost.

Take, for example, an application required to charge a 2200 mAh, single Li-lon cell from a car adapter at a constant current charge rate of 0.5C or 1C. It would be extremely difficult to utilize a linear solution in this application due to the thermal issues involved. A linear solution employing thermal regulation could be utilized, but the charge cycle times at the reduced charge currents may be prohibitive.

The first step to designing a successful switch mode charging solution is to choose a topology: buck, boost, buck-boost, flyback, Single-Ended Primary Inductive Converter (SEPIC) or other. Knowing the input and output requirements, and experience, quickly narrows the choices down to two for this application: buck or SEPIC. A buck converter has the advantage of requiring a single inductor. Disadvantages of this topology include an additional diode required for reverse discharge protection, high-side gate drive and current sense and pulsed input current (EMI concern).

The SEPIC topology has advantages that include lowside gate drive and current sense, continuous input current and dc isolation from input to output. The main disadvantage of the SEPIC topology is the use of two inductors and an energy transfer capacitor.

Figure 6 depicts a schematic for a switch mode charger. Microchip's high speed Pulse Width Modulator (PWM), MCP1630, has been utilized in a pseudo smart battery charger application. The MCP1630 is a high-speed, microcontroller adaptable, pulse width modulator. When used in conjunction with a microcontroller, the MCP1630 will control the power system duty cycle to provide output voltage or current regulation. The microcontroller, PIC16F684, can be used to regulate output voltage or current, switching frequency and maximum duty cycle. The MCP1630 generates duty cycle, and provides fast over current protection based off various external inputs. External signals include the input oscillator, the reference voltage, the feedback voltage and the current sense. The output signal is a square-wave pulse. The power train used for the charger is SEPIC.

The microcontroller provides an enormous amount of design flexibility. In addition, the microcontroller can communicate with a battery monitor (Microchip's PS700) inside the battery pack to significantly reduce charge cycle times.

Figure 6: Switch Mode SEPIC Charger.

### **Charge Cycle Waveforms**

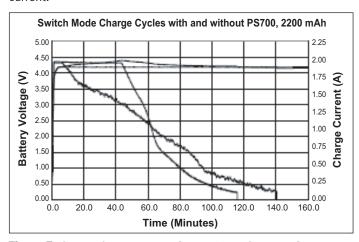

Figure 7 depicts complete charge cycles utilizing the switch mode charging solution. By utilizing a battery monitor in the charging system, charge cycles can be significantly reduced. The battery monitor eliminates sensing the voltage produced across the packs protection circuitry and contact resistance by the charging current.

Figure 7: Charge Cycles Using a Switch Mode Charging Solution.

### Conclusion

Properly restoring energy using the latest battery technology for today's portable products requires careful consideration. An understanding of the charging characteristics of the battery and the application's requirements is essential in order to design an appropriate and reliable battery charging system.

Linear and switch mode charging solutions for Li-lon batteries were presented. The guidelines and considerations presented herein should be taken into account when developing any battery charging system.

### References

- "Handbook of Batteries Third Edition", David Linden, Thomas

- B. Reddy, New York: McGraw-Hill, Inc., 2002.

- http://sanyo.com/batteries/lithium\_ion.cfm

- $\hbox{``MCP73843 Data Sheet'', Microchip Technology Inc., DS21823.}$

- "MCP73861 Data Sheet", Microchip Technology Inc., DS21893.

- "MCP1630 Data Sheet", Microchip Technology Inc., DS21896.

- "PIC16F684 Data Sheet", Microchip Technology Inc., DS41202.

- "PS700 Data Sheet", Microchip Technology Inc., DS21760.

# Working Your Amplifier Inside The Single-Supply Voltage "Box"

By Bonnie C. Baker, Microchip Technology Inc.

It may seem easy enough to transfer classical dual-supply, operational-amplifier circuits directly into a single-supply environment. This is true for a few circuits, but now your amplifier output is swinging much closer to the supply rails than before, and your ground reference has disappeared. In this article, we are going to examine standard voltage-feedback, amplifier circuits (such as non-inverting gain) inverting gain, difference amplifiers, instrumentation amplifiers and a photo-sensing configuration. Within these discussions, we will explore the advantages and limitations of working inside the single-supply environment.

## Issues to Consider When You Convert from Dual Supply to a Single Supply

You could say that an operational amplifier is an operational amplifier, regardless of the supply voltage that is used. The general characteristics from one device to another are consistent. All voltage-feedback amplifiers have two high-impedance inputs and a low-impedance output. When in a closed-loop circuit, the voltage of the two inputs of the amplifier track each other. The amplifier open-loop gain from input to output is usually above 80 dB or 10,000 V/V. These general characteristics are not the issues that get you into trouble when you convert from dual-supplies to a single-supply. In this article, the voltage of the dual supplies is  $\pm 15 \text{V}$  and the voltage of the single supply is 0-5V.

You should focus on two performance characteristics when performing this conversion. These two issues are the input-voltage range and output-voltage swing. The input and output characteristics are fully specified in single-supply operational amplifier data sheets. Generally, if you are converting to a single-supply amplifier circuit these specifications, from amplifier to amplifier, are very close. However, if you don't account for these performance limitations, you will drive the input or output of your amplifier well outside the operating ranges. Outside these ranges the "good" and the "best" single-supply amplifiers act the same.

In this discussion, it is presumed that you understand the circuit design topologies of single-supply amplifiers. "Operational Amplifiers Part 1 of 6: What Does "Rail-to-Rail" Input Operation Really Mean?"(1) discusses the details of the topology of the single-supply amplifier input stages. If you read this article, you will find that when common-mode voltage goes beyond the capabilities of the input transistors the output of the amplifier will latch to either rail. "Operational Amplifiers Part 2 of 6: Working with Single-Supply Operational-Amplifier Output Characteristics"(2) discusses the details of single-supply amplifier output-stage performance. This article defines two areas of the amplifier output-stage operation. If you drive your amplifier "hard" into either rail (within a few 10s of millivolts), the amplifier will leave its linear region. If you only drive your amplifier a few hundred millivolts from the rails (as defined in the open-loop gain specification), the amplifier will perform in its linear region.

We will concentrate on these two performance characteristics. You will find that this gives you enough guidance to successfully convert all of your amplifier dual power-supply circuits to single supply. And, as stated before, besides these two areas, an amplifier is an amplifier.

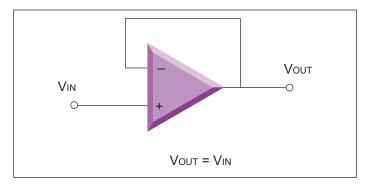

# The Buffer Amplifier Configuration

The buffer is the easiest amplifier circuit to transfer from a dual-supply to a single-supply environment. Figure 1 shows an amplifier configured as a buffer.

**Figure 1:** The amplifier buffer operates with the same circuit topology for a dual or single-supply application.

When an amplifier is configured using a single-supply source, there are a few unexpected limitations of the input stage and output stage. The input stage of single-supply amplifiers can stop the signal from entering the amplifier. If the data sheet of the amplifier does not claim rail-to-rail operation, it most likely will not be a rail-to-rail input amplifier. This limits your input swing. If the input to the amplifier, VIN, goes above the limits of the input transistor, the output travels to the positive rail.

The output stage also limits the performance of this circuit in a single-supply configuration. With dual-supplies, the output stage is able to perform across its full output range without distortion. For instance, if the amplifier in Figure 1 had a  $\pm 15\text{V}$  supply and the input, Vin, was 10V, Vout would be 10V also (assuming no offset errors exist). This conclusion is obvious. However, if you use 0-5V supplies on the same circuit, with an input voltage of zero volts the output will not produce the same voltage. The output will ride 10s of millivolts above ground. The actual limit for this value is the low-level, output-voltage swing and dependant on the particular amplifier you are using.

If you are counting on sending a negative voltage through this circuit, it will not work. Again, this may seem obvious. However, you are converting from a dual-supply to a single-supply environment. If the electronics before the amplifier still use a dual supply, this can be a problem.

The phenomena will also happen at the positive, output-voltage rail. If you are using a rail-to-rail input amplifier and you drive the output high, the output will fall short of reaching the supply rail, or 5V. It will actually fall short by 10s of millivolts below the supply. The amplifier's data sheet calls out this actual limit as the high-level output-voltage swing.

This may not seem like a significant problem unless you are counting on using these extreme voltages in your system. For instance, if your amplifier is driving an A/D converter that has an input range of 0 to 5V, several codes on the bottom and top of your digital output word will never appear.

## Non-Inverting Configurations With Gain Built-in

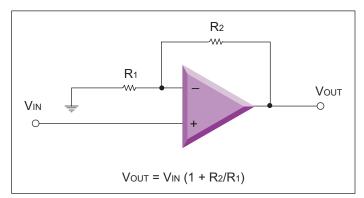

The non-inverting configuration is more forgiving than the buffer circuit. With the non-inverting amplifier configuration (Figure 2.), the gain of the circuit is greater than +1V/V. This circuit will send the voltage applied to  $\text{V}_{\text{IN}}$  and gain it using the resistors in the circuit.

**Figure 2:** The non-inverting, gained amplifier circuit is also easy to transfer from a dual-supply environment to a single-supply system. Since the signal is gained by the equation (1+ R2/R1) to the output, the input stage is not exercised as much as it is with the buffer. The output stage is more likely to over-range because of the gain in the system.

This circuit is not hard to convert between a dual- and single-supply environment. The input stage limitations do not come into play as much as they did with the buffer circuit. Most single-supply amplifiers have an input, common-mode-range to ground. This amplifier circuit will gain any signal on the input, VIN, to a higher value. It is probable that the output stage will limit the signal on the positive supply rail before the input stage can reach any internal limits.

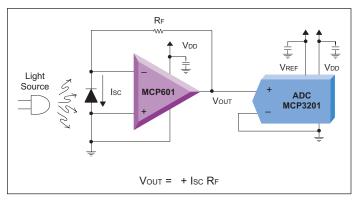

## **Photo-Sensing Problems**

The transimpedance amplifier that is used for photo-sensing applications is a little more difficult to convert from dual- to single-supply environments. A primary issue is to correctly bias the photo sensor across the input terminals. Figure 3 illustrates the proper connection.

**Figure 3:** Grounding the anode of the photo sensor and attaching cathode to RF allows the sensor current to flow through RF creating a positive voltage at Voυτ. If the polarity of the photo sensor is reversed across the amplifier-input terminals, the sensor current will be reversed causing the output of the amplifier to remain on the ground rail.

In this configuration (Figure 3), the current from the photo diode during excitation from a light source will change the output of the amplifier in a positive direction. This arrangement appears to work well except for the fact that the amplifier's output is unable to swing all the way down to ground. Consequently, smaller magnitudes of luminance from the light source will be not be registered by the A/D converter.

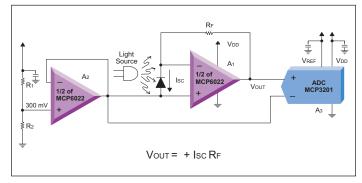

Figure 4 provides a solution to this problem. The output of the amplifier is raised by 300 mV (from ground) to ensure that the amplifier is operating in its linear region. A level-shift network, consisting of R<sub>1</sub>, R<sub>2</sub> and A<sub>2</sub>, achieves this goal.

**Figure 4:** R1 and R2, in conjunction with VDD, form a voltage divider. The output of this divider is 300 mV. A buffer, A2, isolates the impedance of R1 and R2 while connecting to the anode of the photo sensor. This circuit configuration creates a 300 mV level shift of the signal to the output of the transimpedance amplifier (A1). The A/D converter also has this level shift applied to its inputs.

The conditions of the open-loop gain specification of the MCP6022 are "Vout = Vss +300 mV and Vdd – 300 mV." This circuit creates a 300 mV level shift of the signal so that the amplifier, A1, remains in its linear region. The selection of A2 is critical. A2 must be able to supply current to the photosensing circuit in a timely manner. Consequently, A2 must be as fast or faster than A1. Dual amplifiers work well with these requirements. A precision voltage reference (replacing Vdd) at the top of R1 will add stability and reduce noise.

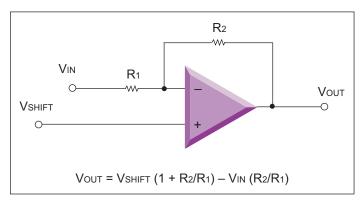

# The Inverting Configuration Will Surprise You

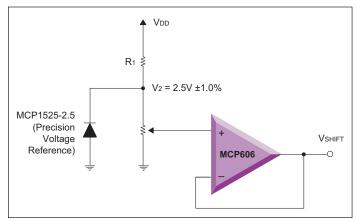

The inverting-amplifier configuration (Figure 5) will only work in a single-supply circuit if you have a voltage reference. You can imagine that by connecting the voltage reference node, VSHIFT, to ground, the circuit would only work if the input signal were negative. Figure 6 shows one example of a voltage-reference circuit.

Figure 5: In a single-supply circuit, you need a voltage to make this system work correctly. By connecting VSHIFT pin to ground, the output will attempt to go below ground with a positive input. This circuit will work well with a VSHIFT ground connect if the input voltage is negative. But, you have to ask yourself, "where will that negative voltage come from in a single-supply circuit?"

Figure 6: Using this type of voltage reference circuit to drive the VSHIFT (Figure 5) input of an amplifier configured in an inverting gain will level shift the output of the circuit amplifier into its linear region. Try to set the VSHIFT voltage around the center of the input range of the circuit.

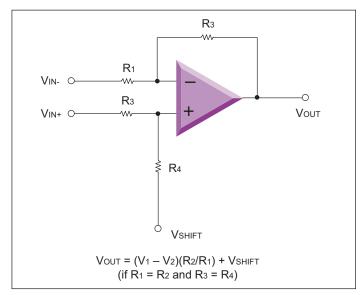

### The Difference Amplifier

Figure 7 illustrates an implementation of the difference-amplifier function. The DC transfer function of this circuit is equal to:

VOUT = V1 R4(R1+R2) / ((R3+R4)R1) - V2(R2/R1) + VSHIFT R3 (R1+R2)/((R3+R4)R1)

If  $R_1/R_2$  is equal to  $R_3/R_4$ , the closed-loop output of this circuit equals:

$$Vout = (V_1 - V_2)(R_2/R_1) + Vshift$$

In this circuit, the maximum allowable voltage of the amplifier's inputs limit the input common-mode range. It is possible to have input voltages at V1 and V2 that exceed the power-supply voltages. The gain oonboth input signals is equal. This resistor configuration also subtracts the common-mode voltage of the two input signals. In addition, by setting the two resistor ratios to be greater than one, you can easily implement a gain larger than one. In a single-supply environment, a voltage reference (VSHIFT) can center the output signal between ground and the power supply. Otherwise, it is possible to drive the output beyond the ground or

VDD rail. The purpose and effects of this reference voltage is to

shift the output signal into the linear region of the amplifier.

Figure 7: The difference amplifier operates best in a dual-supply environment. In a dual-supply environment, connect VDual- and single-supply can power the two amp-instrumentation amplifier. Single-supply circuits require a center-supply reference, VSHIFT to ground. In the single-supply environment, where there is no "mid-supply" connect, connecting the VSHIFT pin to ½ VDD is appropriate.

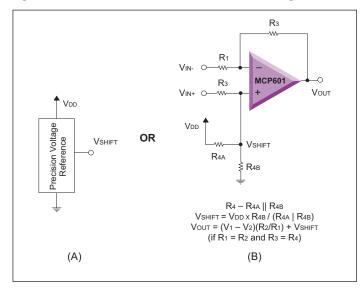

Figure 8 illustrates two possible circuits for the voltage, Vshift.

**Figure 8:** A precision voltage reference (A) or a resistor divider (B) between V<sub>DD</sub> and ground is used to generate the voltage at V<sub>SHIFT</sub> in Figure 7. Single-supply difference amplifiers, three-amp instrumentation amplifiers and the two-amp instrumentation amplifiers use these circuits.

The precision, voltage-reference device in Figure 8A is a suitable high-precision solution for your single-supply circuits. This voltage reference will give you accurate, DC results at room and over temperature. Figure 8B illustrates an alternative solution. In this circuit, splitting the resistor, R4 (Figure 7) between VDD and ground provides a voltage for VSHIFT. Figure 8 summarizes the governing equations for the voltage of VSHIFT and gain of the difference amplifier. The accuracy of this circuit depends on the resistor matching and stability of VDD.

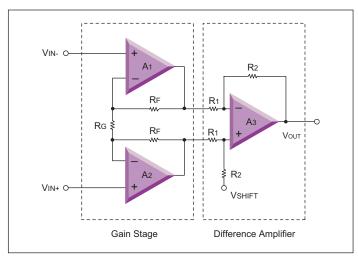

## The Three-Amp Instrumentation Amplifier

The most versatile instrumentation amplifier configuration uses three operational amplifiers in its implementation. This instrumentation amplifier is easy to understand because each of the three operational amplifiers serves a specific function. With this circuit configuration (shown in Figure 9), two of the three operational amplifiers (A1 and A2) gain the two input signals. The third amplifier, A3, subtracts the two gained input signals, thereby providing a single-ended output. The transfer function of the circuit is equal to:

Vout = (Vin+ - Vin-)(1 + 2RF/Rg) (R2/R1)

**Figure 9:** The three-amp instrumentation amplifier has two fundamental stages. The first stage (gain stage gains the input signals and present the results to the second stage (difference amplifier).

In single-supply applications, the circuits in Figure 8 generate the center-supply reference,  $\mbox{\sc VSHIFT}.$

### **The Two-Amp Instrumentation Amplifier**

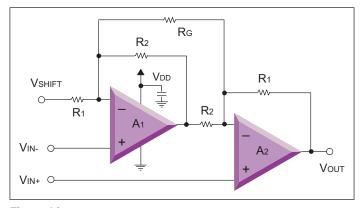

The design shown in Figure 10 uses two operational amplifiers. This design configuration is typically called the two op-amp instrumentation amplifier.

**Figure 10:** Dual- and single- supply can power the two amp instrumentation amplifier. Single-supply circuits require a center-supply reference, VSHIFT.

Discrete designs use dual amplifiers for good matching of bandwidth and performance over temperature. This instrumentation amplifier utilizes the high impedance of the non-inverting input of the operational amplifiers, thereby significantly reducing source impedance mismatch problems at DC. The transfer function of this circuit is equal to:

$$VOUT = (VIN+ - VIN-)(1 + R1/R2 + 2R1/RG) + VSHIFT$$

If the application is in a single-supply environment, this circuit will typically require a reference that is half of the way between the power-supply voltages. In Figure 10, VSHIFT serves that function. This circuit does not allow for zero-volt, common mode, input voltages in single-supply systems.

The center-supply reference, Vshift, is implemented using circuits in Figure 8.

### Conclusion

The task of transferring your dual-supply amplifier circuits to single-supply environments is straightforward. During the conversion, pay attention to input common-mode range and output-swing specification violations. If any violations of the single-supply amplifier's input or output stage occur as a result of the new power supplies, the addition of a voltage reference can eliminate these violations, making the circuit usable.

### References

"Operational Amplifiers Part 1 of 6: What Does "Rail-to-Rail" Input Operation Really Mean?", Bonnie C. Baker, AnalogZone, March 22, 2004.

"Operational Amplifiers Part 2 of 6: Working with Single-Supply Operational-Amplifier Output Characteristics", Bonnie C. Baker, AnalogZone, May 3, 2004.

# **Every Amplifier Is Waiting To Oscillate And Every Oscillator Is Waiting To Amplify**

By Bonnie C. Baker, Microchip Technology Inc.

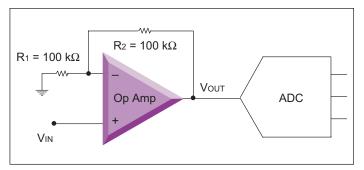

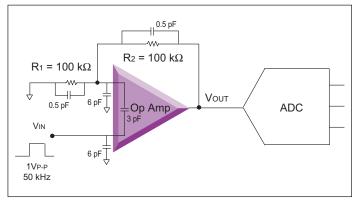

What is operational amplifier (op amp) circuit stability, and how do you know when you are on the "hairy edge"? Typically, there is a feedback system around the op amp to stabilize the variability and reduce the magnitude of the open-loop gain from part to part. With this approach, the stability of your amplifier circuit depends on the variability of the resistors in your circuit, not your op amps . Using resistors around your op amp provides circuit "stability". At least you hope that a predictable gain is ensured. But, it is possible to design an amplifier circuit that does quite the opposite.

You can design an amplifier circuit that is extremely unstable to the point of oscillation. In these circuits, the closed gain is somewhat trivial, because an oscillation is "swamping out" your results at the output of the amplifier. In a closed-loop amplifier system, stability can be ensured if you know the phase margin of the amplifier system. In this evaluation, the Bode stability-analysis technique is commonly used. With this technique, the magnitude (in dB) and phase response (in degrees) of both the open-loop response of the amplifier and circuit-feedback factor are included in the Bode plot. This article looks at these concepts and makes suggestions on how to avoid the design of a "singing" circuit when your primary feedback is frequency stability.

# The Internal Basics of the Operational-Amplifier Block Diagram

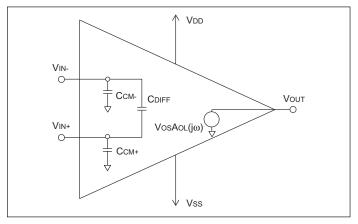

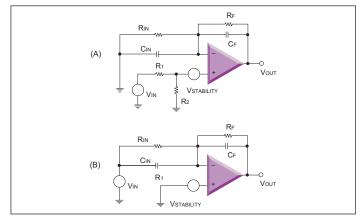

Before getting started on the frequency analysis of an amplifier circuit, let's review a few amplifier topology concepts. Figure 1 shows the critical internal op-amp elements that you need to be familiar with if you engage in a frequency analysis. This amplifier has five terminals, as expected, but it also has parasitics, such as input capacitance and frequency dependent open-loop gain.

**Figure 1:** The voltage-feedback operational amplifier frequency model includes the input capacitances (CDIFF and CCM) to ensure that the interaction of the external input-source parasitics and the feedback parasitics can be taken into account in a frequency evaluation. This model also has the internal open-loop gain over frequency (AOL ( $j\omega$ )). These two parameters ensure that the internal parasitics of the output stage are in the analysis.

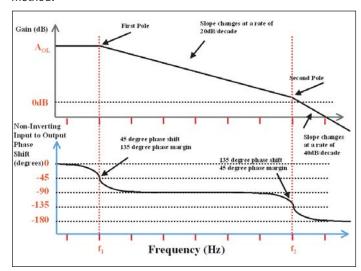

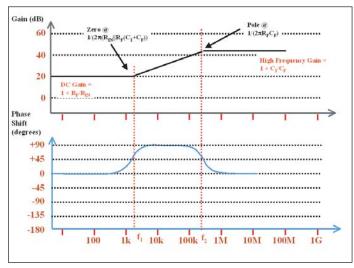

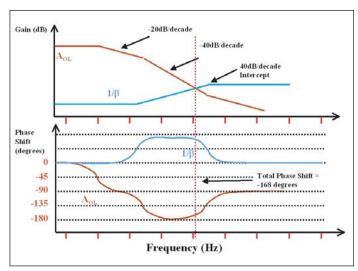

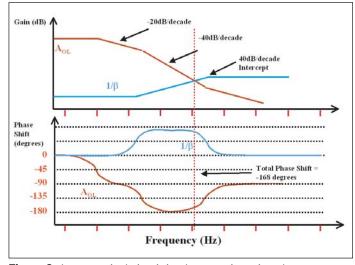

The two input terminals have a common-mode capacitances to ground (Ccm) and differential capacitance (CDIFF) between the inputs. AoL (j $\varpi$ ) represents the open-loop gain, frequency response of the amplifier. Figure 2 shows the frequency response of a typical voltage-feedback amplifier using the Bode-plot method.

**Figure 2:** A gain plot and a phase plot illustrate the frequency behavior of a voltage-feedback amplifier. In this simple representation, the amplifier has two dominant poles. The first pole occurs at lower frequencies, typically between 10 Hz to 1 kHz (depending on the gain-bandwidth product of the amplifier). The second pole resides at higher frequencies. This pole occurs at a higher frequency than the zero decibels (dB) frequency. If it is lower, the amplifier is usually unstable in a unity-gain circuit.

The amplifier gain response over frequency (AoL (j $\omega$ )) for a voltage-feedback amplifier is usually modeled with a simple second order transfer function. This second-order transfer function has two poles. The two plots in Figure 2 illustrate the gain (top) and phase response (bottom) of a typical op amp. The units of the y-axis of the gain curve are dB.

Ideally, the open-loop gain of an amplifier is equal to the magnitude of the ratio of the voltage at the output terminal, divided by the difference of the voltages applied between the two input terminals.

$$AoL (dB) = 20log |( Vout / (Vin+ - Vin- ))|$$

It would be nice if this open-loop gain ratio were infinite. But in reality, the complete frequency response of the open-loop gain, AoL (j $\omega$ ), is less than ideal at DC, FT attenuates at a rate of 20 dB/decade. This attenuation starts at the frequency where the first pole in the transfer function appears. This is illustrated in the Bode plot in Figure 2.

Usually, the first pole of the open-loop response of an operational amplifier occurs between 1 Hz to 1 kHz. The second pole occurs at a higher frequency, nearer to where the open-loop gain-curve crosses 0 dB. The gain response of an amplifier starts to fall off at 40 dB/decade, which is at the frequency where the second pole occurs.

The units of the y-axis of the phase plot in Figure 2 (bottom plot) are degrees. You can convert degrees to radians with the following formula:

Phase in radians = (Phase in degrees)\* $2\pi/360^{\circ}$

Phase in degrees can be translated to phase delay or group delay (seconds) with the following formula:

Phase delay = -  $(\delta phase/\delta f)/360^{\circ}$

The same x-axis frequency scale aligns across both plots.

The phase response of an amplifier in this open-loop configuration is also predictable. The phase shift or change from the non-inverting input to the output of the amplifier is zero degrees at DC. Conversely, the phase shift from the inverting input terminal to the output is equal to -180 degrees at DC.

At one decade (1/10 f1) before the first pole, f1, the phase relationship of non-inverting input to output has already started to change,  $\sim$  -5.7 degrees. At the frequency where the first pole appears in the open-loop gain curve (f1), the phase margin has dropped to -45 degrees. The phase continues to drop for another decade (10f1) where it is 5.7 degrees above its final value of -90 degrees. These phase-response changes are repeated for the second pole, f2.

What is important to understand are the ramifications of changes in this phase relationship with respect to the input and output of the amplifier. One frequency decade past the second pole, the phase shift of the non-inverting input to output is  $\sim$ -180 degrees. At this same frequency, the phase shift of the inverting input to output is zero or  $\sim$ -360 degrees. With this type of shift, Vin+ is actually inverting the signal to the output. In other words, the roles of the two inputs have reversed. If the role of either of the inputs changes like this, the amplifier will ring as the signal goes from the input to the output in a closed-loop system. The only thing stopping this condition from occurring with the stand-alone amplifier is that the gain drops below 0 dB. If the open-loop gain of the amplifier drops below 0 dB in a closed-loop system, the feedback is essentially "turned OFF".

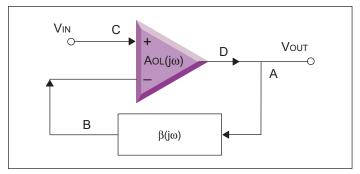

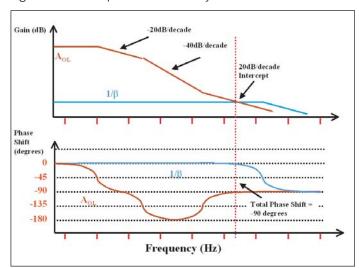

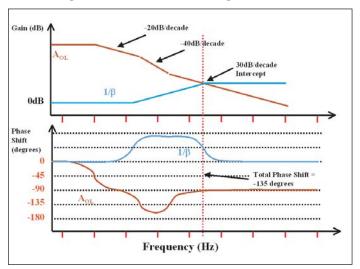

### Stability in Closed-Loop Amplifier Systems

Typically, op amps have a feedback network around them. This reduces the variability of the open-loop gain response from part to part. Figure 3 shows a block diagram of this type of network.

**Figure 3:** A block diagram of an amplifier circuit, which includes the amplifier-gain cell, AoL and the feedback network, B.

In Figure 3,  $\beta(j\omega)$  represents the feedback factor. Due to the fact that the open-loop gain of the amplifier (AoL) is relatively large and the feedback factor is relatively small, a fraction of the output voltage is fed back to the inverted input of the amplifier. This configuration sends the output back to the inverting terminal, creating a negative-feedback condition. If  $\beta$  were fed back to the non-inverting terminal, this small fraction of the output voltage would be added instead of subtracted. In this configuration, there would be positive feedback and the output would eventually saturate.

### **Closed-Loop Transfer Function**

If you analyze the loop in Figure 3, you must assume an output voltage exists. This makes the voltage at A equal to  $Vou\tau(j\omega)$ . The signal passes through the feedback system,  $\beta(j\omega)$ , so that the voltage at B is equal to  $\beta(j\omega)Vou\tau(j\omega)$ . The voltage, or input voltage, at C is added to the voltage at B; C is equal to  $(VIN(j\omega) - b(j\omega)Vou\tau(j\omega))$ . With the signal passing through the gain cell,  $AoL(j\omega)$ , the voltage at point D is equal to  $AoL(j\omega)(VIN(j\omega) - \beta(j\omega)Vou\tau(j\omega))$ . This voltage is equal to the original node, A, or  $Vou\tau$ . The formula that describes this complete closed-loop system is equal to:

A = D or