# Spread Aware™, Frequency Multiplier and Zero Delay Buffer

#### **Features**

- Spread Aware<sup>™</sup>—designed to work with SSFTG reference signals

- 90ps typical jitter OUT2

- 200ps typical jitter OUT1

- 65ps typical output-to-output skew

- 90ps typical propagation delay

- Voltage range: 3.3V±5%, or 5V±10%

- Output frequency range: 20MHz-133MHz

- Two outputs

- Configuration options allow various multiplication of the reference frequency, refer to Table 1 to determine the specific option which meets your multiplication needs

- · Available in 8-pin SOIC package

**Table 1. Configuration Options**

| FBIN | FS0 | FS1 | OUT1     | OUT2    |

|------|-----|-----|----------|---------|

| OUT1 | 0   | 0   | 2 X REF  | REF     |

| OUT1 | 1   | 0   | 4 X REF  | 2 X REF |

| OUT1 | 0   | 1   | REF      | REF/2   |

| OUT1 | 1   | 1   | 8 X REF  | 4 X REF |

| OUT2 | 0   | 0   | 4 X REF  | 2 X REF |

| OUT2 | 1   | 0   | 8 X REF  | 4 X REF |

| OUT2 | 0   | 1   | 2 X REF  | REF     |

| OUT2 | 1   | 1   | 16 X REF | 8 X REF |

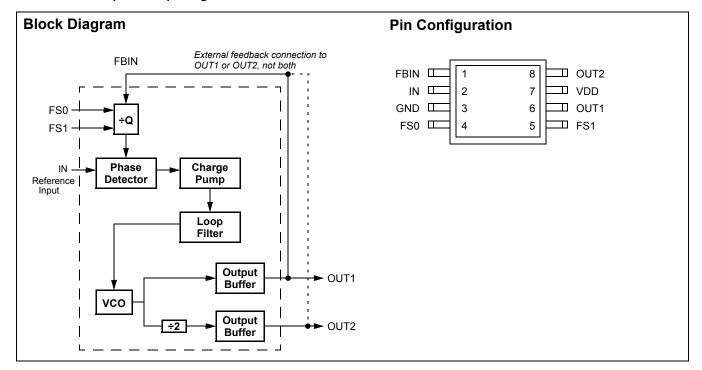

#### **Pin Definitions**

| Pin Name | Pin No. | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                            |  |

|----------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IN       | 2       | 1           | Reference Input: The output signals will be synchronized to this signal.                                                                                                                                                                                                                                                                                                   |  |

| FBIN     | 1       | I           | <b>Feedback Input:</b> This input must be fed by one of the outputs (OUT1 or OUT2) to ensure proper functionality. If the trace between FBIN and the output pin being used for feedback is equal in length to the traces between the outputs and the signal destinations, then the signals received at the destinations will be synchronized to the REF signal input (IN). |  |

| OUT1     | 6       | 0           | Output 1: The frequency of the signal provided by this pin is determined by the feedback signal connected to FBIN, and the FS0:1 inputs (see Table 1).                                                                                                                                                                                                                     |  |

| OUT2     | 8       | 0           | Output 2: The frequency of the signal provided by this pin is one-half of the frequency of OUT1. See Table 1.                                                                                                                                                                                                                                                              |  |

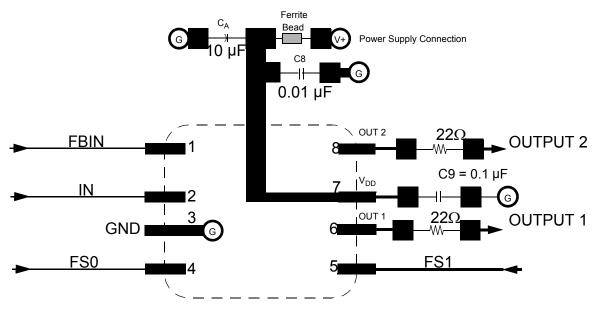

| VDD      | 7       | Р           | <b>Power Connections:</b> Connect to 3.3V or 5V. This pin should be bypassed with a $0.1$ - $\mu$ F decoupling capacitor. Use ferrite beads to help reduce noise for optimal jitter performance.                                                                                                                                                                           |  |

| GND      | 3       | Р           | Ground Connection: Connect all grounds to the common system ground plane.                                                                                                                                                                                                                                                                                                  |  |

| FS0:1    | 4, 5    | I           | Function Select Inputs: Tie to VDD (HIGH, 1) or GND (LOW, 0) as desired per Table 1.                                                                                                                                                                                                                                                                                       |  |

#### Overview

The CY23S02 is a two-output zero delay buffer and frequency multiplier. It provides an external feedback path allowing maximum flexibility when implementing the Zero Delay feature. This is explained further in the sections of this data sheet titled "How to Implement Zero Delay," and "Inserting Other Devices in Feedback Path."

The CY23S02 is a pin-compatible upgrade of the Cypress W42C70-01. The CY23S02 addresses some application dependent problems experienced by users of the older device. Most importantly, it addresses the tracking skew problem induced by a reference that has Spread Spectrum Timing enabled on it.

# **Spread Aware**

Many systems being designed now utilize a technology called Spread Spectrum Frequency Timing Generation. Cypress has been one of the pioneers of SSFTG development, and we designed this product so as not to filter off the Spread Spectrum feature of the Reference input, assuming it exists. When a zero delay buffer is not designed to pass the SS feature through, the result is a significant amount of tracking skew which may cause problems in systems requiring synchronization.

For more details on Spread Spectrum timing technology, please see the Cypress application note titled, "EMI Suppression Techniques with Spread Spectrum Frequency Timing Generator (SSFTG) ICs."

Figure 1. Schematic/Suggested Layout

# **How to Implement Zero Delay**

Typically, zero delay buffers (ZDBs) are used because a designer wants to provide multiple copies of a clock signal in phase with each other. The whole concept behind ZDBs is that the signals at the destination chips are all going HIGH at the same time as the input to the ZDB. In order to achieve this, layout must compensate for trace length between the ZDB and the target devices. The method of compensation is described below.

External feedback is the trait that allows for this compensation. The PLL on the ZDB will cause the feedback signal to be in phase with the reference signal. When laying out the board, match the trace lengths between the output being used for feed back and the FBIN input to the PLL.

If it is desirable to either add a little delay, or slightly precede the input signal, this may also be affected by either making the trace to the FBIN pin a little shorter or a little longer than the traces to the devices being clocked.

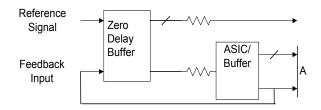

# Inserting Other Devices in Feedback Path

Another nice feature available due to the external feedback is the ability to synchronize signals up to the signal coming from some other device. This implementation can be applied to any device (ASIC, multiple output clock buffer/driver, etc.) which is put into the feedback path.

Referring to Figure 2, if the traces between the ASIC/Buffer and the destination of the clock signal(s) (A) are equal in length

to the trace between the buffer and the FBIN pin, the signals at the destination(s) device will be driven HIGH at the same time the Reference clock provided to the ZDB goes HIGH. Synchronizing the other outputs of the ZDB to the outputs from the ASIC/Buffer is more complex however, as any propagation delay in the ASIC/Buffer must be accounted for.

Figure 2. Six Output Buffer in the Feedback Path

### **Phase Alignment**

In cases where OUT1 (i.e., the higher frequency output) is connected to FBIN input pin the output OUT2 rising edges may be either 0 or 180° phase aligned to the IN input waveform (as set randomly when the input and/or power is supplied). If OUT2 is desired to be rising-edge aligned to the IN input's rising edge, then connect the OUT2 (i.e., the lowest frequency output) to the FBIN pin. This set-up provides a consistent input-output phase relationship.

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other condi-

tions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>                    | Power Dissipation                      | 0.5          | W    |

# **DC Electrical Characteristics**: $T_A$ =0°C to 70°C or -40° to 85°C, $V_{DD}$ = 3.3V ±5%

| Parameter       | Description         | Test Condition         | Min. | Тур. | Max. | Unit |

|-----------------|---------------------|------------------------|------|------|------|------|

| I <sub>DD</sub> | Supply Current      | Unloaded, 133 MHz      | _    | 17   | 35   | mA   |

| V <sub>IL</sub> | Input Low Voltage   |                        | _    | _    | 0.8  | V    |

| V <sub>IH</sub> | Input High Voltage  |                        | 2.0  | _    |      | V    |

| V <sub>OL</sub> | Output Low Voltage  | I <sub>OL</sub> = 8 mA | _    | _    | 0.4  | V    |

| V <sub>OH</sub> | Output High Voltage | I <sub>OH</sub> = 8 mA | 2.4  | _    |      | V    |

| I <sub>IL</sub> | Input Low Current   | V <sub>IN</sub> = 0V   | -40  | _    | 5    | μΑ   |

| I <sub>IH</sub> | Input High Current  | $V_{IN} = V_{DD}$      |      | _    | 5    | μΑ   |

# **DC Electrical Characteristics:** $T_A = 0^{\circ}C$ to $70^{\circ}C$ or $-40^{\circ}$ to $85^{\circ}C$ , $V_{DD} = 5V \pm 10\%$

| Parameter       | Description Test Condition                 |                                   | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------------------|-----------------------------------|------|------|------|------|

| I <sub>DD</sub> | Supply Current                             | Unloaded, 133 MHz                 | _    | 31   | 50   | mA   |

| V <sub>IL</sub> | Input Low Voltage                          |                                   | _    | _    | 0.8  | V    |

| V <sub>IH</sub> | Input High Voltage                         |                                   | 2.0  | _    |      | V    |

| V <sub>OL</sub> | Output Low Voltage                         | I <sub>OL</sub> = 8 mA            | _    | _    | 0.4  | V    |

| V <sub>OH</sub> | Output High Voltage I <sub>OH</sub> = 8 mA |                                   | 2.4  | _    |      | V    |

| I <sub>IL</sub> | Input Low Current                          | V <sub>IN</sub> = 0V              | -80  | _    | 5    | μА   |

| I <sub>IH</sub> | Input High Current                         | V <sub>IN</sub> = V <sub>DD</sub> | _    | _    | 5    | μА   |

# AC Electrical Characteristics: $T_A$ = 0°C to +70°C or -40° to 85°C, $V_{DD}$ = 3.3V±5%

| Parameter          | Description                                         | Test Condition           | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------------|--------------------------|------|------|------|------|

| f <sub>IN</sub>    | Input Frequency <sup>[1]</sup>                      | OUT2 = REF               | 10   | _    | 133  | MHz  |

| f <sub>OUT</sub>   | Output Frequency                                    | OUT1                     | 20   | _    | 133  | MHz  |

| t <sub>R</sub>     | Output Rise Time                                    | 0.8V to 2.0V, 15-pF load | _    | _    | 3.5  | ns   |

| t <sub>F</sub>     | Output Fall Time                                    | 2.0V to 0.8V, 15-pF load | _    | _    | 2.5  | ns   |

| t <sub>ICLKR</sub> | Input Clock Rise Time <sup>[2]</sup>                |                          | _    | _    | 10   | ns   |

| t <sub>ICLKF</sub> | Input Clock Fall Time <sup>[2]</sup>                |                          | _    | _    | 10   | ns   |

| t <sub>PD</sub>    | FBIN to IN (Reference Input) Skew <sup>[3, 4]</sup> |                          | _    | _    | 300  | ps   |

| t <sub>DC</sub>    | Duty Cycle <sup>[5]</sup>                           | Note 5                   | 40   | 50   | 60   | %    |

| t <sub>LOCK</sub>  | PLL Lock Time                                       | Power supply stable      |      | _    | 1.0  | ms   |

| t <sub>JC</sub>    | Jitter, Cycle-to-Cycle <sup>[6]</sup>               | OUT1                     | _    | 200  | 300  | ps   |

|                    |                                                     | OUT2                     | _    | 90   | 300  | ps   |

| t <sub>SKEW</sub>  | Output-output Skew                                  |                          | _    | 65   | 250  | ps   |

| t <sub>PD</sub>    | Propagation Delay                                   |                          | -350 | 90   | 350  | ps   |

# AC Electrical Characteristics: $T_A = 0$ °C to +70°C or -40° to 85°C, $V_{DD} = 5V\pm10\%$

| Parameter          | Description                                         | Test Condition           | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------------|--------------------------|------|------|------|------|

| f <sub>IN</sub>    | Input Frequency <sup>[1]</sup>                      | OUT2 = REF               | 10   | _    | 133  | MHz  |

| f <sub>OUT</sub>   | Output Frequency                                    | OUT1                     | 20   | _    | 133  | MHz  |

| t <sub>R</sub>     | Output Rise Time                                    | 0.8V to 2.0V, 15-pF load | _    | _    | 3.5  | ns   |

| t <sub>F</sub>     | Output Fall Time                                    | 2.0V to 0.8V, 15-pF load | _    | _    | 2.5  | ns   |

| t <sub>ICLKR</sub> | Input Clock Rise Time <sup>[2]</sup>                |                          | _    | _    | 10   | ns   |

| t <sub>ICLKF</sub> | Input Clock Fall Time <sup>[2]</sup>                |                          | _    | _    | 10   | ns   |

| t <sub>PD</sub>    | FBIN to IN (Reference Input) Skew <sup>[3, 4]</sup> |                          | _    | _    | 300  | ps   |

| t <sub>D</sub>     | Duty Cycle <sup>[7, 8]</sup>                        |                          | 40   | 50   | 60   | %    |

| t <sub>LOCK</sub>  | PLL Lock Time                                       | Power supply stable      | _    | _    | 1.0  | ms   |

| t <sub>JC</sub>    | Jitter, Cycle-to-Cycle <sup>[6]</sup>               | OUT1                     | _    | 200  | 300  | ps   |

|                    |                                                     | OUT2                     | _    | 90   | 300  | ps   |

| t <sub>SKEW</sub>  | Output-output Skew                                  |                          | _    | 65   | 250  | ps   |

| t <sub>PD</sub>    | Propagation Delay                                   |                          | -350 | 90   | 350  | ps   |

# **Ordering Information**

| Ordering Code | Package Type                         | Temperature Grade        |

|---------------|--------------------------------------|--------------------------|

| CY23S02SI-1   | 8-pin SOIC (150 mil)                 | Industrial, –40° to 85°C |

| CY23S02SI-1T  | 8-pin SOIC (150 mil) - Tape and Reel | Industrial, –40° to 85°C |

| Lead-free     |                                      |                          |

| CY23S02SXI-1  | 8-pin SOIC (150 mil)                 | Industrial, –40° to 85°C |

| CY23S02SXI-1T | 8-pin SOIC (150 mil) - Tape and Reel | Industrial, –40° to 85°C |

- Input frequency is limited by output frequency range and input to output frequency multiplication factor (which is determined by circuit configuration).

Longer input rise and fall time will degrade skew and jitter performance.

All AC specifications are measured with a 50Ω transmission line, load terminated with 50Ω to 1.4V.

- 4. Skew is measured at 1.4V on rising edges.

- 5. Duty cycle is measured at 1.4V.

- 6. Jitter is measured on 133-MHz signal at 1.4V, low frequency jitter = 350 ps.

- 7. Duty cycle is measured at 1.4V, 120 MHz.8. Duty cycle at 133 MHz is 35/65 worst case.

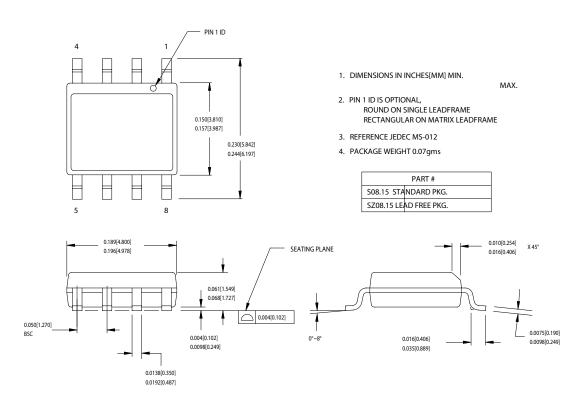

# **Package Drawing and Dimensions**

#### 8-lead (150-Mil) SOIC S8

51-85066-\*C

Spread Aware is a trademark of Cypress Semiconductor Corporation. All products and company names mentioned in this document may be the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY23S02 Spread Aware™, Frequency Multiplier and Zero Delay Buffer Document Number: 38-07155 |         |               |                    |                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| REV.                                                                                                        | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                     |  |  |

| **                                                                                                          | 110265  | 12/18/01      | SZV                | Change from Spec number: 38-00795 to 38-07155                                                             |  |  |

| OBS                                                                                                         | 292037  | See ECN       | RGL                | To Obsolete the DS                                                                                        |  |  |

| *B                                                                                                          | 348376  | See ECN       | RGL                | Minor Change: Re-activate the Spec, only commercial are obsoleted, All industrial parts area still active |  |  |

| *C                                                                                                          | 378857  | See ECN       | RGL                | Add typical char data Added Phase Alignment paragraph                                                     |  |  |