Silicon P Channel Power MOS FET High Speed Power Switching

# HITACHI

ADE-208-475 D (Z) 5th. Edition February 1999

#### Features

- Low on-resistance

- Capable of 2.5 V gate drive

- Low drive current

- High density mounting

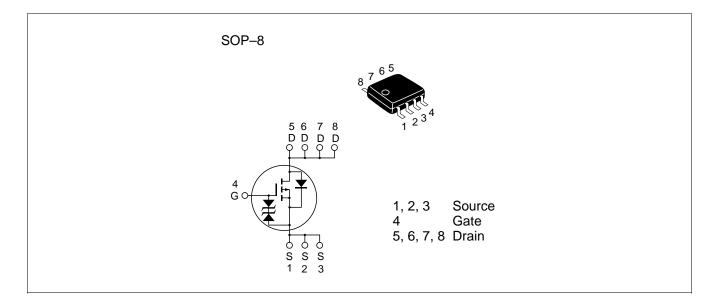

#### Outline

#### **Absolute Maximum Ratings** (Ta = $25^{\circ}$ C)

| Item                                   | Symbol            | Ratings     | Unit |  |

|----------------------------------------|-------------------|-------------|------|--|

| Drain to source voltage                | V <sub>DSS</sub>  | - 20        | V    |  |

| Gate to source voltage                 | V <sub>GSS</sub>  | ± 10        | V    |  |

| Drain current                          | I <sub>D</sub>    | - 5.5       | А    |  |

| Drain peak current                     | Note1<br>D(pulse) | - 44        | А    |  |

| Body-drain diode reverse drain current | I <sub>DR</sub>   | - 5.5       | A    |  |

| Channel dissipation                    | Pch Note2         | 2.5         | W    |  |

| Channel temperature                    | Tch               | 150         | °C   |  |

| Storage temperature                    | Tstg              | -55 to +150 | °C   |  |

Note: 1. PW  $\leq 10\mu s$ , duty cycle  $\leq 1 \%$

2. When using the glass epoxy board (FR4 40 x 40 x 1.6 mm), PW $\leq$  10s

#### **Electrical Characteristics** (Ta = 25°C)

| Item                                      | Symbol             | Min   | Тур   | Max   | Unit | Test Conditions                                                 |

|-------------------------------------------|--------------------|-------|-------|-------|------|-----------------------------------------------------------------|

| Drain to source breakdown voltage         | $V_{(BR)DSS}$      | - 20  | _     | —     | V    | $I_{\rm D} = -10 \text{ mA}, V_{\rm GS} = 0$                    |

| Gate to source breakdown voltage          | $V_{(BR)GSS}$      | ± 10  | _     | _     | V    | $I_{\rm G} = \pm 100 \ \mu A, \ V_{\rm DS} = 0$                 |

| Gate to source leak current               | I <sub>GSS</sub>   | _     | _     | ± 10  | μΑ   | $V_{GS} = \pm 8 V, V_{DS} = 0$                                  |

| Zero gate voltege drain current           | I <sub>DSS</sub>   | —     | —     | - 10  | μΑ   | $V_{\rm DS} = -20$ V, $V_{\rm GS} = 0$                          |

| Gate to source cutoff voltage             | $V_{GS(off)}$      | - 0.5 | —     | - 1.5 | V    | $V_{\rm DS} = -10 \text{ V}, \text{ I}_{\rm D} = -1 \text{ mA}$ |

| Static drain to source on state           | $R_{DS(on)}$       | —     | 0.048 | 0.060 | Ω    | $I_{\rm D} = -3$ A, $V_{\rm GS} = -4$ V <sup>Note3</sup>        |

| resistance                                | $R_{DS(on)}$       | —     | 0.065 | 0.085 | Ω    | $I_{\rm D} = -3$ A, $V_{\rm GS} = -2.5$ V <sup>Note3</sup>      |

| Forward transfer admittance               | y <sub>fs</sub>    | 6     | 9.5   | —     | S    | $I_{\rm D} = -3$ A, $V_{\rm DS} = -10$ V <sup>Note3</sup>       |

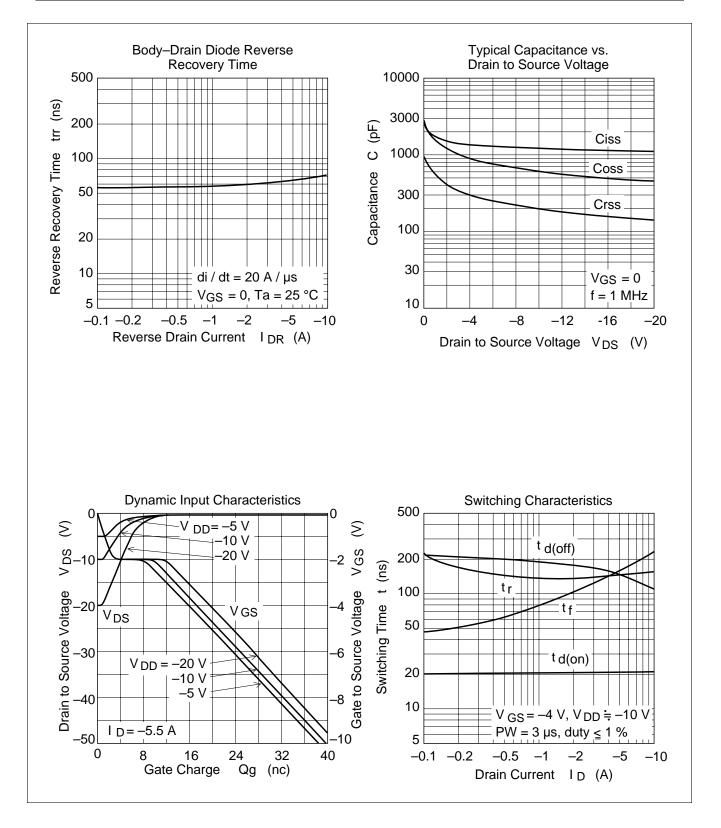

| Input capacitance                         | Ciss               |       | 1200  | _     | pF   | V <sub>DS</sub> = - 10 V                                        |

| Output capacitance                        | Coss               |       | 630   |       | pF   | $V_{GS} = 0$                                                    |

| Reverse transfer capacitance              | Crss               | —     | 200   | —     | pF   | f = 1MHz                                                        |

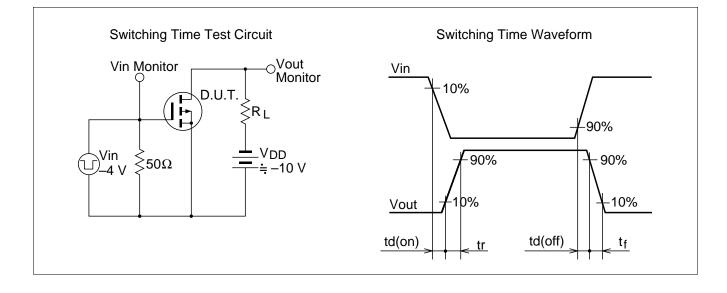

| Turn-on delay time                        | t <sub>d(on)</sub> | —     | 20    | —     | ns   | $V_{GS} = -4 V, I_{D} = -3 A$                                   |

| Rise time                                 | t,                 | _     | 120   | _     | ns   | $V_{DD} \cong -10 \text{ V}$                                    |

| Turn-off delay time                       | $t_{d(off)}$       |       | 175   | _     | ns   |                                                                 |

| Fall time                                 | t <sub>f</sub>     | _     | 140   | _     | ns   | _                                                               |

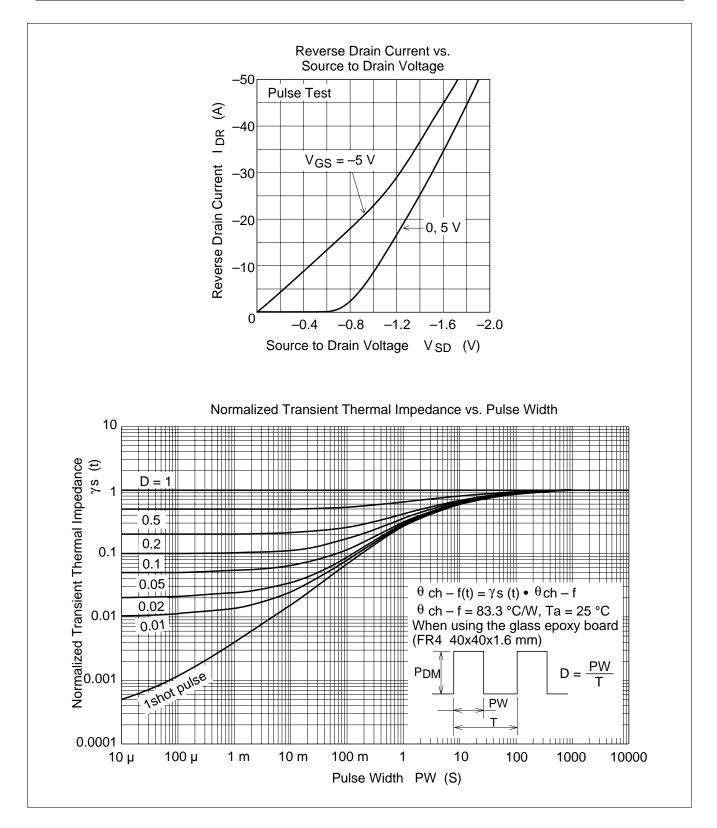

| Body-drain diode forward voltage          | $V_{\text{DF}}$    |       | - 0.9 | - 1.4 | V    | $IF = -5.5 A, V_{GS} = 0^{Note3}$                               |

| Body–drain diode reverse<br>recovery time | t <sub>rr</sub>    |       | 65    |       | ns   | IF = $-5.5$ A, V <sub>GS</sub> = 0<br>diF/ dt = 20 A/µs         |

Note: 3. Pulse test

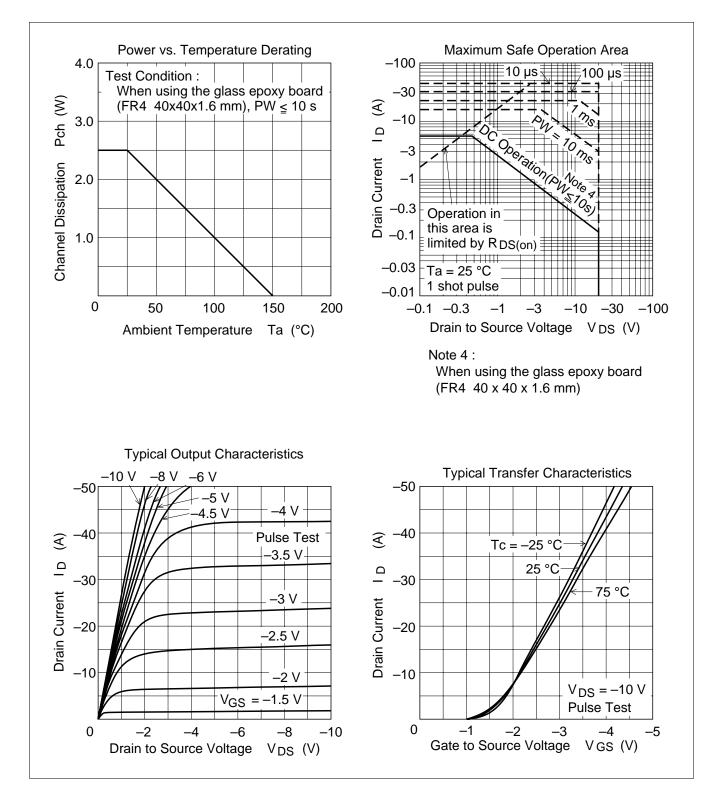

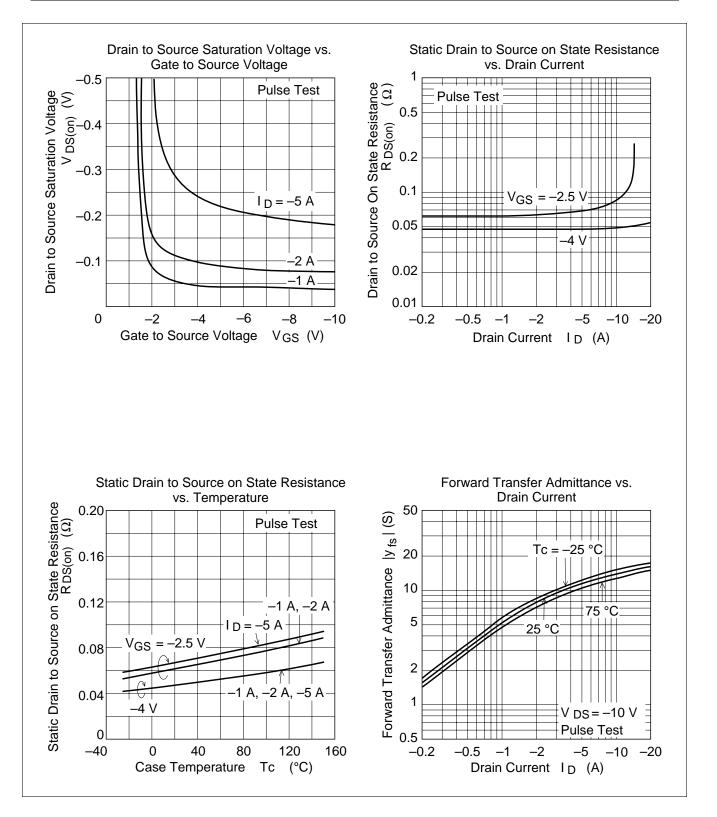

#### **Main Characteristics**

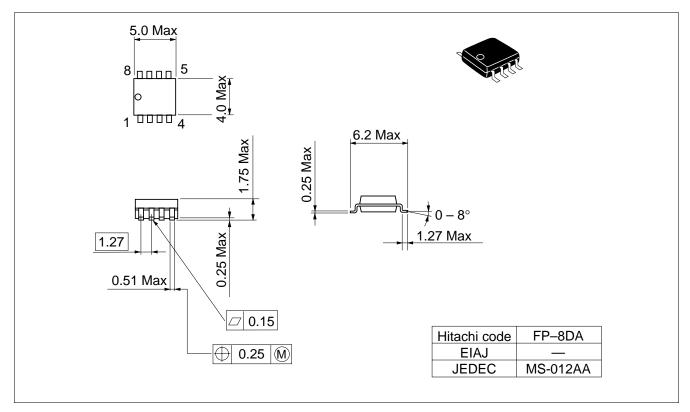

#### **Package Dimensions**

Unit: mm

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.