**SystemPower**<sup>™</sup>

### Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **General Description**

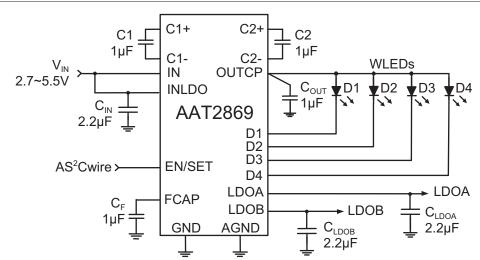

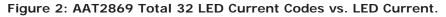

The AAT2869 is a low-noise, constant-frequency charge pump DC/DC converter that uses a dual-mode load switch (1x) and fractional (1.5x) conversion to maximize efficiency for white LED applications. The AAT2869 is capable of driving 4 white LEDs at a total of 124mA from a 2.7V to 5.5V input. The current sinks may be operated individually or in parallel for driving higher-current LEDs. A low external parts count (two 1 $\mu$ F flying capacitors and two small 1 $\mu$ F capacitors at IN and OUTCP) makes the AAT2869 ideally suited for small battery-powered applications. The fade-in/fade-out feature makes backlight turn-on/turn-off more visual comfortable. The AAT2869 also includes two 150mA low, drop-out linear regulators as additional power supplies for display and related camera power. The LDO voltage is also programmable.

AnalogicTech's Advanced Simple Serial Control<sup>TM</sup> (AS<sup>2</sup>Cwire<sup>TM</sup>) serial digital input is used to enable, disable and set the maximum LED current to one of 32 levels for the LEDs, to enable/disable the LDOs, and to set the LDO's output. The programmable LED current ranges from 31mA to 0.4mA.

Each output of the AAT2869 is equipped with built-in protection for short-circuit and auto-disable for load short-circuit conditions. The soft-start circuitry prevents excessive inrush current at charge pump start-up and mode transitions. The AAT2869 is available in the Pb-free, space-saving TQFN3.0x2.2-18L package, and operates over the -40°C to 85°C ambient temperature range.

#### Features

- 2.7V to 5.5V Supply Voltage Range

- Charge Pump for LED Driver

- Dual Mode 1x/1.5x

- Drives up to 4 LEDs with up to 31mA each

- Linear LED Output Control Options

- Maximum LED Current Set by AS<sup>2</sup>Cwire Interface, 32 Steps

- Fade In and Fade Out

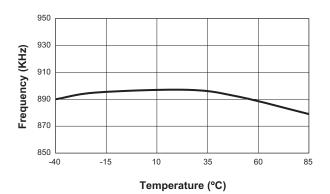

- 0.9MHz Constant Frequency

- Automatic Soft-Start Limits Inrush Current

- Dual 150mA LDOs

- Five Voltages with 1.2V, 1.5V, 1.8V, 2.8V, and 3.0V, Sixteen Combinations Set by AS<sup>2</sup>Cwire

- Enable Control Independently by AS<sup>2</sup>Cwire

- Integrated Discharge Resistor when Disabled

- < 1.0µA in Shutdown

- Short Circuit Protection

- Small Application Circuit

- -40°C to 85°C Temperature Range

- RoHS Compliant, Halogen-Free TQFN3.0x2.2-18 Package

### **Applications**

- Camera Phones

- Digital Still Cameras (DSCs)

- LED Photo Flash/Torch

- MP3 Players

- PDAs and Notebook PCs

- Smartphones

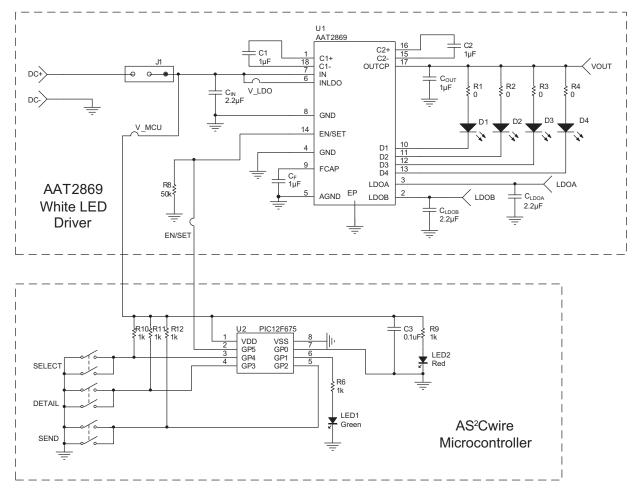

### **Typical Application**

**SystemPower**<sup>™</sup>

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

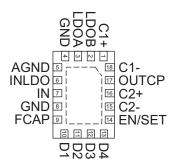

### **Pin Descriptions**

| Pin # | Symbol | Function | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | C1+    | I        | Flying capacitor C1 positive terminal. Connect a 1µF capacitor between C1+ and C1                                                                                                                                                                                                                                                                                  |

| 2     | LDOB   | 0        | LDOB output. Four output voltages can be programmed by AS <sup>2</sup> Cwire: 1.2V, 1.5V, 1.8V, and 2.5V. 2.8V is the default output voltage.                                                                                                                                                                                                                      |

| 3     | LDOA   | 0        | LDOA output. Four output voltages can be programmed by AS <sup>2</sup> Cwire: 1.5V, 1.8V, 2.5V, and 3.0V. 1.8V is the default output voltage.                                                                                                                                                                                                                      |

| 4,8   | GND    | PG       | Ground connection.                                                                                                                                                                                                                                                                                                                                                 |

| 5     | AGND   | AG       | Analog ground connection.                                                                                                                                                                                                                                                                                                                                          |

| 6     | INLDO  | Р        | Input power supply pin to LDOs. Connect this pin to IN. A $1\mu$ F capacitor is recommended for bypass use from this pin to ground.                                                                                                                                                                                                                                |

| 7     | IN     | Р        | Input power supply pin. Connect a 1µF bypass capacitor from this pin to ground.                                                                                                                                                                                                                                                                                    |

| 9     | FCAP   | I        | Fade-in/fade-out filter. Connect a $1\mu$ F capacitor to enable fade-in time of 1s at 20mA LED current each. If the fade-in/fade-out function is not used, leave this pin floating.                                                                                                                                                                                |

| 10    | D1     | I        | LED driver current sink D1. Connect LED cathode to this pin. If not used, please tie to OUTCP.                                                                                                                                                                                                                                                                     |

| 11    | D2     | I        | LED driver current sink D2. Connect LED cathode to this pin. If not used, please tie to OUTCP.                                                                                                                                                                                                                                                                     |

| 12    | D3     | I        | LED driver current sink D3. Connect LED cathode to this pin. If not used, please tie to OUTCP.                                                                                                                                                                                                                                                                     |

| 13    | D4     | I        | LED driver current sink D4. Connect LED cathode to this pin. If not used, please tie to OUTCP.                                                                                                                                                                                                                                                                     |

| 14    | EN/SET | I        | Charge pump enable/set. When in the low state, AAT2869 is powered down, and consumes less than 1 $\mu$ A. When EN/SET jumps from low to high, the charge pump is active and 20mA LED current each are set. The two LDOs are still inactive until data 3 is written to address 4 through the AS <sup>2</sup> Cwire interface. This pin should not be left floating. |

| 15    | C2-    | I        | Flying capacitor C2 negative terminal. Connect a 1µF capacitor between C1+ and C1                                                                                                                                                                                                                                                                                  |

| 16    | C2+    |          | Flying capacitor C2 positive terminal. Connect a 1µF capacitor between C2+ and C2                                                                                                                                                                                                                                                                                  |

| 17    | OUTCP  | 0        | Charge pump output. Connect a 1µF bypass capacitor between this pin to ground.                                                                                                                                                                                                                                                                                     |

| 18    | C1-    | I        | Flying capacitor C1 negative terminal. Connect a 1µF capacitor between C2+ and C2                                                                                                                                                                                                                                                                                  |

| EP    |        |          | Exposed pad. Connect to ground directly beneath the package.                                                                                                                                                                                                                                                                                                       |

### **Pin Configuration**

#### TQFN3.0x2.2 -18 (Top View)

**AAT2869**

SystemPower™

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### Absolute Maximum Ratings<sup>1</sup>

| Symbol               | Description                                         | Value                 | Units |

|----------------------|-----------------------------------------------------|-----------------------|-------|

| V <sub>IN</sub>      | Input Voltage                                       | -0.3 to 6.0           | V     |

| V <sub>EN</sub>      | EN to GND Voltage                                   | -0.3 to 6.0           | V     |

| V <sub>EN(MAX)</sub> | Maximum EN to Input Voltage or GND                  | V <sub>IN</sub> + 0.3 | V     |

| I <sub>OUT</sub>     | Maximum DC Output Current (continuous) <sup>2</sup> | 470                   | mA    |

| T                    | Maximum Junction Operating Temperature              | -40 to +150           | - °C  |

| T <sub>LEAD</sub>    | Maximum Soldering Temperature (at leads, 10 sec.)   | 300                   |       |

### **Thermal Information<sup>3</sup>**

| Symbol          | Description                                 | Value | Units |

|-----------------|---------------------------------------------|-------|-------|

| θ <sub>JA</sub> | Thermal Resistance from Junction to Ambient | 65.83 | °C/W  |

| θ <sub>JC</sub> | Thermal Resistance from Junction to Case    | 38.90 | °C/W  |

| P <sub>D</sub>  | Maximum Power Dissipation                   | 1.5   | W     |

1. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

2. Based on long-term current density limitation.

3. Mounted on an FR4 board.

SystemPower<sup>™</sup>

## Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### Electrical Characteristics<sup>1</sup>

$V_{IN}$  = 3.6V;  $C_{IN}$  = 1µF;  $C_{OUT}$  = 1µF;  $C_{FLY}$  = 1µF;  $C_{FLT}$  = 56nF;  $T_A$  = -40°C to 85°C, unless otherwise noted. Typical values are  $T_A = 25^{\circ}C$ .

| Symbol                                                | Description                                                         | Conditions                                                                        | Min  | Тур  | Max | Units |

|-------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|-----|-------|

| Input Powe                                            | er Supply                                                           |                                                                                   |      |      |     | 1     |

| V <sub>IN</sub>                                       | Input Voltage Range                                                 |                                                                                   | 2.7  |      | 5.5 | V     |

| V <sub>OUT (max)</sub>                                | Maximum Output Voltage                                              |                                                                                   |      | 5.5  |     | V     |

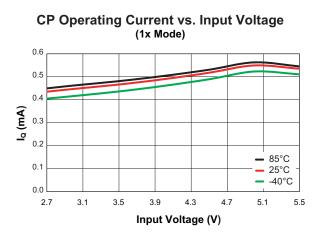

|                                                       | · · · · ·                                                           | 1x Mode, No Load Current, CP enabled                                              |      | 0.5  | 1   |       |

| I <sub>cc</sub>                                       | Operating Current                                                   | 1.5x Mode, $I_{D1}$ = FS, excluding $I_{D1}, \ V_{D2}$ = $V_{D3}$ = $V_{D4}$ = IN |      | 2    | 4   | mA    |

| SHDN(MAX)                                             | Shutdown Current                                                    | EN = 0                                                                            |      |      | 1.0 | μA    |

| Charge Pu                                             | np Section                                                          |                                                                                   |      |      |     |       |

| I <sub>OUT(MAX)</sub>                                 | Maximum Output Current                                              | $V_{\rm F} = 3.6 V$                                                               |      | 124  |     | mA    |

| f <sub>osc</sub>                                      | Oscillator Frequency                                                |                                                                                   |      | 0.9  |     | MHz   |

| t <sub>ss</sub>                                       | Charge Pump Setup Time                                              |                                                                                   |      | 100  |     | μs    |

| V <sub>IN_(TH)</sub>                                  | Charge Pump Mode Hysteresis                                         | 1.5x to 1x Transition; $I_{D1} = I_{D2} = I_{D3} = I_{D4} = 31 \text{mA}$         |      | 300  |     | mV    |

|                                                       | t Sink Outputs                                                      |                                                                                   |      |      |     |       |

|                                                       |                                                                     | Data 1, $T_{A} = 25^{\circ}C$                                                     | -10  |      | +10 |       |

| I <sub>DX</sub>                                       | I <sub>SINK</sub> Current Accuracy <sup>2</sup>                     | Data 32 only                                                                      |      | ±15  |     | 0/    |

| I <sub>DX(MATCH)</sub>                                | Current Marching Between Any Two<br>Current Sinks <sup>3</sup>      | V <sub>F</sub> ; D1:D4 = 3.6V                                                     | -5   |      | +5  | %     |

| V <sub>D_(TH)</sub>                                   | Charge Pump Mode Transition                                         | 1x to 1.5x Mode, $I_{D1} = I_{D2} = I_{D3} = I_{D4} = 31$ mA                      |      | 120  | 250 | mV    |

| AS <sup>2</sup> Cwire C                               | ontrol and EN/SET Control                                           | ·                                                                                 |      |      |     |       |

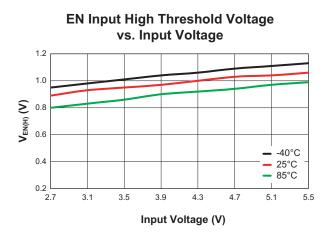

| V <sub>EN/SET (L)</sub>                               | EN/SET                                                              |                                                                                   |      |      | 0.4 | V     |

| V <sub>EN/SET (H)</sub>                               | EN/SET                                                              |                                                                                   | 1.4  |      |     | V     |

| ILEAK                                                 | EN/SET Input Leakage                                                |                                                                                   | -1   |      | 1   | mA    |

| t <sub>EN/SET(LOW)</sub>                              | EN/SET Input Low Time                                               |                                                                                   | 0.3  |      | 75  | μs    |

| t <sub>EN/SET(HI_MIN)</sub>                           | EN/SET Minimum High Time                                            |                                                                                   |      | 50   |     | ns    |

| t <sub>EN/SET(HIMAX)</sub>                            | EN/SET Maximum High Time                                            |                                                                                   |      |      | 75  | μs    |

| t <sub>EN/SET(OFF)</sub>                              | EN/SET Input Off Timeout <sup>4</sup>                               |                                                                                   |      |      | 500 | us.   |

| t <sub>EN/SET(LAT)</sub>                              | EN/SET Latch Timeout <sup>₅</sup>                                   |                                                                                   |      |      | 500 | μs    |

| Linear Reg                                            |                                                                     | 1                                                                                 |      |      | 1   |       |

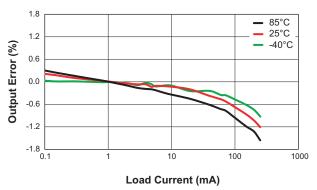

| ΔV <sub>OUT[A/B]</sub> /                              | LDO <sub>A</sub> , LDO <sub>B</sub> Output Voltage                  | $I_{OUT} = 1 \text{mA to } 150 \text{mA}; T_A = 25^{\circ}\text{C}$               | -2   |      | 2   | %     |

| V <sub>OUT[A/B]</sub>                                 | Tolerance                                                           | $I_{OUT} = 1$ mA to 150mA; $T_A = -40^{\circ}$ C to $+85^{\circ}$ C               | -3.0 |      | 3.0 | %     |

| I <sub>OUT[A/B](MAX)</sub>                            | LDO <sub>A</sub> , LDO <sub>B</sub> Maximum Load Current            |                                                                                   | 200  |      | -   | mA    |

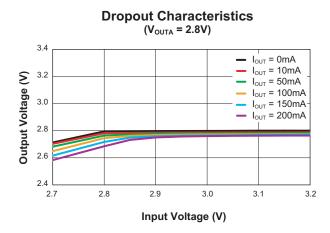

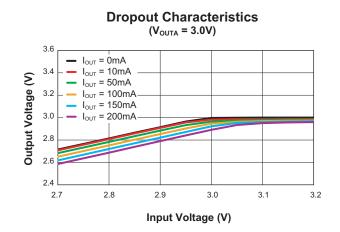

| V <sub>OUT[A/B](DO)</sub>                             | LDO <sub>A</sub> , LDO <sub>B</sub> <sup>6</sup>                    | $V_{OUT[A/B]} \ge 3.0V; I_{OUT} = 150mA$                                          |      | 100  | 150 | mV    |

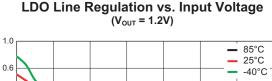

| $\frac{\Delta V_{OUT}}{V_{OUT}} \times \Delta V_{IN}$ | Line Regulation                                                     | $V_{IN} = (V_{OUT[A/B]} + 1V)$ to 5V                                              |      | 0.09 |     | %/V   |

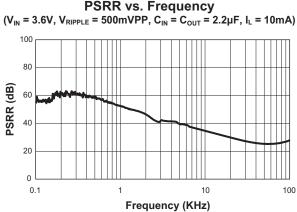

| PSRR <sub>[A/B]</sub>                                 | LDO <sub>A</sub> , LDO <sub>B</sub> Power Supply Rejection<br>Ratio | I <sub>OUT[A/B]</sub> =10mA, 1kHz                                                 |      | 50   |     | dB    |

| R <sub>OUT_(DCHG)</sub>                               | LDO <sub>A</sub> , LDO <sub>B</sub> Auto-Discharge<br>Resistance    |                                                                                   |      | 720  |     | Ω     |

| Thermal                                               |                                                                     |                                                                                   |      |      |     |       |

| T <sub>SD</sub>                                       | T, Thermal Shutdown Threshold                                       |                                                                                   |      | 140  |     | °C    |

| T <sub>HYS</sub>                                      | T <sub>J</sub> Thermal Shutdown Hysteresis                          |                                                                                   |      | 20   |     | °C    |

1. The AAT2869 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assuredby design, characterization, and correlation with statistical process controls.

2. Determined by the average of all active channels.

- 5. The EN/SET pin must remain logic high (greater than V<sub>in</sub>) for the duration of longer than 500µs to guarantee the latch timeout.

6.  $V_{DO[A/B]}$  is defined as  $V_{IN} - LDO[A/B]$  when LDO[A/B] is 98% of nominal.

Current matching is defined as the deviation of any sink current from the average of all active channels.

The EN/SET pin must remain logic low (less than V<sub>IL</sub>) for the duration of longer than 500µs to guarantee the off timeout.

**AAT2869**

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

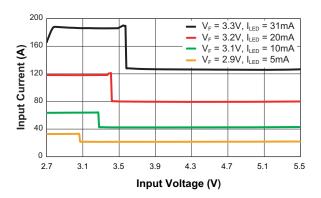

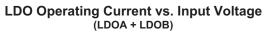

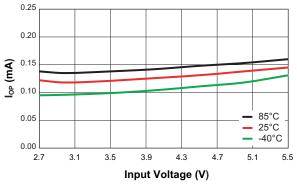

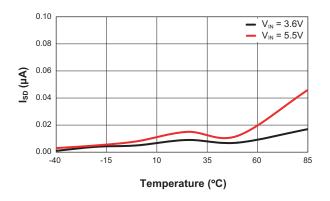

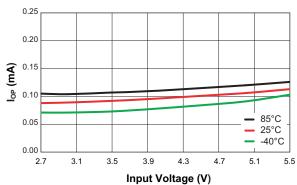

### **Typical Characteristics**

**CP Input Current vs. Input Voltage**

**CP** Operating Current vs. Input Voltage (1.5x Mode) 3.0 2.5 2.0 la (mA) 1.5 1.0 85°C 0.5 25°C -40°C 0.0 3.1 3.5 4.7 5.1 5.5 2.7 3.9 4.3 Input Voltage (V)

Shutdown Current vs. Temperature

LDO Operating Current vs. Input Voltage (LDOA Only)

5

**SystemPower**<sup>™</sup>

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Typical Characteristics**

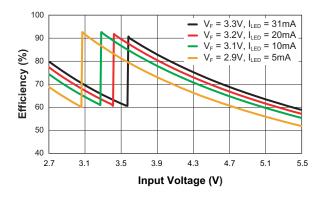

#### **CP Efficiency vs. Input Voltage**

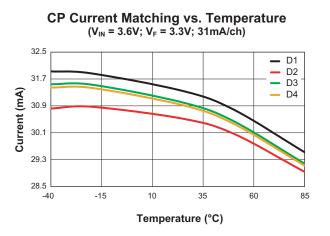

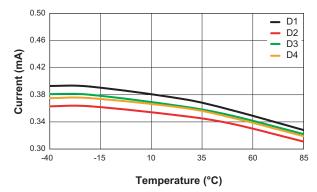

#### CP Current Matching vs. Temperature (V<sub>IN</sub> = 3.6V; V<sub>F</sub> = 3.3V; 0.5mA/ch)

LDO Load Regulation vs. Output Current (V<sub>out</sub> = 1.2V)

Frequency vs. Temperature

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Typical Characteristics**

**PRODUCT DATASHEET**

**AAT2869**

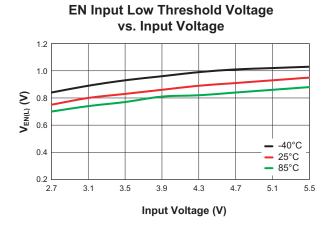

EN/SET Input Latch Time vs. Input Voltage

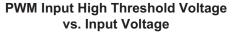

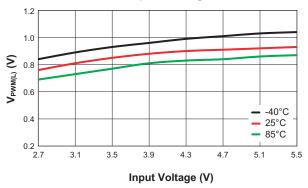

PWM Input Low Threshold Voltage vs. Input Voltage

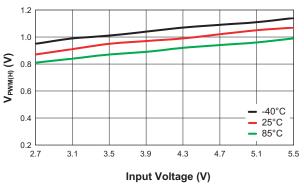

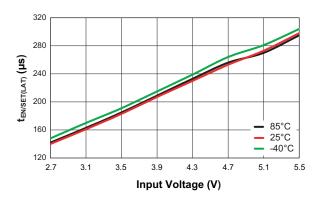

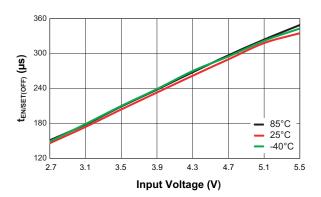

EN/SET Input Off Time vs. Input Voltage

**AAT2869**

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Typical Characteristics**

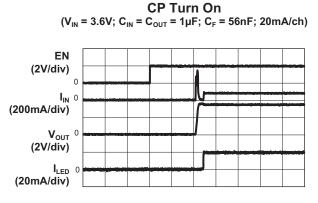

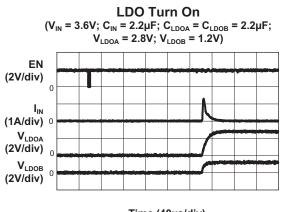

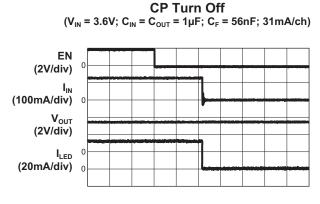

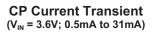

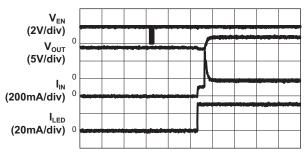

Time (100µs/div)

**CP Current Transient** (V<sub>IN</sub> = 3.6V; 31mA to 0.5mA)

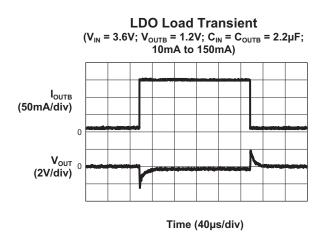

Time (40µs/div)

Time (40µs/div)

Time (100µs/div)

Time (100µs/div)

Time (40µs/div)

SystemPower™

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Typical Characteristics**

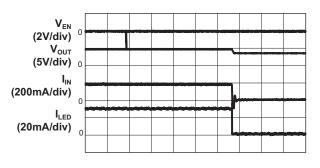

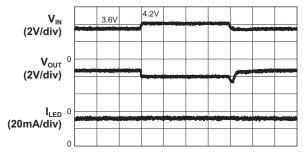

Time (1ms/div)

Time (1ms/div)

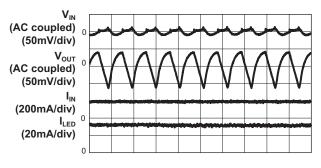

1.5x Mode Operating Characteristics  $(V_{IN} = 3.2V; C_{IN} = C_{OUT} = 1\mu F; 31mA/ch)$

Time (1µs/div)

**CP Mode Transient** (V<sub>IN</sub> = 3.6V to 4.2V;  $C_{IN} = C_{OUT} = 1\mu$ F; 31mA/ch)

Time (100µs/div)

**PSRR vs. Frequency**

**AAT2869**

SystemPower™

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Typical Characteristics**

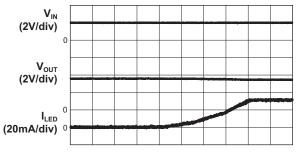

Fade In From CP Disable To Enable ( $V_{IN} = 3.6V$ ;  $C_{IN} = C_F = 1\mu F$ ; 31mA/ch)

Time (400ms/div)

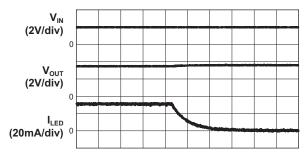

Fade Out From CP Enable To Disable  $(V_{IN} = 3.6V; C_{IN} = C_F = 1\mu F; 31mA/ch)$

Time (400ms/div)

**AAT2869**

SystemPower™

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

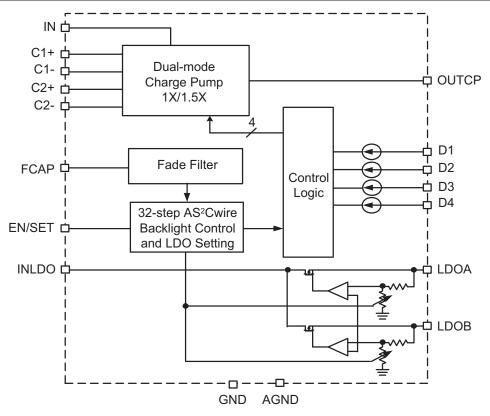

### **Functional Block Diagram**

### **Functional Description**

The AAT2869 is a high efficiency charge pump white LED driver for portable applications. It can drive up to 4 white LEDs. The two integrated LDOs can provide 1.2V, 1.5V, 1.8V, 2.8V and 3.0V output voltages in 16 combinations with up to 150mA load capability.

The AAT2869's charge pump is a fractional charge pump and can multiply the input voltage by 1 or 1.5 times. The charge pump switches at a fixed frequency of 0.9MHz. The internal mode-selection circuit automatically switches the mode between 1x and 1.5x based on the input voltage, white LED forward voltage V<sub>F</sub>, and the programmed LED current. This mode switching maximizes the efficiency throughout the entire LED load range. When the input voltage is high enough, the charge pump operates in 1x mode (no charge pump) to provide maximum efficiency. If the input voltage is too low to supply the programmed LED current, typically when the battery discharges and the voltage decays, the 1.5x charge pump mode is automatically enabled. When the battery is connected to a charger and the input voltage rises sufficiently, the device will switch back to 1x mode.

Six registers are designed for charge pump enable/disable control, LED current programming, fade-in, fadeout enable/disable, two LDOs enable/disable control and LDO output voltage combination setting through the AS<sup>2</sup>Cwire interface. After writing address 3, the LED current value is programmed by the EN/SET serial data AS<sup>2</sup>Cwire interface. The AS<sup>2</sup>Cwire interface records rising edges of the EN/SET pin and decodes them into 32 individual current level settings from 0.4mA to 31mA. To get a visual fade in and fade out effect, a small external capacitor is used to set LED current rising exponentially to the programmed value and decreasing exponentially to the programmed floor LED current level.

The AAT2869 has five registers with up to four bits each to control LED backlighting enable/disable, LED current, enable/disable for the two LDOs, output voltages, etc. as shown in Table 1. Each data register can be written with 1 to 16 EN/SET rising edges. Some bits are internally reserved and should only be written with data 0, such as address 0, bit D0, D1 and D3, etc. in order to avoid unexpected results. Address 0 is the default address.If EN/SET is pulled high after a low level lasting for at least

**SystemPower**<sup>™</sup>

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

#### AS<sup>2</sup>Cwire Registers

| Address     |                        | Data                  |        |        |          |          |                        |

|-------------|------------------------|-----------------------|--------|--------|----------|----------|------------------------|

| Number      | EN/SET Rising<br>Edges | Function              | D3     | D2     | D1       | D0       | EN/SET Rising<br>Edges |

| 0 [Default] | 17                     | Backlight Enable      | 0      | BL_ENB | FADE_EN  | FADE_IN  | 1 ~ 8                  |

| 1           | 18                     | Backlight Floor Level | 0      | 0      | FLOOR[1] | FLOOR[2] | 1 ~ 4                  |

| 2           | 19                     | Backlight MSB         | 0      | 0      | 0        | BL[4]    | 1 or 2                 |

| 3           | 20                     | Backlight LSBs        | BL[3]  | BL[2]  | BL[1]    | BL[0]    | 1 ~ 16                 |

| 4           | 21                     | LDO Enable Control    | 0      | 0      | LDOA_EN  | LDOB_EN  | 1 ~ 4                  |

| 5           | 22                     | LDO Output Voltage    | LDO[3] | LDO[2] | LDO[1]   | LDO[0]   | 1 ~ 16                 |

Table 1: AAT2869 AS<sup>2</sup>Cwire Registers.

500 $\mu s$   $t_{\text{OFF}}$  time, data 0 is written to address 0 and LED backlighting is enabled with default 20mA LED current each.

#### Address 0 – Backlight Enable and Fade Enable

The BL\_ENB bit of address register 0 is adopted to enable or disable the white LED backlighting. 0 enables backlighting; 1 disables backlighting. The FADE\_EN and FADE\_IN bits are adopted to enable/disable the fade-in/ fade-out function. The other bits of the register should be written with data 0.

For example, to enable a 20mA fade-in visual effect, send 4 data EN/SET rising edges after an EN/SET low lasting for  $t_{LAT}$  or send 4 data EN/SET rising edges after 17 address EN/SET rising edges.

#### Address 1 – Backlight Fade Floor Settings

When the fade-out function is enabled, the LED current decreases to the programmed floor level instead of decreasing to zero. The other bits of the register should be written with data 0.

#### Addresses 2 and 3 – LED Current Level Settings

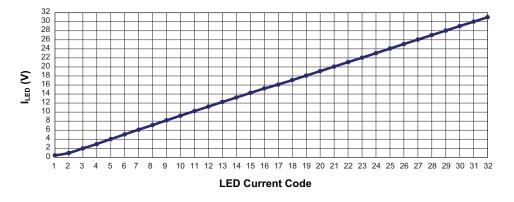

The LED current level is set via the AS<sup>2</sup>Cwire interface in a linear scale by 32 codes where the LED current of each higher code is higher than the lower one, as shown in Table 4. In this manner, the LED current decreases linearly with each decreasing code.

| Description                          | BL_ENB | FADE_EN | FADE_IN | EN/SET Rising Edges |

|--------------------------------------|--------|---------|---------|---------------------|

| Backlight on [default]               | 0      | 0       | 0       | 1                   |

| Backlight on                         | 0      | 0       | 1       | 2                   |

| Backlight on, Fade enabled: fade out | 0      | 1       | 0       | 3                   |

| Backlight on, Fade enabled: fade in  | 0      | 1       | 1       | 4                   |

| Backlight off                        | 1      | 0/1     | 0/1     | 5 ~ 8               |

#### Table 2: AS<sup>2</sup>Cwire Register Address 0.

| Description           | FLOOR[1] | FLOOR[2] |

|-----------------------|----------|----------|

| Floor 0.5mA [default] | 0        | 0        |

| Floor 1.0mA           | 0        | 1        |

| Floor 2.0mA           | 1        | 0        |

| Floor 3.0mA           | 1        | 1        |

Table 3: AS<sup>2</sup>Cwire Register Address 1.

SystemPower™

### Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

| LED              | Address 2 |     | Addr | ess 3 |     | LED               |

|------------------|-----------|-----|------|-------|-----|-------------------|

| Current<br>Codes | BL4       | BL3 | BL2  | BL1   | BLO | Current<br>(mA)   |

| 1                | 0         | 0   | 0    | 0     | 0   | 0.4               |

| 2                | 0         | 0   | 0    | 0     | 1   | 0.9               |

| 3                | 0         | 0   | 0    | 1     | 0   | 1.9               |

| 4                | 0         | 0   | 0    | 1     | 1   | 2.9               |

| 5                | 0         | 0   | 1    | 0     | 0   | 3.9               |

| 6                | 0         | 0   | 1    | 0     | 1   | 4.9               |

| 7                | 0         | 0   | 1    | 1     | 0   | 6.0               |

| 8                | 0         | 0   | 1    | 1     | 1   | 7.0               |

| 9                | 0         | 1   | 0    | 0     | 0   | 8.0               |

| 10               | 0         | 1   | 0    | 0     | 1   | 9.0               |

| 11               | 0         | 1   | 0    | 1     | 0   | 10.0              |

| 12               | 0         | 1   | 0    | 1     | 1   | 11.0              |

| 13               | 0         | 1   | 1    | 0     | 0   | 12.0              |

| 14               | 0         | 1   | 1    | 0     | 1   | 13.0              |

| 15               | 0         | 1   | 1    | 1     | 0   | 14.0              |

| 16               | 0         | 1   | 1    | 1     | 1   | 15.0              |

| 17               | 1         | 0   | 0    | 0     | 0   | 16.0              |

| 18               | 1         | 0   | 0    | 0     | 1   | 17.0              |

| 19               | 1         | 0   | 0    | 1     | 0   | 18.0              |

| 20               | 1         | 0   | 0    | 1     | 1   | 19.0              |

| 21               | 1         | 0   | 1    | 0     | 0   | 20.0<br>[default] |

| 22               | 1         | 0   | 1    | 0     | 1   | 21.0              |

| 23               | 1         | 0   | 1    | 1     | 0   | 22.0              |

| 24               | 1         | 0   | 1    | 1     | 1   | 23.0              |

| 25               | 1         | 1   | 0    | 0     | 0   | 24.0              |

| 26               | 1         | 1   | 0    | 0     | 1   | 25.0              |

| 27               | 1         | 1   | 0    | 1     | 0   | 26.0              |

| 28               | 1         | 1   | 0    | 1     | 1   | 27.0              |

| 29               | 1         | 1   | 1    | 0     | 0   | 28.0              |

| 30               | 1         | 1   | 1    | 0     | 1   | 29.0              |

| 31               | 1         | 1   | 1    | 1     | 0   | 30.0              |

| 32               | 1         | 1   | 1    | 1     | 1   | 31.0              |

Table 4: AS<sup>2</sup>Cwire Register Addresses 2 and 3<sup>1</sup>.

#### Address 4 – LDO Enable Control

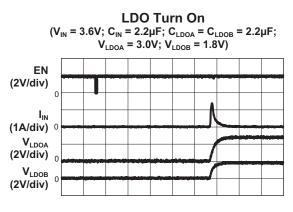

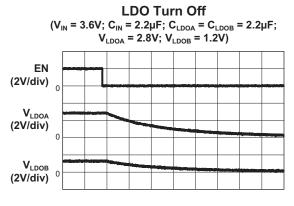

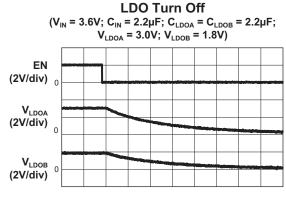

The AAT2869 includes two low dropout (LDO) linear regulators. These regulators are powered from the battery and produce a fixed output voltage which is set using the AS<sup>2</sup>Cwire serial interface. AS<sup>2</sup>Cwire address register 4 turns the two LDOs on/off through the AS<sup>2</sup>Cwire serial interface. An internal resistor is used to discharge the LDO output voltage when the LDO is disabled.

|                                    | Data    |         |                        |  |  |  |

|------------------------------------|---------|---------|------------------------|--|--|--|

| Description                        | LDOA_EN | LDOB_EN | EN/SET<br>Rising Edges |  |  |  |

| LDOA Off,<br>LDOB Off<br>[Default] | 0       | 0       | 1                      |  |  |  |

| LDOA Off,<br>LDOB On               | 0       | 1       | 2                      |  |  |  |

| LDOA On,<br>LDOB Off               | 1       | 0       | 3                      |  |  |  |

| LDOA On,<br>LDOB On                | 1       | 1       | 4                      |  |  |  |

| Table 5: AS <sup>2</sup> Cwire | Register | Address 4. |

|--------------------------------|----------|------------|

|--------------------------------|----------|------------|

#### Address 5 - LDO Voltage Output Setting

Register address 5 is used to set the LDOA and LDOB output voltage levels. Sixteen combinations of the two LDOs can be programmed by the 4 bits of the register. LDOA can be set to one of four levels: 1.5V, 1.8V, 2.8V, or 3.0V. LDOB can be set to one of four levels: 1.2V, 1.5V, 1.8V, or 2.8V. The LDO regulators require only a small 2.2µF ceramic output capacitor for stable operation. If improved load transient response is required, larger-valued capacitors can be used without stability degradation.

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

|                                    | Data   |        |        |        |                     |

|------------------------------------|--------|--------|--------|--------|---------------------|

| Description                        | LDO[3] | LDO[2] | LDO[1] | LDO[0] | EN/SET Rising Edges |

| LDOA = 3.0V, LDOB = 2.8V           | 0      | 0      | 0      | 0      | 1                   |

| LDOA = 3.0V, LDOB = 1.8V           | 0      | 0      | 0      | 1      | 2                   |

| LDOA = 3.0V, LDOB = 1.5V           | 0      | 0      | 1      | 0      | 3                   |

| LDOA = 3.0V, LDOB = 1.2V           | 0      | 0      | 1      | 1      | 4                   |

| LDOA = 2.8V, LDOB = 2.8V           | 0      | 1      | 0      | 0      | 5                   |

| LDOA = 2.8V, LDOB = 1.8V           | 0      | 1      | 0      | 1      | 6                   |

| LDOA = 2.8V, LDOB = 1.5V           | 0      | 1      | 1      | 0      | 7                   |

| LDOA = 2.8V, LDOB = 1.2V           | 0      | 1      | 1      | 1      | 8                   |

| LDOA = 1.8V, LDOB = 2.8V [default] | 1      | 0      | 0      | 0      | 9                   |

| LDOA = 1.8V, LDOB = 1.8V           | 1      | 0      | 0      | 1      | 10                  |

| LDOA = 1.8V, LDOB = 1.5V           | 1      | 0      | 1      | 0      | 11                  |

| LDOA = 1.8V, LDOB = 1.2V           | 1      | 0      | 1      | 1      | 12                  |

| LDOA = 1.5V, LDOB = 2.8V           | 1      | 1      | 0      | 0      | 13                  |

| LDOA = 1.5V, LDOB = 1.8V           | 1      | 1      | 0      | 1      | 14                  |

| LDOA = 1.5V, LDOB = 1.5V           | 1      | 1      | 1      | 0      | 15                  |

| LDOA = 1.5V, LDOB = 1.2V           | 1      | 1      | 1      | 1      | 16                  |

Table 6: AS<sup>2</sup>Cwire Register Address 5 LDOA and LDOB Output Voltage Settings.

#### AS<sup>2</sup>Cwire EN/SET Interface

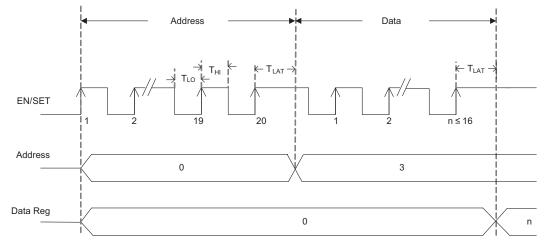

The AAT2869 is dynamically programmable using the AS<sup>2</sup>Cwire single-wire interface. AS<sup>2</sup>Cwire records rising edges detected at the EN/SET pin to address and load the data registers. The timing diagram in Figure 1 shows the typical transmission protocol.

The AAT2869 latches address or data after the EN/SET input has been held high for time  $t_{LAT}$  (500µs) through the AS<sup>2</sup>Cwire interface. Address and data are differentiated by the number of EN/SET rising edges. An address has from 17 to 22 EN/SET rising edges; data has from 1 to 16 EN/ SET rising edges. A typical AS<sup>2</sup>Cwire interface write protocol is a burst of EN/SET rising edges identifying a particular address, followed by a pause with EN/SET held high for the  $t_{LAT}$  timeout period, then a burst of rising edges signifying data, and another  $t_{LAT}$  timeout after the data has been sent. Once an address is set, multiple writes to that address are allowed since the address is not reset after each write. Address edges are needed when changing the address, or writing to an address other than the default after shutdown. Address 0 is the default address after shutdown. If the part is enabled with only one rising edge after shutdown, then Address 0 will be programmed and LED backlight channels BL1-BL4 will be enabled to the default setting of 20mA each.

When EN/SET is held low for a time longer than  $t_{OFF}$  (500µs), the AAT2869 enters shutdown mode with the charge pump and both LDOs all turning off and draws less than 1µA of current from IN. At shutdown, the data and address registers are reset to 0.

#### Short Circuit and Over-Temperature Protection

The AAT2869 integrates short circuit protection to limit the input current in case of the charge pump output or the two LDO outputs are shorted to ground by fault. The backlight and the two LDOs will recover to normal operation once the fault is removed.

The AAT2869 also includes over-temperature protection circuitry. When the junction temperature is too high, the over-temperature protection circuitry is active and the IC enters standby mode, turning off the LED current and LDO outputs. When the fault is removed, the LED backlighting and the LDO outputs all recover.

**AAT2869**

SystemPower™

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

Figure 1: AS<sup>2</sup>Cwire Timing Diagram.

### **Application Information**

#### LED Selection

The AAT2869 is designed to drive high intensity white flash LEDs with forward voltages up to 4.4V. Though AAT2869 switches the charge pump mode 1x and 1.5x mode automatically to maintain the continuous LED current accuracy, to obtain higher efficiency lower  $V_F$  white LEDs should be selected.

#### Maximum LED Current Setting

32 maximum LED current codes from 0.4mA to 31mA can be set by two registers using addresses 2 and 3 through the EN/SET AS<sup>2</sup>Cwire interface as shown in Figure 2. To obtain linear LED current change, the AAT2869 will not change the LED current when only address 2 is written. The control circuit only loads data to the address 2 and address 3 registers after address 3 is written to determine which LED current code is programmed. The address 2 BL4 default value is 0 after one EN/SET rising edge.

Codes 1 to 16 with LED current from 0.4mA to 15mA can be set after sending 20 rising edges to address 3 and sending data with 1 to 16 rising edges after  $t_{LAT}$ . Codes 17 to 32 with LED current from 16mA to 31mA can be obtained after writing both address 2 and address 3. This operation is performed using the following steps:

- 1. Select address 2 by sending 19 rising edges to EN/SET and holding high for  $t_{\text{LAT}}\!\!\!\!;$

- 2. Send data 1 to set DL4 by sending 2 rising edges and holding high for  $t_{\text{LAT}}$

- 3. Select address 3 by sending 20 rising edges on EN/ SET and holding high for  $t_{\text{LAT}}\!\!\!\!;$

- 4. Send data 15 to enable LED current code 32 setting by sending 16 rising edges on EN/SET and holding high for  $t_{\text{LAT}}$ .

**SystemPower**<sup>™</sup>

### Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

#### Fade In and Fade Out

AAT2869 adopts several linear current change segments to approximate the exponential LED current change to get a fashion fade-in visual effect. The fade-in time is mainly determined by the external capacitor  $C_F$  and the charge current. The following formula can be used to estimate how much capacitance is suitable for an expected fade-in time.

$$C_{F} (\mu F) = \frac{t_{FADE-IN}}{48.7 \cdot I_{LED}}$$

For example, for a 1 second fade-in time at 20mA LED current each, a 1µF  $C_F$  capacitor can be used. Table 7 shows the fade-in time with  $C_F$  of 560nF and 1µF  $C_F$  at different LED current settings.

| C <sub>F</sub> (μF) | I <sub>LED</sub> (mA) | t <sub>FADE-IN</sub> (s) |

|---------------------|-----------------------|--------------------------|

| 0.56                | 10                    | 0.273                    |

| 0.56                | 15                    | 0.409                    |

| 0.56                | 20                    | 0.545                    |

| 0.56                | 25                    | 0.682                    |

| 0.56                | 30                    | 0.818                    |

| 1                   | 10                    | 0.5                      |

| 1                   | 15                    | 0.7                      |

| 1                   | 20                    | 1.0                      |

| 1                   | 25                    | 1.2                      |

| 1                   | 30                    | 1.5                      |

# Table 7: Fade-in Time Examples at Different $C_F$ and LED Current Settings.

Fade-out time is determined by the discharging time of the  $C_F$  through an internal 200k $\Omega$  resistor R. For example, 1µF  $C_F$  generates 800ms fade-out time; 560nF  $C_F$  generates 450ms fade-out time.

$$t_{FADE-OUT}(s) = 4 \cdot RC_F = 0.8 \cdot C_F$$

#### **Charge Pump Efficiency**

#### 1x Mode Efficiency

The AAT2869's 1x mode is operational at all times and functions alone to enhance device power conversion efficiency when  $V_{IN}$  is higher than the voltage across the load. When in 1x mode, voltage conversion efficiency is defined as output power divided by input power.

$$\eta = \frac{\mathsf{P}_{\mathsf{OUT}}}{\mathsf{P}_{\mathsf{IN}}}$$

The ideal efficiency ( $\eta$ ) in 1X charge pump mode can be expressed as:

PRODUCT DATASHEET

**AAT286**

$$\eta = \frac{\mathsf{P}_{\mathsf{OUT}}}{\mathsf{P}_{\mathsf{IN}}} = \frac{\mathsf{V}_{\mathsf{F}} \cdot \mathsf{I}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{IN}}} \approx \frac{\mathsf{V}_{\mathsf{F}}}{\mathsf{V}_{\mathsf{IN}}}$$

-or-

$$\eta(\%) = 100 \left( \frac{V_{F}}{V_{IN}} \right)$$

#### 1.5x Charge Pump Mode Efficiency

The AAT2869 contains a fractional charge pump which will boost the input supply voltage in the event where  $V_{IN}$  is less than the voltage required to supply the output. The efficiency ( $\eta$ ) can be simply defined as a linear voltage regulator with an effective output voltage that is equal to one and one half times the input voltage. Efficiency ( $\eta$ ) for an ideal 1.5x charge pump can be calculated by the following equation:

$$\eta = \frac{\mathsf{P}_{\mathsf{OUT}}}{\mathsf{P}_{\mathsf{IN}}} = \frac{\mathsf{V}_{\mathsf{F}} \cdot \mathsf{I}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{IN}}} = \frac{\mathsf{V}_{\mathsf{F}} \cdot \mathsf{I}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}} \cdot 1.5 \cdot \mathsf{I}_{\mathsf{OUT}}} \approx \frac{\mathsf{V}_{\mathsf{F}}}{1.5 \cdot \mathsf{V}_{\mathsf{IN}}}$$

-or

$$\eta(\%) = 100 \left( \frac{V_{\text{OUT}}}{1.5 \cdot V_{\text{IN}}} \right)$$

#### **Capacitor Selection**

The AAT2869 requires seven capacitors in its typical application:  $C_{IN}$ ,  $C_{OUT}$ ,  $C_1$ ,  $C_2$ ,  $C_{FLT}$  and  $C_{LOA}$ ,  $C_{LOB}$ . Among them,  $C_{IN}$ ,  $C_1$ ,  $C_2$  and  $C_{OUT}$  are required for 1.5x mode charge pump operation. 1µF surface-mount multi-layer ceramic capacitors with low (less than 100m $\Omega$ ) equivalent series resistance (ESR) are recommended. Though ESR of the capacitors will not affect the ability of the capacitor to store energy, it has a large effect on performance such as equivalent output resistance, efficiency, and output voltage ripple of the charge pump. Tantalum and aluminum electrolytic capacitors are not recommended due to their high ESR. A value of 2.2µF or above is required for the LDOA and LDOB output capacitors for proper load voltage regulation and stable operation. Some recommended capacitors are listed in Table 6.

Downloaded from Elcodis.com electronic components distributor

AT286

SystemPower™

### Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

| Manufacturer | Part Number       | Value (µF) | Voltage | Temp. Co. | ESR (mΩ) at 1MHz | Case |

|--------------|-------------------|------------|---------|-----------|------------------|------|

|              | GRM188R61C105KA93 | 1          | 16      | X5R       | 18               | 0603 |

| Murata       | GRM185R60J105KE21 | 1          | 6.3     | X5R       | 16               | 0603 |

|              | GRM188R61A225KE34 | 2.2        | 10      | X5R       | 12               | 0603 |

| TDK -        | C1608X5R1C105K    | 1          | 16      | X5R       | 5.5              | 0603 |

|              | C1608X5R0J225K    | 2.2        | 6.3     | X5R       | 3.3              | 0603 |

| Table 6: | AAT2869 | Recommended | Capacitors. |

|----------|---------|-------------|-------------|

|----------|---------|-------------|-------------|

For most applications, ceramic capacitors with X5R temperature characteristic are preferred for AAT2869 application. These capacitors have good capacitor tolerance over wide temperature (X5R:  $\pm 15\%$  over  $-55^{\circ}$ C to  $+85^{\circ}$ C). Capacitors with Y5V or Z5U temperature characteristic are generally not recommended for AAT2869. They have wide capacitance tolerance over special temperature (Y5V: +22%, -82% over  $-30^{\circ}$ C to  $+85^{\circ}$ C, Z5U: +22%, -56% over  $+10^{\circ}$ C to  $+85^{\circ}$ C).

Careful selection of the four external capacitors  $C_{IN}$ ,  $C_1$ ,  $C_2$ ,  $C_{OUT}$  is important because they will affect turn on time, output ripple and transient performance. Optimum performance will be obtained when low ESR (<100m $\Omega$ ) ceramic capacitors are used. In general, low ESR may be defined as less than 100m $\Omega$ . A capacitor value of 1uF for all four capacitors is a good starting point when choosing capacitors. If the LED current sinks are only programmed for light current levels, then the capacitor size may be decreased.

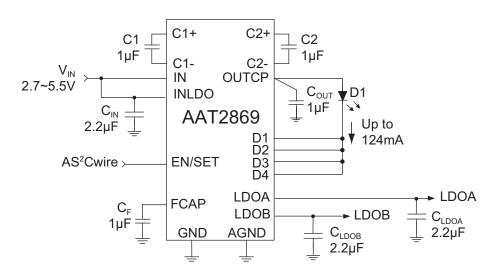

#### **Additional Applications**

The current sinks of the AAT2869 can be combined to drive higher current levels through a single LED. As an example, Figure 3 shows the AAT2869 driving a single white LED with up to 124mA by connecting D1-D4 together to the LED cathode.

#### Printed Circuit Board Layout Recommendations

When designing a PCB for the AAT2869, the key requirements are:

- 1. Place the flying capacitors C1 and C2 as close to the chip as possible; otherwise 1.5x mode performance will be compromised.

- 2. Place the input and output decoupling capacitors as close to the chip as possible to reduce switching noise and output ripple.

- 3. Connect the exposed pad to GND plane for optimal power dissipation.

Figure 3: Higher Current, Single LED Application.

**SystemPower**<sup>™</sup>

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

#### Schematic and Layout

Figure 4: AAT2869 Evaluation Board Schematic.

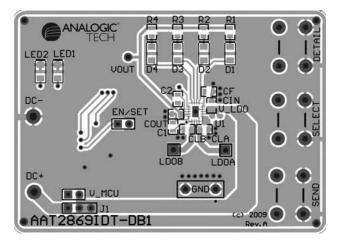

Figure 5: AAT2869 Evaluation Board Top Side Layout.

Figure 6: AAT2869 Evaluation Board Bottom Side Layout.

**AAT2869**

**SystemPower**<sup>™</sup>

## Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

| Component                                 | Part Number      | Description                                                                     | Manufacturer      |  |

|-------------------------------------------|------------------|---------------------------------------------------------------------------------|-------------------|--|

| U1                                        | AAT2869IDT       | Fade-in/Fade-out 4 Channel 1X/1.5X Charge Pump for<br>White LEDs with Dual LDOs | Analogic Tech     |  |

| U2                                        | PIC12F675        | 8-Pin Flash-Based 8-Bit CMOS Microcontroller                                    | Microchip         |  |

| R1, R2, R3, R4                            | RC0603FR-070RL   | Res 0Ω 1/10W 1% 0603 SMD                                                        | Yageo             |  |

| R8                                        | RC0603FR-0749K9L | Res 49.9KΩ 1/10W 1% 0603 SMD                                                    |                   |  |

| R6, R9, R10, R11, R12                     | RC0603FR-071KL   | Res 1KΩ 1/10W 1% 0603 SMD                                                       |                   |  |

| C1, C2, C <sub>OUT</sub> , C <sub>F</sub> | GRM188R71C105K   | Cap Ceramic 1µF 0603 X7R 16V 10%                                                | 5R 10V 10% Murata |  |

| CLA, CLB, C <sub>IN</sub>                 | GRM188R61A225K   | Cap Ceramic 2.2µF 0603 X5R 10V 10%                                              |                   |  |

| C3                                        | GRM188R71C104K   | Cap Ceramic 0.1µF 0603 X7R 16V 10%                                              |                   |  |

| D1, D2, D3, D4                            | RS-0805UW        | 20mA White LED 0805                                                             | Realstar          |  |

| LED1                                      | 0805KGCT         | Green LED 0805                                                                  | HB                |  |

| LED2                                      | 0805KRCT         | Red LED 0805                                                                    | HB                |  |

| CYCLE, UP, DOWN                           | 6*6*5            | 12V 50mA Pushbutton                                                             | E-LT              |  |

Table 8: AAT2869IDT-DB1 Evaluation Board Bill of Materials.

SystemPower<sup>™</sup>

Fade-In/Fade-Out 4 Channel Backlight Driver with Dual LDOs

### **Ordering Information**

| Package         | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------------|----------------------|------------------------------------------|

| TQFN3.0x2.2-18L | F3XYY                | AAT2869IDT-T1                            |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/aboutus/quality.php.

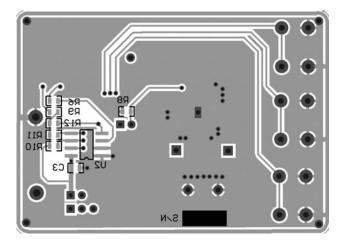

### Package Information

TQFN3.0x2.2-183

All dimensions in millimeters.

1. XYY = assembly and date code.

2. Sample stock is generally held on part numbers listed in BOLD.

3. The leadless package family, which includes QFN, TQFN, DFN, TDFN and STDFN, has exposed copper (unplated) at the end of the lead terminals due to the manufacturing process. A solder fillet at the exposed copper edge cannot be guaranteed and is not required to ensure a proper bottom solder connection.

Advanced Analogic Technologies, Inc. 3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

#### © Advanced Analogic Technologies, Inc.

O Advanced Analogic Technologies, Inc.

Analogic Technologies, Inc.

Analogic Technologies, Inc.

Analogic Technologies, Inc.

Analogic Tech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech and the customer's applications, adequate design and operating safeguards must be provided by the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech holders.