#### **General Description**

The AAT1405 is a highly integrated, high efficiency LED backlight solution for notebook computers, monitors and portable TVs. The device operates from DC inputs, cigarette lighter adapters, or multi-cell Li-ion batteries over the 4.5V to 26V voltage range.

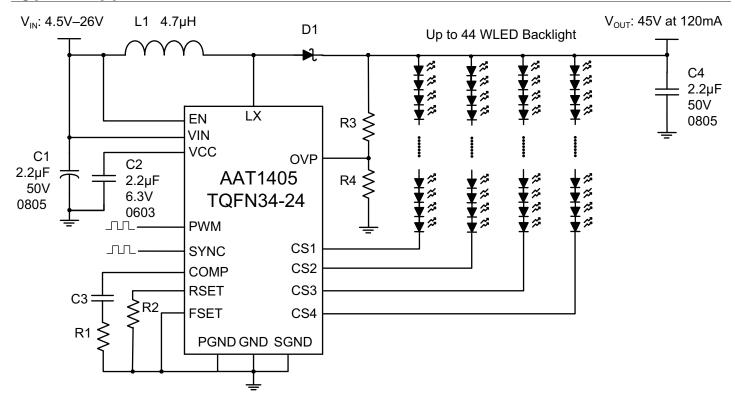

An integrated boost (step-up) converter provides up to 45V output for driving series LEDs. Four precision current sinks are programmed up to 30mA per string through one external  $R_{\text{SET}}$  resistor, supporting up to 44 $^{\circ}$  white LEDs at 120mA total output current.

LED strings may be disabled or operated in parallel for increased drive capability. The boost output voltage is set by the LED string with the highest voltage requirement, allowing a wide range of LED characteristics.

The PWM dimming range at 100Hz is up to 1,000:1.

The boost switching frequency is selectable (up to 1.3MHz) to allow optimum efficiency and the smallest external L/C filtering components. Alternatively, the device may be synchronized to an external clock.

Boost current mode control provides fast response to line and load transients. Integrated Light-Load mode ensures highest efficiency across the entire load range.

Fault tolerant circuitry extends system life by disabling open LED strings. The unique high voltage current sinks prevent damage resulting from shorted LEDs.

The AAT1405 is available in the Pb-free, thermally enhanced 24-pin 3x4 TQFN package.

#### **Features**

- V<sub>IN</sub> Range: 4.5V to 5.5V / 5.0V to 26.0V

- LX Rated to 50V

- Maximum I<sub>OUT</sub>: 120mA

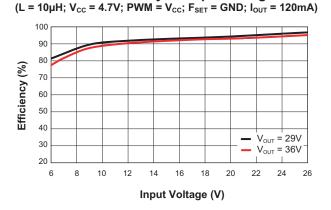

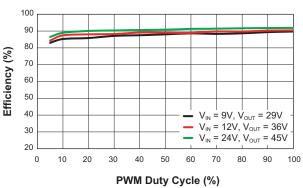

- Up to 92% Efficiency

- High Efficiency Light-Load Mode

- 4 LED Current Sinks up to 30mA/each

- ±2% Accuracy (21mA)

- ±2% Matching (21mA)

- Flexible Configurations

- Disable or Parallel

- Switching Frequency Options

- 675kHz or 1.3MHz

- Synchronize to System Clock

- PWM Direct Dimming Input

- Up to 100kHz Prevents Audio Interference

- Fast Turn-On/Off

- Wide 1,000:1 Dimming Range (100Hz)

- Fault Tolerant: Open/Short LED(s)

- Current Limit Protection

- Over-Voltage Protection

- Over-Temperature Protection

- · Soft-Start Minimizes Inrush Current

- TQFN34-24 Low Profile Package

- -40°C to +85°C Temperature Range

## **Applications**

- Monitors

- Notebook Computers

- Portable TV

- Portable DVD Players

- White LED Backlight

<sup>1.</sup> The maximum number of LEDs in each string is dependent upon the maximum  $V_F$  of the diodes in that string. Under no event should the voltage at LX be exceeded.

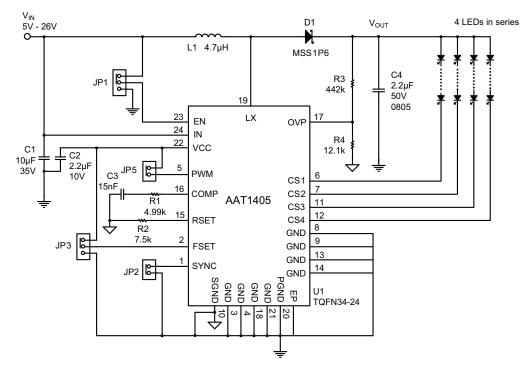

## **Typical Application**

2

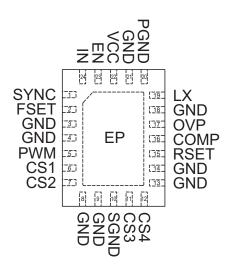

## **Pin Descriptions**

| Pin #                         | Symbol | Function | Description                                                                                                                                                                                                                         |  |

|-------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                             | SYNC   | I        | Synchronizes switching frequency to external system clock. Tie to GND to disable this feature.                                                                                                                                      |  |

| 2                             | FSET   | I        | Connect logic high to set internal oscillator to 1300kHz. Connect logic low to set internal oscillator to 675kHz.                                                                                                                   |  |

| 3, 4, 8, 9, 13,<br>14, 18, 21 | GND    | GND      | Connect to GND.                                                                                                                                                                                                                     |  |

| 5                             | PWM    | I        | Direct PWM input pin. Connect logic level PWM input signal in the frequency range 100Hz-100kHz to this pin to enable PWM dimming.                                                                                                   |  |

| 6                             | CS1    | 0        | Output current sink 1. Connect to SGND to disable channel 1.                                                                                                                                                                        |  |

| 7                             | CS2    | 0        | Output current sink 2. Connect to SGND to disable channel 2.                                                                                                                                                                        |  |

| 10                            | SGND   | GND      | Current sink ground tied to return of internal current sinks CS1-CS4.                                                                                                                                                               |  |

| 11                            | CS3    | 0        | Output current sink 3. Connect to SGND to disable channel 3.                                                                                                                                                                        |  |

| 12                            | CS4    | 0        | Output current sink 4. Connect to SGND to disable channel 4.                                                                                                                                                                        |  |

| 15                            | RSET   | I        | Connect resistor to ground to set maximum current through the LED strings.                                                                                                                                                          |  |

| 16                            | COMP   | I        | Connect an external resistor and capacitor to ground to compensate the boost converter.                                                                                                                                             |  |

| 17                            | OVP    | I        | Over-voltage protection pin. Connect resistive divider between VOUT and GND. Care should be taken to ensure that the voltage at LX does not exceed its maximum rating under extreme opening conditions.                             |  |

| 19                            | LX     | 0        | Switching node of boost converter. Connect an inductor between this pin and input voltage source. Connect the anode of Schottky diode between this pin and the boost output capacitor.                                              |  |

| 20                            | PGND   | GND      | Power ground; tied to source of integrated NMOS switching device.                                                                                                                                                                   |  |

| 22                            | VCC    | 1/0      | Internal regulated voltage when operating from input voltage range 5.0V to 26.0V. De-couple a 2.2µF capacitor to ground. Do not source current from this node. Input voltage pin when op ing from input voltage range 4.5V to 5.5V. |  |

| 23                            | EN     | I        | Logic high enable pin. Pull logic high or tie to IN to enable the device. Pull low to disable the device and minimize quiescent current; pulling low also disables the internal linear regulator.                                   |  |

| 24                            | IN     | I        | Input voltage to IC. Tied to input voltage source and input boost inductor.                                                                                                                                                         |  |

| EP                            |        | GND      | Exposed paddle. Connect to PCB GND plane. PCB paddle should maintain acceptable junction temperature.                                                                                                                               |  |

## **Pin Configuration**

TQFN34-24 (Top View)

## Absolute Maximum Ratings<sup>1</sup>

| Symbol                         | Description                                       | Value       | Units |  |

|--------------------------------|---------------------------------------------------|-------------|-------|--|

| $V_{LX}$                       | LX Voltage to GND                                 | 50          |       |  |

| V <sub>IN,EN</sub>             | Input Voltage, EN to GND                          | -0.3 to 30  | V     |  |

| $V_{CSx}$                      | Output Current Sinks CS1 – CS4 to GND             | -0.3 to 32  |       |  |

| V <sub>cc</sub>                | V <sub>cc</sub> Voltage to GND                    | -0.3 to 7.0 |       |  |

| OVP, COMP, PWM,<br>SYNC, RSET, | 1 OVE COME PANI SAME CLK AUTSUCE TO (2011)        |             |       |  |

| I <sub>OUT</sub>               | Maximum DC Output Current <sup>2</sup>            | 134         | mA    |  |

| TJ                             | Maximum Junction Operating Temperature            | -40 to +150 | °C    |  |

| T <sub>LEAD</sub>              | Maximum Soldering Temperature (at leads, 10 sec.) | 300         |       |  |

| P <sub>D</sub>                 | Maximum Power Dissipation <sup>3</sup>            | 2           | W     |  |

| $\Theta_{JA}$                  | Thermal Resistance <sup>3, 4</sup>                | 50          | °C/W  |  |

## **Recommended Operating Conditions**

| Symbol           | Description                                    | Value      | Units |  |

|------------------|------------------------------------------------|------------|-------|--|

| $V_{IN}$         | Input Voltage Range                            | 5 to 26    | W     |  |

| V <sub>out</sub> | Output Voltage Range V <sub>IN</sub> + 3 to 45 |            |       |  |

| $F_PWM$          | PWM Dimming Frequency Range                    | 0.1 to 100 | kHz   |  |

| I <sub>OUT</sub> | DC Output Current                              | 80 to 120  | mA    |  |

| T <sub>A</sub>   | Operating Ambient Temperature                  | -40 to 85  | °C    |  |

| TJ               | Operating Junction Temperature                 | -40 to 125 | °C    |  |

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

Based on long-term current density limitation.

<sup>3.</sup> Mounted on an FR4 board.

<sup>4.</sup> Derate 20mW/°C above 25°C.

#### Electrical Characteristics<sup>1</sup>

$V_{IN}=12V;~C_{IN}=4.7\mu F,~C_{OUT}=2.2\mu F;~C_{VCC}=2.2\mu F;~L_{1}=10\mu H;~R_{SET}=7.5k\Omega~(I_{CSx}=21mA);~T_{A}=-40^{\circ}C~to~85^{\circ}C~unless~otherwise~noted.$  Typical values are at  $T_{A}=25^{\circ}C$ .

| Symbol                              | Description                                | Conditions                                                                    | Min  | Тур                      | Max  | Units |

|-------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------|------|--------------------------|------|-------|

| Power Supply, Current Sinks         |                                            |                                                                               |      |                          |      |       |

|                                     |                                            | $V_{IN} = V_{CC}$                                                             | 4.5  |                          | 5.5  | V     |

| V <sub>IN</sub>                     | Input Voltage Range                        | $V_{cc}$ = Open                                                               | 5.0  |                          | 26.0 | V     |

|                                     |                                            | V <sub>IN</sub> Rising                                                        |      |                          | 4.3  | V     |

| V <sub>UVLO</sub>                   | Under-Voltage Threshold                    | Hysteresis                                                                    |      | 500                      |      | mV    |

|                                     | _                                          | V <sub>IN</sub> Falling                                                       | 3.2  |                          |      | V     |

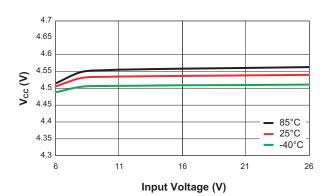

| V <sub>cc</sub>                     | V <sub>cc</sub> Output Voltage             | $EN = Logic High, I_{CC(OUT)} = OmA$                                          | 4.0  | 4.5                      | 6    | V     |

| V <sub>cx</sub>                     | Current Sink Voltage                       | EN = Logic High, $I_{CSx} = 21\text{mA}$<br>( $R_{SET} = 7.5\text{k}\Omega$ ) |      | 0.5                      |      | V     |

| Ι <sub>Q</sub>                      | IN Quiescent Current (no switching)        | $I_{CSx} = 0\%$ , $V_{CSx} = 0.5V$ , EN = Logic High                          |      | 1.5                      |      | mA    |

| I <sub>SD</sub>                     | IN Pin Shutdown Current                    | CS1-CS4 = Open, EN = Logic Low, does not include LX leakage current           |      |                          | 40.0 | μA    |

| I <sub>CSx</sub>                    | Current Sink Accuracy                      | $I_{CSx} = 21mA$                                                              | -5   | ±2                       | +5   | %     |

| I <sub>CSx-Matching</sub>           | Current Matching Between Any Sink Channel  | $I_{CSx} = 21mA$                                                              | -3   | ±2                       | +3   | %     |

|                                     | Over-Voltage Threshold                     | V <sub>OUT</sub> Rising                                                       | 1.1  | 1.2                      | 1.3  | V     |

| $V_{OVP}$                           | Over-Voltage Hysteresis                    | V <sub>OUT</sub> Falling                                                      |      | 100                      |      | mV    |

| R <sub>DS(ON)LO</sub>               | Low Side Switch On Resistance              | $V_{CC} = 4.5V$                                                               |      | 200                      |      | mΩ    |

| D <sub>MAX</sub>                    | Maximum Duty Cycle                         |                                                                               | 90   |                          |      | %     |

| T <sub>MIN</sub>                    | Minimum On-Time                            |                                                                               |      | 100                      |      | ns    |

| I <sub>CSx</sub> /I <sub>RSET</sub> | Current Set Ratio                          | $I_{CSx}/I_{RSET}$ , $V_{RSET} = 0.6V$                                        |      | 262                      |      | A/A   |

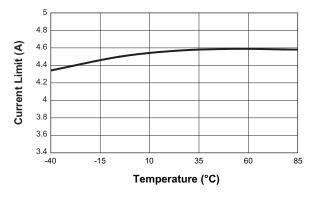

| I <sub>LIMIT</sub>                  | Low Side Switch Current Limit              |                                                                               | 3.0  |                          | 6.5  | Α     |

| ,                                   | LX Pin Leakage                             | $EN = Logic Low; V_{LX} = 40V$                                                |      |                          | 1    | μA    |

| I <sub>LEAK</sub>                   | CSx Pin Leakage                            | EN = Logic Low; CSx = 30V                                                     |      |                          | 10   | μA    |

| F <sub>osc</sub>                    | Oscillator Frequency                       | FSET = Logic Low; $V_{IN} = 5.0$ to 26.0V; $V_{IN} = V_{CC} = 4.5$ to 5.5V    | 550  | 675                      | 800  | kHz   |

|                                     | -                                          | FSET = Logic High; $V_{IN} = 5.0$ to 26.0V; $V_{IN} = V_{CC} = 4.5$ to 5.5V   | 1100 | 1300                     | 1500 | kHz   |

| F <sub>SYNC</sub>                   | Sync Frequency                             |                                                                               |      | F <sub>osc</sub><br>±20% |      | kHz   |

| F <sub>SYNC</sub>                   | Sync Duty Cycle Range                      | F <sub>osc</sub> ± 20%                                                        | 10   |                          | 90   | %     |

| F <sub>PWM(MAX)</sub>               | Maximum Direct PWM Frequency               |                                                                               |      | 50                       | 100  | kHz   |

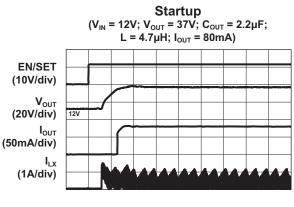

| T <sub>ss</sub>                     | Soft-Start Time                            | $V_{OUT} = 35V$ , $C_{COMP} = 18nF$ , $R_{COMP} = 10k\Omega$                  |      | 1                        |      | ms    |

|                                     | el Inputs: EN Pin                          |                                                                               |      |                          | ı    |       |

| V <sub>EN(L)</sub>                  | Threshold Low                              |                                                                               |      |                          | 0.4  | V     |

| V <sub>EN(H)</sub>                  | Threshold High                             |                                                                               | 2.5  |                          |      | V     |

| I <sub>LEN</sub>                    | Input Leakage Enable Pin                   | $V_{EN} = 5V$ , $V_{IN} = 5V$                                                 |      |                          | 3    | μA    |

|                                     | el Inputs: SYNC, PWM, FSET Pins            |                                                                               |      |                          | ı    |       |

| V <sub>(H)</sub>                    | Threshold Low                              |                                                                               |      |                          | 0.4  | V     |

| V <sub>(H)</sub>                    | Threshold High                             |                                                                               | 1.4  |                          |      | V     |

| I <sub>LK</sub>                     | Input Leakage                              | $V_{SYNC} = V_{PWM} = V_{FSET} = 5V$                                          | -1   |                          | 1    | μA    |

| T <sub>PWM(ON/OFF)</sub>            | PWM Turn On/Off Delay                      | PWM transition to 95%/5% I <sub>RSET</sub>                                    |      | 1                        |      | μs    |

|                                     | Protection                                 |                                                                               |      |                          | 1    |       |

| $T_{J(SD)}$                         | T <sub>J</sub> Thermal Shutdown Threshold  |                                                                               |      | 140                      |      | °C    |

| $T_{J(HYS)}$                        | T <sub>J</sub> Thermal Shutdown Hysteresis |                                                                               |      | 15                       |      | °C    |

<sup>1.</sup> The AAT1405 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

<sup>2.</sup> Output voltage must result in a voltage lower than the LX maximum rating under all operating conditions.

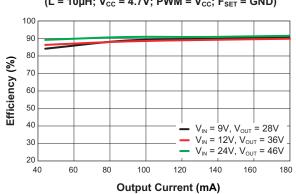

## **Typical Characteristics**

Boost Efficiency vs. Input Voltage

Boost Efficiency vs. Load Current (L =  $10\mu$ H;  $V_{CC}$  = 4.7V; PWM =  $V_{CC}$ ;  $F_{SET}$  = GND)

Boost Efficiency vs. PWM Duty Cycle (L =  $10\mu H$ ;  $V_{CC} = 4.7V$ ;  $F_{SET} = GND$ )

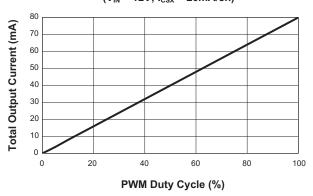

Output Current vs. PWM Duty Cycle (V<sub>IN</sub> = 12V; I<sub>CSX</sub> = 20mA/ch)

Low Side Switch Current Limit vs. Temperature (V<sub>IN</sub> = 5V to 26V)

V<sub>cc</sub> Line Regulation vs. Input Voltage

#### **Typical Characteristics**

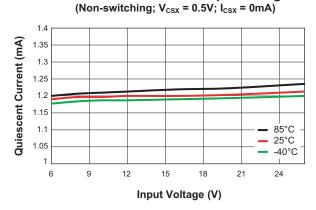

## Quiescent Current vs. Input Voltage

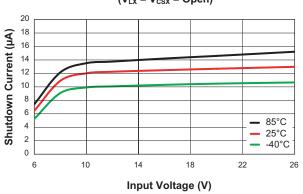

# Shutdown Current vs. Input Voltage (V<sub>LX</sub> = V<sub>CSX</sub> = Open)

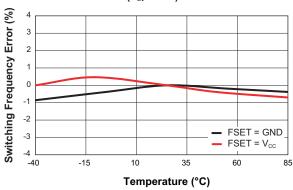

# Switching Frequency vs. Temperature (V<sub>IN</sub> = 12V)

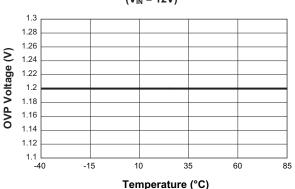

Over-Voltage Threshold vs Temperature (V<sub>IN</sub> = 12V)

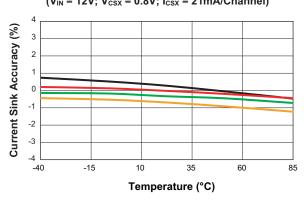

# Current Sink Accuracy vs. Temperature (V<sub>IN</sub> = 12V; V<sub>CSX</sub> = 0.8V; I<sub>CSX</sub> = 21mA/Channel)

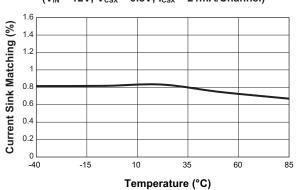

# Current Sink Matching vs. Temperature (V<sub>IN</sub> = 12V; V<sub>CSX</sub> = 0.8V; I<sub>CSX</sub> = 21mA/Channel)

## **Typical Characteristics**

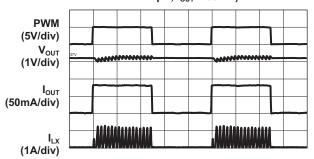

Time (100µs/div)

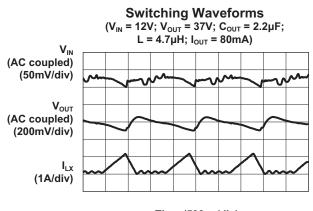

Time (500ns/div)

#### **PWM Switching Waveforms**

$(V_{IN} = 12V; V_{OUT} = 37V; C_{OUT} = 2.2 \mu F;$  $L = 4.7 \mu H; I_{OUT} = 80 mA)$

Time (100µs/div)

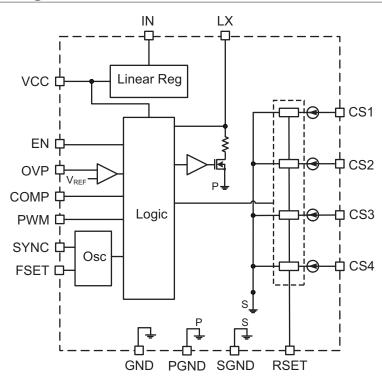

## **Functional Block Diagram**

## **Functional Description**

The AAT1405 is a highly integrated, high efficiency white LED backlight solution for notebook computers, monitors and portable TVs. The device operates from regulated DC inputs, cigarette lighter adapters, and multi-cell Li-ion batteries over a voltage range from 4.5V to 26V.

The integrated boost (step-up) converter provides up to 45V output to drive multiple strings of series LEDs. The maximum number of LEDs is dependent upon the forward voltage of each LED. Four precision current sinks can provide constant current drive for up to 44 white LEDs depending upon LED  $V_{\rm F}$ . The LED current is set by a single external resistor up to 30mA per string for a total output current capability of 120mA. The controller derives output feedback from the channel with the lowest current sink voltage while maintaining the programmed current in each LED string. This ensures the lowest possible output voltage, highest efficiency and continuous operation with mismatched LED strings.

The AAT1405 is designed for maximum flexibility. The LED strings may be disabled or used in parallel for increased

current capability. Thus, the AAT1405 allows operation with fewer than 4 LED strings with the maximum number of LEDs per channel set by the LED  $V_{\rm F}$  and the output voltage of the boost converter. A lower number of LEDs can also be used. Unused current sinks are disabled by tying them to ground. The unique high voltage current sinks support non-matching LED strings (LED quantity, type, etc.). For high current applications, such as high-brightness LEDs, multiple current sinks may be connected in parallel providing up to 120mA per LED string.

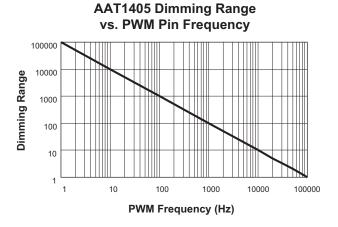

The AAT1405 supports a high input PWM frequency to help eliminate potential audio emissions caused by harmonic/sub-harmonic resonance of the power stage. The PWM dimming range is up to 1,000:1 (see Figure 1).

The output voltage is regulated by the string with the highest voltage requirement, allowing a wide range of LED characteristics. The boost switching frequency is adjustable up to 1300kHz for optimum efficiency and the smallest external filtering components. Alternatively, the device may be synchronized to an external clock. Current mode control provides fast response to line and load

transients. Integrated light load mode ensures highest efficiency across the entire input voltage and load range.

Fault tolerant circuitry extends system life by disabling open LED strings. The high voltage current sinks maintain normal operation with non-matched strings while also preventing damage due to shorted LEDs.

The AAT1405 is available in a Pb-free, thermally enhanced 24-pin 3x4 TQFN package.

#### **PWM Dimming**

The AAT1405 provides direct PWM dimming. After initial power-up or when EN is cycled, the device is enabled with brightness controlled by PWM duty cycle and the  $R_{\text{SET}}$  resistor value.

The ultra-fast 1µs turn-on and turn-off time of the boost regulator and current sinks ensures high performance and excellent dimming range in applications requiring high frequency PWM dimming. The high PWM dimming frequency eliminates audio interference. The integrated current sinks ensure good timing between strings (PWM matching) while the fast response yields a linear PWM duty-cycle versus LED current characteristic. PWM inputs from 100Hz to 100kHz are recommended.

Figure 1: PWM Input Frequency vs. Dimming Range.

#### **Fault Tolerant Operation**

The AAT1405 device is protected from faults arising from LED opens and/or shorts.

An LED open condition will be detected by the controller at startup and during normal operation. The low voltage on the current sink is detected by the controller, which disables the feedback to the boost converter from that current sink. The remaining LED strings to continue to operate normally. The controller re-enables the current sink feedback if the LED open condition is removed during a power or EN cycle. This feature extends backlight life and reliability, which is otherwise limited by intermittent conditions in the LED string(s) and/or circuit board interconnections.

Under all conditions, the over-voltage protection circuitry prevents the switching node (LX) from exceeding the maximum operating voltage prior to disabling the current sink. Over-voltage protection (OVP) disables boost switching while maintaining the programmed LED current. Boost switching is re-enabled when OVP hysteresis is satisfied.

A LED short condition results in a higher voltage appearing on the affected channels' current-sink pin. The affected current sink automatically compensates for the additional voltage. The current sink can withstand a high voltage indefinitely. However, the increased voltage across the current sink causes an increase in power dissipation. The channel will continue to operate until the over-temperature protection activates.

Integrated over-current protection is provided. Overcurrent protection prevents inductor saturation and any resulting damage to the switching device occurring during an overload fault condition.

#### **Application Information**

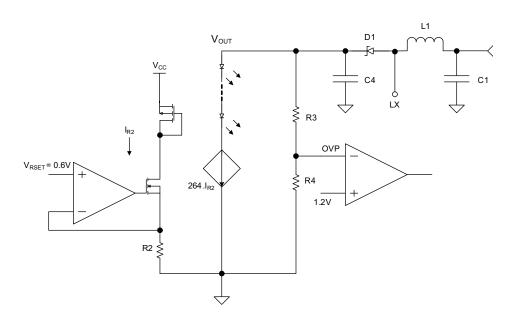

#### **OVP Protection with Open LED Failure**

The AAT1405's OVP protection consists of a resistive divider network (R3 and R4) as shown in Figure 2. The resistor divider must be selected so that the voltage at the OVP pin exceeds the OVP rising threshold when the output is at  $V_{\text{OUT}(\text{MAX})}$ .

$$R3 = R4 \cdot \left( \frac{V_{OUT(MAX)}}{V_{OVP(MAX)}} - 1 \right)$$

When the OVP rising threshold is exceeded, the converter stops switching. The open LED channel is removed from the boost converter feedback loop. When the voltage at the OVP pin falls below the OVP hysteresis voltage, the boost converter can resume switching.

It is important that during normal operation the current sinks are given enough headroom so that the OVP threshold is not tripped.

The output voltage at the minimum OVP threshold is

$$V_{\text{OUT(MIN)}} = V_{\text{OVP(MIN)}} \cdot \left(\frac{R_3}{R_4} + 1\right)$$

The maximum voltage of each LED string including the current sink headroom should not exceed  $V_{\text{OUT}(\text{MIN})}$ .

$$\begin{split} & V_{\text{OUT(MIN)}} > V_{\text{CSX}} + N \cdot V_{\text{FLED(MAX)}} \\ & V_{\text{OVP(MIN)}} \cdot \left(\frac{R_3}{R_4} + 1\right) > V_{\text{CSX}} + N \cdot V_{\text{FLED(MAX)}} \\ & R_3 > R_4 \cdot \left(\frac{V_{\text{CSX}} + N \cdot V_{\text{FLED(MAX)}} - V_{\text{OVP(MIN)}}}{V_{\text{OVP(MIN)}}}\right) \end{split}$$

Where:

N is the number of LED in each string.

$V_{\text{OVP(MIN)}} = 1.1 \text{V}$  is the minimum over-voltage threshold.  $V_{\text{CSX}} = 0.5 \text{V}$  is the current sink voltage.

$V_{FLED(MAX)}$  is the maximum forward LED voltage at 20mA.

Another factor in setting the OVP voltage using the resistive divider is that the maximum voltage at the LX pin should not exceed  $V_{LX(MAX)} = 50V$ .

$$V_{LX(MAX)} = V_{OUT(MAX)} + V_{D1} + V_{RING}$$

$V_{\text{D1}}$  is the forward voltage of the Schottky diode D1.  $V_{\text{RING}}$  is the voltage spike at LX node caused by the delay of D1 at turn on.

Measurements should confirm that the maximum switching node voltage  $V_{\text{LX}(\text{MAX})}$  is less than 50V under worst case conditions.

Figure 2: Over-Voltage Protection and Current Sink Setting Circuit.

For example, if the number of white LEDs in each string is N =11, the resistor divider R3 can be calculated by selecting R4 =  $12.1k\Omega$ :

$$R_3 > 12.1k\Omega \cdot \left(\frac{0.5V + 11 \cdot 3.7V - 1.1}{1.1}\right) = 441.1k\Omega$$

choose R3 =  $442k\Omega$ .

The maximum output voltage with the selected values of R4, R3 is

$$V_{\text{OUT(MAX)}} = V_{\text{OVP(MAX)}} \cdot \left(\frac{R_3}{R_4} + 1\right) = 1.3V \cdot \left(\frac{442k\Omega}{12.1k\Omega} + 1\right) = 48.8V$$

#### **LED Current Sink Setting**

The current sink is controlled by the RSET voltage (0.6V) and the  $R_{\text{SET}}$  resistor (R2). For maximum accuracy, a 1% tolerance resistor is recommended.

The  $R_{\text{SET}}$  resistor (R2) value can be calculated as follows:

$$R_2 = \frac{262 \cdot 0.6V}{I_{CSX(MAX)}}$$

Where  $V_{RSET} = 0.6V$ .

For example, if the maximum current for each string of LEDs is 30mA, this corresponds to a minimum resistor value of  $5.23k\Omega$ .

$$R_2 = \frac{262 \cdot 0.6V}{30 \text{mA}} = 5.23 \text{k}\Omega$$

| Maximum I <sub>LED</sub> Current (mA) | R2 (k <b>Ω</b> ) |

|---------------------------------------|------------------|

| 30                                    | 5.23             |

| 25                                    | 6.19             |

| 20                                    | 7.87             |

| 15                                    | 10.5             |

| 10                                    | 15.8             |

| 5                                     | 31.6             |

Table 2: Maximum LED Current Sink vs. R<sub>SET</sub> Resistor (R2) Values.

#### **Schottky Diode Selection**

To ensure minimum forward voltage drop, high voltage Schottky diodes are considered the best choice for the white LED boost converter. The output diode is sized to maintain acceptable efficiency and reasonable operating junction temperature under full load operating conditions. Forward voltage ( $V_F$ ) and package thermal resistance ( $\theta_{JA}$ ) are the dominant factors to consider in selecting a diode. The diode non-repetitive peak forward surge current rating ( $I_{FSM}$ ) should be considered for high pulsed load applications.  $I_{FSM}$  rating drops with increasing conduction period. Manufacturers' datasheets should be consulted to verify reliability under peak loading conditions. The diode's published current rating may not reflect actual operating conditions and should be used only as a comparative measure between similarly rated devices.

During the on-time, the output voltage on the output cap is applied to the cathode of the external Schottky diode. The rectifier's reverse breakdown voltage rating should be greater than the maximum output voltage rating of the Boost. 40V rated Schottky diodes are recommended for outputs less than 30V, while 60V rated Schottky diodes are recommended for outputs greater than 35V.

The approximate power loss on the Schottky diode can be calculated:

$$I_{AVG} = I_{OUT}$$

The average output current multiplied by the forward diode voltage determines the loss of the output diode.

$$P_{LOSS-DIODE} = I_{AVG} \cdot V_F = I_{OUT} \cdot V_F$$

Diode junction temperature can be estimated.

$$T_J = T_{AMB} + \theta_{JA} \cdot P_{LOSS-DIODE}$$

Output diode junction temperature should be maintained below 110°C, but may vary depending on application and/or system guidelines. The diode  $\theta_{JA}$  can be minimized with additional PCB area on the cathode. PCB heat-sinking the anode may degrade EMI performance. The reverse leakage current of the rectifier must be considered to maintain low quiescent (input) current and high efficiency under light load. The rectifier reversed current increases dramatically at elevated temperatures.

#### **Inductor Selection**

The white LED boost (step-up) converter is designed to operate with an inductor with a minimum value of  $4.7\mu H$  for all input and output voltage combinations. The inductor saturation current rating should be greater than the NMOS current at maximum duty cycle.

$$D_{MAX} = \frac{(V_{OUT} + V_F - V_{IN(MIN)})}{V_{OUT} + V_F}$$

The inductor (L) is selected to avoid saturation at minimum input voltage, maximum output load conditions. Peak current may be calculated from the following equation, again assuming continuous conduction mode. Worst-case peak current occurs at minimum input voltage (maximum duty cycle) and maximum load.

$$I_{PEAK} = \frac{I_{OUT}}{1 - D_{MAX}} + \frac{D_{MAX} \cdot V_{IN(MIN)}}{2 \cdot F_{s} \cdot L}$$

#### **Output Capacitor**

The high output ripple inherent in the boost converter necessitates low impedance output filtering.

Multi-layer ceramic (MLC) capacitors provide small size and adequate capacitance, low parasitic equivalent series resistance (ESR) and equivalent series inductance (ESL), and are well suited for use with the white LED boost regulator. MLC capacitors of type X7R or X5R are recommended to ensure good capacitance stability over the full operating temperature range.

The output capacitor is sized to maintain the output load without significant voltage droop ( $\Delta V_{\text{OUT}}$ ) during the power switch ON interval, when the output diode is not conducting. A ceramic output capacitor from 2.2µF to 4.7µF is recommended. Typically, 50V rated capacitors are required for the 42V maximum boost output. Ceramic capacitors sized as small as 0805 or 1206 are available which meet these requirements.

MLC capacitors exhibit significant capacitance reduction with applied voltage. Output ripple measurements should confirm that output voltage droop and operating stability are acceptable. Voltage derating can minimize this factor, but results may vary with package size and among specific manufacturers.

The output capacitor size can be estimated using the equation:

$$C_{\text{OUT}} = \frac{I_{\text{OUT}} \cdot D_{\text{MAX}}}{F_{\text{S}} \cdot \Delta V_{\text{OUT}}}$$

To maintain stable operation at full load, the output capacitor should be sized to maintain  $\Delta V_{\text{OUT}}$  between 100mV and 200mV.

The WLED boost converter input current flows during both ON and OFF switching intervals. The input ripple current is less than the output ripple and, as a result, less input capacitance is required.

#### Compensation Component Selection

The AAT1405 Boost architecture uses peak current mode control to eliminate the double pole effect of the output L&C filter and simplifies the compensation loop design. The current mode control architecture simplifies the transfer function of the control loop to be a one-pole, one left plane zero and one right half plane (RHP) system in frequency domain. The dominant pole can be calculated by:

$$f_{P} = \frac{1}{2\pi \cdot R_{0} \cdot C_{4}}$$

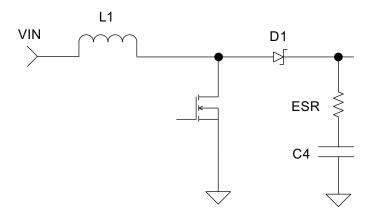

The ESR zero of the output capacitor (see Figure 3) can be calculated by:

$$f_{Z\_{ESR}} = \frac{1}{2\pi \cdot R_{ESR} \cdot C_4}$$

Where:

${\rm C_4}$  is the output filter capacitor  ${\rm R_O}$  is the equivalent load resistor value  ${\rm R_{ESR}}$  is the equivalent series resistance of the output capacitor.

The right half plane (RHP) zero can be calculated by:

$$f_{z\_{ESR}} = \frac{{V_{iN}}^2}{2\pi \cdot L_1 \cdot I_{OUT} \cdot V_{OUT}}$$

Figure 3: AAT1405 Equivalent Output Stage.

It is recommended to design the bandwidth to one decade lower than the frequency of RHP zero to guarantee the loop stability. A series capacitor and resistor network (R1 and C3) connected to the COMP pin sets the pole and zero which are given by:

$$f_{P\_{COM}} = \frac{1}{2\pi \cdot R_{EA} \cdot C_3}$$

$$f_{Z\_{COM}} = \frac{1}{2\pi \cdot R_1 \cdot C_3}$$

Where:

$C_3$  is the compensation capacitor  $R_1$  is the compensation resistor

$R_{\text{EA}}$  is the output resistance of the error amplifier (2.97M $\Omega$ ).

A 15nF (C3) capacitor and a  $5k\Omega$  (R1) resistor in series are chosen for optimum phase margin and fast transient response.

- L1 Sumida, CDRH5D28RHPNP-4R7N, 4.7 $\mu$ H, 3.7A, DCR = 43.1m $\Omega$

- D1 Vishay, Schottky Barrier Diode, MSS1P6, 1A, 60V C1 Taiyo Yuden, GMK325BJ106KN-T, 10μF, 35V, X5R,1210; OR Murata GRM32ER71H106K, 10μF, 50V, X7R, 1210

- C2 2.2µF, 10V, 0603

- C3 15nF, 10V, 0603

- C4 Murata, GRM31CR71H225KA88L, 2.2µF, 50V, X7R, 1206

- R1, R2, R3, R4 Carbon Film resistors, 1%, 0603

Figure 4: AAT1405IMK Evaluation Board Schematic.

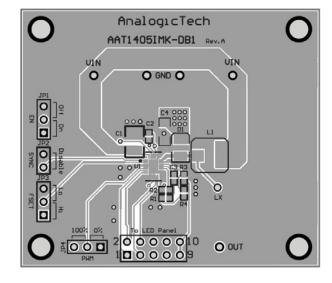

Figure 5: AAT1405IMK Evaluation Board Top Side Layout.

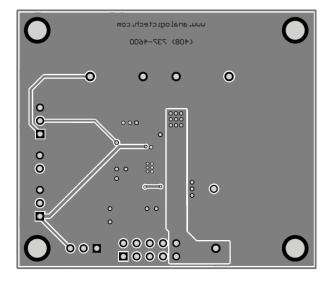

Figure 6: AAT1405IMK Evaluation Board **Bottom Side Layout.**

#### **Ordering Information**

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| TQFN34-24 | K3XYY                | AAT1405IMK-T1                            |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/aboutus/quality.php.

#### Package Information

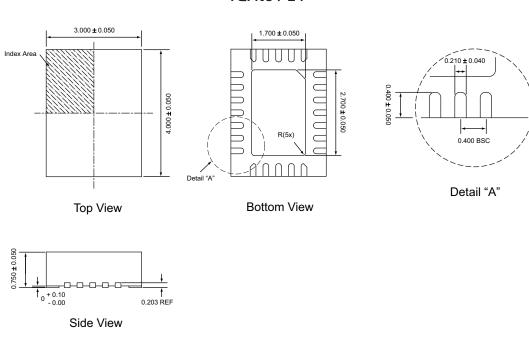

**TQFN34-24**3

All dimensions in millimeters

Advanced Analogic Technologies, Inc. 3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech and the AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other brand and product names appearing in this document are registered trademarks of their respective holders.

<sup>1.</sup> XYY = assembly and date code.

Sample stock is generally held on part numbers listed in BOLD.

<sup>3.</sup> The leadless package family, which includes QFN, TQFN, DFN, TDFN and STDFN, has exposed copper (unplated) at the end of the lead terminals due to the manufacturing process. A solder fillet at the exposed copper edge cannot be guaranteed and is not required to ensure a proper bottom solder connection.