# 5V Automotive Regulator with Windowed Watchdog

### **Description**

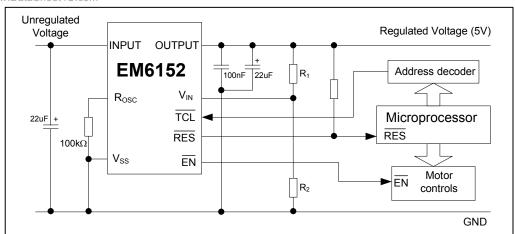

The EM6152 offers a high level of integration by combining voltage regulation, voltage monitoring monitoring using a windowed watchdog.

A comparator monitors the voltage applied at the V<sub>IN</sub> input comparing it with an internal voltage reference V<sub>REF</sub>. The power-on reset function is initialized after VIN reaches VREF and takes the reset output inactive after a delay TPOR depending on external resistance Rosc. The reset output goes active low when the  $V_{IN}$  voltage is less than  $V_{REF}$ . The  $\overline{RES}$ and EN outputs are guaranteed to be in a correct state for a regulated output voltage as low as 1.2 V. The watchdog function monitors software cycle time and execution.

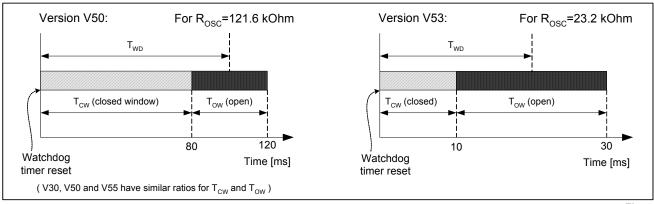

If software clears the watchdog too quickly (incorrect cycle time) or too slowly (incorrect execution) it will cause the system to be reset. For enhanced security, the watchdog must be serviced within an "open" time window. During the remaining time, the watchdog time window is "closed" and a reset will occur should a TCL pulse be received by the watchdog during this "closed" time window. The ratio of the open/closed window is either 33%/67% or 67%/33%.

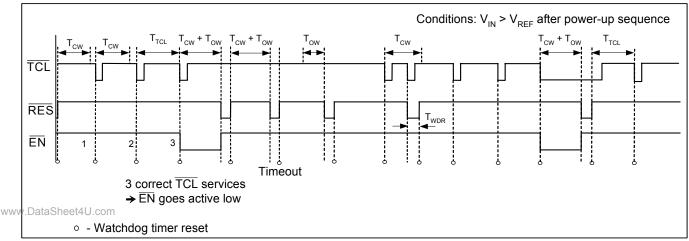

The system ENABLE output prevents critical control functions being activated until software has successfully cleared the watchdog three times. Such a security could be used to prevent motor controls being energized on repeated resets of a faulty system.

When the microcontroller goes in stand-by mode or stops working, no signal is received on the TCL input of the EM6152 (version 55) and it goes into a stand-by mode in order to save power (CAN-bus sleep detector).

wwwInDEM6152, the voltage regulator has a low dropout voltage and a low quiescent current of 135  $\mu$ A. The quiescent current increases only slightly in dropout prolonging battery life. Builtin protection includes a positive transient absorber for up to 45 V (load dump) and the ability to survive an unregulated input voltage of -42 V (reverse battery). The input may be connected to ground or to a reverse voltage without reverse current flowing from the output to the input.

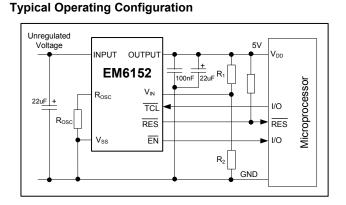

Fig. 1

#### **Features**

- Low quiescent current 135 µA

- -40°C to +125°C temperature range

- Highly accurate 5 V. 400 mA guaranteed output (actual maximum current depends on power dissipation)

- Low dropout voltage, typically 250 mV at 250 mA

- Unregulated DC input can withstand -42 V reverse battery and +45 V power transients

- Fully operational for unregulated DC input voltage up to 40 V and regulated output voltage down to 3.0 V

- No reverse output current

- Very low temperature coefficient for the regulated output

- Current limiting

- Windowed watchdog with an adjustable time windows, guaranteeing a minimum time and a maximum time between software clearing of the watchdog

- Time base accuracy ±8% (at 100ms)

- Sleep mode function (V55)

- Adjustable threshold voltage using external resistors

- Adjustable power on reset (POR) delay using one external resistor

- Open-drain active-low RESET output

- Reset output guaranteed for regulated output voltage down to 1.2 V

- System ENABLE output offers added security

- Qualified according to AEC-Q100

- Green SO-8 and PSOP2-16 packages (RoHS compliant)

## **Applications**

- Automotive systems

- Industrial

- Home security systems

- Telecom / Networking

- Computers

- Set top boxes

#### Selection Table

| Part Number       | V <sub>REF</sub> | Closed<br>Window | Open<br>Window | CAN-bus sleep<br>detector |  |  |

|-------------------|------------------|------------------|----------------|---------------------------|--|--|

| EM6152 <b>V30</b> | 1.17 V           | 67%              | 33%            | No                        |  |  |

| EM6152 <b>V50</b> | 1.52 V           | 67%              | 33%            | No                        |  |  |

| EM6152 <b>V53</b> | 1.52 V           | 33%              | 67%            | No                        |  |  |

| EM6152 <b>V55</b> | 1.275 V          | 67%              | 33%            | Yes                       |  |  |

Please refer to Fig. 4 for more information about the open/closed window of the watchdog.

# **Ordering Information**

| Part Number     | Version | $V_{REF}$ | Package  | Delivery Form         | Package<br>Marking |  |

|-----------------|---------|-----------|----------|-----------------------|--------------------|--|

| EM6152V30SO8A+  |         |           | SO-8     | Stick, 97 pcs         | 6152030            |  |

| EM6152V30SO8B+  | V30     | 1.17 V    | 30-6     | Tape & Reel, 2500 pcs | 0132030            |  |

| EM6152V30PS16B+ |         |           | PSOP2-16 | Tape & Reel, 2500pcs  | EM6152 030         |  |

| EM6152V50SO8A+  |         |           | SO-8     | Stick, 97 pcs         | 6152050            |  |

| EM6152V50SO8B+  | V50     | 1.52 V    | 1.52 V   | Tape & Reel, 2500 pcs | 0152050            |  |

| EM6152V50PS16B+ |         |           | PSOP2-16 | Tape & Reel, 2500pcs  | EM6152 050         |  |

| EM6152V53SO8A+  |         |           | SO-8     | Stick, 97 pcs         | 6152053            |  |

| EM6152V53SO8B+  | V53     | 1.52V     | 30-0     | Tape & Reel, 2500 pcs | 0102000            |  |

| EM6152V53PS16B+ |         |           | PSOP2-16 | Tape & Reel, 2500pcs  | EM6152 053         |  |

| EM6152V55SO8A+  | V55     | 1.275 V   | SO-8     | Stick, 97 pcs         | 6152055            |  |

| EM6152V55SO8B+  | V55     | 1.273 V   | 30-6     | Tape & Reel, 2500 pcs | 0152055            |  |

Note: the "+" symbol at the end of the part number means that this product is RoHS compliant (green).

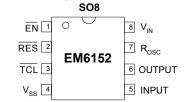

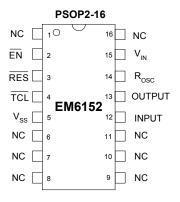

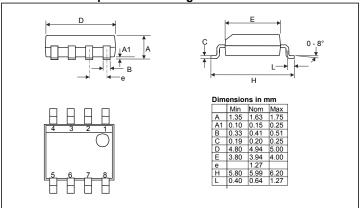

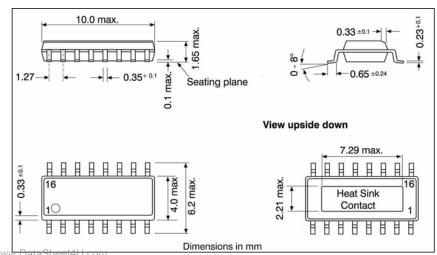

## **Pin Assignment and Description**

| SO8             | PSOP2-16             | Name     | Function                                                                                        |

|-----------------|----------------------|----------|-------------------------------------------------------------------------------------------------|

| 1               | 2                    | ĒΝ       | Push-pull active low enable output                                                              |

| 2               | 3                    | RES      | Open drain active low reset output. RES must be pulled up to V <sub>OUTPUT</sub> even if unused |

| 3               | 4                    | TCL      | Watchdog timer clear input signal                                                               |

| 4               | 5                    | $V_{SS}$ | GND terminal                                                                                    |

| 5               | 12                   | INPUT    | Voltage regulator input                                                                         |

| 6               | 13                   | OUTPUT   | Voltage regulator output                                                                        |

| 7               | 14                   | Rosc     | R <sub>OSC</sub> input for RC oscillator tuning                                                 |

| 8               | 15                   | $V_{IN}$ | Voltage comparator input                                                                        |

| -               | 1, 6 to 11, 16       | NC       | No connect                                                                                      |

| -<br>U Data Sha | Heat Sink<br>Contact |          | Can be connected to Vss or left floating                                                        |

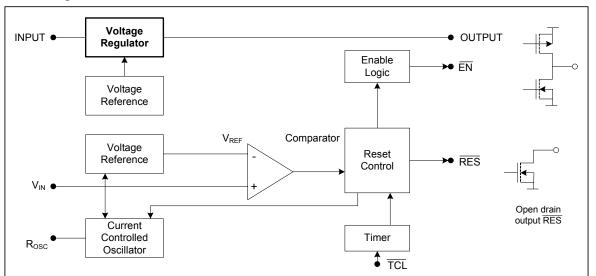

### **Block Diagram EM6152**

Fig. 3

#### **Absolute Maximum Ratings**

| Parameter                               | Symbol             | Conditions                 |

|-----------------------------------------|--------------------|----------------------------|

| Continuous voltage at INPUT             | V <sub>INPUT</sub> | -0.3 to +40V               |

| to V <sub>SS</sub>                      |                    |                            |

| Transients on INPUT for                 | V <sub>TRANS</sub> | Up to +45V                 |

| t < 100 ms and duty cycle 1%            | V TRANS            | Op to +45V                 |

| Max. voltage at any signal pin          | $V_{MAX}$          | V <sub>OUTPUT</sub> + 0.3V |

| Min. voltage at any signal pin          | $V_{MIN}$          | $V_{SS} - 0.3V$            |

| Reverse supply voltage on INPUT         | $V_{REV}$          | -42V                       |

| Storage temperature                     | T <sub>STO</sub>   | -65 to +150 °C             |

| ESD                                     |                    |                            |

| According to MIL-STD-883C method 3015.7 | $V_{Smax}$         | 2000V                      |

Table 1

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

#### **Decoupling Methods**

The input capacitor is necessary to compensate the line influences. A resistor of approx. 1  $\Omega$  connected in series with the input capacitor may be used to damp the oscillation of the input capacitor and input inductance. The ESR value of the capacitor plays a major role regarding the efficiency of the decoupling. It is recommended also to connect a ceramic capacitor (100 nF) directly at the IC's pins. In general the user must assure that pulses on the input line have slew rates lower than 1 V/ $\mu$ s. On the output side, the capacitor is necessary for the stability of the regulation circuit. The stability is guaranteed for values of 22  $\mu$ F or greater. It is especially important to choose a capacitor with

a low ESR value. Tantalum capacitors are recommended. See the notes related to Table 2. Special care must be taken in disturbed environments (automotive, proximity of motors and relays, etc.).

#### **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, it is advised that normal precautions be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the voltage range. At any time, all inputs must be tied to a defined logic voltage level.

#### **Operating Conditions**

| Parameter                                                                                         | Symbol               | Min. | Max.                | Units |

|---------------------------------------------------------------------------------------------------|----------------------|------|---------------------|-------|

| Operating junction temperature                                                                    | Tj                   | -40  | +125                | °C    |

| INPUT voltage (note 1)                                                                            | $V_{INPUT}$          | 2.3  | 40                  | V     |

| OUTPUT voltage (note 1, 2)                                                                        | $V_{\text{OUTPUT}}$  | 1.2  | 5.5                 | V     |

| RES and EN guaranteed (note 3)                                                                    | V <sub>OUTPUT</sub>  | 1.2  |                     | V     |

| OUTPUT current (note 4)                                                                           | I <sub>OUTPUT</sub>  |      | 400                 | mA    |

| Comparator input voltage                                                                          | $V_{IN}$             | 0    | $V_{\text{OUTPUT}}$ | V     |

| RC-oscillator programming                                                                         | Rosc                 | 10   | 1000                | kΩ    |

| Package thermal resistance<br>from junction to ambient :<br>SO-8<br>PSOP2-16 150 MILS<br>(note 5) | R <sub>th(j-a)</sub> | 30   | 160<br>90           | °C/W  |

Table 2

www.DataSheet4U.com

- Note 1: full operation guaranteed. To achieve the load regulation specified in Table 3 a 22  $\mu$ F capacitor or greater is required on the INPUT, see Fig. 1b. The 22  $\mu$ F must have an effective resistance  $\leq$  5  $\Omega$  and a resonant frequency above 500 kHz.

- Note 2: a 22  $\mu F$  load capacitor and a 100 nF decoupling capacitor are required on the regulator OUTPUT for stability. The 22  $\mu F$  must have an effective series resistance of  $\leq$  5  $\Omega$  and a resonant frequency above 500 kHz.

- Note 3:  $\overline{RES}$  must be pulled up externally to  $V_{OUTPUT}$  even if it is unused. ( $\overline{RES}$  and  $\overline{EN}$  are used as inputs by EM test)

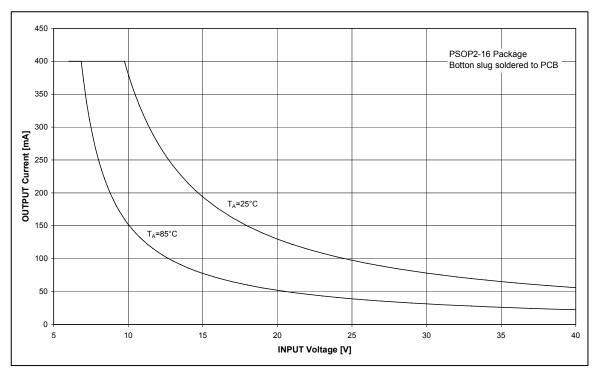

- **Note 4:** the OUTPUT current will not apply to the full range of input voltage. Power dissipation that would require the EM6152 to work above the maximum junction temperature (+125°C) must be avoided.

- **Note 5:** the thermal resistance specified assumes the package is soldered to a PCB. A typical value of 51°C/W has been obtained with a dual layer board, with the slug soldered to the heat-sink area of the PCB.

#### **Electrical Characteristics**

$V_{INPUT}$  = 13.5 V,  $C_L$  = 22  $\mu$ F + 100 nF,  $C_{INPUT}$  = 22  $\mu$ F,  $T_j$  = -40 to +125 °C, unless otherwise specified

| Parameter                                             | Symbol              | Test Conditions                                                                                                                                       | Min.     | Тур.  | Max.                | Unit  |

|-------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|---------------------|-------|

| Supply current in standby mode and sleep mode for V55 | I <sub>SS</sub>     | $R_{OSC}$ = don't care, TCL = $V_{OUTPUT}$ , $V_{IN}$ = 0 V, $I_L$ = 1 mA                                                                             |          | 135   | 270                 | μΑ    |

| Supply current (note1)                                | I <sub>SS</sub>     | $R_{OSC}$ = 100 kΩ, I/P <sub>S</sub> at V <sub>OUTPUT</sub> , O/P <sub>S</sub> 1 MΩ to V <sub>OUTPUT</sub> , I <sub>L</sub> = 1 mA                    |          | 145   | 280                 | μΑ    |

| Supply current (note 1)                               | I <sub>SS</sub>     | $R_{OSC}$ = 100 k $\Omega$ , I/P <sub>S</sub> at V <sub>OUTPUT</sub> , O/P <sub>S</sub> 1 M $\Omega$ to V <sub>OUTPUT</sub> , I <sub>L</sub> = 250 mA |          | 7     | 14                  | mA    |

| Output voltage                                        | V <sub>OUTPUT</sub> | $5 \text{ mA} \leq I_L \leq 250 \text{ mA}$                                                                                                           | 4.8      | 5     | 5.2                 | V     |

| Line regulation (note 2)                              | $V_{LINE}$          | $12 \text{ V} \le V_{\text{INPUT}} \le 32 \text{ V}, I_{\text{L}} = 5 \text{ mA}$                                                                     |          | 10    | 25                  | mV    |

| Load regulation (note 2)                              | $V_L$               | $5 \text{ mA} \le I_L \le 250 \text{ mA}, V_{INPUT}=6V$                                                                                               |          | 35    | 80                  | mV    |

| Dropout voltage (note 3)                              | $V_{DROPOUT}$       | I <sub>L</sub> = 250 mA                                                                                                                               |          | 250   | 500                 | mV    |

| Output voltage temperature coefficient (note 4)       | $V_{th(coeff)}$     |                                                                                                                                                       |          | 0.5   |                     | mV/°C |

| Current limit                                         | I <sub>Lmax</sub>   | OUTPUT tied to V <sub>SS</sub> , V <sub>INPUT</sub> =6V                                                                                               | 400      | 600   |                     | mA    |

| RES & EN                                              |                     | V <sub>OUTPUT</sub> = 4.5 V, I <sub>OL</sub> = 8 mA                                                                                                   |          | 0.25  | 0.45                | V     |

| Output Low Voltage                                    | $V_{OL}$            | $V_{OUTPUT} = 2.0 \text{ V}, I_{OL} = 4 \text{ mA}$                                                                                                   |          | 0.2   | 0.4                 | V     |

|                                                       |                     | $V_{OUTPUT} = 1.2 \text{ V}, I_{OL} = 0.5 \text{ mA}$                                                                                                 |          | 0.04  | 0.2                 | V     |

| EN                                                    |                     | $V_{OUTPUT} = 4.5 \text{ V}, I_{OH} = -1 \text{ mA}$                                                                                                  | 3.5      | 4.1   |                     | V     |

| Output High Voltage                                   | $V_{OH}$            | $V_{OUTPUT} = 2.0 \text{ V}, I_{OH} = -100 \mu\text{A}$                                                                                               | 1.8      | 1.9   |                     | V     |

|                                                       |                     | $V_{OUTPUT} = 1.2 \text{ V}, I_{OH} = -20 \mu\text{A}$                                                                                                | 0.9      | 1.05  |                     | V     |

| TCL Input Low Level                                   | $V_{IL}$            |                                                                                                                                                       | $V_{SS}$ |       | 0.5                 | V     |

| TCL Input High Level                                  | $V_{IH}$            |                                                                                                                                                       | 2.5      |       | $V_{\text{OUTPUT}}$ | V     |

| Leakage current                                       | $I_{LI}$            | $V_{SS} \le V_{TCL} \le V_{OUTPUT}$                                                                                                                   |          | 0.05  |                     | μΑ    |

|                                                       |                     | Version V30 (replaces A6130)                                                                                                                          | 1.135    | 1.170 | 1.205               | V     |

| Comparator reference (note 5, 6)                      | $V_{REF}$           | Version V50 (replaces A6150 and A6250)                                                                                                                | 1.475    | 1.520 | 1.565               | V     |

|                                                       |                     | Version V53                                                                                                                                           | 1.475    | 1.520 | 1.565               | V     |

|                                                       |                     | Version V55 (replaces A6155)                                                                                                                          | 1.235    | 1.275 | 1.315               | V     |

| Comparator hysteresis (note 6)                        | $V_{HY}$            |                                                                                                                                                       |          | 2     |                     | mV    |

| V <sub>IN</sub> input resistance                      | R <sub>VIN</sub>    |                                                                                                                                                       |          | 100   |                     | MΩ    |

Table 3

www.DataSheet4U.com

Note 1: if INPUT is connected to  $V_{SS}$ , no reverse current will flow from the OUTPUT to the INPUT, however the supply current specified will be sank by the OUTPUT to supply the EM6152.

**Note 2:** regulation is measured at constant junction temperature using pulse testing with a low duty cycle. Changes in OUTPUT voltage due to heating effects are covered in the specification for thermal regulation.

Note 3: the dropout voltage is defined as the INPUT to OUTPUT differential, measured with the input voltage equal to 5.0 V.

Note 4: output voltage temperature coefficient is defined as the change in OUTPUT voltage after a change in power dissipation is applied, excluding load or line regulation effects.

Note 5: the comparator and the voltage regulator have separate voltage references (see "Block Diagram" Fig. 3).

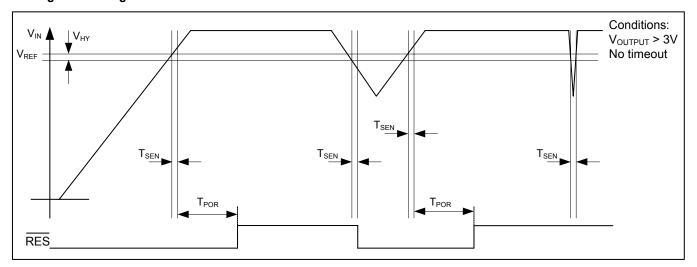

Note 6: the comparator reference is the power-down reset threshold. The power-on reset threshold equals the comparator reference voltage plus the comparator hysteresis (see Fig. 5).

# **Timing Characteristics**

$V_{INPUT}$  = 13.5 V,  $I_L$  = 100  $\mu$ A,  $C_L$  = 22  $\mu$ F + 100 nF,  $C_{INPUT}$  = 22  $\mu$ F,  $T_j$  = -40 to + 125 °C, unless otherwise specified

| Parameter                                 | Symbol             | Test Conditions                                                                      | Min.            | Тур.                | Max.      | Units |

|-------------------------------------------|--------------------|--------------------------------------------------------------------------------------|-----------------|---------------------|-----------|-------|

| Propagation delay TCL to Output Pins      | $T_{DIDO}$         |                                                                                      |                 | 250                 | 500       | ns    |

| V <sub>IN</sub> sensitivity               | T <sub>SEN</sub>   | V <sub>INhigh</sub> =1.1xV <sub>REF</sub> , V <sub>INlow</sub> =0.9xV <sub>REF</sub> | 0.5             | 3                   | 15        | μS    |

| Watchdog Reset Pulse Period               | $T_{WDRP}$         | TCL inactive                                                                         | T <sub>CW</sub> | + T <sub>OW</sub> + | $T_{WDR}$ | ms    |

| Version V30                               |                    |                                                                                      |                 |                     |           |       |

| Power-on Reset delay                      | T <sub>POR</sub>   | R <sub>OSC</sub> = 116.9 kΩ ±1%                                                      | 91.6            | 100                 | 108.3     |       |

| Closed Window Time                        | T <sub>CW</sub>    |                                                                                      | 74              | 80                  | 85.76     |       |

| Open Window Time                          | Tow                |                                                                                      | 37              | 40                  | 42.88     | ms    |

| Watchdog Time                             | $T_{WD}$           |                                                                                      | 92.5            | 100                 | 107.2     |       |

| Watchdog Reset Pulse Width if no TCL      | $T_{WDR}$          |                                                                                      | 2.25            | 2.5                 | 2.75      |       |

| Version V50                               |                    |                                                                                      |                 |                     |           |       |

| Power-on Reset delay                      | T <sub>POR</sub>   | R <sub>OSC</sub> = 121.6 kΩ ±1%                                                      | 91.6            | 100                 | 108.3     |       |

| Closed Window Time                        | T <sub>CW</sub>    |                                                                                      | 74              | 80                  | 85.76     |       |

| Open Window Time                          | T <sub>OW</sub>    |                                                                                      | 37              | 40                  | 42.88     | ms    |

| Watchdog Time                             | T <sub>WD</sub>    |                                                                                      | 92.5            | 100                 | 107.2     |       |

| Watchdog Reset Pulse Width if no TCL      | T <sub>WDR</sub>   |                                                                                      | 2.25            | 2.5                 | 2.75      |       |

| Version V53                               |                    |                                                                                      |                 |                     |           |       |

| Power-on Reset delay                      | T <sub>POR</sub>   | $R_{OSC} = 23.2 \text{ k}\Omega \pm 1\%$                                             | 4.57            | 5.0                 | 5.44      |       |

| Closed Window Time                        | T <sub>CW</sub>    |                                                                                      | 9.24            | 10                  | 10.77     |       |

| Open Window Time                          | T <sub>OW</sub>    |                                                                                      | 18.48           | 20                  | 21.54     | ms    |

| Watchdog Time                             | $T_{WD}$           |                                                                                      | 18.48           | 20                  | 21.54     |       |

| Watchdog Reset Pulse Width if no TCL      | $T_{WDR}$          |                                                                                      | 0.56            | 0.625               | 0.69      |       |

| Version V55                               |                    |                                                                                      |                 |                     |           |       |

| Power-on Reset delay                      | T <sub>POR</sub>   | $R_{OSC} = 107.5 \text{ k}\Omega \pm 1\%$                                            | 91.6            | 100                 | 108.3     |       |

| Closed Window Time                        | $T_CW$             |                                                                                      | 74              | 80                  | 85.76     |       |

| Open Window Time                          | Tow                |                                                                                      | 37              | 40                  | 42.88     |       |

| Watchdog Time                             | $T_{WD}$           |                                                                                      | 92.5            | 100                 | 107.2     | ms    |

| Watchdog Reset Pulse Width if no TCL      | T <sub>WDR</sub>   |                                                                                      | 2.25            | 2.5                 | 2.75      |       |

| Watchdog Reset Pulse Width in Sleep Mode  | T <sub>WDRS</sub>  | $R_{OSC}$ off; $R_{INT}$ =1 $M\Omega$                                                | 2.8             | 3.2                 | 3.6       |       |

| Watchdog Reset Pulse Period in Sleep Mode | T <sub>WDRPS</sub> | TCL inactive                                                                         | 750             | 1100                | 1450      | 1     |

Table 4

# **Timing Waveforms**

### **Watchdog Timeout Period**

Fig. 4

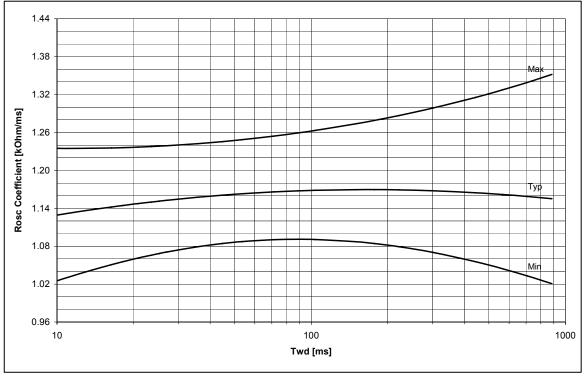

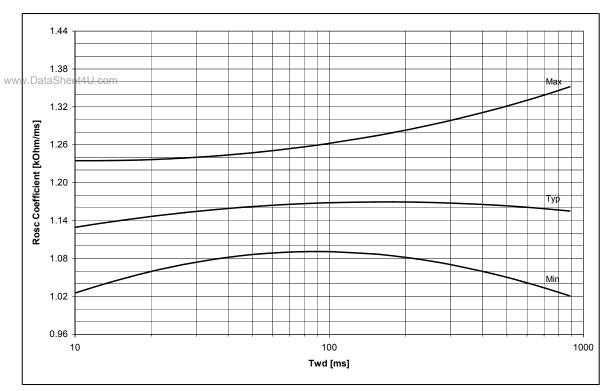

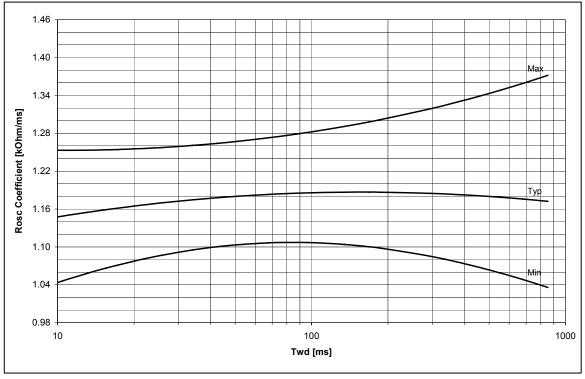

www.For different values of  $T_{WD}$  and  $R_{OSC}$ , see figures 9 to 12.

#### **Voltage Monitoring**

Fig. 5

#### **Timer Reaction**

Fig. 6

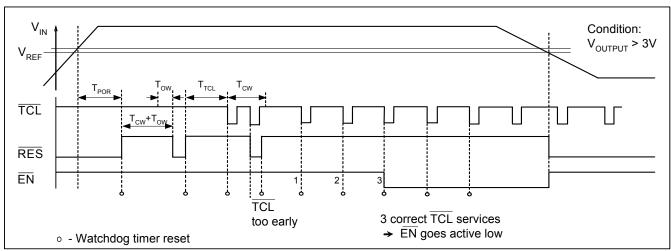

### **Combined Voltage and Timer Reaction**

Fig. 7

#### **Functional Description**

#### **VIN Monitoring**

The power-on reset and the power-down reset are generated as a response to the external voltage level applied on the  $V_{\text{IN}}$  input. The threshold voltage at which reset is asserted or released ( $V_{\text{RESET}}$ ) is determined by the external voltage divider between  $V_{\text{DD}}$  and  $V_{\text{SS}}$ , as shown on Fig. 8. A part of  $V_{\text{DD}}$  is compared to the internal voltage reference. To determine the values of the divider, the leakage current at  $V_{\text{IN}}$  must be taken into account as well as the current consumption of the divider itself. Low resistor values will need more current, but high resistor values will make the reset threshold less accurate at high temperature, due to a possible leakage current at the  $V_{\text{IN}}$  input. The sum of the two resistors ( $R_1+R_2$ ) should stay below 500 k $\Omega$ . The formula is:

$$V_{RESET} = V_{REF} x (1 + R_1/R_2).$$

Example: choosing  $R_1$  = 200 k $\Omega$  and  $R_2$  = 100 k $\Omega$  gives  $V_{RESET}$  =4.56 V (typical) for version V50 and V53.

At power-up the reset output ( $\overline{RES}$ ) is held low (see Fig. 5). When  $V_{IN}$  becomes greater than  $V_{REF}$ , the  $\overline{RES}$  output is held low for an additional power-on-reset (POR) delay  $T_{POR}$  (defined with the external resistor connected at  $R_{OSC}$  pin). The  $T_{POR}$  delay prevents repeated toggling of  $\overline{RES}$  even if  $V_{DD}$  voltage drops out and recovers. The  $T_{POR}$  delay allows the microprocessor's crystal oscillator time to start and stabilize and ensures correct recognition of the reset signal to the microprocessor.

The RES output goes active low generating the power-down reset whenever  $V_{\text{IN}}$  falls below  $V_{\text{REF}}$ . The sensitivity or reaction time of the internal comparator to the voltage level on  $V_{\text{IN}}$  is typically 3  $\mu s$ .

#### **Timer Programming**

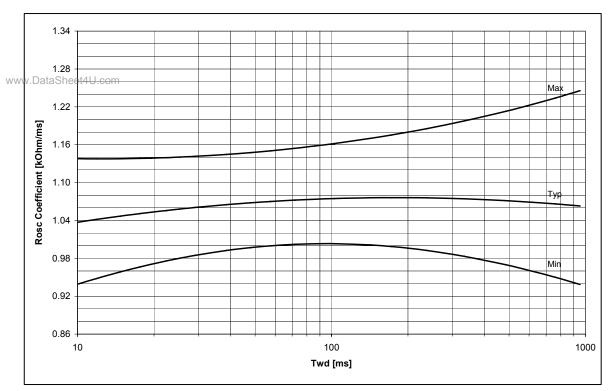

wwwThetonichip oscillator allows the user to adjust the power-on reset (POR) delay  $T_{POR}$  and the watchdog time  $T_{WD}$  by changing the resistor value of the external resistor  $R_{OSC}$  connected between the pin  $R_{OSC}$  and  $V_{SS}$  (see Fig. 8). The closed and open window times ( $T_{CW}$  and  $T_{OW}$ ) as well as the watchdog reset pulse width ( $T_{WDR}$ ), which are  $T_{TCL}$  dependent, will vary accordingly. The watchdog time  $T_{WD}$  can be obtained with figures 9 to 12 or with the Excel application EM6151ResCalc.xls available on EM website.  $T_{POR}$  is equal to  $T_{WD}$  with the minimum and maximum tolerances increased by 1% (For Version 53,  $T_{POR}$  is one fourth of  $T_{WD}$ ).

Note that the current consumption increases as the frequency increases.

#### Voltage Regulator

The EM6152 has a 5 V, 400 mA, low dropout voltage regulator. The low supply current makes the EM6152 particularly suitable for automotive systems which remain continuously powered. The input voltage range is 2.3 V to 40 V for operation and the input protection includes both reverse battery (42 V below ground) and load dump (positive transients up to 45 V). There is no reverse current flow from the OUTPUT to the INPUT when the INPUT equals  $V_{\rm SS}$ . This feature is important for systems which need to implement (with capacitance) a minimum power supply hold-up time in the event of power failure. To achieve

good load regulation a 22  $\mu F$  capacitor (or greater) is needed on the INPUT (see Fig. 8). Tantalum or aluminium electrolytic are adequate for the 22  $\mu F$  capacitor; film types will work but are relatively expensive. Many aluminium electrolytic have electrolytes that freeze at about  $-30^{\circ}C$ , so tantalums are recommended for operation below  $-25^{\circ}C$ . The important parameters of the 22  $\mu F$  capacitor are an effective series resistance of lower than 3  $\Omega$  and a resonant frequency above 500 kHz.

A 22  $\mu$ F capacitor (or greater) and a 100 nF capacitor are required on the OUTPUT to prevent oscillations due to instability. The specification of the 22  $\mu$ F capacitor is as per the 22  $\mu$ F capacitor on the INPUT (see previous paragraph).

The EM6152 will remain stable and in regulation with no external load and the dropout voltage is typically constant as the input voltage fall below its minimum level (see Table 2). These features are especially important in CMOS RAM keep-alive applications.

#### **Power Dissipation**

Care must be taken not to exceed the maximum junction temperature (+125°C). The power dissipation within the EM6152 is given by the formula:

$$P_{TOTAL} = (V_{INPUT} - V_{OUTPUT}) \times I_{OUTPUT} + (V_{INPUT}) \times I_{SS}$$

The maximum continuous power dissipation at a given temperature can be calculated using the formula:

$$P_{MAX} = (125^{\circ}C - T_{A}) / R_{th(j-a)}$$

where  $R_{th(j-a)}$  is the thermal resistance from the junction to the ambient and is specified in Table 2. Note that  $R_{th(j-a)}$  given in Table 2 assumes that the package is soldered to a PCB (see figure 16). The above formula for maximum power dissipation assumes a constant load (i.e. >100 s). The transient thermal resistance for a single pulse is much lower than the continuous value.

#### **CAN-Bus Sleep Mode Detector (version 55)**

When the microcontroller goes into a standby mode, it implies that it does not send any pulses on the  $\overline{TCL}$  input of the EM6152. After three reset pulse periods ( $T_{CW}+T_{OW}+T_{WDR}$ ) on the  $\overline{RES}$  output, the circuit switches on an internal resistor of 1  $M\Omega$ , and it will have a reset pulse of typically 3 ms every 1 second on the  $\overline{RES}$  output. When a  $\overline{TCL}$  edge (rising or falling) appears on the  $\overline{TCL}$  input or the power supply goes down and up, the circuit switches to the  $R_{OSC}$ .

#### **Watchdog Timeout Period Description**

The watchdog timeout period is divided into two periods, a closed window period ( $T_{CW}$ ) and an open window period ( $T_{CW}$ ), see Fig. 4. If no pulse is applied on the  $\overline{TCL}$  input during the open window period  $T_{OW}$ , the  $\overline{RES}$  output goes low for a time  $T_{WDR}$ . When a pulse is applied on the  $\overline{TCL}$  input, the cycle is restarted with a close window period.

For example if  $T_{WD}$  =  $T_{POR}$  = 100ms,  $T_{CW}$  = 80 ms,  $T_{OW}$  = 40ms and  $T_{WDR}$  = 2.5ms.

When  $V_{IN}$  recovers after a drop below  $V_{REF}$ , the pad  $\overline{RES}$  is set low for the time  $T_{POR}$  during which any  $\overline{TCL}$  activation is disabled.

#### Timer Clearing and RES Action

The watchdog circuit monitors the activity of the processor. If the user's software does not send a pulse to the  $\overline{TCL}$  input within the programmed open window timeout period a short watchdog  $\overline{RES}$  pulse is generated which is equal to  $T_{WDR}$  (see Fig. 6).

With the open window constraint, new security is added to conventional watchdogs by monitoring both software cycle time and execution. Should software clear the watchdog too quickly (incorrect cycle time) or too slowly (incorrect execution) it will cause the system to be reset. If software is stuck in a loop which includes the routine to clear the watchdog then a conventional watchdog would not make a system reset even though the software is malfunctioning; the circuit would make a system reset because the watchdog would be cleared too quickly.

If no  $\overline{TCL}$  signal is applied before the closed and open windows expire,  $\overline{RES}$  will start to generate square waves of period  $T_{WDRP} = T_{CW} + T_{OW} + T_{WDR}$ . The watchdog will remain in this state until the next  $\overline{TCL}$  falling edge appears during an open window, or until a fresh power-up sequence. The system enable output,  $\overline{EN}$ , can be used to prevent critical control functions being activated in the event of the system going into this failure mode (see section "Enable- $\overline{EN}$  Output").

The  $\overline{RES}$  output must be pulled up to  $V_{OUTPUT}$  even if the output is not used by the system (see Fig 8).

#### **Combined Voltage and Timer Action**

The combination of voltage and timer actions is illustrated by the sequence of events shown in Fig. 6. On power-up, when the voltage at  $V_{IN}$  reaches  $V_{REF}$ , the power-on-reset, POR, delay is initialized and holds  $\overline{RES}$  active for the time

of the POR delay. A  $\overline{TCL}$  pulse will have no effect until this power-on-reset delay is completed. When the risk exists that  $\overline{TCL}$  temporarily floats, e.g. during  $T_{POR}$ , a pull-up to  $V_{OUTPUT}$  is required on that pin. After the POR delay has elapsed,  $\overline{RES}$  goes inactive and the watchdog timer starts acting. If no  $\overline{TCL}$  pulse occurs,  $\overline{RES}$  goes active low for a short time  $T_{WDR}$  after each closed and open window period. A  $\overline{TCL}$  pulse coming during the open window clears the watchdog timer. When the  $\overline{TCL}$  pulse occurs too early (during the closed window),  $\overline{RES}$  goes active and a new timeout sequence starts. A voltage drop below the  $V_{REF}$  level for longer than typically  $3\mu s$  overrides the timer and immediately forces  $\overline{RES}$  active and  $\overline{EN}$  inactive. Any further  $\overline{TCL}$  pulse has no effect until the next power-up sequence has completed.

### Enable - EN Output

The system enable output,  $\overline{\text{EN}}$ , is inactive always when  $\overline{\text{RES}}$  is active and remains inactive after a  $\overline{\text{RES}}$  pulse until the watchdog is serviced correctly 3 consecutive times (i.e. the  $\overline{\text{TCL}}$  pulse must come in the open window). After three consecutive services of the watchdog with  $\overline{\text{TCL}}$  during the open window, the  $\overline{\text{EN}}$  goes active low.

A malfunctioning system would be repeatedly reset by the watchdog. In a conventional system critical motor controls could be energized each time reset goes inactive (time allowed for the system to restart) and in this way the electrical motors driven by the system could function out of control. The circuit prevents the above failure mode by using the  $\overline{\text{EN}}$  output to disable the motor controls until software has successfully cleared the watchdog three times (i.e. the system has correctly re-started after a reset condition).

# **Typical Application**

www.DataSheet4U.com

Fig. 8

The important parameters of the 22  $\mu F$  input capacitor are an effective series resistance lower than 3  $\Omega$  and a resonant frequency above 500 kHz.

# V30 $R_{OSC}$ Coefficient versus $T_{WD}$ at $V_{DD}$ = 5.0V and $T_j$ =-40 to +125°C

Fig. 9

# V50 $R_{OSC}$ Coefficient versus $T_{WD}$ at $V_{DD}$ = 5.0V and $T_j$ =-40 to +125°C

Fig. 10

# V53 R $_{OSC}$ Coefficient versus $T_{WD}$ at $V_{DD}$ = 5.0V and $T_{j}$ =-40 to +125°C

Fig. 11

# V55 $R_{OSC}$ Coefficient versus $T_{WD}$ at $V_{DD}$ = 5.0V and $T_j$ =-40 to +125°C

Fig. 12

# Typical maximum OUTPUT current versus INPUT voltage

Fig. 13

www.DataSheet4U.com

#### **Package Information**

# **Dimensions of 8-pin SOIC Package**

Fig. 14

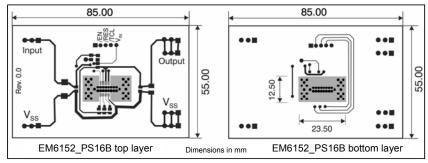

#### **Dimensions of PSOP2-16 Package**

Fig. 15

#### **Dual Layer PCB**

Fig. 16

EM Microelectronic-Marin SA (EM) makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in EM's General Terms of Sale located on the Company's web site. EM assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of EM are granted in connection with the sale of EM products, expressly or by implications. EM's products are not authorized for use as components in life support devices or systems.

### SUBJECT TO CHANGE WITHOUT NOTICE