## DS26502 T1/E1/J1/64KCC BITS Element

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS26502 is a building-integrated timingsupply (BITS) clock-recovery element. It also functions as a basic T1/E1 transceiver. The receiver portion can recover a clock from T1, E1, 64kHz composite clock (64KCC), and 6312kHz synchronization timing interfaces. In T1 and E1 modes, the Synchronization Status Message (SSM) can also be recovered. The transmit portion can directly interface to T1, E1, or 64KCC synchronization interfaces as well as source the SSM in T1 and E1 modes. The DS26502 can translate between any of the supported inbound synchronization clock rates to any supported outbound rate. A separate output is provided to source a 6312kHz clock. The device is controlled through a parallel, serial, or hardware controller port.

#### **APPLICATIONS**

BITS Timing Rate Conversion

#### ORDERING INFORMATION

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS26502L  | 0°C to +70°C   | 64 LQFP     |

| DS26502LN | -40°C to +85°C | 64 LQFP     |

#### **FEATURES**

- G.703 2048kHz Synchronization Interface Compliant

- G.703 64kHz Centralized (Option A) and Codirectional Timing Interface Compliant

- G.703 Appendix II 64kHz and 6312kHz Japanese Synchronization Interface Compliant

- Interfaces to Standard T1/J1 (1.544MHz) and E1 (2.048MHz)

- Interface to CMI-Coded T1/J1 and E1

- Short- and Long-Haul Line Interface

- Transmit and Receive T1 and E1 SSM Messages with Message Validation

- T1/E1 Jitter Attenuator with Bypass Mode

- Fully Independent Transmit and Receive Functionality

- Internal Software-Selectable Receive- and Transmit-Side Termination for  $75\Omega/100\Omega/110\Omega/120\Omega$  T1, E1, and Composite Clock Interfaces

- Monitor Mode for Bridging Applications

- Accepts 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz Master Clock

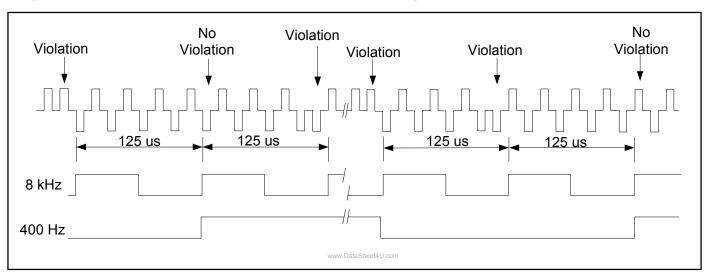

- 64kHz, 8kHZ, and 400Hz Outputs in Composite Clock Mode

- 8-Bit Parallel Control Port, Multiplexed or Nonmultiplexed, Intel or Motorola

- Serial (SPI) Control Port

- Hardware Control Mode

- Provides LOS, AIS, and LOF Indications Through Hardware Output Pins

- Fast Transmitter-Output Disable Through Device Pin for Protection Switching

- IEEE 1149.1 JTAG Boundary Scan

- 3.3V Supply with 5V-Tolerant Inputs and Outputs

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="https://www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

## **TABLE OF CONTENTS**

| 1.         | FEATURES                                  | 7  |

|------------|-------------------------------------------|----|

| 1.1        | GENERAL                                   | 7  |

| 1.2        | LINE INTERFACE                            |    |

| 1.3        | JITTER ATTENUATOR (T1/E1 MODES ONLY)      | 7  |

| 1.4        | FRAMER/FORMATTER                          |    |

| 1.5        | TEST AND DIAGNOSTICS                      | 8  |

| 1.6        | CONTROL PORT                              | 8  |

| 2.         | SPECIFICATIONS COMPLIANCE                 | 9  |

| 3.         | BLOCK DIAGRAMS                            | 11 |

| 4.         | PIN FUNCTION DESCRIPTION                  | 14 |

| 4.1        | Transmit PLL                              | 14 |

| 4.2        | TRANSMIT SIDE                             |    |

| 4.3        | RECEIVE SIDE                              |    |

| 4.4        | CONTROLLER INTERFACE                      |    |

| 4.5        | JTAG                                      | 20 |

| 4.6        | LINE INTERFACE                            | 20 |

| 4.7        | Power                                     | 21 |

| <b>5</b> . | PINOUT                                    | 22 |

| <b>6</b> . | HARDWARE CONTROLLER INTERFACE             | 25 |

| 6.1        | TRANSMIT CLOCK SOURCE www.DataSheet4U.com | 25 |

| 6.2        | INTERNAL TERMINATION                      |    |

| 6.3        | LINE BUILD-OUT.                           |    |

| 6.4        | Receiver Operating Modes                  |    |

| 6.5        | Transmitter Operating Modes               | 27 |

| 6.6        | MCLK Pre-Scaler                           |    |

| 6.7        | OTHER HARDWARE CONTROLLER MODE FEATURES   | 28 |

| <b>7</b> . | PROCESSOR INTERFACE                       | 29 |

| 7.1        | PARALLEL PORT FUNCTIONAL DESCRIPTION      | 29 |

| 7.2        |                                           | 29 |

|            | 2.1 Clock Phase and Polarity              | 29 |

|            | 2.2 Bit Order                             |    |

|            | 2.3 Control Byte                          |    |

|            | 2.4 Burst Mode                            |    |

|            | 2.5 Register Writes                       |    |

|            | 2.6 Register Reads                        |    |

| 7.3        |                                           |    |

|            | 3.1 Power-Up Sequence                     |    |

|            | 3.2 Test Reset Register                   |    |

| 7.4        |                                           |    |

| 7.4        | STATUS REGISTERS                          |    |

| 7.6        | INFORMATION REGISTERS                     |    |

|            |                                           |    |

| 7.7                                                                              | Interrupt Information Registers                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 8.                                                                               | T1 FRAMER/FORMATTER CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                  | 39 |

| 8.1                                                                              | T1 CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39 |

| 9.                                                                               | E1 FRAMER/FORMATTER CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

| 9.1<br>9.2                                                                       | E1 CONTROL REGISTERSE1 INFORMATION REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 10.                                                                              | I/O PIN CONFIGURATION OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                          | 51 |

| 11.                                                                              | T1 SYNCHRONIZATION STATUS MESSAGE                                                                                                                                                                                                                                                                                                                                                                                                                      | 54 |

| 11.1<br>11.2<br>11.3                                                             | Pransmit BOC                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

| <b>12</b> .                                                                      | E1 SYNCHRONIZATION STATUS MESSAGE                                                                                                                                                                                                                                                                                                                                                                                                                      | 63 |

| 12.1<br>12.2                                                                     | ALTERNATE SA/SI BIT ACCESS BASED ON DOUBLE-FRAME                                                                                                                                                                                                                                                                                                                                                                                                       | 73 |

| 13.                                                                              | LINE INTERFACE UNIT (LIU)                                                                                                                                                                                                                                                                                                                                                                                                                              | 76 |

| 13.1<br>13.2<br>13<br>13<br>13.3<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7<br>13.8 | LIU OPERATION LIU RECEIVER 3.2.1 Receive Level Indicator 3.2.2 Receive G.703 Section 10 Synchronization Signal 3.2.3 Monitor Mode LIU TRANSMITTER 3.3.1 Transmit Short-Circuit Detector/Limiter 3.3.2 Transmit Open-Circuit Detector 3.3.3 Transmit BPV Error Insertion 3.3.4 Transmit G.703 Section 10 Synchronization Signal (E1 Mode) MCLK PRE-SCALER JITTER ATTENUATOR CMI (CODE MARK INVERSION) OPTION LIU CONTROL REGISTERS RECOMMENDED CIRCUITS |    |

| 14.                                                                              | LOOPBACK CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| <b>15</b> .                                                                      | 64KHZ SYNCHRONIZATION INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                        | 95 |

| 15.1<br>15.2                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 16.                                                                              | 6312KHZ SYNCHRONIZATION INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                      | 97 |

| 16.1<br>16.2                                                                     | Pransmit 6312kHz Synchronization Interface Operation                                                                                                                                                                                                                                                                                                                                                                                                   | 97 |

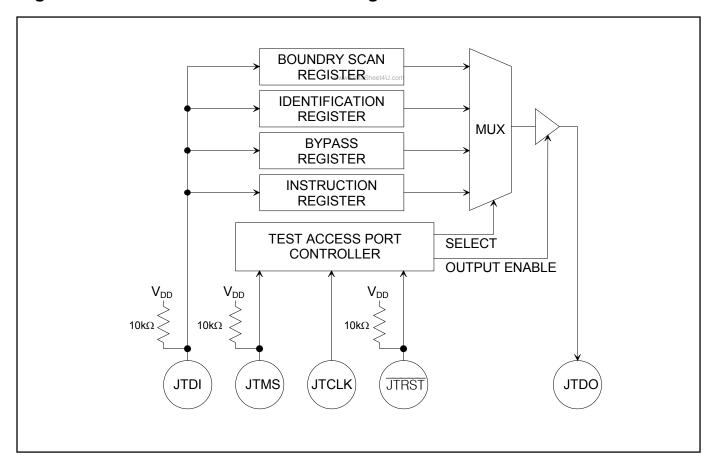

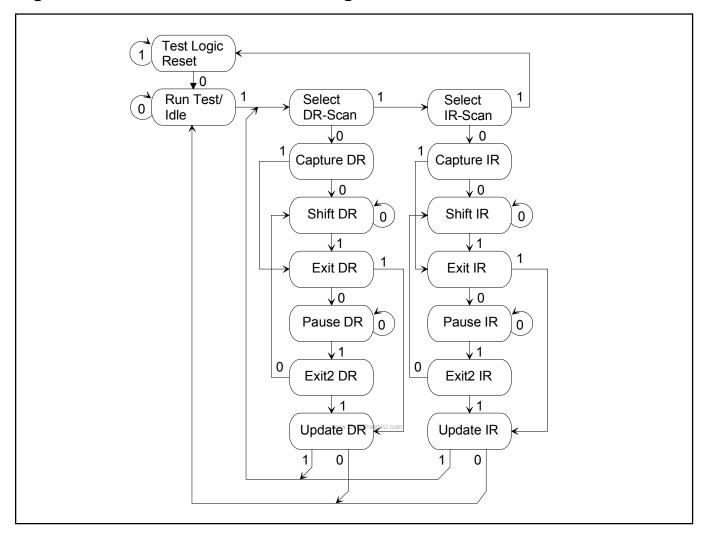

| 17.                                                                              | JTAG BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT                                                                                                                                                                                                                                                                                                                                                                                                   | 98 |

| 17.1<br>17.2                                                                     | Instruction Register  Test Registers                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 17.3                         | BOUNDARY SCAN REGISTER           | 103                      |

|------------------------------|----------------------------------|--------------------------|

| 17.4                         | Bypass Register                  |                          |

| 17.5                         | IDENTIFICATION REGISTER          |                          |

| 18. F                        | UNCTIONAL TIMING DIAGRAMS        | 106                      |

| 18.1                         | Processor Interface              | 106                      |

|                              | .1 Parallel Port Mode            |                          |

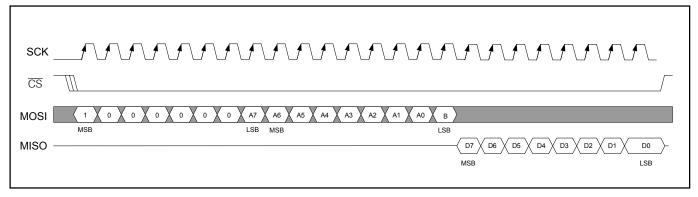

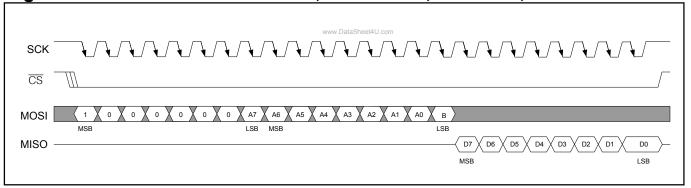

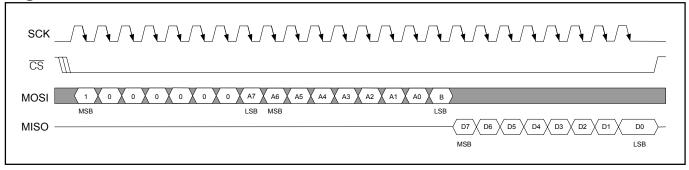

|                              | .2 SPI Serial Port Mode          |                          |

| 19. C                        | PERATING PARAMETERS              | 109                      |

| 20. <i>A</i>                 | C TIMING PARAMETERS AND DIAGRAMS | 111                      |

|                              |                                  |                          |

| 20.1                         | MULTIPLEXED BUS                  | 111                      |

| 20.1<br>20.2                 | MULTIPLEXED BUS                  | 114                      |

|                              | NONMULTIPLEXED BUS               | 114                      |

| 20.2                         |                                  | 114<br>117               |

| 20.2                         | NONMULTIPLEXED BUS               | 114<br>117<br>119        |

| 20.2<br>20.3<br>20.4<br>20.5 | NONMULTIPLEXED BUS               | 114<br>117<br>119<br>121 |

www.DataSheet4U.com

## **LIST OF FIGURES**

| Figure 3-1. Block Diagram                                           |     |

|---------------------------------------------------------------------|-----|

| Figure 3-2. Loopback Mux Diagram (T1/E1 Modes Only)                 | 12  |

| Figure 3-3. Transmit PLL Clock Mux Diagram                          | 12  |

| Figure 3-4. Master Clock PLL Diagram                                |     |

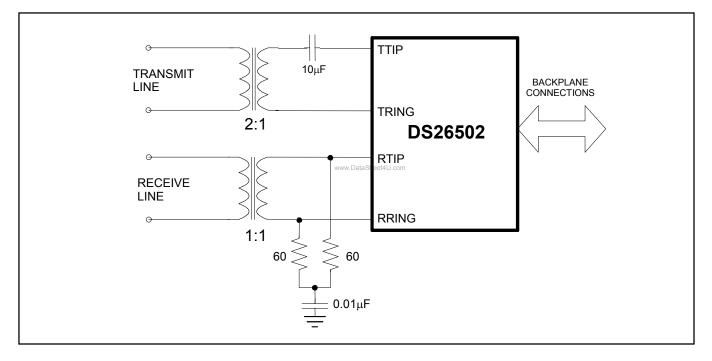

| Figure 13-1. Basic Network Connection                               | 76  |

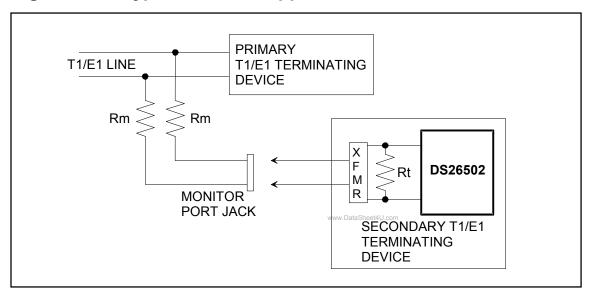

| Figure 13-2. Typical Monitor Application                            | 78  |

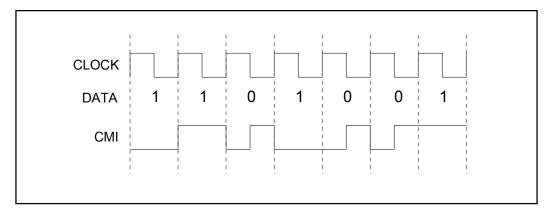

| Figure 13-3. CMI Coding                                             |     |

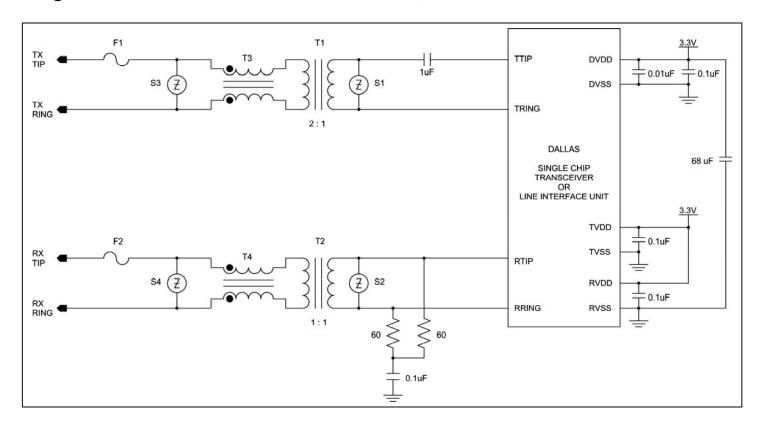

| Figure 13-4. Software-Selected Termination, Metallic Protection     |     |

| Figure 13-5. Software-Selected Termination, Longitudinal Protection |     |

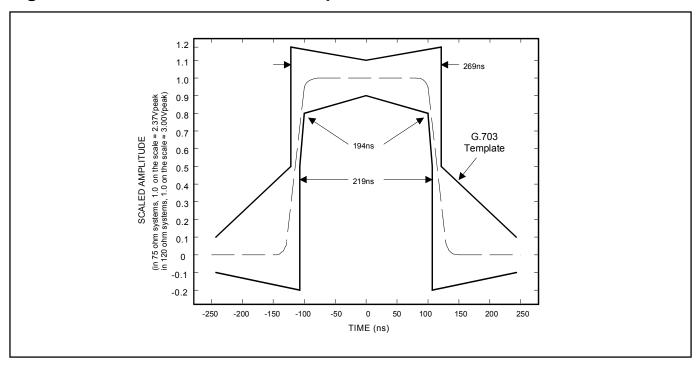

| Figure 13-6. E1 Transmit Pulse Template                             |     |

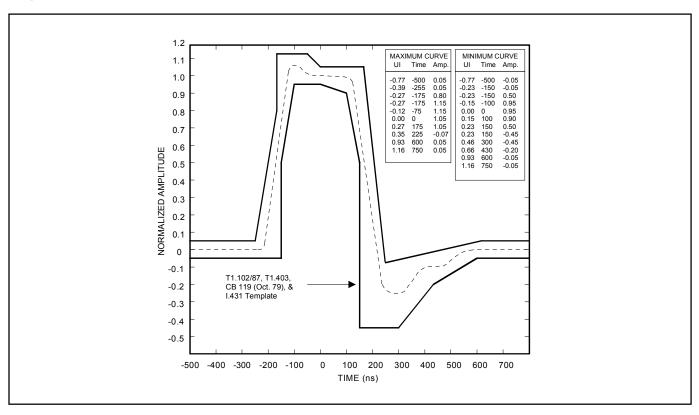

| Figure 13-7. T1 Transmit Pulse Template                             |     |

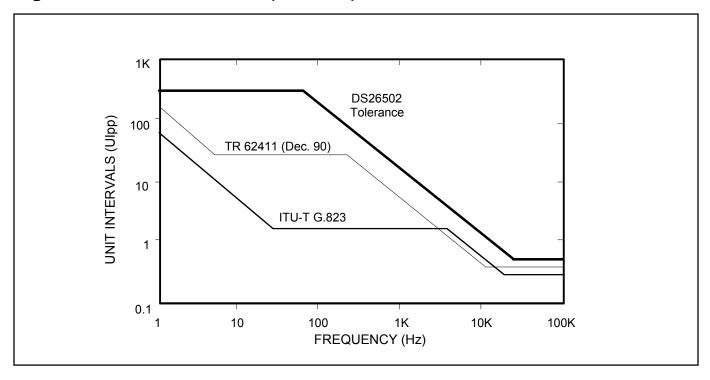

| Figure 13-8. Jitter Tolerance (T1 Mode)                             |     |

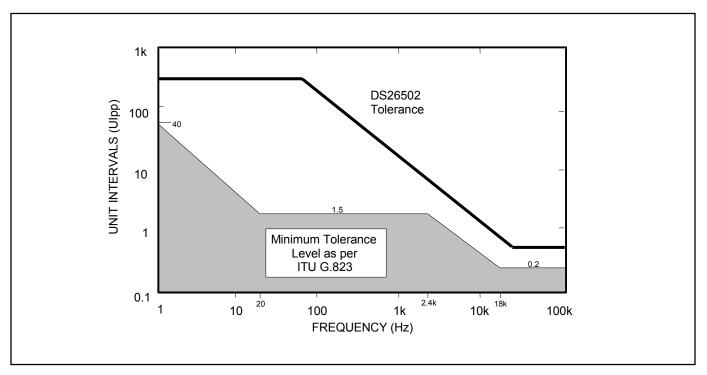

| Figure 13-9. Jitter Tolerance (E1 Mode)                             |     |

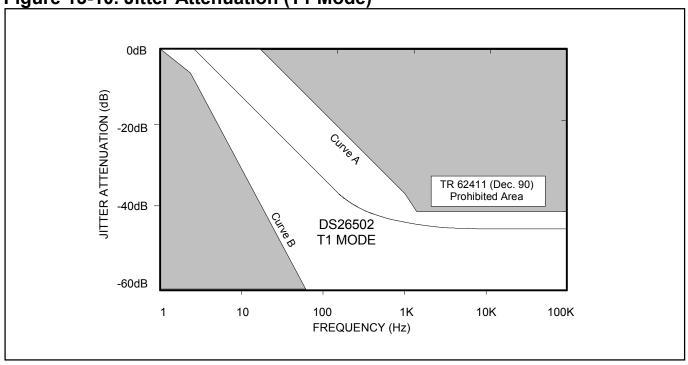

| Figure 13-10. Jitter Attenuation (T1 Mode)                          |     |

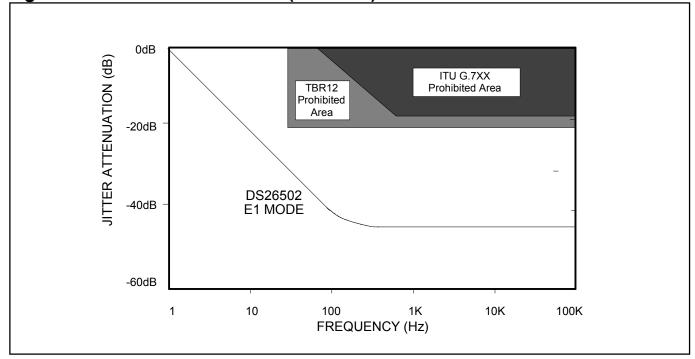

| Figure 13-11. Jitter Attenuation (E1 Mode)                          |     |

| Figure 15-1. 64kHz Composite Clock Mode Signal Format               |     |

| Figure 17-1. JTAG Functional Block Diagram                          |     |

| Figure 17-2. TAP Controller State Diagram                           |     |

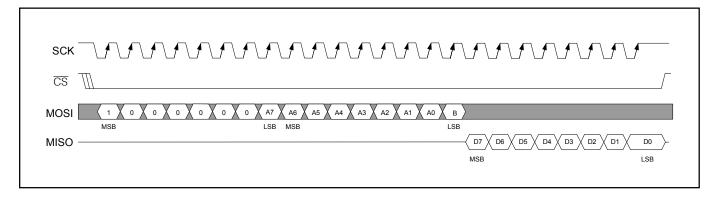

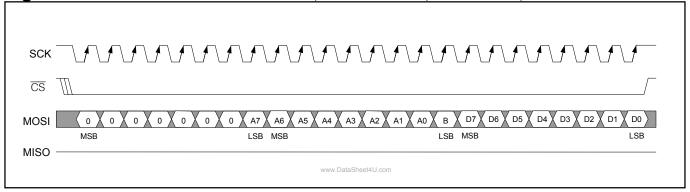

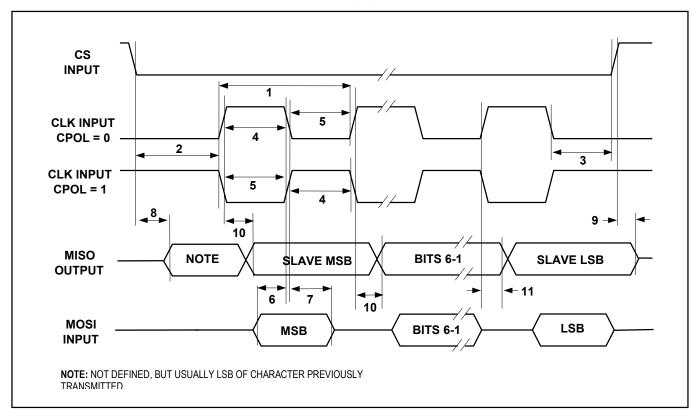

| Figure 18-1. SPI Serial Port Access, Read Mode, CPOL = 0, CPHA = 0  |     |

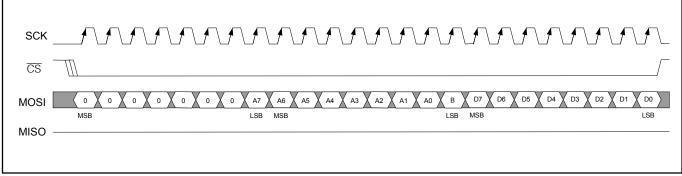

| Figure 18-2. SPI Serial Port Access, Read Mode, CPOL = 1, CPHA = 0  |     |

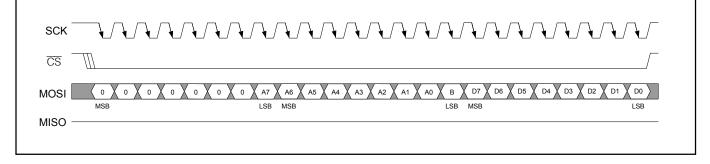

| Figure 18-3. SPI Serial Port Access, Read Mode, CPOL = 0, CPHA = 1  |     |

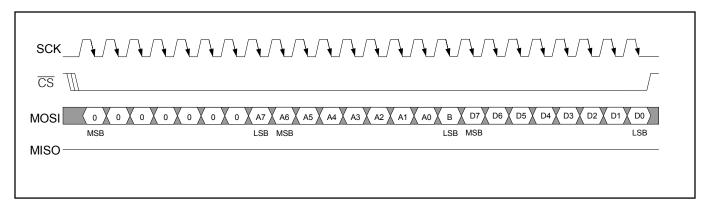

| Figure 18-4. SPI Serial Port Access, Read Mode, CPOL = 1, CPHA = 1  |     |

| Figure 18-5. SPI Serial Port Access, Write Mode, CPOL = 0, CPHA = 0 |     |

| Figure 18-6. SPI Serial Port Access, Write Mode, CPOL = 1, CPHA = 0 |     |

| Figure 18-7. SPI Serial Port Access, Write Mode, CPOL = 0, CPHA = 1 |     |

| Figure 18-8. SPI Serial Port Access, Write Mode, CPOL = 1, CPHA = 1 |     |

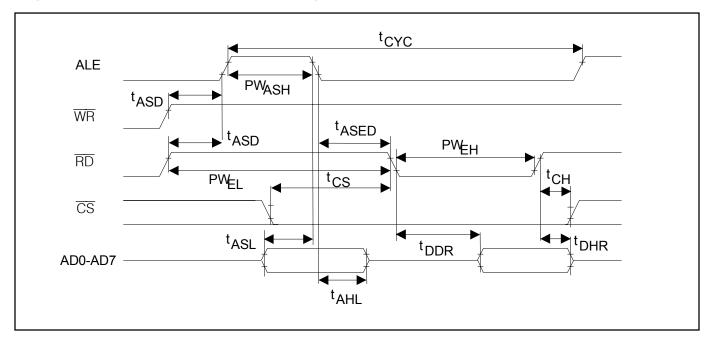

| Figure 20-1. Intel Bus Read Timing (BTS = 0 / BIS[1:0] = 00)        |     |

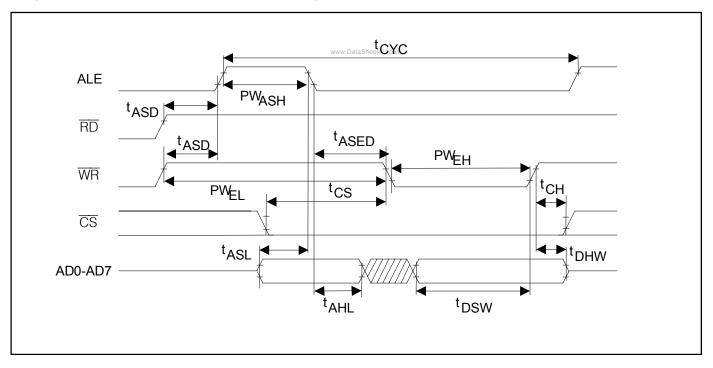

| Figure 20-2. Intel Bus Write Timing (BTS = 0 / BIS[1:0] = 00)       |     |

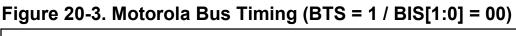

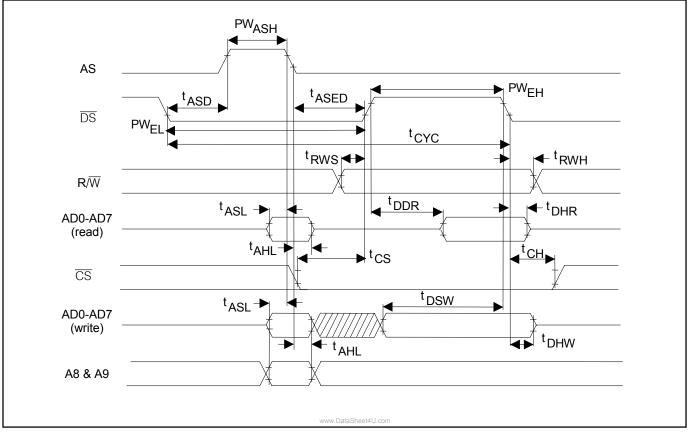

| Figure 20-3. Motorola Bus Timing (BTS = 1 / BIS[1:0] = 00)          |     |

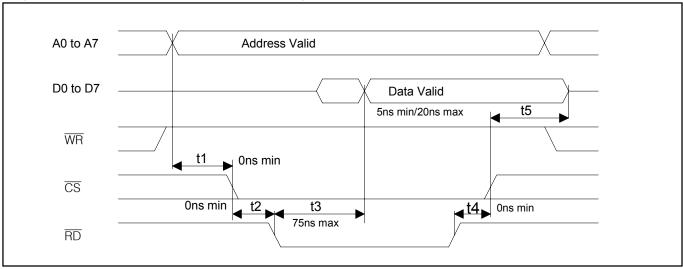

| Figure 20-4. Intel Bus Read Timing (BTS = 0 / BIS[1:0] = 01)        |     |

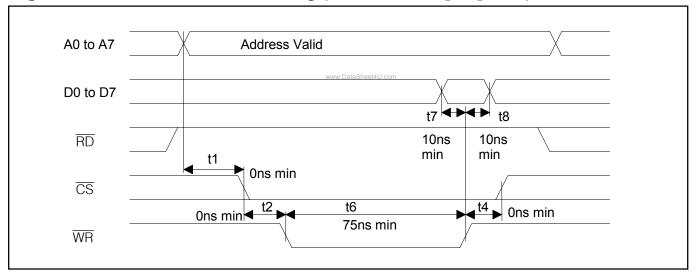

| Figure 20-5. Intel Bus Write Timing (BTS = 0 / BIS[1:0] = 01)       |     |

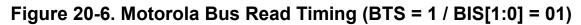

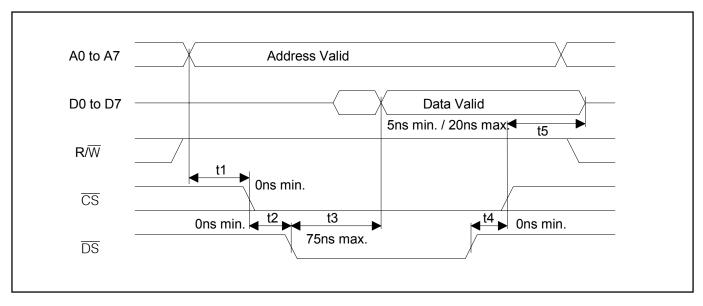

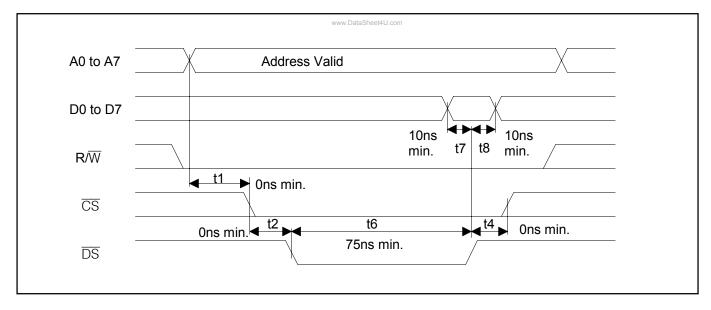

| Figure 20-6. Motorola Bus Read Timing (BTS = 1 / BIS[1:0] = 01)     |     |

| Figure 20-7. Motorola Bus Write Timing (BTS = 1 / BIS[1:0] = 01)    |     |

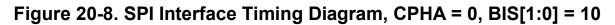

| Figure 20-8. SPI Interface Timing Diagram, CPHA = 0, BIS[1:0] = 10  |     |

| Figure 20-9. SPI Interface Timing Diagram, CPHA = 1, BIS[1:0] = 10  |     |

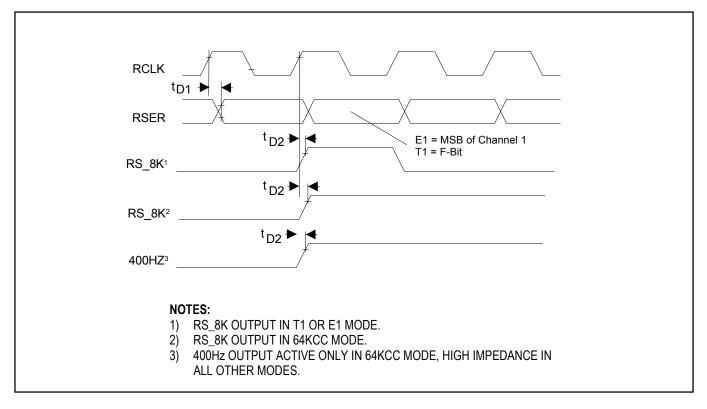

| Figure 20-10. Receive Timing, T1, E1, 64KCC Mode                    |     |

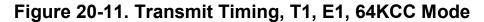

| Figure 20-11. Transmit Hilling, 11, E1, 04NOC Wode                  | 122 |

## **LIST OF TABLES**

| Table 2-1. T1-Related Telecommunications Specifications                             | 9   |

|-------------------------------------------------------------------------------------|-----|

| Table 2-2. E1-Related Telecommunications Specifications                             | 10  |

| Table 5-1. LQFP Pinout                                                              | 22  |

| Table 6-1. Transmit Clock Source                                                    | 25  |

| Table 6-2. Internal Termination                                                     | 25  |

| Table 6-3. E1 Line Build-Out                                                        | 26  |

| Table 6-4. T1 Line Build-Out                                                        |     |

| Table 6-5. Receive Path Operating Mode                                              | 26  |

| Table 6-6.Transmit Path Operating Mode                                              | 27  |

| Table 6-7. MCLK Pre-Scaler for T1 Mode                                              | 27  |

| Table 6-8. MCLK Pre-Scaler for E1 Mode                                              | 28  |

| Table 6-9. Other Operational Modes                                                  | 28  |

| Table 7-1. Port Mode Select                                                         | 29  |

| Table 7-2. Register Map Sorted By Address                                           | 31  |

| Table 8-1. T1 Alarm Criteria                                                        |     |

| Table 9-1. E1 Sync/Resync Criteria                                                  | 46  |

| Table 9-2. E1 Alarm Criteria                                                        |     |

| Table 10-1. TS_8K_4 Pin Functions                                                   | 52  |

| Table 10-2. RLOF_CCE Pin Functions                                                  | 52  |

| Table 11-1. T1 SSM Messages                                                         | 54  |

| Table 12-1. E1 SSM Messages                                                         |     |

| Table 13-1. Component List (Software-Selected Termination, Metallic Protection)     | 89  |

| Table 13-2. Component List (Software-Selected Termination, Longitudinal Protection) | 90  |

| Table 15-1. Specification of 64kHz Clock Signal at Input Port                       |     |

| Table 15-2. Specification of 64kHz Clock Signal at Output Port                      | 96  |

| Table 16-1. Specification of 6312kHz Clock Signal at Input Port                     | 97  |

| Table 16-2. Specification of 6312kHz Clock Signal at Output Port                    |     |

| Table 17-1. Instruction Codes for IEEE 1149.1 Architecture                          |     |

| Table 17-2. ID Code Structure                                                       | 103 |

| Table 17-3. Device ID Codes                                                         |     |

| Table 17-4. Boundary Scan Control Bits                                              | 104 |

| Table 19-1. Thermal Characteristics                                                 | 109 |

| Table 19-2. Theta-JA ( $\theta_{JA}$ ) vs. Airflow                                  | 109 |

| Table 19-3. Recommended DC Operating Conditions                                     | 109 |

| Table 19-4. Capacitance                                                             | 109 |

| Table 19-5. DC Characteristics                                                      | 110 |

| Table 20-1. AC Characteristics, Multiplexed Parallel Port                           | 111 |

| Table 20-2. AC Characteristics, Non-Mux Parallel Port                               | 114 |

| Table 20-3. AC Characteristics, Serial Bus                                          | 117 |

| Table 20-4. Receive Side AC Characteristics                                         | 119 |

| Table 20-5 Transmit Side AC Characteristics                                         | 121 |

#### 1. FEATURES

#### 1.1 General

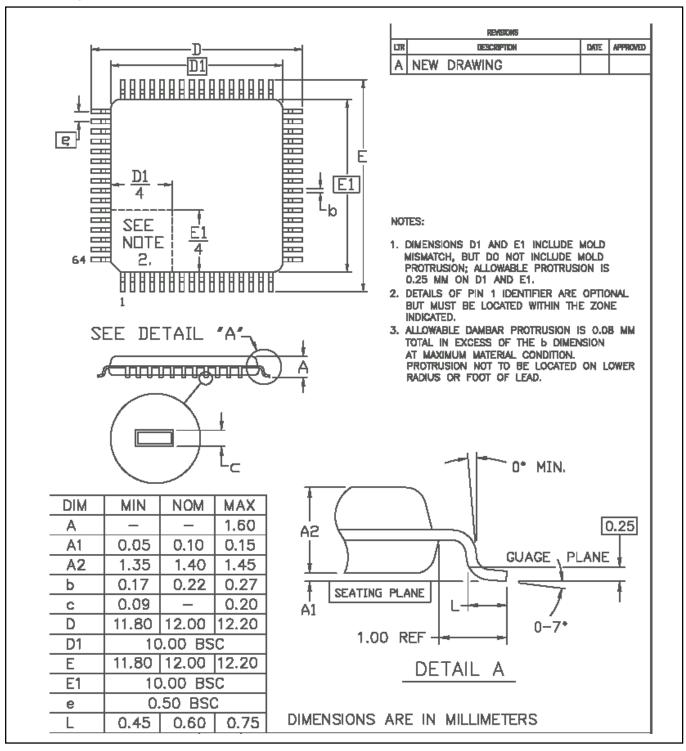

- 64-pin, 10mm x 10mm LQFP package

- 3.3V supply with 5V-tolerant inputs and outputs

- Evaluation kits

- IEEE 1149.1 JTAG Boundary Scan

- Driver source code available from the factory

#### 1.2 Line Interface

- Requires a single master clock (MCLK) for E1, T1, or J1 operation. Master clock can be 2.048MHz, 4.096MHz, 8.192MHz, or 16.384MHz. Option to use 1.544MHz, 3.088MHz, 6.176MHz, or 12.352MHz for T1-only operation.

- Fully software configurable

- Short- and long-haul applications

- Automatic receive sensitivity adjustments

- Ranges include 0dB to -43dB or 0dB to -12dB for E1 applications; 0dB to -36dB or 0dB to -15dB for T1 applications

- Receive level indication in 2.5dB steps from -42.5dB to -2.5dB

- Internal receive termination option for  $75\Omega$ ,  $100\Omega$ ,  $110\Omega$ , and  $120\Omega$  lines

- Monitor application gain settings of 20dB, 26dB, and 32dB

- G.703 receive-synchronization signal mode

- Flexible transmit-waveform generation www.DataSheet4U.co

- T1 DSX-1 line build-outs

- E1 waveforms include G.703 waveshapes for both  $75\Omega$  coax and  $120\Omega$  twisted cables

- AIS generation independent of loopbacks

- Alternating ones and zeros generation

- Square-wave output

- Open-drain output option

- Transmitter power-down

- Transmitter 50mA short-circuit limiter with exceeded indication of current limit

- Transmit open-circuit-detected indication

### 1.3 Jitter Attenuator (T1/E1 Modes Only)

- 32-bit or 128-bit crystal-less jitter attenuator

- Requires only a 2.048MHz master clock for both E1 and T1 operation with the option to use 1.544MHz for T1 operation

- Can be placed in either the receive or transmit path or disabled

- Limit trip indication

### 1.4 Framer/Formatter

- Full receive and transmit path transparency

- T1 framing formats include D4 and ESF

- E1 framing formats include FAS and CRC4

- Detailed alarm and status reporting with optional interrupt support

- RLOF, RLOS, and RAIS alarms interrupt on change of state

- Japanese J1 support includes:

- Ability to calculate and check CRC6 according to the Japanese standard

- Ability to generate yellow alarm according to the Japanese standard

### 1.5 Test and Diagnostics

Remote and Local Loopback

### 1.6 Control Port

- 8-bit parallel or serial control port

- Multiplexed or nonmultiplexed buses

- Intel or Motorola formats

- Supports polled or interrupt-driven environments

- Software access to device ID and silicon revision

- Software-reset supported with automatic clear on power-up

- Hardware controller port

- Hardware reset pin

www.DataSheet4U.con

#### 2. SPECIFICATIONS COMPLIANCE

The DS26502 meets all applicable sections of the latest telecommunications specifications including those listed in the following tables.

### **Table 2-1. T1-Related Telecommunications Specifications**

| ANSI T1.102: Digital Hierarchy Electrical Interface |

|-----------------------------------------------------|

|-----------------------------------------------------|

ANSI T1.231: Digital Hierarchy–Layer 1 in Service Performance Monitoring

ANSI T1.403: Network and Customer Installation Interface–DS1 Electrical Interface

TR62411

(ANSI) "Digital Hierarchy–Electrical Interfaces"

(ANSI) "Digital Hierarchy-Formats Specification"

(ANSI) "Digital Hierarchy-Layer 1 In-Service Digital Transmission Performance Monitoring"

(ANSI) "Network and Customer Installation Interfaces – DS1 Electrical Interface"

(AT&T) "Requirements for Interfacing Digital Terminal Equipment to Services Employing the Extended Super frame Format"

(AT&T) "High Capacity Digital Service Channel Interface Specification"

(TTC) "Frame Structures on Primary and Secondary Hierarchical Digital Interfaces"

(TTC) "ISDN Primary Rate User-Network Interface Layer 1 Specification"

www.DataSheet4U.cor

### **Table 2-2. E1-Related Telecommunications Specifications**

ITUT G.703 Physical/Electrical Characteristics of G.703 Hierarchical Digital Interfaces

ITUT G.736 Characteristics of Synchronous Digital Multiplex Equipment operating at 2048kbps

ITUT G.742 Second-Order Digital Multiplex Equipment Operating at 8448kbps

**ITUT G.772**

**ITUT G.775**

ITUT G.823 The control of jitter and wander within digital networks, which are based on 2.048kbps hierarchy

ETSI 300 233

(ITU) "Synchronous Frame Structures used at 1544, 6312k, 2048, 8488, and 44,736kbps Hierarchical Levels"

(ITU) "Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame Structures Defined in Recommendation G.704"

(ITU) "Characteristics of primary PCM Multiplex Equipment Operating at 2048kbps"

(ITU) Characteristics of a synchronous digital multiplex equipment operating at 2048kbps"

(ITU) "Loss Of Signal (LOS) and Alarm Indication Signal (AIS) Defect Detection and Clearance Criteria"

(ITU) "The Control of Jitter and Wander Within Digital Networks Which are Based on the 2048kbps Hierarchy"

(ITU) "Primary Rate User-Network Interface – Layer 1 Specification"

(ITU) "Error Performance Measuring Equipment Operating at the Primary Rate and Above"

(ITU) "In-service code violation monitors for digital systems"

(ETSI) "Integrated Services Digital Network (ISDN); Primary rate User-Network Interface (UNI); Part 1/ Layer 1 specification" www.DataSheet4U.com

(ETSI) "Transmission and multiplexing; Physical/electrical characteristics of hierarchical digital interfaces for equipment using the 2048kbps-based plesiochronous or synchronous digital hierarchies"

(ETSI) "Integrated Services Digital Network (ISDN); Access digital section for ISDN primary rate"

(ETSI) "Integrated Services Digital Network (ISDN); Attachment requirements for terminal equipment to connect to an ISDN using ISDN primary rate access"

(ETSI) "Business Telecommunications (BT); Open Network Provision (ONP) technical requirements; 2048lkbps digital unstructured leased lines (D2048U) attachment requirements for terminal equipment interface"

(ETSI) "Business Telecommunications (BTC); 2048kbps digital structured leased lines (D2048S); Attachment requirements for terminal equipment interface"

(ITU) "Synchronous Frame Structures used at 1544, 6312, 2048, 8488, and 44,736kbps Hierarchical Levels"

(ITU) "Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame Structures Defined in Recommendation G.704"

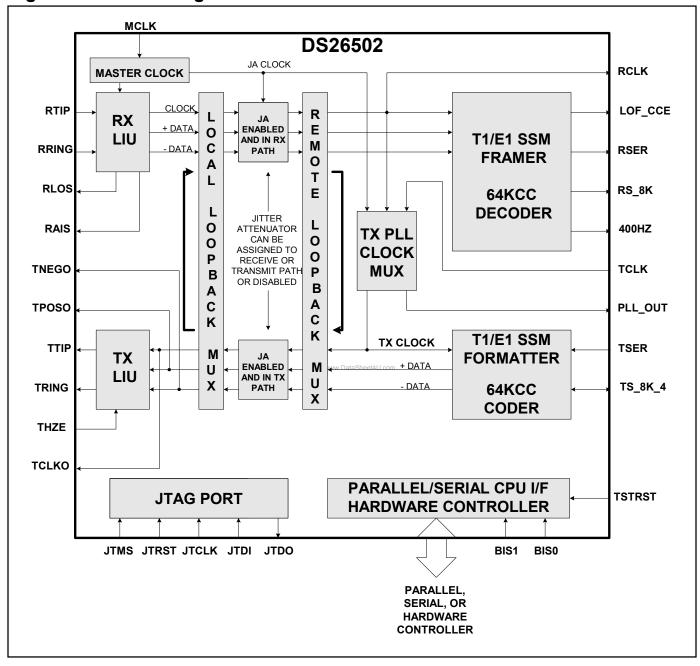

### 3. BLOCK DIAGRAMS

Figure 3-1. Block Diagram

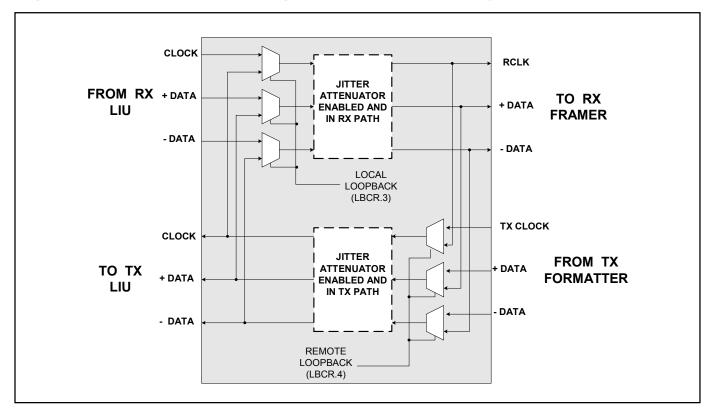

Figure 3-2. Loopback Mux Diagram (T1/E1 Modes Only)

www.DataSheet4U.com

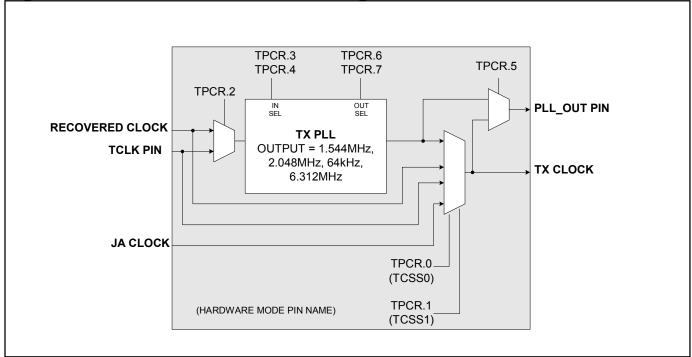

Figure 3-3. Transmit PLL Clock Mux Diagram

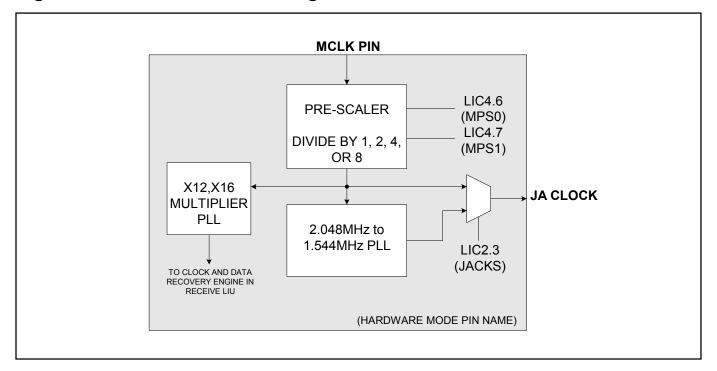

Figure 3-4. Master Clock PLL Diagram

www.DataSheet4U.com

### 4. PIN FUNCTION DESCRIPTION

### 4.1 Transmit PLL

| NAME    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                           |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL_OUT | О    | <b>Transmit PLL Output.</b> This pin can be selected to output the 1544kHz, 2048kHz, 64kHz, or 6312kHz output from the internal TX PLL or the internal signal, TX CLOCK. See <u>Figure 3-3</u> and <u>Figure 3-4</u> .                                                                             |

| TCLK    | I    | <b>Transmit Clock Input.</b> A 64kHz, 1.544MHz, 2.048MHz, or 6312kHz primary clock. May be selected by the TX PLL mux to either directly drive the transmit section or be converted to one of the other rates prior to driving the transmit section. See <u>Figure 3-3</u> and <u>Figure 3-4</u> . |

### 4.2 Transmit Side

| NAME    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                              |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSER    | I    | <b>Transmit Serial Data.</b> Source of transmit data sampled on the falling edge of TX CLOCK (an internal signal). See <u>Figure 3-1</u> , <u>Figure 3-3</u> , and the transmit timing diagram ( <u>Figure 20-11</u> ).                                                                               |

|         |      | TSYNC, 8kHz Sync, 400Hz Sync                                                                                                                                                                                                                                                                          |

|         |      | T1/E1 Mode: In input mode, this pin is sampled on the falling edge of TX CLOCK (an internal signal) and a pulse at this pin will establish either frame or multiframe boundaries for the transmit side. See Figure 3-1 and the transmit timing diagram (Figure 20-11).                                |

| TS_8K_4 | I/O  | In output mode, this pin is updated on the rising edge of TX CLOCK (an internal signal) and can be programmed to output a frame or multiframe sync pulse useful for aligning data. See <u>Figure 3-1</u> and the transmit timing diagram ( <u>Figure 20-11</u> ).                                     |

|         |      | 64KCC Mode: In input mode, this pin is sampled on the falling edge of TX CLOCK (an internal signal) and will establish the boundary for the 8kHz portion of the Composite Clock or the 400Hz boundary based on the setting of IOCR1.3. See Figure 3-1 and the transmit timing diagram (Figure 20-11). |

|         |      | In output mode, this pin is updated on the rising edge of TX CLOCK (an internal signal) and will indicate the 8kHz or 400Hz composite clock alignment. See <u>Figure 3-1</u> and the transmit timing diagram ( <u>Figure 20-11</u> ).                                                                 |

| TCLKO   | 0    | <b>Transmit Clock Output.</b> In normal operation this output is the selected transmit clock from the TX_PLL, TCLK pin or the recovered clock (RCLK). When remote loopback is enabled this pin will output the recovered network clock.                                                               |

| TPOSO   | 0    | <b>Transmit Positive-Data Output.</b> In T1 or E1 mode, updated on the rising edge of TCLKO with the bipolar data out of the transmit-side formatter. Can be programmed to source NRZ data via the output-data format (IOCR1.0) control bit. In 64KCC or 6312kHz mode this pin will be low.           |

| TNEGO   | О    | <b>Transmit Negative-Data Output.</b> In T1 or E1 mode, updated on the rising edge of TCLKO with the bipolar data out of the transmit-side formatter. In 64KCC or 6312kHz mode this pin will be low.                                                                                                  |

## 4.3 Receive Side

| NAME     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | О    | Receive Clock. Recovered 1.544MHz (T1), 2.048MHz (E1), 6312 kHz                                                                                                                                                                                                                                                                                                                                   |

| KCEK     | 0    | (G.703 Synchronization Interface), or 64 kHz (Composite Clock) clock.                                                                                                                                                                                                                                                                                                                             |

| RS_8K    | O    | Receive Sync/ 8kHZ Clock. T1/E1 Mode: An extracted pulse, one RCLK wide, is output at this pin that identifies either frame (IOCR1.5 = 0) or multiframe (IOCR1.5 = 1) boundaries. If set to output frame boundaries, then through IOCR1.6, RS_8K can also be set to output double-wide pulses on signaling frames in T1 mode. 64KCC Mode: This pin will output the extracted 8 kHz portion of the |

|          |      | composite clock signal.                                                                                                                                                                                                                                                                                                                                                                           |

|          |      | 6312kHz Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                         |

|          |      | 400HZ Clock Output                                                                                                                                                                                                                                                                                                                                                                                |

| 400117   | 0    | T1/E1 Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                           |

| 400HZ    | О    | 64KCC Mode: This pin will output the 400Hz clock if enabled.                                                                                                                                                                                                                                                                                                                                      |

|          |      | 6312kHz Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                         |

|          |      | Receive Serial Data                                                                                                                                                                                                                                                                                                                                                                               |

| RSER     | O    | T1/E1 Mode: This is the received NRZ serial data updated on rising edges of RCLK.                                                                                                                                                                                                                                                                                                                 |

|          |      | 64KCC Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                           |

|          |      | 6312kHz Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                         |

|          |      | Receive Loss Of Frame or Composite Clock Error. This output can be configured to be a Loss Of Transmit Clock indicator via IOCR.4 when operating in T1 or E1 mode.                                                                                                                                                                                                                                |

| RLOF_CCE | О    | T1/E1 Mode: Set when the receive synchronizer is searching for frame alignment (RLOF mode), or set when the signal at the TCLK pin has not transitioned for approximately 15 periods of the scaled MCLK (LOTC mode).                                                                                                                                                                              |

|          |      | 64KCC Mode: Active high when errors are detected in the 8kHz clock or 400Hz clock                                                                                                                                                                                                                                                                                                                 |

|          |      | 6312kHz Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                         |

|          |      | Receive Loss Of Signal                                                                                                                                                                                                                                                                                                                                                                            |

|          |      | T1 Mode: High when 192 consecutive zeros detected.                                                                                                                                                                                                                                                                                                                                                |

| RLOS     | O    | E1 Mode: High when 255 consecutive zeros detected.                                                                                                                                                                                                                                                                                                                                                |

|          |      | 64KCC Mode: High when consecutive zeros detected for 130μs typically.                                                                                                                                                                                                                                                                                                                             |

|          |      | 6312kHz Mode: High when consecutive zeros detected for 65µs typically.                                                                                                                                                                                                                                                                                                                            |

|          |      | Receive Alarm Indication Signal                                                                                                                                                                                                                                                                                                                                                                   |

|          |      | T1 Mode: Will toggle high when receive Blue Alarm is detected.                                                                                                                                                                                                                                                                                                                                    |

| RAIS     | О    | E1 Mode: Will toggle high when receive AIS is detected.                                                                                                                                                                                                                                                                                                                                           |

|          |      | 64KCC Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                           |

|          |      | 6312kHz Mode: This pin will be in a high-impedance state.                                                                                                                                                                                                                                                                                                                                         |

## 4.4 Controller Interface

| NAME                    | TYPE | FUNCTION                                                                                                       |

|-------------------------|------|----------------------------------------------------------------------------------------------------------------|

|                         |      | Interrupt/JA Clock Source Select 1 INT: Flags host controller during events, alarms, and conditions defined in |

| $\overline{\text{INT}}$ | I/O  | the status registers. Active-low open-drain output.                                                            |

| JACKS                   | 1, 0 | JACKS: Hardware Mode: JA Clock Select. Set this pin high for T1 mode                                           |

|                         |      | operation when either a 2.048MHz, 4.096MHz, 8.192MHz or 16.382MHz                                              |

|                         |      | signal is applied at MCLK.                                                                                     |

| TMODE1                  | т    | <b>Transmit Mode Select 1.</b> In Hardware Mode (BIS[1:0] = 11), this bit is used                              |

| TMODE1                  | I    | to configure the transmit operating mode.                                                                      |

| TMODE2                  | т    | <b>Transmit Mode Select 2.</b> In Hardware Mode (BIS[1:0] = 11), this bit is used                              |

| TMODE2                  | I    | to configure the transmit operating mode.                                                                      |

|                         |      | Tri-State Control and Device Reset. A dual-function pin. A zero-to-one                                         |

|                         |      | transition issues a hardware reset to the DS26502 register set. Configuration                                  |

| TSTRST                  | I    | register contents are set to the default state. Leaving TSTRST high tri-states                                 |

|                         |      | all output and I/O pins (including the parallel control port). Set low for                                     |

|                         |      | normal operation. Useful for in-board level testing.                                                           |

|                         |      | Bus Interface Mode Select 1, 0. These bits select the controller interface                                     |

|                         |      | mode of operation.                                                                                             |

|                         |      |                                                                                                                |

| BIS[1:0]                | I    | BIS[1:0]: 00 = Parallel Port Mode (Multiplexed)                                                                |

|                         |      | 01 = Parallel Port Mode (Nonmultiplexed)                                                                       |

|                         |      | 10 = Serial Port Mode                                                                                          |

|                         |      | 11 = Hardware Mode                                                                                             |

|                         |      | Data Bus D[7] or Address/Data Bus AD[7]/Transmit Termination Select                                            |

|                         |      | A[7]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data                                   |

| AD[7]/                  | 1/0  | bus D[7].                                                                                                      |

| RITD                    | I/O  | AD[7]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the                                          |

|                         |      | multiplexed address/data bus AD[7].                                                                            |

|                         |      | RITD: In Hardware Mode (BIS[1:0] = 11), it disables the internal receive termination.                          |

|                         |      | Data Bus D[6] or Address/Data Bus AD[6]/Transmit Termination Select                                            |

|                         |      | A[6]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data                                   |

|                         |      | bus D[6].                                                                                                      |

| AD[6]/                  | I/O  | AD[6]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the                                          |

| TITD                    | 1, 0 | multiplexed address/data bus AD[6].                                                                            |

|                         |      | TITD: In Hardware Mode (BIS[1:0] = 11), it disables the internal transmit                                      |

|                         |      | termination.                                                                                                   |

|                         |      | Data Bus D[5] or Address/Data Bus AD[5]/Receive Framing Mode Select                                            |

|                         |      | Bit 1                                                                                                          |

|                         |      | A[5]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data                                   |

| AD[5]/                  | I/O  | bus D[5].                                                                                                      |

| RMODE1                  | 1/0  | AD[5]: In multiplexed bus operation (BIS[1:0] = $00$ ), it serves as the                                       |

|                         |      | multiplexed address/data bus AD[5].                                                                            |

|                         |      | RMODE1: In Hardware Mode (BIS[1:0] = 11), it selects the receive side                                          |

|                         |      | operating mode.                                                                                                |

| NAME                      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[4]/<br>RMODE0          | I/O  | Data Bus D[4] or Address/Data Bus AD[4]/Receive Framing Mode Select Bit 0  A[4]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data bus D[4].  AD[4]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the multiplexed address/data bus AD[4].  RMODE0: In Hardware Mode (BIS[1:0] = 11), it selects the receive side operating mode.                                                                                                                   |

| AD[3]/TSM                 | I/O  | Data Bus D[3] or Address/Data Bus AD[3]/TS_8K_4 Mode Select A[3]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data bus D[3]. AD[3]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the multiplexed address/data bus AD[3]. TSM: In Hardware Mode (BIS[1:0] = 11), this pin selects the function of TS_8K_4. Please see the register descriptions for more detailed information.                                                                     |

| AD[2]/RSM/<br>SCLK        | I/O  | Data Bus D[2] or Address/Data Bus AD[2]/RS_8K Mode Select/ Serial Clock A[2]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data bus D[2]. AD[2]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the multiplexed address/data bus AD[2]. RSM: In Hardware Mode (BIS[1:0] = 11), this pin selects the function of RS_8K. Please see the register descriptions for more detailed information. SCLK: In Serial Port mode this is the serial clock input. |

| AD[1]/<br>RMODE3/<br>MOSI | I/O  | Data Bus D[1] or Address/Data Bus AD[1]/Receive Mode Select 3/Master Out-Slave In  A[1]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data bus D[1].  AD[1]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the multiplexed address/data bus AD[1].  RMODE3: In Hardware Mode (BIS[1:0] = 11), this pin selects the receive side operating mode.  MOSI: Serial data input called Master Out-Slave In for clarity of data transfer direction.         |

| AD[0]/<br>TCSS0/<br>MISO  | I/O  | Data Bus D[0] or Address/Data Bus AD[0]/Transmit Clock Source Select 0/Master In-Slave Out A[0]: In nonmultiplexed bus operation (BIS[1:0] = 01), it serves as the data bus D[0]. AD[0]: In multiplexed bus operation (BIS[1:0] = 00), it serves as the multiplexed address/data bus AD[0]. TCSS0: Transmit Clock Source Select 0. MISO: In serial bus mode (BIS[1:0] = 10), this pin serves as the serial data output Master In-Slave Out.                                           |

| TCSS1                     | I    | Transmit Clock Source Select. Transmit Clock Source Select 1                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NAME               | ТҮРЕ | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6/MPS0            | I    | Address Bus Bit A[6]/MCLK Prescale Select A6: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[6]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low. MPS0: In Hardware Mode (BIS[1:0] = 11), MCLK prescale select is used to set the prescale value for the PLL.                                                                                                                                                                                                                           |

| A5/CPOL/<br>TMODE0 | I    | Address Bus Bit A[5]/Serial Port Clock Polarity Select/Transmit Mode Select 0  A5: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[5]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low.  CPOL: In Serial Port Mode (BIS[1:0] = 10), this pin selects the serial port clock polarity. Please see the functional timing diagrams for the Serial Port Interface for more information.  TMODE0: In Hardware Mode (BIS[1:0] = 11), this pin is used to configure the transmit operating mode. |

| A4/CPHA/<br>L2     | I    | Address Bus Bit A[4]/Serial Port Clock Phase Select/Line Build-Out Select 2  A4: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[4]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low.  CPHA: In Serial Port Mode (BIS[1:0] = 10), this pin selects the serial port clock phase. See the functional timing diagrams for the Serial Port Interface for more information.  L2: In Hardware Mode (BIS[1:0] = 11), this pin selects the line build-out value.                                 |

| A3/L1              | I    | Address Bus Bit A[3]/Line Build-Out Select 1 A3: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[3]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low. L1: In Hardware Mode (BIS[1:0] = 11), this pin selects the line build-out value.                                                                                                                                                                                                                                                   |

| A2/L0              | I    | Address Bus Bit A[2]/Line Build-Out Select 0 A2: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[2]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low. L0: In Hardware Mode (BIS[1:0] = 11), this pin selects the line build-out value.                                                                                                                                                                                                                                                   |

| A1/TAIS            | I    | Address Bus Bit A[1]/Transmit AIS  A1: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[1]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low.  TAIS: When set to a 1 and in T1/E1 operating modes, the transmitter will transmit an AIS pattern. This pin is ignored in all other operating modes.                                                                                                                                                                                         |

| NAME                 | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0/E1TS I            |      | Address Bus Bit A[0]/E1 Termination Select A0: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[0]. In multiplexed bus operation (BIS[1:0] = 00), these pins are not used and should be tied low. E1TS: In Hardware Mode (BIS[1:0] = 11), selects the E1 internal termination value (0 = $120\Omega$ , 1 = $75\Omega$ ).                                                                                                                                  |

| BTS/HBE              | I    | Bus Type Select/Transmit and Receive B8ZS/HDB3 Enable BTS: Strap high to select Motorola bus timing; strap low to select Intel bus timing. This pin controls the function of the $\overline{RD}$ ( $\overline{DS}$ ), ALE (AS), and $\overline{WR}$ ( $R/\overline{W}$ ) pins. If BTS = 1, then these pins assume the function listed in parentheses (). HBE: In Hardware Mode (BIS[1:0] = 11), this pin enables transmit and receive B8ZS/HDB3 when in T1/E1 operating modes. |

| RD(DS)/<br>RMODE2    | Ι    | Read Input-Data Strobe/Receive Mode Select Bit 2  RD (DS): These pins are active-low signals. DS is active high when BIS[1:0] = 01. See the bus timing diagrams.  RMODE2: In Hardware Mode (BIS[1:0] = 11), this pin selects the receive side operating mode.                                                                                                                                                                                                                  |

| CS/RLB               | Ι    | Chip Select/Remote Loopback Enable  CS: This active-low signal must be low to read or write to the device. This signal is used for both the parallel port and the serial port modes.  RLB: In Hardware Mode (BIS[1:0] = 11), when high, remote loopback is enabled. This function is only valid when the transmit side and receive side are in the same operating mode.                                                                                                        |

| ALE (AS)/<br>A7/MPS1 | Ι    | Address Latch Enable (Address Strobe)/Address Bus Bit 7/MCLK  Prescale Select 1  ALE (AS): In multiplexed bus operation (BIS[1:0] = 00), it serves to demultiplex the bus on a positive-going edge.  A7: In nonmultiplexed bus operation (BIS[1:0] = 01), this pin serves as A[7]. MPS1: In Hardware Mode (BIS[1:0] = 11), MCLK prescale select, used to set the prescale value for the PLL.                                                                                   |

| WR (R/W)/<br>TMODE3  | I    | Write Input (Read/Write)/Transmit Mode Select 3 WR: In Processor Mode, this pin is the active-low write signal. TMODE3: In Hardware Mode, this pin selects the transmit-side operating mode.                                                                                                                                                                                                                                                                                   |

## **4.5 JTAG**

| NAME   | TYPE | FUNCTION                                                                                              |

|--------|------|-------------------------------------------------------------------------------------------------------|

| JTCLK  | Ţ    | JTAG Clock. This clock input is typically a low frequency (less than 10MHz)                           |

| UTCER  | •    | 50% duty cycle clock signal.                                                                          |

| JTMS   | Ţ    | JTAG Mode Select (with Pullup). This input signal is used to control the                              |

| 311115 | 1    | JTAG controller state machine and is sampled on the rising edge of JTCLK.                             |

|        |      | JTAG Data Input (with Pullup). This input signal is used to input data into                           |

| JTDI   | I    | the register that is enabled by the JTAG controller state machine and is sampled                      |

|        |      | on the rising edge of JTCLK.                                                                          |

|        | 0    | JTAG Data Output. This output signal is the output of an internal scan shift                          |

|        |      | register enabled by the JTAG controller state machine and is updated on the                           |

| JTDO   |      | falling edge of JTCLK. The pin is in the high-impedance mode when a register                          |

|        |      | is not selected or when the $\overline{\text{JTRST}}$ signal is high. The pin goes into and exits the |

|        |      | high impedance mode after the falling edge of JTCLK                                                   |

|        |      | JTAG Reset (Active Low). This input forces the JTAG controller logic into                             |

|        |      | the reset state and forces the JTDO pin into high impedance when low. This pin                        |

| JTRST  | I    | should be low while power is applied and set high after the power is stable.                          |

|        |      | The pin can be driven high or low for normal operation, but must be high for                          |

|        |      | JTAG operation.                                                                                       |

## 4.6 Line Interface

| NAME  | TYPE | www.DataSheet4U.c <b>FUNCTION</b>                                                                                                                                                                                                                                                                                                 |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK  | I    | <b>Master Clock Input.</b> A (50ppm) clock source. This clock is used internally for both clock/data recovery and for the jitter attenuator for both T1 and E1 modes. The clock rate can be 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz. When using the DS26502 in T1-only operation, a 1.544MHz (50ppm) clock source can be used. |

| RTIP  | I    | <b>Receive Tip.</b> Analog input for clock recovery circuitry. This pin connects via a 1:1 transformer to the network. See the <i>Line Interface Unit</i> section for details.                                                                                                                                                    |

| RRING | I    | <b>Receive Ring.</b> Analog input for clock recovery circuitry. This pin connects via a 1:1 transformer to the network. See the <i>Line Interface Unit</i> section for details.                                                                                                                                                   |

| TTIP  | О    | <b>Transmit Tip.</b> Analog line-driver output. This pin connects via a 1:2 step-up transformer to the network. See the <i>Line Interface Unit</i> section for details.                                                                                                                                                           |

| TRING | О    | <b>Transmit Ring.</b> Analog line-driver output. This pin connects via a 1:2 step-up transformer to the network. See the <i>Line Interface Unit</i> section for details.                                                                                                                                                          |

| THZE  | I    | <b>Transmit High-Impedance Enable.</b> When high, TTIP and TRING will be placed into a high-impedance state.                                                                                                                                                                                                                      |

### 4.7 Power

| NAME    | TYPE | FUNCTION                                                                               |

|---------|------|----------------------------------------------------------------------------------------|

| DVDD    |      | <b>Digital Positive Supply.</b> $3.3V \pm 5\%$ . Should be tied to the RVDD and TVDD   |

| DVDD    |      | pins.                                                                                  |

| RVDD    |      | <b>Receive Analog Positive Supply.</b> $3.3V \pm 5\%$ . Should be tied to the DVDD and |

| KVDD    |      | TVDD pins.                                                                             |

| TVDD    |      | <b>Transmit Analog Positive Supply.</b> 3.3V ±5%. Should be tied to the DVDD           |

| TVDD    |      | and RVDD pins.                                                                         |

| DVSS    |      | <b>Digital Signal Ground.</b> 0.0V. Should be tied to the RVSS and TVSS pins.          |

| D 100   |      | Digital Signal Givana. 0.0 v. Should be ded to the RVSS and I viss phis.               |

| RVSS    |      | <b>Receive Analog Signal Ground.</b> 0.0V. Should be tied to the DVSS and TVSS         |

| IX V SS | _    | pins.                                                                                  |

| TVSS    |      | Transmit Analog Signal Ground. 0.0V. Should be tied to the DVSS and                    |

|         |      | RVSS pins.                                                                             |

www.DataSheet4U.com

### 5. PINOUT

**Table 5-1. LQFP Pinout**

|              |      |                  | MODE           |          |                                                                                                                                                                      |  |  |

|--------------|------|------------------|----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN          | TYPE | PARALLEL<br>PORT | SERIAL<br>PORT | HARDWARE | FUNCTION                                                                                                                                                             |  |  |

| 1            | I/O  | AD2              | SCLK           | RSM      | Parallel Port Mode: Address/Data Bus Bit 2<br>Serial Port Mode: Serial Clock<br>Hardware Mode: RS_8K Mode Select                                                     |  |  |

| 2            | I/O  | AD3              | _              | TSM      | Parallel Port Mode: Address/Data Bus Bit 3 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: TS 8K 4 Mode Select                     |  |  |

| 3            | I/O  | AD4              | _              | RMODE0   | Parallel Port Mode: Address/Data Bus Bit 4 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: Receive Mode Select 0                   |  |  |

| 4            | I/O  | AD5              | _              | RMODE1   | Parallel Port Mode: Address/Data Bus Bit 5 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: Receive Mode Select 1                   |  |  |

| 5            | I/O  | AD6              | _              | TITD     | Parallel Port Mode: Address/Data Bus Bit 6 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: Transmit Internal Termination Disable   |  |  |

| 6            | I/O  | AD7              | _              | RITD     | Parallel Port Mode: Address/Data Bus Bit 7 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: Receive Internal Termination Disable    |  |  |

| 7, 24,<br>58 | I    | DVDD             | DVDD           | DVDD     | Digital Positive Supply                                                                                                                                              |  |  |

| 8, 22,<br>56 | I    | DVSS             | DVSS           | DVSS     | Digital Signal Ground                                                                                                                                                |  |  |

| 9            | I    | A0               | _              | E1TS     | Parallel Port Mode: Address Bus Bit 0 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: E1 Internal Termination Select               |  |  |

| 10           | I    | A1               | _              | TAIS     | Parallel Port Mode: Address Bus Bit 1 Serial Port Mode: Unused, should be connected to V <sub>SS</sub> . Hardware Mode: Transmit AIS                                 |  |  |

| 11           | I    | A2               | _              | L0       | Parallel Port Mode: Address Bus Bit 2<br>Serial Port Mode: Unused, should be connected to V <sub>SS</sub> .<br>Hardware Mode: Line Build-Out Select 0                |  |  |