# DS1610 Partitioned NV Controller

www.dalsemi.com

#### **FEATURES**

- Converts CMOS RAMs into nonvolatile memories

- SOIC version is pin-compatible with the Dallas Semiconductor DS1210 NV Controller

- Unconditionally write protects all of memory when V<sub>CC</sub> is out of tolerance

- Write protects selected blocks of memory regardless of V<sub>CC</sub> status when programmed

- Automatically switches to battery backup supply when power-fail occurs

- Provides for multiple batteries

- Consumes less than 100 nA of battery current

- Test battery on power-up by inhibiting the second memory cycle

- Optional 5% or 10% power-fail detection

- 16-pin DIP or 16-pin SOIC surface-mount package

- Low forward voltage drop on the V<sub>CC</sub> switch with currents of up to 150 mA

- Optional industrial temperature range of -40°C to +85°C

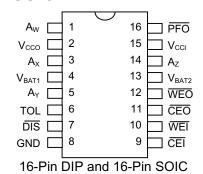

#### PIN ASSIGNMENT

#### PIN DESCRIPTION

| $V_{CCI}$           | - Input +5 Volt Supply |

|---------------------|------------------------|

| $V_{BAT1}$          | - + Battery 1 Input    |

| $V_{\mathrm{BAT2}}$ | - + Battery 2 Input    |

$V_{CCO}$  - RAM Power ( $V_{CC}$ ) Supply

GND - Ground

- Chip Enable Input

- Chip Enable Output

- Chip Enable Output

- Write Enable Input

- Write Enable Output

TOL - Power Supply Tolerance Select

$A_W$  -  $A_Z$  - Address Inputs

DIS - Memory Partition Disable

PFO - Power-Fail Output

### **DESCRIPTION**

The DS1610 is a low-power CMOS circuit which solves the application problems of converting CMOS RAMS into nonvolatile memories. In addition the device has the ability to unconditionally write protect blocks of memory so that inadvertent write cycles do not corrupt program and special data space. The power supply incoming voltage at the  $V_{\rm CCI}$  input pin is constantly monitored for an out-of-tolerance condition. When such a condition is detected, both the chip enable and write enable outputs are inhibited to protect stored data. The battery inputs are used to supply  $V_{\rm CCO}$  with power when  $V_{\rm CCI}$  is less than the battery input voltages. Special circuitry uses a low leakage CMOS process which affords precise voltage detection at extremely low current consumption. By combining the DS1610 Partitioned NV Controller chip with a CMOS memory and batteries, nonvolatile RAM operation can be achieved.

The DS1610 Partitioned NV Controller functions like the Dallas Semiconductor DS1210 NV controller when the  $(\overline{DIS})$  disable pin is grounded. An internal pulldown resistor to ground on the  $\overline{DIS}$  pin of the DS1610S allows it to retrofit into DS1210S applications. When the  $\overline{DIS}$  pin is grounded the address inputs  $A_W$  -  $A_Z$  and the write enable input  $\overline{WEI}$  are ignored. Also the power-fail output  $\overline{PFO}$  and the write enable output  $\overline{WEO}$  are tristated.

1 of 10 111999

## **OPERATION - DISABLE PIN CONNECTED TO V<sub>CCO</sub>**

The DS1610 performs five circuit functions required to battery backup a RAM. First, a switch is provided to direct power from the battery or the incoming power supply (V<sub>CCI</sub>) depending on which is greater. This switch has a voltage drop of less than 0.2 volts. The second function provided by the DS1610 is powerfail detection. The incoming supply (V<sub>CCI</sub>) is constantly monitored. When the supply goes out of tolerance a precision comparator detects power failure and inhibits both the chip enable output (CEO) and the write enable output ( WEO ). A third function of write protection is accomplished by holding both the chip enable output  $\overline{\text{CEO}}$  and write enable output  $\overline{\text{WEO}}$  to within 0.2 volts of  $V_{CCO}$  when  $V_{CCI}$  is out of tolerance. If  $\overline{\text{CEI}}$  is low at the time that power-fail detection occurs the  $\overline{\text{CEO}}$  signal is kept low until  $\overline{\text{CEI}}$ is brought high again. However,  $\overline{CEO}$  is forced high after 1.5  $\mu$ s regardless of the state of  $\overline{CEI}$ . Similarly, if  $\overline{\text{WEI}}$  is low at the time that power fail detection occurs, the  $\overline{\text{WEO}}$  signal will remain low until  $\overline{\text{WEI}}$  is brought high or 1.5 µs elapses. The delay of write protection until the current memory cycle is complete prevents corrupted data. Power-fail detection occurs in the range of 4.75 to 4.5 volts with the tolerance pin TOL grounded. If the tolerance pin is connected to V<sub>CCO</sub> then power-fail detection occurs in the range of 4.5 volts to 4.25 volts. The  $\overline{PF0}$  signal is driven low and remains low until  $V_{CCI}$  returns to nominal conditions. During nominal supply conditions  $\overline{\text{CEO}}$  will follow  $\overline{\text{CEI}}$  and  $\overline{\text{WEO}}$  will follow  $\overline{\text{WEI}}$ . The fourth function which the DS1610 performs is a battery status warning so that potential data loss is avoided. Each time V<sub>CCI</sub> is applied to the device battery status is checked with a precision comparator. If during battery backup no switch occurred from one battery to the other, the voltage of the battery supplying power when V<sub>CCI</sub> is applied is checked. If this voltage is less than 2.0 volts the second chip enable cycle after power is applied is inhibited. If any switch from one battery to another did occur the voltage of both batteries is checked. If either voltage is less than 2.0 volts the second chip enable cycle will be inhibited. Battery status can therefore be determined by performing a read cycle after power up to any location in memory, verifying that memory location's contents. A subsequent write cycle can then be executed to the same memory location altering the data. If the next read cycle fails to verify the written data then the data is in danger of being corrupted. The fifth function of the DS1610 provides for battery redundancy. When data integrity is extremely important it is wise to use two batteries to insure reliability. The DS1610 controller provides an internal isolation switch which allows the connection of two batteries. When entering battery backup operation, the battery with the highest voltage is selected for use. If one battery should fail, the other would then supply energy to the connected load. The switch to a redundant battery is transparent to circuit operation and to the user. In applications where battery redundancy is not a major concern a single battery should be connected to the BAT1 pin. The BAT2 battery pin must be grounded. When batteries are first connected to one or both of the V<sub>BAT</sub> pins V<sub>CCO</sub> will not show the battery potential until V<sub>CCI</sub> is applied and removed for the first time.

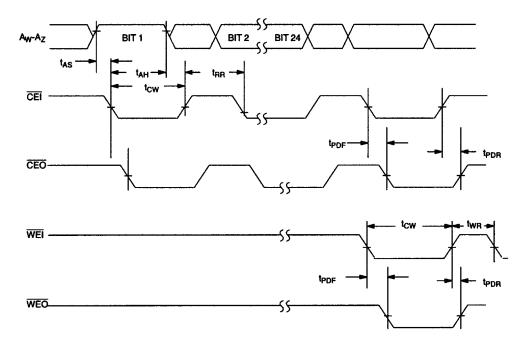

#### OPERATION - WRITE PROTECTION PROGRAMMING MODE

When the disable pin is connected to  $V_{\rm CCI}$  or  $V_{\rm CCO}$ , the DS1610 performs all of the functions described earlier with the addition of a partition switch which selectively write protects blocks of memory. The state of the  $\overline{\rm DIS}$  pin is strobed and latched as  $V_{\rm CCI}$  crosses the power-fail trip point so that the DS1610 maintains its configuration during power loss. If the strobed value of  $\overline{\rm DIS}$  is a high the internal pulldown resistor on the  $\overline{\rm DIS}$  pin will be disconnected in the power-fail state to eliminate the possibility of battery discharge. The register controlling the partition switch is selected by recognition of a specific binary pattern which is sent on address lines  $A_W$  - $A_Z$ . These address lines are normally the four upper order address lines being sent to RAM. The pattern is sent by 20 consecutive read cycles with the exact pattern as shown in Table 1. Pattern matching must be accomplished using read cycles; any write cycles will reset the pattern matching circuitry. If this pattern is matched perfectly, then the 21<sup>st</sup> through 24<sup>th</sup> read cycle will load the partition switch. Since there are 16 possible write protected partitions, the size of each partition is determined by the size of the memory. For example, a 128k X 8 memory would be divided into 16 partitions of 128k/16 or 8k X 8. Each partition is represented by one of the 16 bits contained in the

$21^{st}$  through  $24^{th}$  read cycle as defined by  $A_W$  through  $A_Z$  and shown in Table 2. A logical 1 in a bit location sets that partition to write protect. A logical 0 in a bit location disables write protection. For example, if during the pattern match sequence bit 22 on address pin  $A_X$  were a 1, this would cause the partition register location for partition 5 to be set to a 1. This in turn would cause the DS1610 to inhibit  $\overline{\text{WEO}}$  from going low as  $\overline{\text{WEI}}$  goes low whenever  $A_ZA_YA_XA_W=0101$ . Note that while setting the partition register, data which is being accessed from the RAM should be ignored as the purpose of the 24 read cycles is to set the partition switch and not for the purpose of accessing data from RAM. Also note that on initial battery attach the partition register can power-up in any state.

### PATTERN MATCH TO WRITE PARTITION REGISTER Table 1

|         | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

|---------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| $A_{W}$ | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | X  | X  | X  | X  |

| $A_X$   | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | X  | X  | X  | X  |

| $A_{Y}$ | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | X  | X  | X  | X  |

| $A_7$   | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | X  | X  | X  | X  |

#### **PARTITION REGISTER MAPPING** Table 2

| Address          | Address Bit number in pattern Partition |              | Address State Affected                                                                           |

|------------------|-----------------------------------------|--------------|--------------------------------------------------------------------------------------------------|

| Pin              | Match sequence                          |              | $(\mathbf{A}_{\mathbf{Z}}\mathbf{A}_{\mathbf{Y}}\mathbf{A}_{\mathbf{X}}\mathbf{A}_{\mathbf{W}})$ |

| $A_{\mathrm{W}}$ | BIT 21                                  | PARTITION 0  | 0000                                                                                             |

| $A_{X}$          | BIT 21                                  | PARTITION 1  | 0001                                                                                             |

| $A_{Y}$          | BIT 21                                  | PARTITION 2  | 0010                                                                                             |

| $A_{Z}$          | BIT 21                                  | PARTITION 3  | 0011                                                                                             |

| $A_{\mathrm{W}}$ | BIT 22                                  | PARTITION 4  | 0100                                                                                             |

| A <sub>X</sub>   | BIT 22                                  | PARTITION 5  | 0101                                                                                             |

| $A_{Y}$          | BIT 22                                  | PARTITION 6  | 0110                                                                                             |

| $A_{Z}$          | BIT 22                                  | PARTITION 7  | 0111                                                                                             |

| $A_{\mathrm{W}}$ | BIT 23                                  | PARTITION 8  | 1000                                                                                             |

| $A_{X}$          | BIT 23                                  | PARTITION 9  | 1001                                                                                             |

| $A_{Y}$          | BIT 23                                  | PARTITION 10 | 1010                                                                                             |

| $A_Z$            | BIT 23                                  | PARTITION 11 | 1011                                                                                             |

| $A_{\mathrm{W}}$ | BIT 24                                  | PARTITION 12 | 1100                                                                                             |

| $A_{X}$          | BIT 24                                  | PARTITION 13 | 1101                                                                                             |

| Ay               | BIT 24                                  | PARTITION 14 | 1110                                                                                             |

| $A_{Z}$          | BIT 24                                  | PARTITION 15 | 1111                                                                                             |

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground

Operating Temperature

O°C to 70°C

Storage Temperature

-55°C to +125°C

Soldering Temperature

260°C for 10 seconds

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### RECOMMENDED DC OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER                        | SYMBOL        | MIN  | TYP | MAX            | UNITS | NOTES |

|----------------------------------|---------------|------|-----|----------------|-------|-------|

| Pin 6 = GND Supply Voltage       | $V_{CCI}$     | 4.75 | 5.0 | 5.5            | V     | 1     |

| Pin $6 = V_{CCO}$ Supply Voltage | $V_{CCI}$     | 4.5  | 5.0 | 5.5            | V     | 1     |

| Logic 1 Input                    | $V_{IH}$      | 2.0  |     | $V_{CC} + 0.3$ | V     | 1     |

| Logic 0 Input                    | $V_{IL}$      | -0.3 |     | +0.8           | V     | 1     |

| Battery Input                    | $V_{BAT1}$ ,  | 2.0  |     | 4.0            | V     | 1, 2  |

|                                  | $ m V_{BAT2}$ |      |     |                |       |       |

# DC ELECTRICAL CHARACTERISTICS (0°C to 70°C, V<sub>CCI</sub> WITHIN DC OPERATING CONDITIONS)

| PARAMETER                                         | SYMBOL       | MIN           | TYP  | MAX  | UNITS | NOTES  |

|---------------------------------------------------|--------------|---------------|------|------|-------|--------|

| Operating Current                                 | $I_{CC1}$    |               |      | 5    | mA    | 3, 14  |

| Standby Current                                   | $I_{CC2}$    |               |      | 200  | μΑ    | 3, 15  |

| Supply Voltage                                    | $V_{CCO}$    | $V_{CC}$ -0.2 |      |      | V     | 1      |

| Supply Current                                    | $I_{CCO1}$   |               |      | 150  | mA    | 4      |

| Input Leakage                                     | $I_{IL}$     | -1.0          |      | +1.0 | μA    |        |

| Output Leakage                                    | $I_{LO}$     | -1.0          |      | +1.0 | μA    |        |

| V <sub>CC</sub> Trip Point (TOL=GND)              | $V_{CCTP}$   | 4.50          | 4.62 | 4.75 | V     | 1, 16  |

| V <sub>CC</sub> Trip Point (TOL=V <sub>CC</sub> ) | $V_{CCTP}$   | 4.25          | 4.37 | 4.50 | V     | 1, 16  |

| CEI to CEO Impedance                              | $Z_{CE}$     |               |      | 30   | Ω     | 5      |

| DIS Pulldown Resistance                           | $R_{ m DIS}$ | 50k           |      | 250k | Ω     |        |

| PFO, WEO Output @ 2.4V                            | $I_{OH}$     | -1.0          |      |      | mA    | 10, 16 |

| PFO, WEO Output @ 0.4V                            | $I_{OL}$     |               |      | 4.0  | mA    | 10, 16 |

## **DC ELECTRICAL CHARACTERISTICS** (0°C to 70°C; $V_{CC}$ <4.5V)

| PARAMETER                                              | SYMBOL       | MIN            | TYP | MAX | UNITS | NOTES   |

|--------------------------------------------------------|--------------|----------------|-----|-----|-------|---------|

| CEO Output                                             | $ m V_{OHL}$ | $V_{BAT}$ -0.2 |     |     | V     |         |

| WEO Output                                             | $ m V_{OHL}$ | $V_{BAT}$ -0.2 |     |     | V     |         |

| V <sub>BAT1</sub> or V <sub>BAT2</sub> Battery Current | $I_{BAT}$    |                |     | 100 | nA    | 2, 3    |

| Battery Backup Current @                               | $I_{CCO2}$   |                |     | 150 | μΑ    | 6, 7, 8 |

| $V_{CCO} = V_{BAT} - 0.2V$                             |              |                |     |     |       |         |

**CAPACITANCE**  $(t_A = 25^{\circ}C)$

| PARAMETER          | SYMBOL    | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|-----------|-----|-----|-----|-------|-------|

| Input Capacitance  | $C_{IN}$  |     |     | 5   | pF    |       |

| Output Capacitance | $C_{OUT}$ |     |     | 7   | pF    |       |

$(0^{\circ}\text{C to }70^{\circ}\text{C}; V_{\text{CCI}} = 4.75\text{V to } 5.50\text{V}, \text{TOL= GND})$

## **AC ELECTRICAL CHARACTERISTICS**

| ( | V <sub>CCI</sub> = 4.50V | to 5.50V, | TOL-V <sub>CCO</sub> ) | ) |

|---|--------------------------|-----------|------------------------|---|

|---|--------------------------|-----------|------------------------|---|

| 7.0 EEEO1111071E 01171117  | ( • 001            | 1.00 0 10 | 0.00 V , I | <u> </u> |       |        |

|----------------------------|--------------------|-----------|------------|----------|-------|--------|

| PARAMETER                  | SYMBOL             | MIN       | TYP        | MAX      | UNITS | NOTES  |

| Address Setup              | $t_{AS}$           | 0         |            |          | ns    | 9      |

| Address Hold               | $t_{AH}$           | 50        |            |          | ns    | 9      |

| Read Recovery              | $t_{RR}$           | 10        |            |          | ns    | 9      |

| CEI, WEI Pulse Width       | $t_{\mathrm{CW}}$  | 75        |            |          | ns    | 9      |

| CEI to CEO Falling         | $t_{\mathrm{PDF}}$ |           |            | 5        | ns    | 10     |

| Propagation Delay          |                    |           |            |          |       |        |

| Later of CEI, WEI to WEO   | $t_{\mathrm{PDF}}$ |           |            | 20       | ns    | 10, 11 |

| Falling Propagation Delay  |                    |           |            |          |       |        |

| CEI to CEO Rising          | $t_{PDR}$          |           |            | 5        | ns    | 10     |

| Propagation Delay          |                    |           |            |          |       |        |

| Earlier of CEI, WEI to WEO | $t_{PDR}$          |           |            | 5        | ns    | 10, 11 |

| Rising Propagation Delay   |                    |           |            |          |       |        |

| Write Recovery             | $t_{\mathrm{WR}}$  | 10        |            |          | ns    | 9, 11  |

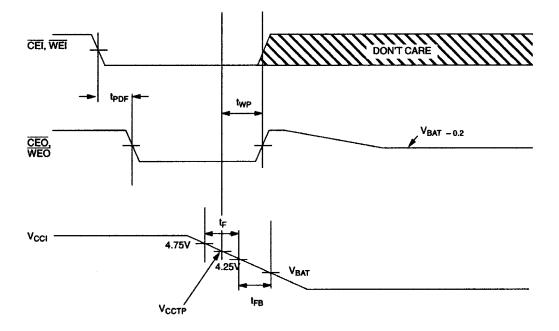

## AC ELECTRICAL CHARACTERISTICS

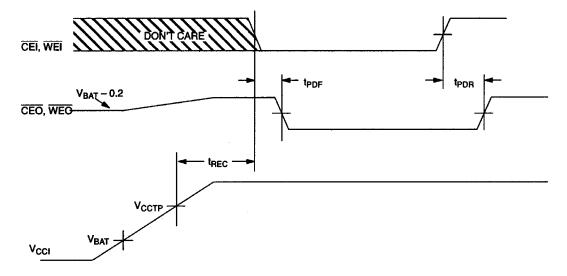

# (0°C to 70°C; V<sub>CC</sub><4.5V)

| PARAMETER                            | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------------------|------------------|-----|-----|-----|-------|-------|

| Recovery at Power-Up                 | $t_{REC}$        | 25  |     | 125 | ms    | 12    |

| V <sub>CC</sub> Slew Rate Power-Down | $t_{\mathrm{F}}$ | 300 |     |     | μs    |       |

| V <sub>CC</sub> Slew Rate Power-Down | $t_{ m FB}$      | 10  |     |     | μs    |       |

| V <sub>CC</sub> Slew Rate Power-Up   | $t_{\mathrm{F}}$ | 0   |     |     | μs    | 13    |

| CEO Pulse Width                      | $t_{WP}, t_{CE}$ |     |     | 1.5 | μs    | 7, 8  |

| WEO Pulse Width                      | $t_{WP}, t_{CE}$ |     |     | 1.5 | μs    | 7, 8  |

## **TIMING DIAGRAM: POWER-UP**

## **TIMING DIAGRAM: POWER-DOWN**

## **TIMING DIAGRAM: LOADING PARTITION REGISTER**

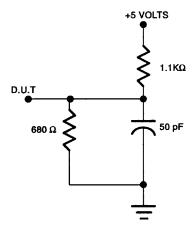

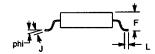

## **OUTPUT LOAD** Figure 1

#### **NOTES:**

- 1. All voltages are reference to ground

- 2. Only one battery input is required.

- 3. Measured with outputs open circuited.

- 4. I<sub>CC01</sub> is the maximum average load which the DS1610 can supply to the memories.

- 5.  $Z_{CE}$  is an average input-to-output impedance as the input is swept from ground to  $V_{CCI}$  and less than 4 mA is forced through  $Z_{CE}$ .

- 6. I<sub>CC02</sub> is the maximum average load current which the DS1610 can supply to the memories in the battery backup mode.

- 7. t<sub>CE</sub> max must be met to insure data integrity on power loss.

- 8. Chip Enable Output CEO can only sustain leakage current in the battery mode.

- 9. Applies only when loading partition switch.

- 10. Measured with a load as shown in Figure 1.

- 11. Measured with  $\overline{DIS}$  at a logic high level.

- 12.  $\overline{\text{CEO}}$  and  $\overline{\text{WEO}}$  will be held high for a time equal to  $t_{\text{REC}}$  (max = 125 ms) after  $V_{\text{CCI}}$  crosses  $V_{\text{CCTP}}$ .

- 13.  $t_R$  is the slew rate of  $V_{CCI}$  from 4.25V to 4.75V.

- 14.  $\overline{\text{CEI}}$ ,  $\overline{\text{WEI}}$ ,  $A_{\text{W}}$   $A_{\text{Z}}$  run at minimum timing set and at voltage levels of 0V to 3V.

- 15. All inputs within 0.3V of ground or  $V_{CCI}$  and  $\overline{CEI}$  within 0.3V of  $V_{CCI}$ .

- 16. The power-fail output signal ( $\overline{PFO}$ ) is driven active ( $V_{OL} = 0.4V$ ) when the  $V_{CC}$  trip point occurs. While active, the  $\overline{PFO}$  pin can sink 4 mA and will maintain a maximum output voltage of 0.4 volts. When inactive, the voltage output of  $\overline{PFO}$  is 2.4 volts minimum and will source a current of 1 mA.

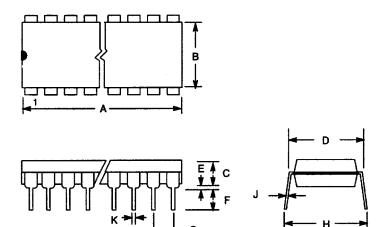

# **DS1610 16-PIN DIP (300-MIL)**

| PKG   | 16-   | PIN   |

|-------|-------|-------|

| DIM   | MIN   | MAX   |

| A IN. | 0.740 | 0.780 |

| MM    | 18.80 | 19.81 |

| B IN. | 0.240 | 0.260 |

| MM    | 6.10  | 6.60  |

| C IN. | 0.120 | 0.140 |

| MM    | 3.05  | 3.56  |

| D IN. | 0.300 | 0.325 |

| MM    | 7.62  | 8.26  |

| E IN. | 0.015 | 0.040 |

| MM    | 0.38  | 1.02  |

| F IN. | 0.120 | 0.140 |

| MM    | 3.04  | 3.56  |

| G IN. | 0.090 | 0.110 |

| MM    | 2.29  | 2.79  |

| H IN. | 0.320 | 0.370 |

| MM    | 8.13  | 9.40  |

| J IN. | 0.008 | 0.012 |

| MM    | 0.20  | 0.30  |

| K IN. | 0.015 | 0.021 |

| MM    | 0.38  | 0.53  |

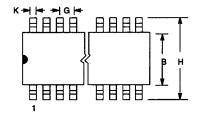

# **DS1610 16-PIN SOIC (300-MIL)**

| PKG   | 16-   | PIN   |

|-------|-------|-------|

|       |       |       |

| DIM   | MIN   | MAX   |

| A IN. | 0.402 | 0.412 |

| MM    | 10.21 | 10.46 |

| B IN. | 0.290 | 0.300 |

| MM    | 7.37  | 7.65  |

| C IN. | 0.089 | 0.095 |

| MM    | 2.26  | 2.41  |

| E IN. | 0.004 | 0.012 |

| MM    | 0.102 | 0.30  |

| F IN. | 0.094 | 0.105 |

| MM    | 2.38  | 2.68  |

| G IN. | .050  | BSC   |

| MM    | 1.27  | BSC   |

| H IN. | 0.398 | 0.416 |

| MM    | 10.11 | 10.57 |

| J IN. | 0.009 | 0.013 |

| MM    | 0.229 | 0.33  |

| K IN. | 0.013 | 0.019 |

| MM    | 0.33  | 0.48  |

| L IN. | .016  | .040  |

| MM    | .40   | 1.02  |

| PHI   | 0°    | 8°    |