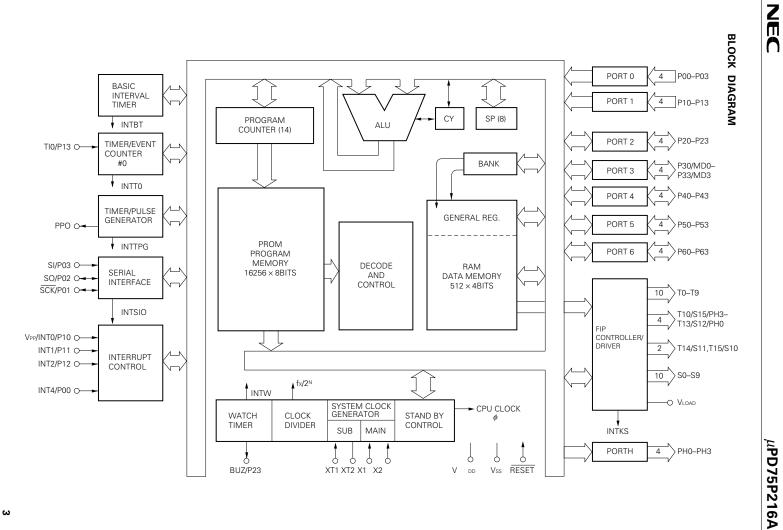

# mos integrated circuit $\mu$ PD75P216A

# **4-BIT SINGLE-CHIP MICROCOMPUTER**

The  $\mu$ PD75P216A is a One-Time PROM version of the  $\mu$ PD75216A. The  $\mu$ PD75P216A is suitable for small-scale production or experimental production in system development.

Also see documents for the  $\mu$ PD75216A.

# FEATURES

- The µPD75216A compatible

- 16256 X 8 bits of on-chip one-time PROM

- Port 6 without pull-down resistor

- High voltage output for display S0 to S8, T0 to T9: On-chip load resistor S9, T10 to T15: Open drain

- Power-on reset circuit is not available

- Single power supply (5 V  $\pm$  10 %)

# **ORDERING INFORMATION**

| Part Number       | Package                             | Quality Grade |  |

|-------------------|-------------------------------------|---------------|--|

| $\mu$ PD75P216ACW | 64-pin plastic shrink DIP (750 mil) | Standard      |  |

# Caution Pull-up resistor mask options are not available.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

# **PIN CONFIGURATION (Top View)**

# CONTENTS

| 1. | PIN FUNCTIONS                                                                 |     |

|----|-------------------------------------------------------------------------------|-----|

|    | 1.1 PORT PINS                                                                 | . 5 |

|    | 1.2 NON-PORT PINS                                                             | . 6 |

|    | 1.3 TREATMENT OF UNUSED PINS                                                  | . 8 |

| 2. | DIFFERENCES BETWEEN THE $\mu$ PD75P216A AND THE $\mu$ PD75216A, $\mu$ PD75208 | 9   |

| 3. | ONE-TIME PROM (PROGRAM MEMORY) WRITE AND VERIFY                               | 10  |

|    | 3.1 PROM WRITE AND VERIFY OPERATION                                           |     |

|    | 3.2 PROM WRITE PROCEDURE                                                      |     |

|    | 3.3 PROM READ PROCEDURE                                                       | 12  |

| 4. | ELECTRICAL SPECIFICATIONS                                                     | 13  |

| 5. | PACKAGE DRAWINGS                                                              | 22  |

|    |                                                                               |     |

| 6. | RECOMMENDED SOLDERING CONDITIONS                                              | 23  |

| AP | PENDIX DEVELOPMENT TOOLS                                                      | 24  |

# **1. PIN FUNCTIONS**

# 1.1 PORT PINS

| Pin name  | Input/<br>output | Shared<br>pin |                                                                                                          | Function                                                                                                                               | 8-bit<br>I/O | When reset | I/O circuit<br>type <sup>Note</sup> |

|-----------|------------------|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-------------------------------------|

| P00       | Input            | INT4          | 4-bit inpu                                                                                               | ıt port (PORT0).                                                                                                                       | ×            | Input      | B                                   |

| P01       | I/O              | SCK           |                                                                                                          |                                                                                                                                        |              |            | F                                   |

| P02       | I/O              | SO            |                                                                                                          |                                                                                                                                        |              |            | G                                   |

| P03       | Input            | SI            |                                                                                                          |                                                                                                                                        |              |            | B                                   |

| P10       | Input            | INT0/Vpp      |                                                                                                          | With noise elimination function                                                                                                        | x            | Input      | B                                   |

| P11       |                  | INT1          |                                                                                                          | With noise elimination function                                                                                                        |              |            |                                     |

| P12       |                  | INT2          | 4-bit inpu                                                                                               | it port (PORT1).                                                                                                                       |              |            |                                     |

| P13       |                  | TI0           |                                                                                                          |                                                                                                                                        |              |            |                                     |

| P20       | I/O              | _             | 4-bit I/O p                                                                                              | port (PORT2).                                                                                                                          | x            | Input      | E                                   |

| P21       |                  | _             |                                                                                                          |                                                                                                                                        |              |            |                                     |

| P22       |                  | _             |                                                                                                          |                                                                                                                                        |              |            |                                     |

| P23       |                  | BUZ           |                                                                                                          |                                                                                                                                        |              |            |                                     |

| P30 - P33 | I/O              | MD0 - MD3     | -                                                                                                        | Programmable 4-bit I/O port (PORT3).<br>I/O can be specified bit by bit.                                                               |              | Input      | E                                   |

| P40 - P43 | I/O              | _             | Can direc<br>Data inpu                                                                                   | 4-bit I/O port (PORT4).<br>Can directly drive LEDs.<br>Data input/output pins for the PROM<br>write and verify (Four low-order bits).  |              | Input      | E                                   |

| P50 - P53 | I/O              | _             | Can direc<br>Data inpu                                                                                   | 4-bit I/O port (PORT5).<br>Can directly drive LEDs.<br>Data input/output pins for the PROM<br>write and verify (Four high-order bits). |              | Input      | E                                   |

| P60 - P63 | I/O              | _             | Programmable 4-bit I/O port (PORT6).<br>I/O can be specified bit by bit.<br>Suitable for keyboard input. |                                                                                                                                        | ×            | Input      | E                                   |

| PH0       | Output           | T13/S12       |                                                                                                          | 4-bit P-ch open-drain output port                                                                                                      |              | High       | I-D                                 |

| PH1       | 1                | T12/S13       |                                                                                                          | stand high voltage and<br>ent (PORTH)                                                                                                  |              | impedance  |                                     |

| PH2       | 1                | T11/S14       |                                                                                                          |                                                                                                                                        |              |            |                                     |

| PH3       | ]                | T10/S15       |                                                                                                          |                                                                                                                                        |              |            |                                     |

**Note** The circle  $(\bigcirc)$  indicates the Schmitt triggered input.

# 1.2 NON-PORT PINS

| Pin name             | Input/<br>output | Shared<br>pin |                                                                                                            | Function                                                                                                                                                                 | When reset        | I/O circuit<br>type <sup>Note 1</sup> |

|----------------------|------------------|---------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|

| T0 - T9              |                  | _             | Note 2                                                                                                     | Used for digit output<br>Can withstand high voltage and high current                                                                                                     | Low level         | I - E                                 |

| T10/S15 -<br>T13/S12 |                  | PH3-PH0       |                                                                                                            | For digit/segment output<br>Can withstand high voltage and high current<br>Unused pin can be used as PORTH.                                                              |                   |                                       |

| T14/S11,<br>T15/S10  | Output           |               | Note 3                                                                                                     | For digit/segment output<br>Can withstand high voltage and high current<br>Static output is possible.                                                                    | High<br>impedance | I - D                                 |

| S9                   |                  | -             |                                                                                                            | For segment output<br>Can withstand high voltage<br>Static output is possible                                                                                            |                   |                                       |

| S0 -S8               |                  |               | Note 2                                                                                                     | For segment output<br>Can withstand high voltage                                                                                                                         | Low level         | I - E                                 |

| PPO                  | Output           | -             | Puls                                                                                                       | e output by timer/pulse generator                                                                                                                                        | High<br>impedance | D                                     |

| T10                  | Input            | P13           | Exte                                                                                                       | rnal event pulse input to timer event counter                                                                                                                            |                   | B                                     |

| SCK                  | I/O              | P01           | Inpu                                                                                                       | t and output to serial clock                                                                                                                                             | Input             | F                                     |

| SO                   | I/O              | P02           | Seria                                                                                                      | al data output or serial data input and output                                                                                                                           | Input             | G                                     |

| SI                   | Input            | P03           | Seria                                                                                                      | al data input or normal input                                                                                                                                            | Input             | B                                     |

| INT4                 | Input            | P00           | -                                                                                                          | e detection vectored interrupt input<br>ected at both rising edge and falling edge)                                                                                      | _                 | B                                     |

| INT0                 | Input            | P10/VPP       | Edge                                                                                                       | e detection vectored interrupt input with noise                                                                                                                          |                   |                                       |

| INT1                 | _ Input          | P11           | elim                                                                                                       | elimination function (edge-detection selectable)                                                                                                                         |                   | B                                     |

| INT2                 | Input            | P12           | Testable input for edge-detection<br>(detected at rising edge)                                             |                                                                                                                                                                          | _                 | B                                     |

| BUZ                  | I/O              | P23           |                                                                                                            | Fixed frequency output<br>(For buzzer or system clock trimming)                                                                                                          |                   | E                                     |

| X1, X2               | Input            | _             | syste<br>sign                                                                                              | tal/ceramic resonator connection for main<br>em clock generation. When external clock<br>al is used, it is applied to X1, and its reverse<br>se signal is applied to X2. | _                 | _                                     |

| XT1                  | Input            |               |                                                                                                            | tal connection for subsystem clock generation.                                                                                                                           |                   |                                       |

| XT2                  | _                | _             |                                                                                                            | n external clock signal is used, it is applied to and XT2 is open.                                                                                                       | _                 | -                                     |

| RESET                | Input            | _             | Syst                                                                                                       | em reset input (low-level active)                                                                                                                                        | _                 | B                                     |

| MD0 - MD3            | I/O              | P30 - P33     | Ope                                                                                                        | ration mode selection during the PROM<br>e/verify cycles.                                                                                                                | _                 | E                                     |

| Vpp                  |                  | P10/INT0      | +12.                                                                                                       | 5 V is applied as the programming voltage<br>ng the PROM write/verify cycles                                                                                             | _                 | B                                     |

| VLOAD                |                  | _             |                                                                                                            | down resistor connection of FIP<br>roller/driver                                                                                                                         | _                 | I - E                                 |

| Vdd                  |                  | _             | Positive power supply<br>+6 V is applied as the programming voltage during<br>the PROM write/verify cycles |                                                                                                                                                                          | _                 | _                                     |

| Vss                  |                  | _             | GND                                                                                                        | potential                                                                                                                                                                | _                 | -                                     |

| NC Note 4            |                  | _             | No c                                                                                                       | connection                                                                                                                                                               | _                 | _                                     |

**Note 1.** The circle ( $\bigcirc$ ) indicates the Schmitt triggered input.

- **2.** Pull-down resistor is incorporated.

- 3. Open-drain output

- **4.** NC pin should be connected to VPRE when sharing print board with the  $\mu$ PD75216A.

Fig. 1-1 Pin Input/Output Circuit

# **1.3 TREATMENT OF UNUSED PINS**

| Pin                     | Recommended connection       |

|-------------------------|------------------------------|

| P00/INT4                | Connect to Vss               |

| P01/SCK                 |                              |

| P02/SO                  | Connect to Vss or Vod        |

| P03/SI                  |                              |

| P10/INT0/Vpp            |                              |

| P11/INT1, P12/INT2      | Connect to Vss               |

| P13/T10                 |                              |

| P20 - P22               |                              |

| P23/BUZ                 |                              |

| P30/MD0 - P33/MD3       | Input: Connect to Vss or VDD |

| P40 - P43               | Output: Open                 |

| P50 - P53               |                              |

| P60 - P63               |                              |

| PPO                     |                              |

| S0 - S9                 |                              |

| T15/S10, T14/S11        | Open                         |

| Т0 - Т9                 |                              |

| T10/S15/PH3-T13/S12/PH0 |                              |

| XT1                     | Connect to Vss or VDD        |

| XT2                     | Open                         |

# Table 1-2 Recommended Connection for Unused Pins

# 2. DIFFERENCES BETWEEN THE $\mu\text{PD75P216A}$ and the $\mu\text{PD75216A},\ \mu\text{PD75208}$

| Paramo                             | eter             | μPD75P216A                             | μPD75216A                                                          | μPD75208                         |  |

|------------------------------------|------------------|----------------------------------------|--------------------------------------------------------------------|----------------------------------|--|

|                                    |                  | One-time PROM                          | Mask                                                               | ROM                              |  |

| ROM                                |                  | 16256 × 8 bits<br>(0000H – 3F7FH)      |                                                                    | 8064 × 8 bits<br>(0000H – 1F7FH) |  |

|                                    |                  | $512 \times 4$ bits                    |                                                                    | 497 × 4 bits                     |  |

| FIP <sup>®</sup> Controller Driver |                  | 9 – 16 segments                        |                                                                    | 9 – 12 segments                  |  |

|                                    | Port 6           | N/A                                    |                                                                    |                                  |  |

| Pull-Down Registor                 | S0 – S8, T0 – T9 | On-chip                                | Mask option                                                        |                                  |  |

|                                    | S9, T10 – T15    | N/A (Open-drain)                       | 1                                                                  |                                  |  |

| Power-On                           | Reset            | N/A                                    | Mask option                                                        |                                  |  |

| Power-O                            | n Flag           | N/A                                    |                                                                    |                                  |  |

|                                    |                  | P10/INT0/VPP                           | P10/INT0                                                           |                                  |  |

| Pin Conn                           | ection           | P30/MD0 – P33/MD3                      | P30 – P33                                                          |                                  |  |

|                                    |                  | NC                                     | V                                                                  | PRE                              |  |

| Operating Ambier                   | nt Temperature   | –10 to +70 °C                          | –40 to                                                             | +85 °C                           |  |

| Operating Supply Voltage           |                  | 5 V $\pm$ 10 %                         | 2.7 to 6.0 V                                                       |                                  |  |

| Packa                              | ge               | 64-pin plastic shrink DIP<br>(750 mil) | 64-pin plastic shrink DIP (750 m<br>64-pin plastic QFP (14 × 20 mm |                                  |  |

# Table 2-1 Differences between the $\mu$ PD75P216A and the $\mu$ PD75216A, $\mu$ PD75208

# 3. ONE-TIME PROM (PROGRAM MEMORY) WRITE AND VERIFY

The  $\mu$ PD75P216A contains 16256 × 8 bits of one-time PROM available of writing. The following table shows the pin functions during the write and verify cycles. Note that it is not necessary to enter an address, because the address is updated by pulsing the X1 clock pins.

| Pin name                                              | Function                                                                                                    |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Vpp                                                   | Voltage application pin for write and verify (Normally VDD potential)                                       |

| X1, X2                                                | Address-update clock input during write/verify.<br>The inverted signal of the X1 should be input to the X2. |

| MD0 - MD3                                             | Operation mode selection pins for write and verify                                                          |

| P40 - P43 (lower 4 bits)<br>P50 - P53 (higher 4 bits) | 8-bit data input/output pins for write and verify                                                           |

| VDD                                                   | Supply voltage application pin Normally 5 V $\pm$ 10 %; 6 V is applied during write/verify                  |

#### Table 3-1 Used Pin at PROM Write and Verify

Caution 1. The pins which are not used during write or verify should be treated as follows

- Port, XT1, RESET ... Connect to Vss through pull-down resistors

- S0 to S9, T0 to T15, PPO, VLOAD ... Connect to VDD through pull-up resistors

- XT2 ... Open

- 2. The  $\mu$ PD75P216A do not have a UV erase window, thus the PROM contents cannot be erased with ultra violet ray.

#### 3.1 PROM WRITE AND VERIFY OPERATION

When +6 V and +12.5 V are applied to the V<sub>DD</sub> and V<sub>PP</sub> pins, respectively, the PROM is placed in the write/ verify mode. The operation is selected by the MD0 to MD3 pins, as shown in the table.

|       | Ope  | eration mod | Ou continue and a |     |     |                                   |  |  |

|-------|------|-------------|-------------------|-----|-----|-----------------------------------|--|--|

| Vpp   | Vdd  | MD0         | MD1               | MD2 | MD3 | Operation mode                    |  |  |

| +12.5 | +6 V | н           | L                 | н   | L   | Clear program memory address to 0 |  |  |

|       |      | L           | Н                 | Н   | Н   | Write mode                        |  |  |

|       |      | L           | L                 | Н   | Н   | Verify mode                       |  |  |

|       |      | н           | ×                 | н   | н   | Program inhibit mode              |  |  |

Table 3-2 PROM Write and Verify Operation

×: Don't care.

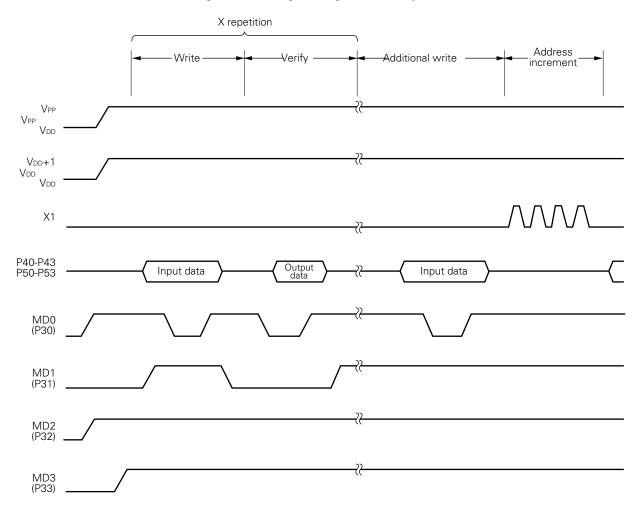

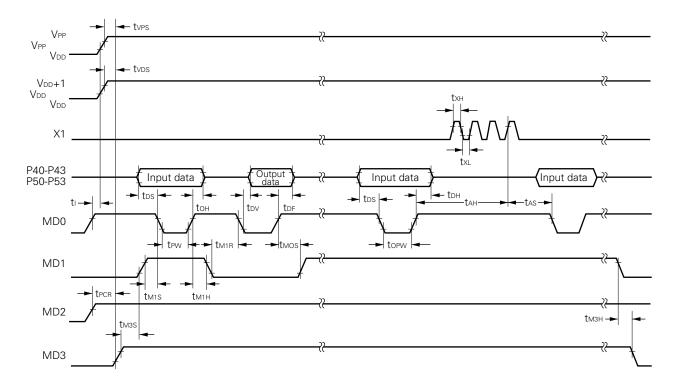

# 3.2 PROM WRITE PROCEDURE

PROM can be written at high speed using the following procedure: (see the following figure)

- (1) Pull unused pins to Vss through resistors. Set the X1 pin low.

- (2) Supply 5 volts to the VDD and VPP pins.

- (3) Wait for 10  $\mu$ s.

- (4) Select the zero clear program memory address mode.

- (5) Supply 6 volts to the VDD and 12.5 volts to the VPP pins.

- (6) Select the program inhibit mode.

- (7) Write data in the 1 ms write mode.

- (8) Select the program inhibit mode.

- (9) Select the verify mode. If the data is correct, proceed to step (10). If not repeat steps (7), (8) and (9).

- (10) Perform one additional write (duration of  $1ms \times number$  of writes at (7) to (9)).

- (11) Select the program inhibit mode.

- (12) Apply four pulses to the X1 pin to increment the program memory address by one.

- (13) Repeat steps (7) to (12) until the end address is reached.

- (14) Select the zero clear program memory address mode.

- (15) Return the VDD and VPP pins back to + 5 volts.

- (16) Turn off the power.

Fig. 3-1 Timing of Program Memory Write

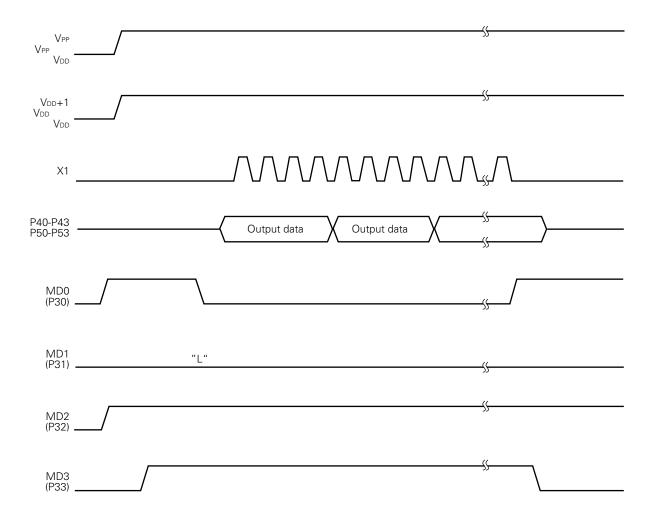

# 3.3 PROM READ PROCEDURE

The PROM contents can be read in the verify mode by using the following procedure: (see the following figure)

- (1) Pull unused pins to Vss through resistors. Set the X1 pin low.

- (2) Supply 5 volts to the VDD and VPP pins.

- (3) Wait for 10  $\mu$ s.

- (4) Select the zero clear program memory address mode.

- (5) Supply 6 volts to the VDD and 12.5 volts to the VPP pins.

- (6) Select the program inhibit mode.

- (7) Select the verify mode. Apply four pulses to the X1 pin. Every four clock pulses will output the data stored in one address.

- (8) Select the program inhibit mode.

- (9) Select the zero clear program memory address mode.

- (10) Return the VDD and VPP pins back to + 5 volts.

- (11) Turn off the power.

# Fig. 3-2 Timing of Program Memory Read

# 4. ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings (Ta = 25 °C)

| Parameter                 | Symbol | Conditions                          | Ratings                                      | Unit |

|---------------------------|--------|-------------------------------------|----------------------------------------------|------|

|                           | Vdd    |                                     | –0.3 to +7.0                                 | V    |

| Supply voltage            | VLOAD  |                                     | V <sub>DD</sub> -40 to V <sub>DD</sub> + 0.3 | V    |

|                           | Vpp    |                                     | –0.3 to +13.5                                | V    |

| Input voltage             | Vı     |                                     | -0.3 to VDD +0.3                             | V    |

| Output voltage            | Vo     | Other than display pins             | -0.3 to VDD +0.3                             | V    |

| Output voltage            | Vod    | Display pins                        | $V_{DD}$ –40 to $V_{DD}$ + 0.3               | V    |

|                           |        | Single pin; other than display pins | -15                                          | mA   |

|                           |        | Single pin; S0 – S9                 | -15                                          | mA   |

| High-level output current | Іон    | Single pin; T0 – T15                | -30                                          | mA   |

|                           |        | Total of all pins other than diplay | -20                                          | mA   |

|                           |        | Total of all display pins           | -120                                         | mA   |

|                           |        | Single pin                          | 17                                           | mA   |

| Low level output current  | Ιοι    | Total of all pins                   | 60                                           | mA   |

| Operating temperature     | Topt   |                                     | -10 to +70                                   | °C   |

| Storage temperature       | Tstg   |                                     | -65 to +150                                  | °C   |

# Operating Supply Voltage ( $T_a = -10$ to + 70 °C)

| Parameter             | Conditions | MIN. | MAX. | Unit |

|-----------------------|------------|------|------|------|

| CPU Note              |            | 4.5  | 5.5  | V    |

| Display controller    |            | 4.5  | 5.5  | V    |

| Timer/pulse generator |            | 4.5  | 5.5  | V    |

| Other hardwares Note  |            | 4.5  | 5.5  | V    |

Note Except system clock oscillation circuit, display controller, timer/pulse generator.

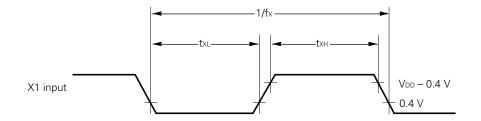

# Main System Clock Configurations (Ta = -10 to +70 °C, VDD = 5 V $\pm$ 10 %)

| Resonator            | Recommended constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parameter                                   | Conditions                                                                            | MIN. | TYP. | MAX.       | Unit |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------|------|------|------------|------|

| Ceramic              | X1 X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Note 1<br>Oscillation<br>frequency (fxx)    | V <sub>DD</sub> = Oscillator<br>operating voltage<br>range                            | 2.0  |      | 5.0 Note 3 | MHz  |

| resonator            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Note 2<br>Oscillation<br>stabilization time | After V <sub>DD</sub> reaches the<br>minimum oscillator<br>operating voltage<br>range |      |      | 4          | ms   |

|                      | constantsParameterConditionsM $x_1$ $x_2$ Note 1VDD = Oscillator<br>operating voltage<br>range2 $x_1$ $x_2$ Oscillation<br>frequency (fxx)After VDD reaches the<br>minimum oscillator<br>operating voltage<br>range2 $x_1$ $x_2$ Note 2After VDD reaches the<br>minimum oscillator<br>operating voltage<br>range2 $x_1$ $x_2$ Oscillation<br>frequency (fxx)2 $x_1$ $x_2$ Oscillation<br>frequency (fxx)2 $x_1$ $x_2$ Oscillation<br>frequency (fxx)2 $x_1$ $x_2$ Note 12 $x_1$ $x_2$ Note 12 $x_1$ $x_2$ Note 12 $x_1$ $x_2$ $x_3$ $x_4$ $x_1$ $x_2$ $x_3$ $x_4$ $x_1$ $x_2$ $x_3$ $x_4$ $x_1$ $x_2$ $x$ | Oscillation                                 |                                                                                       | 2.0  | 4.19 | 5.0 Note 3 | MHz  |

| Crystal<br>resonator |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             |                                                                                       | 10   | ms   |            |      |

|                      | X1 X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X1 input                                    |                                                                                       | 2.0  |      | 5.0 Note 3 | MHz  |

| External<br>clock    | μPD74HCU04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | low-level width                             |                                                                                       | 100  |      | 250        | ns   |

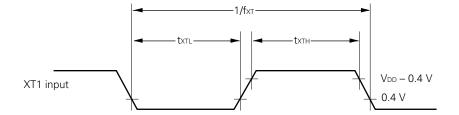

# Subsystem Clock Configurations (Ta = –10 to +70 °C, Vdd = 5 V $\pm$ 10 %)

| Resonator | Recommended constants                                                                                                                                                                                                                                   | Parameter                                             | Conditions | MIN. | TYP.   | MAX. | Unit |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------|------|--------|------|------|

| Crystal   | XT1 XT2                                                                                                                                                                                                                                                 | Note 1<br>Oscillation<br>frequency (fx⊤)              |            | 32   | 32.768 | 35   | kHz  |

| resonator | or constants Parameter<br>XT1 XT2<br>R<br>C3<br>C4<br>Oscillation<br>frequency (fxr)<br>Oscillation<br>stabilization ti<br>XT1 input<br>frequency (fxr)<br>XT1 input<br>frequency (fxr)<br>XT1 input<br>frequency (fxr)<br>XT1 input<br>frequency (fxr) | Note 2<br>Oscillation<br>stabilization time           |            |      | 1      | 2    | s    |

| External  |                                                                                                                                                                                                                                                         | XT1 input<br>frequency (fxt)                          |            | 32   |        | 100  | kHz  |

| clock     |                                                                                                                                                                                                                                                         | X1 input high- and<br>low-level width<br>(txTH, tXTL) |            | 10   |        | 32   | μs   |

- **Note 1.** The oscillation frequency and input frequency only indicate the characteristics of the oscillation circuit. Refer to the AC characteristics for the instruction execution time.

- **2.** The oscillation stabilization time is the time until the oscillation enters a stable state after the application of V<sub>DD</sub> or the release of STOP mode.

- ★ 3. When the oscillation frequency is 4.19 < fx ≤ 5.0 MHz, PCC = 0011 should not be selected as the instruction execution time. If PCC = 0011 is selected, 1 machine cycle is less than the specified minimum value, which is 0.95 µs.</li>

14

#### Capacitance (T<sub>a</sub> = 25 $^{\circ}$ C, V<sub>DD</sub> = 0 V)

| Parameter                |                           | Symbol | Conditions                      | MIN. | TYP. | MAX. | Unit |

|--------------------------|---------------------------|--------|---------------------------------|------|------|------|------|

| Input capacitance        | Input capacitance         |        |                                 |      |      | 15   | pF   |

| Output conscitones       | Other than display output | Соит   | f = 1 MHz                       |      |      | 15   | pF   |

| Output capacitance       | Display<br>output         | COUT   | Unmeasured pins returned to 0 V |      |      | 35   | pF   |

| Input/Output capacitance |                           | Сю     |                                 |      |      | 15   | pF   |

#### DC Characteristics (Ta = -10 to +70 °C, VDD = 5 V $\pm$ 10 %)

| Parameter                                                                                                                                                                                                                                                                                                                                                                                         | Symbol | Conditions                            |                         | MIN.     | TYP.                                                  | MAX.                             | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------|-------------------------|----------|-------------------------------------------------------|----------------------------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                   | VIH1   | All except ports 0, 1, 6              | 0.7 Vdd                 |          | Vdd                                                   | V                                |      |

| lich lovel innut veltage                                                                                                                                                                                                                                                                                                                                                                          | VIH2   | Port 0, 1 RESET                       |                         | 0.75 Vdd |                                                       | Vdd                              | V    |

| High-level input voltage<br>Low-level input voltage<br>High-level output voltage<br>Low-level output voltage<br>Low-level output voltage<br>Low-level input leakage<br>current<br>Low-level input leakage<br>current<br>High-level output leakage<br>current<br>Low-level output leakage<br>current<br>Low-level output leakage<br>current<br>Display output current<br>Dn-chip pull-down resisto | Vінз   | X1, X2, XT1                           |                         | VDD-0.4  |                                                       | Vdd                              | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                   | VIH4   | Port 6                                |                         | 0.65 VDD |                                                       | Vdd                              | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                   | VIL1   | All except ports 0, 1, 6              | 6, X1, X2, XT1, RESET   | 0        |                                                       | 0.3 Vdd                          | V    |

| Low-level input voltage                                                                                                                                                                                                                                                                                                                                                                           | VIL2   | Port 0, 1, 6 RESET                    |                         | 0        |                                                       | 0.2 VDD                          | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                   | VIL3   | X1, X2, XT1                           |                         | 0        | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 0.4                              | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                   | Vон    |                                       | Iон = −1 mA             | Vdd-1.0  |                                                       |                                  | V    |

| High-level output voltage                                                                                                                                                                                                                                                                                                                                                                         | • ОН   | All outputs                           | Іон = −100 μА           | VDD-0.5  |                                                       |                                  | V    |

| 1 1 1 4 14                                                                                                                                                                                                                                                                                                                                                                                        | N      | Port 4, 5                             | lo∟ = 15 mA             |          | 0.4                                                   | 2.0                              | V    |

| Low-level output voltage                                                                                                                                                                                                                                                                                                                                                                          | Vol    | All outputs                           | lo∟ = 1.6 mA            |          |                                                       | 0.4                              | V    |

| High-level input leakage                                                                                                                                                                                                                                                                                                                                                                          | Ілні   | All except X1, X2, XT1                |                         |          |                                                       | 3                                | μA   |

| current                                                                                                                                                                                                                                                                                                                                                                                           | ILIH2  | X1, X2, XT1                           | VI = VDD                |          |                                                       | 0.4<br>3<br>20<br>-3<br>-20<br>3 | μΑ   |

| Low-level input leakage                                                                                                                                                                                                                                                                                                                                                                           |        | All except X1, X2, XT1                |                         |          |                                                       | -3                               | μΑ   |

| current                                                                                                                                                                                                                                                                                                                                                                                           | ILIL2  | X1, X2, XT1                           | 1<br>V1 = 0 V           |          |                                                       | -20                              | μA   |

| High-level output leakage current                                                                                                                                                                                                                                                                                                                                                                 | Ігон   | All outputs                           | Vo = Vdd                |          |                                                       | 3                                | μA   |

| Low-level output leakage                                                                                                                                                                                                                                                                                                                                                                          | ILOL1  | All except display output             | Vo = 0 V                |          |                                                       | -3                               | μA   |

| current                                                                                                                                                                                                                                                                                                                                                                                           | ILOL2  | Display outputs                       | Vo = Vload = Vdd - 35 V |          |                                                       | -10                              | μA   |

|                                                                                                                                                                                                                                                                                                                                                                                                   |        | S0 - S9                               | <u> </u>                | -3       | -5.5                                                  |                                  | mA   |

| Display output current                                                                                                                                                                                                                                                                                                                                                                            | Гор    | T0 - T15                              | $V_{OD} = V_{DD} - 2 V$ | -15      | -22                                                   |                                  | mA   |

| On-chip pull-down resistor                                                                                                                                                                                                                                                                                                                                                                        | R∟     | Display outputs                       | Vod – Vload = 35 V      | 25       | 70                                                    | 135                              | kΩ   |

|                                                                                                                                                                                                                                                                                                                                                                                                   | IDD1   | 4.19 MHz                              | Note 2                  |          | 3.0                                                   | 9.0                              | mA   |

|                                                                                                                                                                                                                                                                                                                                                                                                   | IDD2   | Crystal oscillator<br>C1 = C2 = 15 pF | HALT mode               |          | 600                                                   | 1 800                            | μA   |

| Power supply current Note 1                                                                                                                                                                                                                                                                                                                                                                       | Ірдз   | 32.768 kHz Note 3                     |                         |          | 100                                                   | 300                              | μA   |

|                                                                                                                                                                                                                                                                                                                                                                                                   | IDD4   | Crystal oscillator                    | HALT mode               |          | 40                                                    | 100                              | μA   |

|                                                                                                                                                                                                                                                                                                                                                                                                   | IDD5   | XT1 = 0 V                             | STOP mode               |          | 0.5                                                   | 20                               | μA   |

Note 1. Does not include the current for the on-chip pull-down resistor (output circuit to S0 to S8, T0 to T9).

- 2. When the processor clock control register (PCC) is set to 0011 and operated in high-speed mode.

- **3.** When the system clock control register (SCC) is set to 1001 to stop the main system clock, and when the sub-system clock is used.

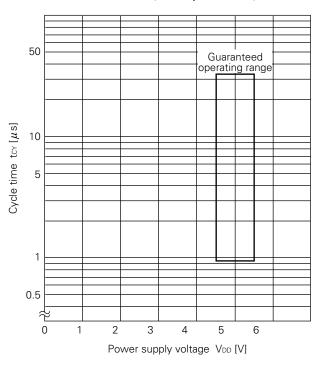

| Parameter                                                                  | Symbol          | Conditions      |         | MIN.              | TYP. | MAX. | Unit |

|----------------------------------------------------------------------------|-----------------|-----------------|---------|-------------------|------|------|------|

| CPU clock time Note 1<br>(minimum instruction                              | 4               |                 |         | 0.95              |      | 32   | μs   |

| execution time = 1 machine cycle)                                          | tcy             | Subsystem clock |         | 114               | 122  | 125  | μs   |

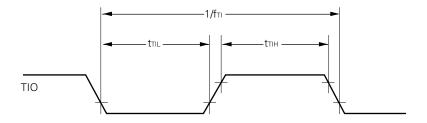

| TI0 input frequency                                                        | f⊤ı             |                 |         | 0                 |      | 0.6  | MHz  |

| TIO input high- and low-level width                                        | t⊤iн, t⊤i∟      |                 |         | 0.83              |      |      | μs   |

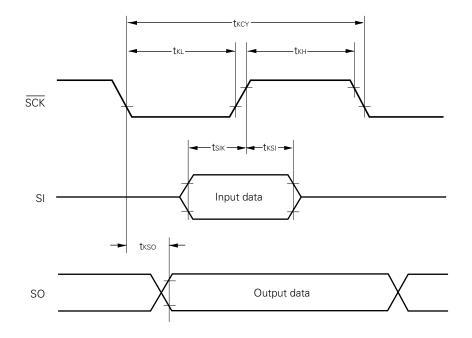

| <u>CCK</u> avala time                                                      | 4               |                 | Input   | 0.8               |      |      | μs   |

| SCK cycle time                                                             | <b>t</b> KCY    |                 | Output  | 0.95              |      |      | μs   |

|                                                                            |                 |                 | Input   | 0.4               |      |      | μs   |

| SCK high- and low-level width                                              | tкн, tк∟        |                 | Output  | tксү/ <b>2-50</b> |      |      | ns   |

| SI setup time (to $\overline{\text{SCK}} \uparrow$ )                       | tsıк            |                 |         | 100               |      |      | ns   |

| SI hold time (to $\overline{\text{SCK}}$ $\uparrow$ )                      | tĸsi            |                 |         | 400               |      |      | ns   |

| $\overline{\text{SCK}} \downarrow \rightarrow \text{SO}$ output delay time | <b>t</b> ĸso    |                 |         |                   |      | 300  | ns   |

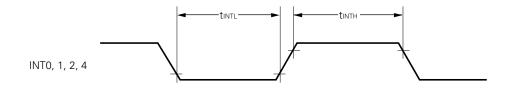

|                                                                            |                 |                 | INT0    | Note 2            |      |      | μs   |

| Interrupt inputs<br>high- and low-level width                              | tinth,<br>tintl |                 | INT1    | 2tcy              |      |      | μs   |

| J                                                                          |                 |                 | INT2, 4 | 10                |      |      | μs   |

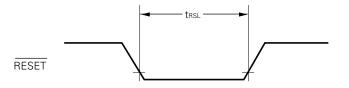

| RESET low-level width                                                      | trsl            |                 |         | 10                |      |      | μs   |

AC Characteristics (Ta = –10 to +70 °C, VDD = +5 V  $\pm$ 10%)

Note 1. The CPU clock (Ø) cycle time is decided by the oscillation frequency of the resonator, system clock control register (SCC), and processor clock control register (PCC). The figure to the right indicates cycle time (tcr) characteristics for supply voltage VDD when using the main system clock.

2. This is 2tcy or 128/fxx according to the interrupt mode register setting (IM0).

tcy vs VDD (Main system clock)

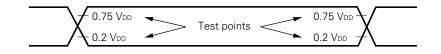

# AC timing Test Point (Except X1, XT1)

# **Clock Timing**

**TIO Timing**

# Serial Transfer Timing

# Interrupt Input Timing

# **RESET** Input Timing

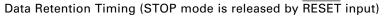

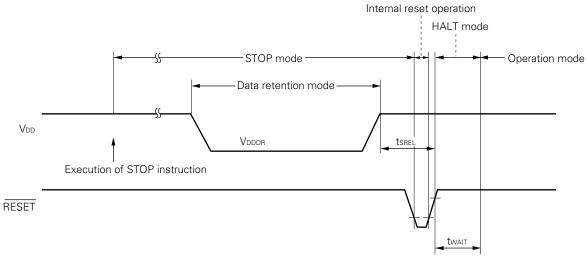

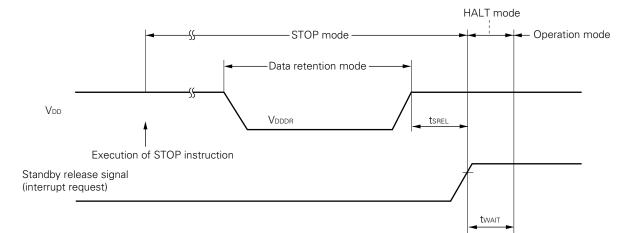

# Data Memory STOP Mode Low Voltage Data Retention Characteristics (Ta = -10 to +70 °C)

| Parameter                      | Symbol | Conditions                    | MIN. | TYP.   | MAX. | Unit |

|--------------------------------|--------|-------------------------------|------|--------|------|------|

| Data retention voltage V       |        |                               | 2.0  |        | 5.5  | V    |

| Data retention current         | Idddr  | VDDDR = 2.0 V                 |      | 0.1    | 10   | μΑ   |

| Released signal SET time       | tsrel  |                               | 0    |        |      | μs   |

| Note 1                         | +      | Released by RESET input       |      | 217/fx |      | ms   |

| Oscillation stabilization time | twait  | Released by interrupt request |      | Note 2 |      | ms   |

- **Note 1.** The oscillation stabilization wait time is a period during which the CPU is kept inactive in order to avoid unstable operation at the start of oscillation.

- 2. Depends on the setting of the basic interval time mode register (BTM) (see the following table).

| BTM3 | BTM2 | BTM1 | BTM0 | Wait time ( ): fxx = 4.19 MHz          |

|------|------|------|------|----------------------------------------|

| -    | 0    | 0    | 0    | 2 <sup>20</sup> /fxx (approx. 250 ms)  |

| -    | 0    | 1    | 1    | 2 <sup>17</sup> /fxx (approx. 31.3 ms) |

| -    | 1    | 0    | 1    | 2 <sup>15</sup> /fxx (approx. 7.82 ms) |

| _    | 1    | 1    | 1    | 2 <sup>13</sup> /fxx (approx. 1.95 ms) |

#### Data Retention Timing (Standby release signal: STOP mode is released by interrupt signal)

# DC Programming Characteristics (Ta = 25 $\pm$ 5 °C, VDD = 6.0 $\pm$ 0.25 V, VPP = 12.5 $\pm$ 0.3 V, Vss = 0 V)

| Parameter                 | Symbol | Conditions           | MIN.    | TYP. | MAX.    | Unit |

|---------------------------|--------|----------------------|---------|------|---------|------|

|                           | VIH1   | All except X1, X2    | 0.7 Vdd |      | VDD     | V    |

| High-level input voltage  | VIH2   | X1, X2               | VDD-0.5 |      | VDD     | V    |

| Low-level input voltage   | VIL1   | All except X1, X2    | 0       |      | 0.3 VDD | V    |

|                           | VIL2   | X1, X2               | 0       |      | 0.4     | V    |

| Input leakage current     | IL1    | VIN = VIL or VIH     |         |      | 10      | μA   |

| High-level output voltage | Vон    | Іон = –1 mA          | VDD-1.0 |      |         | V    |

| Low-level output voltage  | Vol    | loι = 1.6 mA         |         |      | 0.4     | V    |

| VDD power supply current  | loo    |                      |         |      | 30      | mA   |

| VPP power supply current  | Ірр    | MD0 = VIL, MD1 = VIH |         |      | 30      | mA   |

Note 1. VPP should not exceed +22 V (including overshoot).

2. VDD should be applied before VPP and turned off after VPP.

# AC Programming Characteristics (Ta = 25 $\pm$ 5 $^{\circ}C$ , Vdd = 6.0 $\pm$ 0.25 V, VpP = 12.5 $\pm$ 0.3 V, Vss = 0 V)

| Parameter                                                     | Symbol       | Note 1      | Conditions                             | MIN.  | TYP. | MAX. | Unit |

|---------------------------------------------------------------|--------------|-------------|----------------------------------------|-------|------|------|------|

| Address setup time <sup>Note 2</sup> (toMD0↓)                 | tas          | tas         |                                        | 2     |      |      | μs   |

| MD1 setup time (to MD0↓)                                      | tмıs         | toes        |                                        | 2     |      |      | μs   |

| Data setup time (to MD0↓)                                     | tos          | tos         |                                        | 2     |      |      | μs   |

| Address hold time Note 2 (from MD0 <sup>↑</sup> )             | tан          | tан         |                                        | 2     |      |      | μs   |

| Data hold time (from MD0 <sup>↑</sup> )                       | tdн          | tон         |                                        | 2     |      |      | μs   |

| MD0 $\uparrow \rightarrow$ data output float delay time       | <b>t</b> df  | <b>t</b> df |                                        | 0     |      | 130  | ns   |

| V <sub>PP</sub> setup time (to MD3 <sup>↑</sup> )             | tvps         | tvps        |                                        | 2     |      |      | μs   |

| V <sub>DD</sub> setup time (to MD3 <sup>↑</sup> )             | tvds         | tvcs        |                                        | 2     |      |      | μs   |

| Initialized program pulse width                               | tew          | tew         |                                        | 0.95  | 1.0  | 1.05 | ms   |

| Additional program pulse width                                | topw         | topw        |                                        | 0.95  |      | 21.0 | ms   |

| MD0 setup time (to MD1 <sup>↑</sup> )                         | tмos         | tces        |                                        | 2     |      |      | μs   |

| MD0 $\downarrow  ightarrow$ data output delay time            | tov          | tov         | MD0 = MD1 = VIL                        |       |      | 1    | μs   |

| MD1 hold time (from MD0↑)                                     | tмін         | tоен        | $t_{\rm max} + t_{\rm max} > 50 \mu_0$ | 2     |      |      | μs   |

| MD1 recovery time (to MD0↓)                                   | tмік         | tor         | tмін + tмік ≥ 50 $\mu$ s               | 2     |      |      | μs   |

| Program counter reset time                                    | <b>t</b> PCR | —           |                                        | 10    |      |      | μs   |

| X1 input high- and low-level width                            | txн, txL     | —           |                                        | 0.125 |      |      | μs   |

| X1 input frequency                                            | fx           | —           |                                        |       |      | 4.19 | MHz  |

| Initial mode set time                                         | tı           | —           |                                        | 2     |      |      | μs   |

| MD3 setup time (to MD1 <sup>↑</sup> )                         | tмзs         | —           |                                        | 2     |      |      | μs   |

| MD3 hold time (from MD1↓)                                     | tмзн         | —           |                                        | 2     |      |      | μs   |

| MD3 setup time (to MD0↓)                                      | tмзsr        | —           | During program read cycle              | 2     |      |      | μs   |

| Address $^{\text{Note 2}} \rightarrow$ Data output delay time | tdad         | tacc        | During program read cycle              | 2     |      |      | μs   |

| Address $^{\text{Note 2}} \rightarrow$ Data output hold time  | <b>t</b> had | tон         | During program resd cycle              | 0     |      | 130  | ns   |

| MD3 hold time (from MD0 <sup>↑</sup> )                        | tмзнк        | _           | During program read cycle              | 2     |      |      | μs   |

| MD3 $\downarrow \rightarrow$ data output float delay time     | <b>t</b> dfr | —           | During program read cycle              | 2     |      |      | μs   |

**Note 1.** Symbol of corresponding  $\mu$ PD27C256.

**2.** Internal address is incremented by 1 at the rising edge of the fourth X1 input. This address signal is not output to external pins.

20

# **Program Memory Write Timing**

# **Program Memory Read Timing**

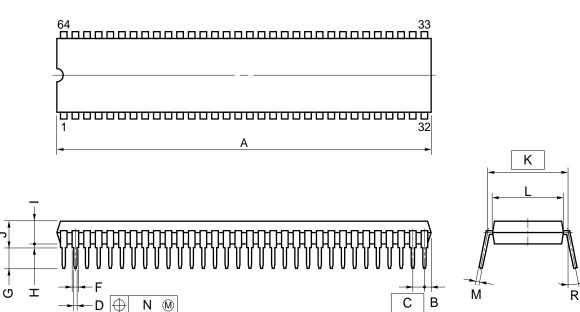

5. PACKAGE DRAWINGS

# 64 PIN PLASTIC SHRINK DIP (750 mil)

#### NOTE

- 1) Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| Α    | 58.68 MAX.             | 2.311 MAX.                |

| В    | 1.78 MAX.              | 0.070 MAX.                |

| С    | 1.778 (T.P.)           | 0.070 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 0.9 MIN.               | 0.035 MIN.                |

| G    | 3.2±0.3                | 0.126±0.012               |

| Н    | 0.51 MIN.              | 0.020 MIN.                |

| Ι    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.08 MAX.              | 0.200 MAX.                |

| К    | 19.05 (T.P.)           | 0.750 (T.P.)              |

| L    | 17.0                   | 0.669                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| Ν    | 0.17                   | 0.007                     |

| R    | 0~15°                  | 0~15°                     |

|      |                        |                           |

P64C-70-750A,C-1

# 6. RECOMMENDED SOLDERING CONDITIONS

The following conditions must be met when soldering this product.

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (IEI-1207).

Please consult with our sales offices in case other soldering process is used, or in case other soldering is done under different conditions.

#### Table 6-1 Type of Through Hole Device

#### $\mu$ PD75P216ACW: 64-pin plastic shrink DIP (750 mil)

| Soldering process                  | Soldering conditions                                                  |

|------------------------------------|-----------------------------------------------------------------------|

| Wave soldering<br>(only lead part) | Solder temperature: 260 °C or lower,<br>Flow time: 10 seconds or less |

| Partial heating method             | Pin temperature: 260 °C or lower,<br>Time: 10 seconds or less         |

# Caution This wave soldering should be applied only to lead part, and don't jet molten solder on the surface of package.

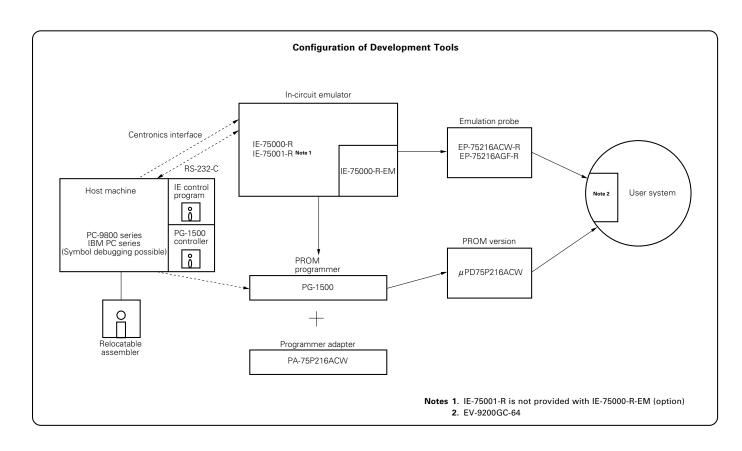

# ★ APPENDIX DEVELOPMENT TOOLS

The following development tools are provided for the development of a system which employs the  $\mu$ PD75P216A.

#### Language processor

| RA75X relocatable assembler | Host machine   |                          |                    | Part number |

|-----------------------------|----------------|--------------------------|--------------------|-------------|

|                             |                | OS                       | Distribution media |             |

|                             | PC-9800 series | MS-DOS™<br>∕ Ver. 3.10 ∖ | 3.5-inch 2HD       | μS5A13RA75X |

|                             |                | Ver. 3.30C               | 5-inch 2HD         | μS5A10RA75X |

|                             | IBM PC series  | PC DOS™<br>(Ver. 3.1)    | 5-inch 2HC         | μS7B10RA75X |

# PROM programming tools