# AN1139 APPLICATION NOTE

# L6254 - L6268 - L6269 12V DISK DRIVE POWER COMBO IC

by Carlo Vertemara

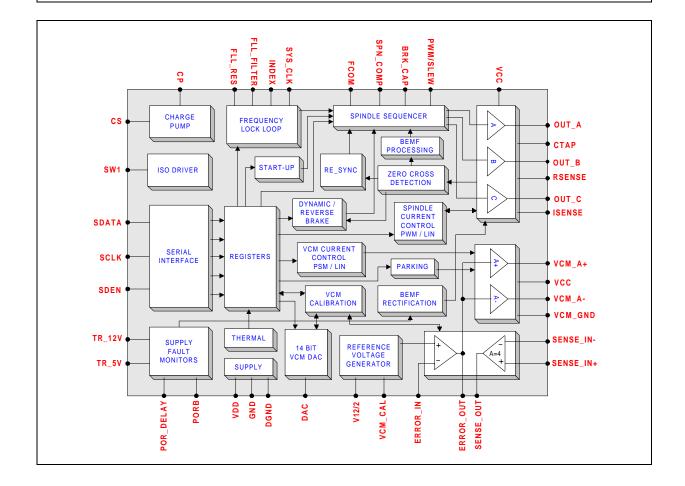

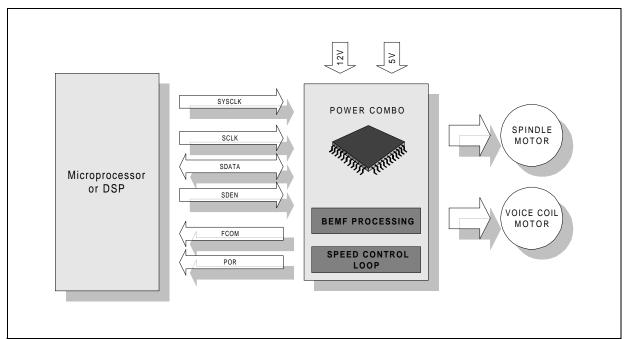

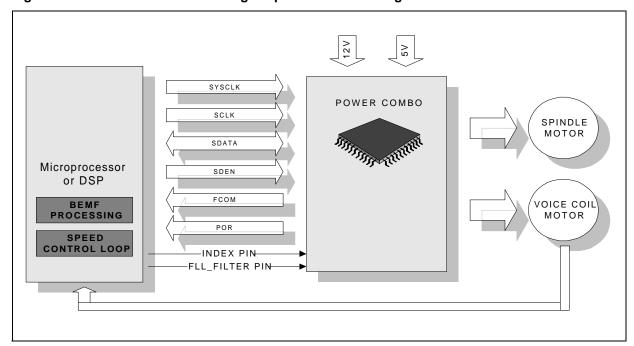

The Devices integrate into a single chip both SPINDLE and VCM controllers as well as power stages. The device is designed for 12V disk drive application requiring up to 2.0A of Spindle and 1.5 of Vcm peak current. A serial port with up to 25MHz capability provides easy interface to the microprocessor. A register controlled Frequency Locked Loop (FLL) allows flexibility in setting the Spindle Speed. Integrated BEMF processing, digital masking, digital commutation delay, and sequencing minimize the number of external components required. Power On Reset (POR) circuitry is included. Upon detection of a low voltage condition, POR is asserted, the internal registers are reset, and Spindle power circuitry is tri-stated. The BEMF is rectified providing power for the actuator retraction followed by dynamic Spindle braking. The device is built in BICMOS technology allowing dense digital / analog circuitry to be combined with a high power DMOS output stage. Minor differences characterize the three devices. The L6254 serial interface lines SDEN, SCLK and SDATA are 5V compatible. The L6268 and L6269 serial interface lines are 3.3V compatible. The L6268 is also provided with a slug mounted on the back of the package to improve power dissipation.

May 1999 1/64

# **INDEX OF CHAPTERS**

| Chapter 1.0                                                                                            | FEATURES                                                                                                                                                                                                                                              | 6                                                  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Chapter 2.0                                                                                            | D: AUXILIARY CIRCUITS                                                                                                                                                                                                                                 | 7                                                  |

| <b>2.2</b> TH                                                                                          | JPPLY MONITORS AND POWER-ON RESET                                                                                                                                                                                                                     | 7                                                  |

| Chapter 3.0                                                                                            | 9: SERIAL INTERFACE CIRCUITS                                                                                                                                                                                                                          | 8                                                  |

| <b>3.2</b> RE                                                                                          | ERIAL PORT EGISTERS MAP TATUS AND IDENTIFICATION REGISTERS                                                                                                                                                                                            | 9                                                  |

| Chapter 4.0                                                                                            | <b>):</b> SPINDLE CIRCUITS                                                                                                                                                                                                                            | 12                                                 |

| 4.1.1<br>4.1.2<br>4.1<br>4.1<br>4.1.3<br>4.1.4<br>4.2 BR<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3 CU<br>4.3.1 | Internal Start-Up External Start-Up  I.2.1 Align & Go I.2.2 Stepping I.2.3 Inductive Sense Resynchronization Motor Stuck RAKE Three Phase Brake Two Phase Brake Reverse Brake Reverse Brake JURRENT CONTROL Current Limitation Linear Current Control | 12<br>13<br>13<br>14<br>16<br>17<br>17<br>18<br>18 |

| 4.3<br>4.3                                                                                             | 3.2.1 Transconductance Loop Stability       2         3.2.2 Slew Rate Control       2                                                                                                                                                                 | 20<br>21                                           |

| 4.3<br>4.3<br>4.4 SP<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 BE<br>4.6 DE<br>4.7 FO<br>4.8 BE                | EMF DETECTION.  ELAY, COMMUTATION & MASK.  COM SIGNAL  EMF RECTIFICATION                                                                                                                                                                              | 22<br>23<br>23<br>23<br>26<br>27<br>27<br>27<br>29 |

| 4.10 E                                                                                                 | OWER STAGE       (3)         EXTERNAL ISOFET       (3)         EXTERNAL BEMF PROCESSING OPTION       (4)                                                                                                                                              | 30                                                 |

|                                                                                                        | XTERNAL SPEED CONTROL OPTION                                                                                                                                                                                                                          |                                                    |

# **AN1139 APPLICATION NOTE**

| Chapter 5.0: VOICE COIL CIRCUITS                                                                                                                                                                                                                                                                   | 1                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5.1 DESCRIPTION       3         5.2 CURRENT CONTROL       3         5.2.1 Linear Control Loop       3         5.2.2 PSM Control Loop       3         5.2.3 D/A converter       3         5.3 RETRACT       3         5.4 OFFSET CALIBRATION       3         5.5 POWER STAGE       3                | 11<br>13<br>13<br>14<br>15 |

| Chapter 6.0: APPLICATION & TOOLS                                                                                                                                                                                                                                                                   | 6                          |

| 6.1 APPLICATION CONFIGURATIONS       3         6.2 TYPICAL APPLICATION       3         6.3 SMART POWER DEVELOPMENT SYSTEM (SPDS)       3         6.3.1 SPDS Hardware       4         6.3.1.1 Interface Board       4         6.3.1.2 Application Board       4         6.3.2 SPDS Software       4 | 8<br>9<br>0<br>0           |

| Chapter 7.0: PACKAGE & THERMAL                                                                                                                                                                                                                                                                     | .4                         |

| 7.1 TQFP44 PACKAGE.       4         7.2 THERMAL CHARACTERISTICS       4         7.3 SLUG.       4                                                                                                                                                                                                  | 5                          |

| Chapter 8.0: APPENDIX                                                                                                                                                                                                                                                                              | 8                          |

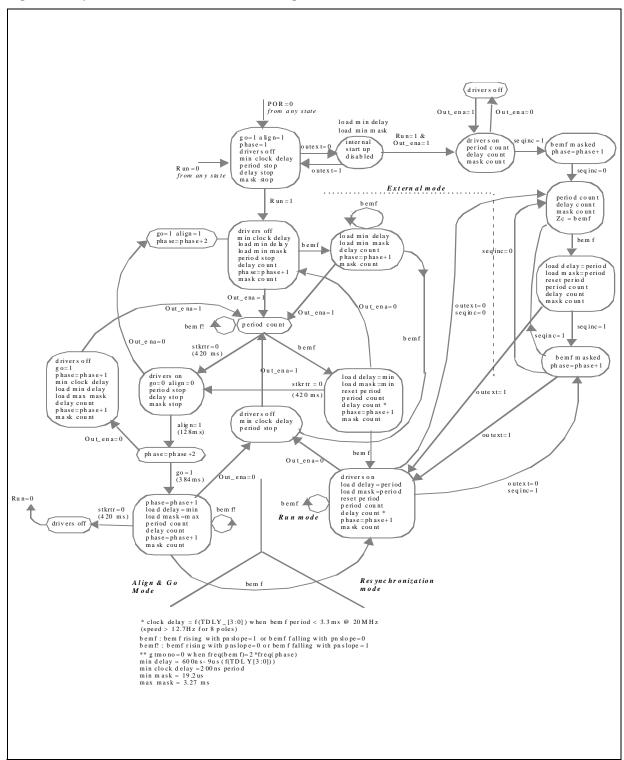

| 8.1 MODELS & MATHCAD ANALISYS       4         8.1.1 Spindle Current Control Loop       4         8.1.2 Spindle Speed Control Loop       5         8.1.3 Voice Coil Current Control Loop       5         8.2 STATE DIAGRAM       6         8.3 INDUCTIVE SENSE START-UP STEP BY STEP       6        | 8<br>2<br>6<br>0           |

# **INDEX OF FIGURES**

| Figure | 1: Serial Port Write Timing                                      | 8    |

|--------|------------------------------------------------------------------|------|

| Figure | 2: Serial Port Read Timing                                       | 8    |

| Figure | 3: INTERNAL ALIGN & GO AUTO START-UP PROFILE                     | .12  |

| Figure |                                                                  |      |

| Figure | 5: Resynchronization TiminG                                      | .16  |

| Figure |                                                                  |      |

| Figure | 7: Spindle Linear Current Loop Bode Diagram                      | .20  |

| Figure | 8: Spindle Pwm Current Control Loop                              | .22  |

| Figure | <b>9:</b> FLL Counters                                           | .24  |

| Figure | <b>10:</b> FLL LOOP                                              |      |

| Figure | 11: BEMF AMPLIFIER                                               |      |

| Figure | 12: Internal Signals Timing                                      | .28  |

| Figure | 13: Voice Coil Linear Control Loop                               |      |

| _      | 14: Voice Coil Psm Control Loop                                  |      |

| Figure | 15: Voice Coil Psm Output Voltages & Current Signals             |      |

| Figure | <b>16:</b> Power Off Sequence                                    |      |

| Figure | 17: Voice Coil Offset Calibration                                |      |

| Figure | 18: Stand Alone Application Configuration                        |      |

| Figure | 19: External Bemf Processing Configuration                       |      |

| Figure | 20: External Speed Control Configuration                         | .37  |

|        | 21: External BEMF Processing & Speed Control Configuration       |      |

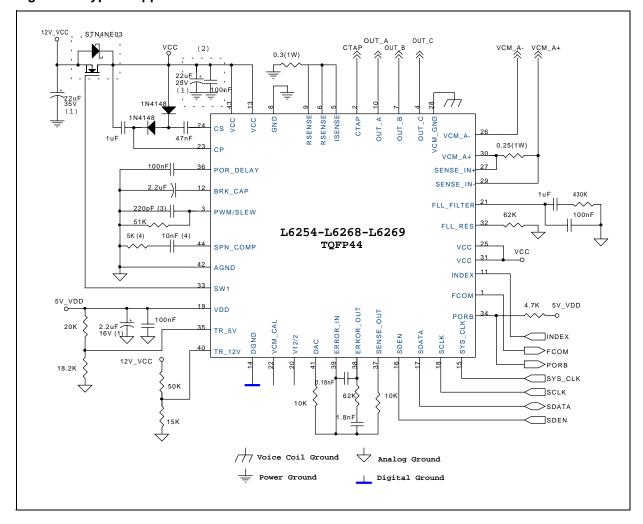

|        | 22: Typical Application Circuit                                  |      |

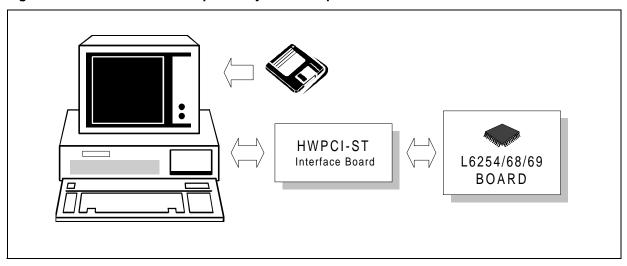

| Figure | 23: Smart Power Development System Setup                         | .40  |

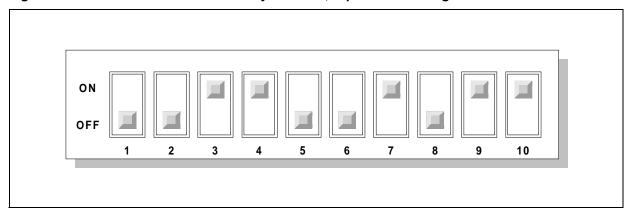

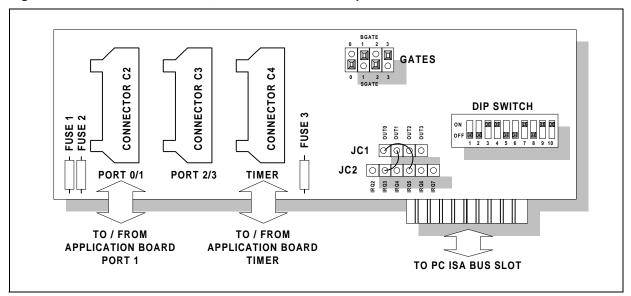

| Figure | 24: SPDS Interface Board Memory Address, Dip Switch Setting      | .40  |

| Figure | 25: SPDS Interface Board, Connectors And Jumpers Location        |      |

| Figure |                                                                  |      |

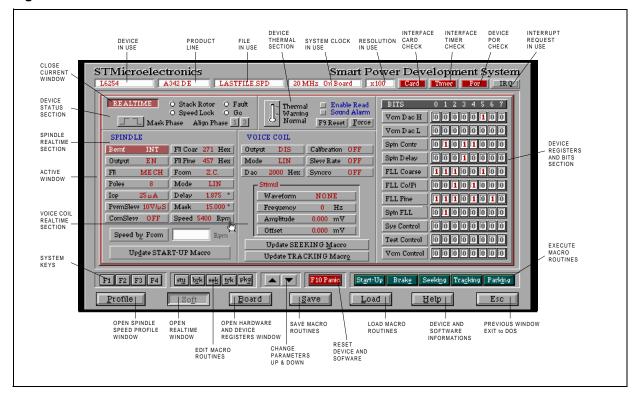

| _      | 27: SPDS Software Realtime Frame                                 |      |

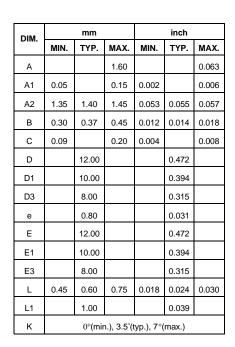

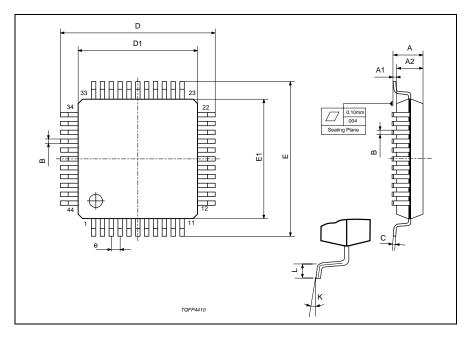

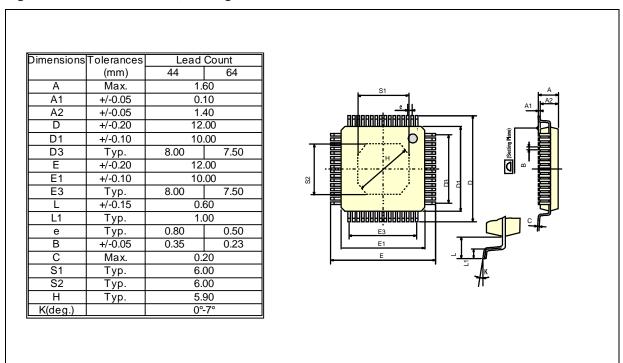

| _      | <b>28:</b> TQFP44 Dimensions                                     |      |

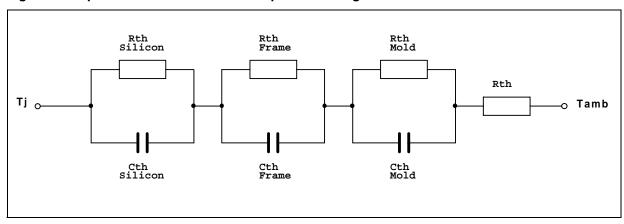

|        | 29: Equivalent Thermal Circuit Simplified Package                |      |

|        | <b>30:</b> TQFP with SLUG, Package Outline                       |      |

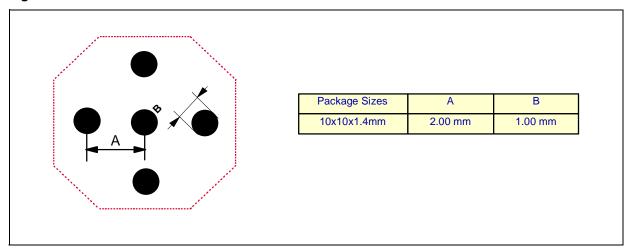

|        | 31: Raccomended Pattern for SLUG SOLDERING TO PCB                |      |

|        | 32: TQFP SLUG design                                             |      |

| Figure | 33: IC Temperature Increase                                      | .47  |

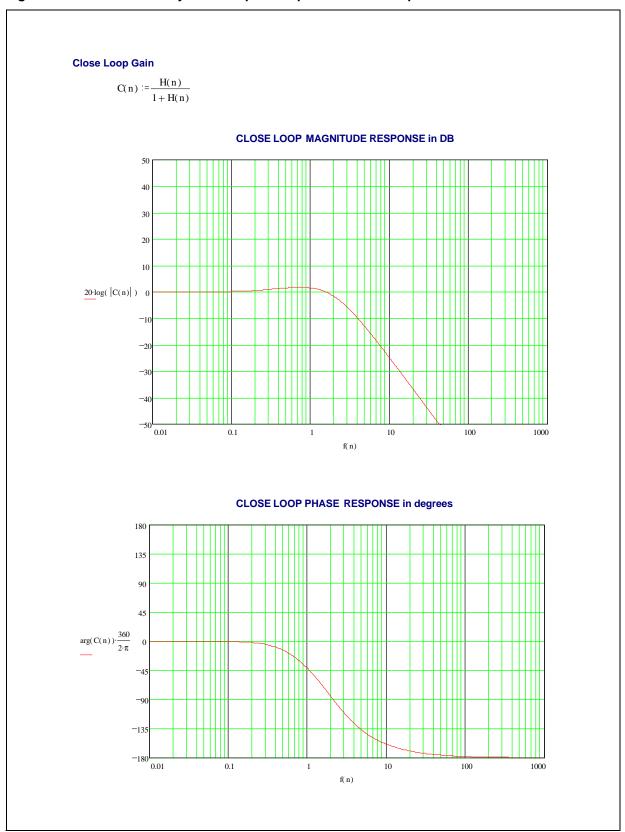

| _      | 34: Spindle Current Control Loop Model                           |      |

| Figure | <b>35a:</b> Mathcad Analisys of the Spindle Current Control Loop |      |

|        | 35b: Mathcad Analisys of the Spindle Current Control Loop        |      |

| _      | <b>35c:</b> Mathcad Analisys of the Spindle Current Control Loop |      |

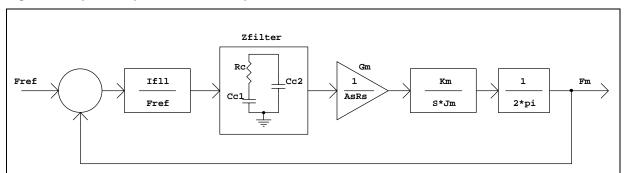

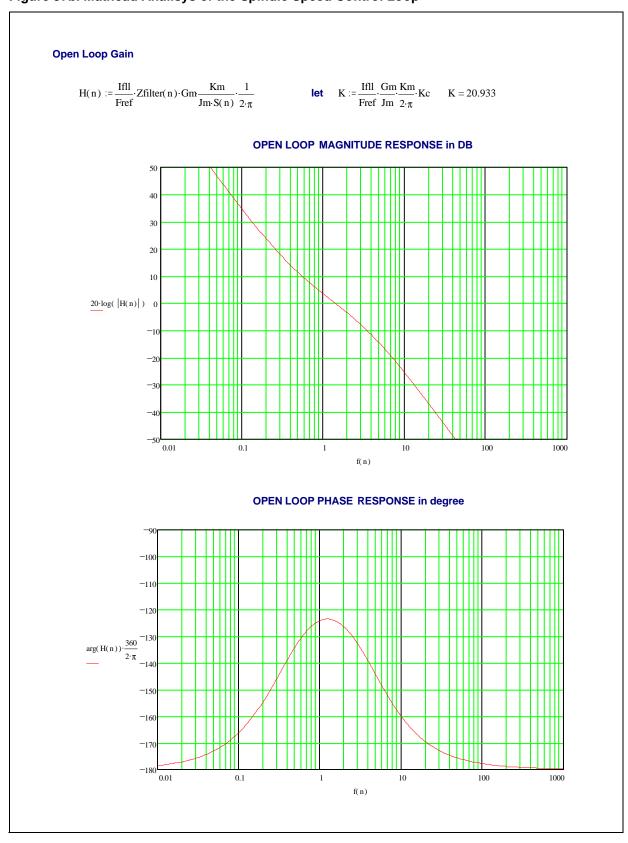

| Figure | <b>36:</b> Spindle Speed Control Loop                            |      |

| _      | 37a: Mathcad Analisys of the Spindle Speed Control Loop          | .53  |

| Figure |                                                                  |      |

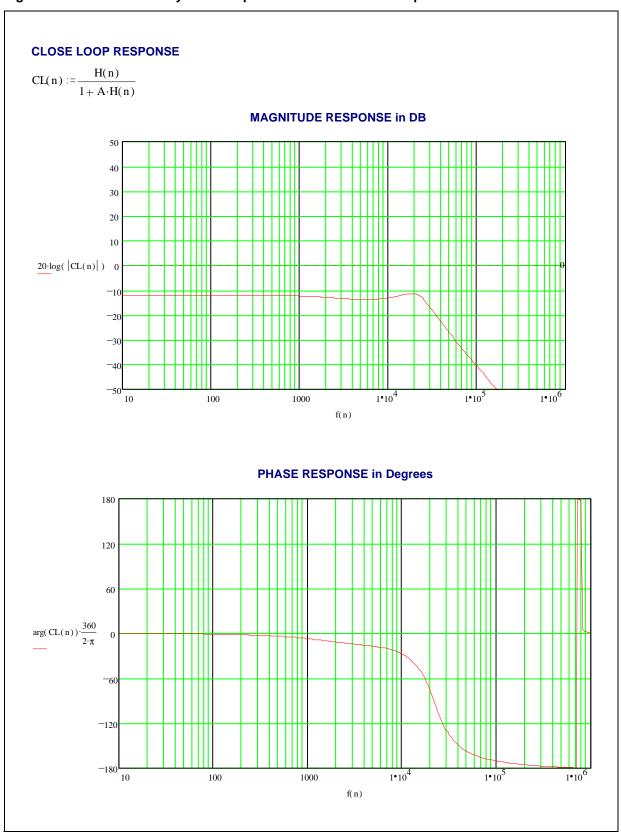

| Figure | 37c: Mathcad Analisys of the Spindle Speed Control Loop          | . 55 |

|        | 38: Voice Coil Current Control Loop Model                        |      |

| Figure | 39a: Mathcad Analisys of the Voice Coil Current Loop             |      |

| Figure | ·                                                                |      |

| Figure | <b>39c:</b> Mathcad Analisys of the Voice Coil Current Loop      | 59   |

|        | 40: Spindle Motor Controller State Diagram                       |      |

|        |                                                                  |      |

# **INDEX OF TABLES & EQUATIONS**

| Equation 1:         | POR Delay Capacitor (nF)                              | 7  |

|---------------------|-------------------------------------------------------|----|

| Table 1:            | Register Map                                          | 9  |

| Equation 2:         | Internal Start-Up Align Time - Ta (mS)                | 13 |

| Equation 3:         | Internal Start-Up Increment Time - Ti (mS)            | 13 |

| Table 2:            | Spindle Inductive Sense Current Limit                 | 14 |

| Equation 4:         | Spindle Inductive Sense Maximum Coil Current (Amp)    | 14 |

| Equation 5:         | Spindle Resyncronization Time - Tsync (mS)            | 16 |

| Equation 6:         | Spindle Motor Stuck Time - Tstuck (ms)                | 17 |

| Equation 7:         | Spindle Brake Capacitor (µF)                          | 17 |

| Table 3:            | Zero Crossing Time after reverse brake                | 18 |

| Table 4:            | Spindle Rsense Voltage Limit                          | 19 |

| Equation 8:         | Spindle Maximum Coil Current (Amp)                    | 19 |

| Equation 9:         | Spindle Output Slew Rate Resistror - Rslew $(\Omega)$ | 21 |

| Equation 10:        | Spindle PWM Constant OFF Time - Toff (µS)             | 22 |

| Table 5:            | Spindle PWM Minimum ON Time                           | 23 |

| Equation 11:        | FLL Coarse Counter                                    | 25 |

| Equation 12:        | FLL Fine Counter]                                     | 25 |

| Table 6:            | FCOM Output Signal                                    | 29 |

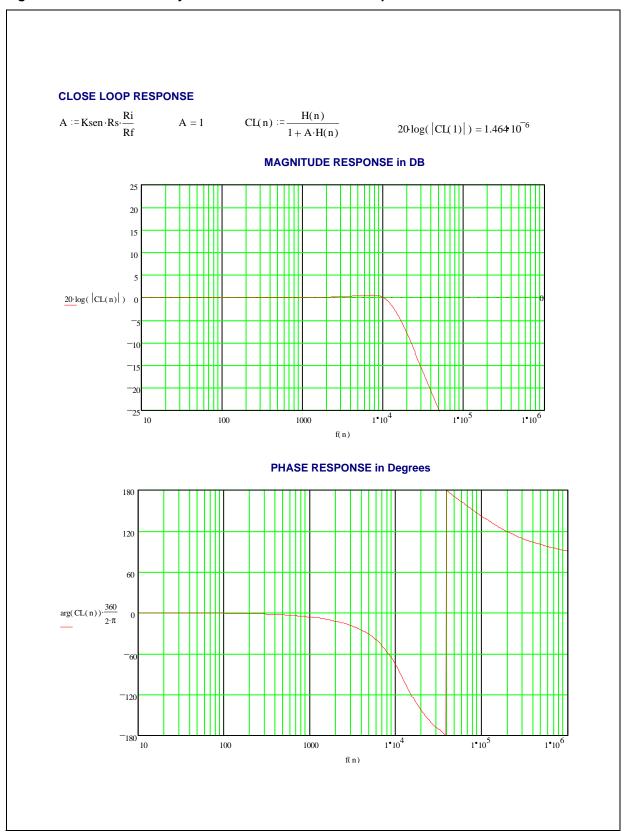

| Equation 13:        | VCM Loop Transfer Function                            | 32 |

| <b>Equation 14:</b> | VCM loop Bandwidth                                    | 32 |

| Equation 15:        | VCM loop low frequency gain                           | 32 |

| Table 7:            | VCM Retract Voltage 3                                 | 34 |

| Table 8:            | VCM Retract Time                                      | 34 |

| Equation 16:        | Junction Temperature                                  | 45 |

477

#### 1.0 FEATURES

- GENERAL

- 12V (+/- 10%) OPERATION.

- REGISTER BASED ARCHITECTURE

- MINIMUM EXTERNAL COMPONENTS

- BICMOS + VERTICAL DMOS TECHNOLOGY (1.5µm)

- VCM DRIVER

- 1.5A DRIVE CAPABILITY

- 0.9Ω TOTAL BRIDGE IMPEDANCE AT 25°C

- LINEAR MODE

- PHASE SHIFT MODULATION (PSM MODE)

- INSTANTANEOUS, (GLITCH FREE) SWITCH BETWEEN THE TWO MODES.

- CLASS AB OUTPUT DRIVERS

- ZERO CROSSOVER DISTORTION

- 14 BIT DAC DEFINE OUTPUT CURRENT

- SELECTABLE TRANSCONDUCTANCE

- 4 PROGRAMMABLE RETRACT VOLTAGE

- DYNAMIC BRAKE

- SPINDLE DRIVER

- 2.0A DRIVE CAPABILITY

- 0.8Ω TOTAL BRIDGE IMPEDANCE AT 25°C

- BEMF, INTERNAL / EXTERNAL, PROCESSING, SENSOR-LESS MOTOR COMMUTATION

- PROGRAMMABLE COMMUTATION DELAY

- LINEAR MODE AND CONSTANT TOFF PWM OPERATION MODE

- INTERNAL FREQUENCY LOCKED LOOP SPEED CONTROL (FLL)

- BEMF RECTIFICATION DURING RETRACT

- RESYNCHRONIZATION

- BUILT-IN ALIGN & GO START UP

- INDUCTIVE SENSE START UP OPTION

- DYNAMIC & REVERSE BRAKE

- PROGRAMMABLE OUTPUT SLEW RATE

- OTHER FUNCTIONS

- 12V, 5V MONITORING WITH EXTERNAL SET TRIP POINTS AND HYSTERESIS

- POWER UP/DOWN SEQUENCING

- LOW VOLTAGE SENSE

- 3.3V INPUT LOGIC COMPATIBILITY (ONLY L6268 AND L6269)

- SLUG FOR POWER DISSIPATION (ONLY L6268)

- THERMAL SHUTDOWN AND PRE-THERMAL WARNING

#### 2.0 AUXILIARY CIRCUITS

#### 2.1 SUPPLY MONITORS AND POWER-ON RESET

The two power supply monitor pins, TR\_5V pin #35 and TR\_12V pin #40, independently monitor the VDD and main supply VCC by means of external resistor dividers. The threshold of the comparators is set internally by the band-gap reference (2V) and hysteresis is 100mV. The ratio of the external resistors set the rising trip point. At Power-Up, PORB output pin (#34) remain low until the POR delay capacitor at POR\_DELAY pin (#36) is charged. It goes low whenever either monitor input goes below the threshold . If power returns to normal during a retract sequence, the retract will finish before the POR delay can begin, which means that the PORB (pin #34) output will remain low until the end of the retract plus the PORB delay time. For POR\_delay, the charge current is  $2\mu$ A and the threshold is 3V. POR delay capacitor is calculated as follow:

• 1.

$$\frac{\text{Time}}{1.5 \times 10^6}$$

POR Delay Capacitor (nF)

Example with Por Delay Time=150milli seconds : Capacitor

$$=\frac{150\times10^{-3}}{1.5\times10^6}=100\,\text{nF}$$

.

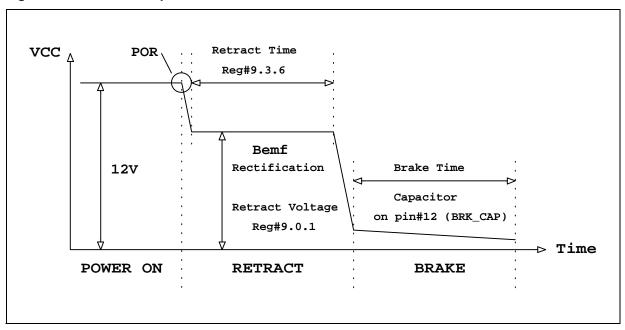

The bits required for VCM parking are not reset by PORB and they must be always written (Reg #5.3, Reg #8.2 and Reg #9.0.1.3.6). All the other bits are reset whenever PORB is low. As long as PORB is low the Spindle outputs are in brake by means of turning on the Low Side Dmos. In case of Power Down with the Spindle previously spinning, at the falling edge of PORB, the Spindle outputs tristate for BEMF rectification and the Voice Coil initiate the retract phase according to the time and voltage set. After the retract time, the Spindle outputs brake. The complete Power Off Sequence is depicted in Figure #16 in chapter 5 (Voice Coil Circuit), section 5.3 (Retract).

#### 2.2 THERMAL WARNING / SHUTDOWN

The Thermal Warning/Shutdown circuit senses the temperature of the die. When the temperature reaches the thermal warning threshold, the "THERMAL\_WARN" bit will be reset (=0). If the temperature rises to 25°C higher than the thermal warning threshold, then "THERMAL" bit will be reset (=0). At this time, the Spindle outputs are tristated and Voice Coil will retract. After retract, also Voice Coil outputs will be tristated. The registers are not reset by Thermal Shutdown. The Spindle and VCM will be tristated as long as the internal Thermal Shutdown signal is active. To release this signal, the die temperature has to decrease and RUN bit (Reg #2.3) or VCM\_EN bit (Reg #9.5) has to be toggled.

The "THERMAL" has approximately 60°C of hysteresis, so that the "THERMAL" bit will not return to normal until the chip has cool to 60°C below the rising "THERMAL" trip point. ("THERMAL" and "THERMAL\_WARN" are in Reg #7.0.1).

## 2.3 CHARGE-PUMP

Two external pins (CP pin 23, CS pin 24) are used. A 47nF capacitor and a diode (in series) is connected between CP and CS. A storage capacitor is connected from CP to VCC (12V). Another diode is connected between VCC and the 47nF capacitor. The voltage at the CP pin is called Vboost. An internal oscillator is running at 200KHz. This can be checked at CS pin. The Vboost Voltage is typical VCC+5.7V. It is possible to stop the oscillator by setting the VB/DIS bit (Reg#10.7). However these are used mainly for testing purpose. The internal oscillator is not stopped by POR condition and it is keeping running for all the retract time as long as the VCC is greater than 2V. The current that CP pin requires is about 3mA with both Spindle and VCM in Linear mode operation and it is about 5mA with Spindle and VCM in PWM mode operation.

477

#### 3.0 SERIAL INTERFACE CIRCUITS

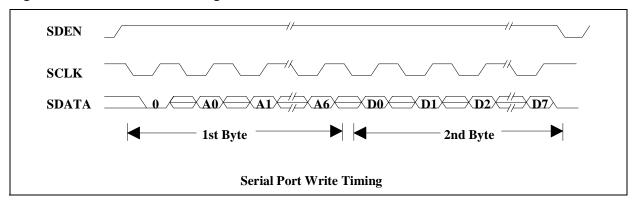

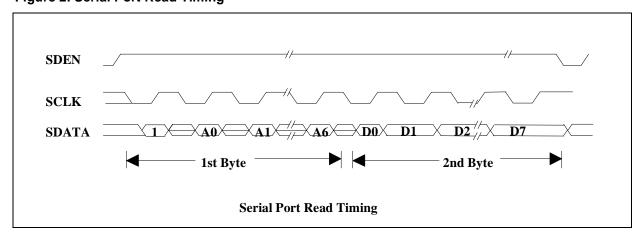

#### 3.1 SERIAL PORT

The serial port interface is used to program the internal registers in addition to interfacing with the status and ID registers. The serial port is enabled for data transfer when the Serial Data Enable pin (SDEN pin #16) is high (=1). SDEN must be asserted high prior to any transmission and it should remain high until the completion of the transfer. At the end of each transfer SDEN should be brought low (=0).

When SDEN is high, the data presented to the Serial Data pin (SDATA pin #17) will be latched on each rising edge of the Serial Clock pin (SCLK pin #18). Rising edges of SCLK should only occur when the desired bit of address or data is being presented on the serial data line. The data is latched into the internal register after the 16th rising edge of SCLK. Each transmission consists of a write control bit followed by a 7 bit address word and 8 bit data word. The address bits select the internal register to be written. The address and data fields are input LSB first, MSB last, where LSB is defined as bit zero. When the write control bit is "1", the contents of the read register that is being addressed will be shifted out on the SDATA pin LSB first (positive SCLK edge). The SDATA pin will switch from input (high Z) to driving output after the falling edge of the 8th SCLK pulse.

All write bits in the registers are reset whenever PORB is low except for Retract time Reg#9.3.6, Retract voltage Reg#9.0.1 and 2/3 Phase Braking Reg#5.3 (this last one only for L6254) which must be set or reset by the external controller soon after power-up to insure that the correct value will be programmed in case of a power down situation. Even though the Reg#8.2 bit is not used, it must be also reset (=0) by the external controller. The devices have different input threshold values, the L6254 is 5V compatible, the L6268 and L6269 are 3.3V compatible.

Figure 1. Serial Port Write Timing

Figure 2. Serial Port Read Timing

## 3.2 REGISTERS MAP

Table 1. Register Map

| Reg. | Description            | Bit 7        | Bit 6        | Bit 5          | Bit 4         | Bit3              | Bit 2           | Bit 1            | Bit 0         | Address         |

|------|------------------------|--------------|--------------|----------------|---------------|-------------------|-----------------|------------------|---------------|-----------------|

| 0    | VCM DAC<br>HIGH BYTE   | VCM<br>_CAL  | PSM/<br>LIN  | VDAC<br>BIT13  | VDAC<br>BIT12 | VDAC<br>BIT11     | VDAC<br>BIT10   | VDAC<br>BIT9     | VDAC<br>BIT8  | 0Eh<br>00001110 |

| 1    | VCM DAC<br>LOW BYTE    | VDAC<br>BIT7 | VDAC<br>BIT6 | VDAC<br>BIT5   | VDAC<br>BIT4  | VDAC<br>BIT3      | VDAC<br>BIT2    | VDAC<br>BIT1     | VDAC<br>BIT0  | 1Eh<br>00011110 |

| 2    | SPINDLE<br>CONTROL     | EXT/<br>INT  | PWM/<br>LIN  | MECH/<br>ELEC  | SPIN_E<br>N   | RUN               | R_SE<br>Q       | START<br>_UP     | INCRE<br>_SEQ | 2Eh<br>00101110 |

| 3    | SPINDLE<br>DELAY       | SD0          | SD1          | SD2            | SD3           | 8_12_<br>POLE     | MIN1            | MIN2             | MASK<br>_TIME | 3Eh<br>00111110 |

| 4    | FLL COARSE<br>COUNTER  | C11          | C10          | C9             | C8            | C7                | C6              | C5               | C4            | 4Eh<br>01001110 |

| 5    | COARSE/FINE<br>COUNTER | C3           | C2           | C1             | C0            | (*) 2/3_<br>PHASE | F10             | F9               | F8            | 5Eh<br>01011110 |

| 6    | FLL FINE<br>COUNTER    | F7           | F6           | F5             | F4            | F3                | F2              | F1               | F0            | 6Eh<br>01101110 |

| 7    | SPINDLE<br>STATUS      | GO           | ALIGN        | ERROR<br>_LOCK | MASK<br>_TIME | FAULT             | ROTOR_<br>STUCK | THERMAL<br>_WARN | THERMAL       | 7Fh<br>01111111 |

| 8    | SPINDLE FLL            | СРН          | CPL          | IL0            | IL1           | ISNS              | SET 0           | ICP              | SSLEW         | 8Eh<br>10001110 |

| 9    | SYSTEM<br>CONTROL      | RETRACT      | RT1          | VCM_EN         | DOUBLE        | RT0               | VR              | PKV_2            | PKV_1         | 9Eh<br>10011110 |

| 10   | TEST<br>CONTROL        | VB/DIS       | SET 0        | REV_<br>BRAKE  | FLL_OUT       | SET 0             | SET 0           | SET 0            | SET 0         | AEh<br>10101110 |

| 11   | VCM<br>CONTROL         | SET 0        | SET 0        | SET 0          | SET 0         | COM<br>SLEW       | SLEEP           | VCMH             | VCMS          | BEh<br>10111110 |

| 12   | CHIP ID                | ID_<br>REV_7 | ID_<br>REV_6 | ID_<br>REV_5   | ID_<br>REV_4  | ID_<br>REV_3      | ID_<br>REV_2    | ID_<br>REV_1     | ID_<br>REV_0  | FFh<br>11111111 |

Reg#0: Bit0~Bit5, D8~D13 of VCM DAC

Bit6, "1" VCM PSM mode, "0" VCM Linear mode

Bit7, "1" VCM calibration

Reg#1: Bit0~Bit7, D0~D7 of VCM DAC

Reg#2: Bit0, "0" to "1" transition increments Spindle sequencer

Bit1, "1" Spindle Internal Align & Go Start-Up, "0" Spindle External Start-Up

Bit2, "1" Resets Spindle sequencer to phase 1 (A -B)

Bit3, "1" Starts Spindle Align & Go Start-Up, "0" Resets control logic and brakes the Spindle

Bit4, "1" Enables Spindle outputs, "0" disables Spindle outputs

Bit5, "1" Electrical cycle for Spindle FLL control, "0" Mechanical cycle for FLL control

Bit6, "1" Spindle PWM mode, "0" Spindle Linear mode

Bit7, "1" External Spindle loop feedback (via Index pin), "0" Internal Spindle Loop feedback

Reg#3: Bit0, "1" 7.5° Spindle Mask time, "0" 15° Spindle Mask time

#### **AN1139 APPLICATION NOTE**

Bit1~Bit2, Spindle PWM mode Minimum ON time

Bit3, "1" 8 pole Spindle motor, "0" 12 pole Spindle motor

Bit4~Bit7, Spindle Commutation Delay control SD0....SD3

Reg#4: Bit0~Bit7, Spindle FLL coarse counter C4...C11

Rea#5: Bit0~Bit2, Spindle FLL fine counter F8...F10

Bit3, "1" Spindle Two phase brake ((\*)only L6254), "0" Spindle Three phase brake

Bit4~Bit7, Spindle FLL coarse counter C0...C3

Reg#6: Bit0~Bit7, Spindle FLL fine counter F0...F7

# Reg#7: Read Only Register

Bit0, "0" Thermal Shutdown ( >= 160°C)

Bit1, "0" Thermal Warning (>= 125°C)

Bit2, "0" Spindle Bemf not detected

Bit3, "1" Rapid deceleration of the Spindle motor or High frequency on FCOM signal.

Bit4, Spindle Mask time signal, "0" Spindle bemf is masked

Bit5, "0" Spindle speed lock error (>16μS/sample)

Bit6, "0" Spindle is in the Internal Start-Up ALIGN Phase

Bit7, "0" Spindle is in the Internal Start-Up GO Phase

# Reg#8: Bit0, Spindle PWM (chopping) slew rate, "1" 20V/μS, "0" 10V/μS

Bit1, Charge pump current in Spindle FLL loop, "1" 25μA, "0" 100μA

Bit3, "1" Presets Spindle inductive sense start-up circuits

Bit4~Bit5, Spindle start-up current limitation

Bit6, "1" Forces Spindle FLL charge pump low

Bit7, "1" Forces Spindle FLL charge pump high

#### Rea#9: Bit0~Bit1, VCM retract voltage

Bit2, "1" Connects the voltage reference (2V) for VCM calibration

Bit3~Bit6, VCM retract time

Bit4, "1" Doubles the times for the internal Spindle Align and Go Start-Up

Bit5, "1" Enables VCM

Bit7, "1" Initiates the VCM retract

# Reg#10: Bit4, "1" Spindle Mechanical or Electrical output, "0" Spindle Zero cross output

Bit5, "1" Spindle reverse brake

Bit7, "1" Disables Vboost

# **Rea#11:** Bit0, VCM PSM (chopping) Slew Rate, "1" $20V/\mu S$ , "0" $10V/\mu S$

Bit1, "1" Forces VCM outputs to be high in PSM mode

Bit2, "1" Unused (Future Power saving mode)

Bit3, "1" Spindle PWM (phase commutation) slew rate "1" 2V/μS, "0" 30V/μS

#### Reg#12: Read Only Register

Bit0~Bit7, for chip ID

# 3.3 STATUS AND IDENTIFICATION REGISTERS

The Status register (Reg#7) and the Identification register (Reg#12) are READ only registers, while all the others are only WRITE registers. The **Status register** provides informations of the Spindle motor (Bits 2...7) and the Thermal behaviour of the device (Bits 1,2).

■ **THERMAL** - Bit #0. Normally is set to 1, when the Junction temperature reaches about 160°C, the bit will be set to 0. This will automatically tristate the Spindle outputs and the Voice Coil will initiate the

retract. The bit will return to normal when the temperature will drop about 60°C. All the functions of the device but the reading in the serial port, will be in stand-by as long as this bit is set to 0.

- THERMAL\_WARN Bit #1. Normally is set to 1, when the Junction temperature reaches about 125°C, the bit will be set to 0. The device will take no action upon this bit set to 0. Corrections are demanded to the μP. This bit will return automatically to normal (=1) when the temperature will drop below the set point (about 125°C).

- ROTOR\_STUCK Bit #2. Normally is set to 1, if the Spindle BEMF is not detected, the bit will be set to 0. This can happen for example during Start-Up because the Spindle motor may be Stucked. The device will tristate the Spindle and VCM outputs upon this bit is set to 0.

- **FAULT** Bit #3. Normally is set to 0, if the Spindle motor decelerate rapidly or the FCOM signal change to high frequency, the bit will be set to 1. The device will take no action upon this bit set to 0. Corrections are demanded to the μP.

- MASK\_TIME Bit #4. By reading continuously this bit, the internal BEMF mask time signal can be monitored. When the bit is 0, the BEMF is masked.

- ERROR\_LOCK Bit #5. When the Spindle speed is at target speed +/- 16µS sample, the bit will be set to 1, otherwise will be set to 0.

- ALIGN Bit #6. Normally is set to 1, when the Spindle motor is in the ALIGN phase of the internal Align&GO start-up, the bit will be set to 0.

- GO Bit #7. Normally is set to 1, when the Spindle motor is in the GO phase of the internal Align&GO start-up, the bit will be set to 0.

By reading and decoding the Identification register, the revision of the Device can be retrieved.

#### 4.0 SPINDLE CIRCUITS

#### 4.1 START-UP DESCRIPTION

The spindle driver has the ability to stand alone start-up the motor using an internal "align & go" algorithm. Although the internal Start-Up will spin-up the motor consistently, the possibility exist where certain applications might require complete microprocessor control. In this case, the chip provides all the function and signals to externally build a custom Start-Up.

#### 4.1.1 Internal Start-Up

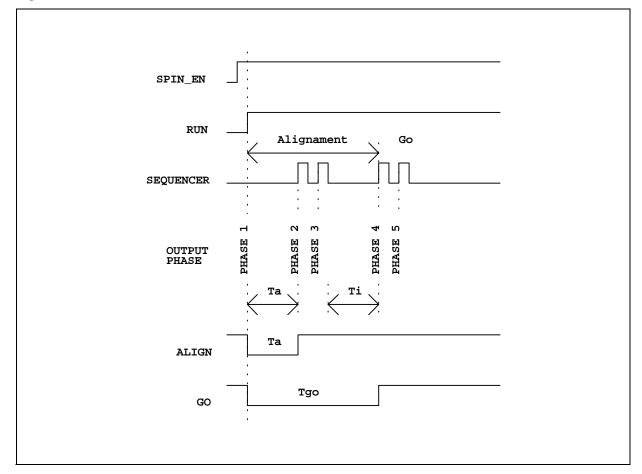

The Internal Start-Up is asserted by setting (=1) the START\_UP bit (Reg#2.1). Assuming that the motor is stationary, when RUN and SPIN\_EN bits (Reg#2.3.4) are set (=1), after a resynchronization time, the motor will be in Align mode with Phase 1 active (output A high and output B low. Please note that this output configuration is true at Power on condition or whenever reset sequencer is asserted, by toggling the R\_SEQ bit (Reg#2.2), otherwise can be different). After a **Ta** time (align time) the sequencer double increments the outputs to Phase 3 (output B high and output C low). After a **Ti** time (increment time) the sequencer double increments again the outputs and the controller enters the GO mode, with the sequencer automatically incrementing the output phase upon detection of the Motor's Bemf. The times labeled **Ta** and **Ti** are two delays that are 25% and 75% respectively of the total delay time and they are determined by the frequency of the system clock signal present on pin#15, (SYS\_CLK). By setting the DOUBLE bit (Reg#9.4), **Ta** and **Ti** can be doubled. **Ta** and **Ti** are calculated as formula #2 and #3. The Figure#3 depicts the internal Align & GO auto Start-Up profile.

Figure 3. INTERNAL ALIGN & GO AUTO START-UP PROFILE

•

$$2.\left(\frac{2.56\times10^6}{\text{Sys\_Clk}}\right)\cdot (1 + \text{DOUBLE})$$

Internal Start-Up Align Time - Ta (mS)

•

$$3.\left(\frac{7.68\times10^6}{\text{Sys\_Clk}}\right)\cdot (\text{1 + DOUBLE})$$

Internal Start-Up Increment Time - Ti (mS)

Example with 20MHz Sys\_Clk and DOUBLE=0:

$$Ta = \left(\frac{2.56 \times 10^6}{20 \times 10^6}\right) \cdot (1+0) = 128 \text{ms} - Ti = \left(\frac{7.68 \times 10^6}{20 \times 10^6}\right) \cdot (1+0) = 384 \text{ms}$$

# 4.1.2 External Start-Up

When the START\_UP bit (Reg#2.1) is reset (=0) the internal Auto-StartUp algorithm is disabled and the sequencer is accessible allowing the microprocessor to control the phase commutation of the motor. The chip offers this capability via the INCRE\_SEQ bit (Reg#2.0). The transition 0 to 1 of this bit increments the sequencer to the next position. A feedback from the motor (zero cross) is available on pin#1, FCOM. FCOM toggles at each successive zero crossing and it can be monitored to assure that motion occurred. With this approach the microprocessor or DSP can access all the function of the chip and different Start-Up algorithm can be applied to spin-up the motor. Following are three Start-Up algorithm examples: **Align & GO**, **Stepping** and **Inductive Sense**.

#### 4.1.2.1 Align & Go

The external Align & Go Start-Up is structured as the Internal one. The times Ta and Ti along with the commutation must be provided externally by the  $\mu P$  allowing further flexibility to the system. Assuming that the motor is stationary, when RUN and SPIN\_EN bits (Reg#2.3.4) are set (=1), the motor is in Align mode with Phase 1 active (output A high and output B low, please note that this output configuration is true at Power ON condition or whenever reset sequencer is asserted, by toggling the R\_SEQ bit (Reg#2.2), otherwise can be different). After a Ta time (align time handled by external  $\mu P$ ) the sequencer can be double incremented to Phase 3 (output B high and output C low) by toggling the INCRE\_SEQ bit (Reg#2.0). After a Ti time (increment time) the sequencer can be double incremented again which should produce torque in the desired direction. A little waiting time greater than the length of the Recirculation Spike produced by the motor coil during commutation (typical  $3\mu S$ ) must be applied prior the end-over operation. At this time, by setting the START\_UP bit (Reg#2.1), the sequencer is controlled by the BEMF zero crossing and the motor should ramp up to speed.

## 4.1.2.2 Stepping

This approach is driven in a similar fashion to a stepper motor. The START\_UP bit (Reg#2.1) must be reset (=0), RUN and SPIN\_EN bits (Reg#2.3.4) must be set=1 . By toggling the INCRE\_SEQ bit (Reg#2.0), the commutation rate is continually increased until the BEMF voltage is large enough to reliably use the zero-crossing for commutation timing. Once this point has been reached, a little waiting time greater than the length of the Recirculation Spike produced by the motor's coil during commutation (typical 3µS) must be applied. By setting the START\_UP bit (Reg#2.1), the BEMF zero crossing will automatically control the sequencer and the Motor Control circuit will take over to bring the motor into frequency lock. The Stepping approach takes longer than other Start-Up algorithm because the initial commutation frequency and subsequent ramp rate must be low enough so that the motor can follow without slipping. This implies that to have a reliable algorithm, the initial frequency and ramp must be carefully calculated according to the mechanical and electrical motor characteristics and under worst case conditions.

#### 4.1.2.3 Inductive Sense

Since hard drive heads are not designed for back rotation, it is important to know which Spindle phase should be energized first, in order to avoid back-rotation.

During operation, the electrical phase of the motor can be detected by sensing the BEMF induced in the unenergized winding by the rotor's magnet in motion, however, when the motor is stopped, detection of the rotor position is more difficult. For this purpose, the Inductive Sense algorithm has been developed. To get the position of a stopped three phase permanent magnet rotor, the inductance of each of the six motor commutation phases is sensed by applying a voltage across each combination of two motor winding and measuring the time required for the current through the windings to reach a certain arbitrary selected value. The shortest rise time should correspond to the lowest inductance and this commutation phase should be the one closest to the mechanical position of the rotor.

Altought no Inductive Sense algorithm is built inside the device, it provides all the hardware functions that interacting with the  $\mu P$  can externally perform the Inductive Sense Start-Up. The ISNS bit (Reg#8.3) must first be set (=1) in order to preset the internal circuit to sense the current in the coils. This allow the FCOM pin (#1) to become the information signal of threshold reached.

There are four different threshold values which adjust the maximum voltage on sense resistor. The threshold can be selected by changing the **IL0** and **IL1** bit in the Reg#8.4.5. The Table #2 shows the available values.

Table 2. Spindle Inductive Sense Current Limit

| "ILO" | "IL1" | "ISNS" | V_SENSE_LIMIT (+/- 15%) |

|-------|-------|--------|-------------------------|

| 0     | 0     | 1      | .15V                    |

| 1     | 0     | 1      | .20V                    |

| 0     | 1     | 1      | .25V                    |

| 1     | 1     | 1      | .30V                    |

The current that flow into the coil is also a function of the Sense resistor connected to the Rsense pin and it is calculated as follow:

Example with Rsense= $0.3\Omega$  and IL0/IL1/ISNS=1: Max Coil Current = (0.3 / 0.3) = 1 A.

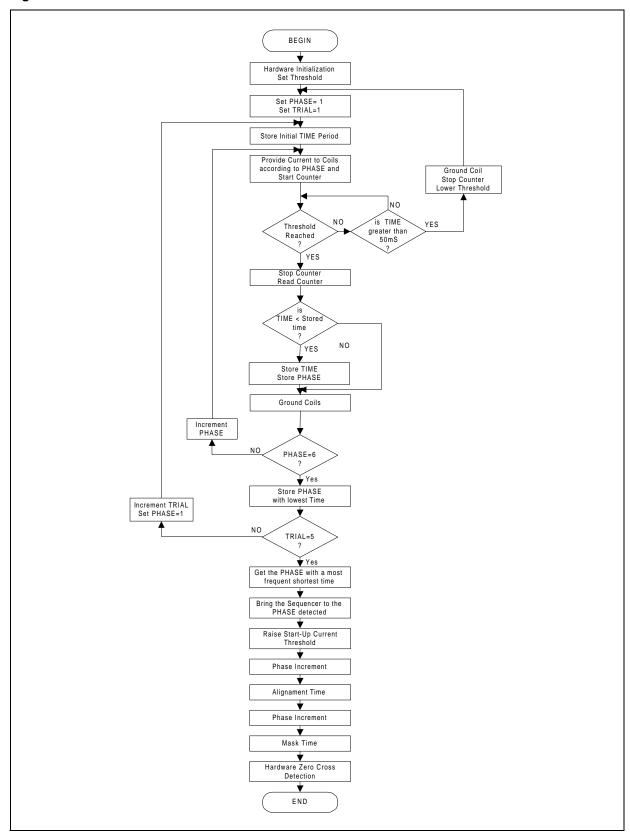

Figure#4 shows the flow chart of the Inductive sense Start-Up routine. A step by step procedure to build the Inductive sense Start-Up, can be found in chapter 8 (Appendix), section 8.3 (Inductive sense start-up step by step).

Figure 4. Inductive Sense Flow Chart

# 4.1.3 Resynchronization

The Resynchronization is the ability to spin-up the motor without going through the Start-Up routine when the Power is momentarily lost with the Motor still moving and BEMF is detected. Supposing that the Spindle is running at a certain speed, when a POR (Power On Reset) occurs, the spindle outputs are tristated and the motor will coast. If the Power come back, PORB high, the internal circuit will first check for the BEMF and if some consecutive zero cross are detected, the system will be able to resynchronize the sequencer and get the motor at speed again. Please note that when POR condition occurs, most of the internal registers are reset, for this reason, it is important to restore the desired bits value as fast as possible upon POR gets back. Also note that the PORB stays at low level until Por Delay time expire. The Spindle resynchronization circuit stand-by for the BEMF (zero cross transition) for a **Tsync** time, which it is calculated as follow:

• 5.

$$\frac{8.4 \times 10^6}{\text{SYS CLK}}$$

Spindle Resyncronization Time - Tsync (mS)

Example with 20MHz Sys\_Clk: Tsync=

$$\left(\frac{8.4 \times 10^6}{20 \times 10^6}\right)$$

= 420ms.

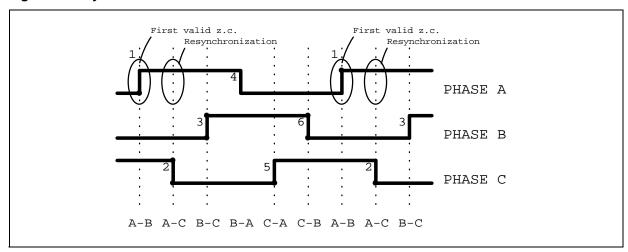

The number of consecutive Zero Cross that the chip needs to detect before resynchronizing depends from the instant that the system is activated (PORB High and REG#2.1.3.4 =1), after for example a glitch in the power supply. The first valid zero cross, as it is shown in Figure #5, is set in point #1 (Phase A-B, this is true right afer POR goes on or whenever R\_SEQ bit (Reg#2.2) is toggled). The points (Zero Crosses) between the system activation and the Resynchronization point (point #2) are the number of Zero Cross that the system has to detect, therefore the time before the resynchronization can initiate. If the motor is coasting and the chip is activated between point 1 and 2, the number of zero cross necessary will be 7. If the chip will be activated between point 6 and 1 the chip will resynchronize after two zero crosses. If the Spindle outputs are disabled by resetting (=0) the SPIN\_EN bit (Reg#2.4), while the motor was spinning, the system will keep track of the zero crosses and it will resynchronize at the next zero cross upon the SPIN\_EN bit is re-asserted.

Figure 5. Resynchronization TiminG

After START\_UP, RUN and SPIN\_EN bits are set (REG#2.1.3.4=1), the system is halted waiting for a zero cross to occur within a Tsync time as explained before. If not enough zero crosses are detected, after Tsync time, the internal Align&GO algorithm is initied. If another Start-Up is required (i.e. Inductive sense), it is mandatory to reset the SPIN\_EN bit before the end of the resynchronization time in order to avoid the internal Start-Up to be initiated. In other word, the external  $\mu P$ , in parallel with the chip, needs to keep track the time and

the BEMF (looking at FCOM pin (#1)) and take action whether internal or external Start-Up is to be initiated. If the motor is spinning and enough zero cross are detected, no actions are required, the chip sequencer will automatically lock on to the proper phase and bring the motor speed up to frequency lock.

#### 4.1.4 Motor Stuck

The purpose of this feature is to protect the motor and the circuits against an over-heating due to high current in the same phase when the motor is not moving. During Start-Up, when a phase is energized according to the sequencer in the GO phase, the current starts to flow into the motor winding producing a torque which should result a mechanical movement of the rotor to the next position. If for some reason the rotor does not move (not enough torque or the motor is stuck) and the BEMF is not detected within **Tstuck** time, the system will shut off the current in the Spindle tristating the outputs and the controller will enter the 'Stuck Rotor Hold' state. To resume from this condition, RUN bit (Reg#2,3) must be toggled. Following is the formula to calculate the Tstuck time.

• 6.

$$\frac{8.4 \times 10^6}{\text{Sys\_Clk}}$$

Spindle Motor Stuck Time - Tstuck (ms)

Example with 20MHz Sys\_Clk: Tstuck =

$$\left(\frac{8.4 \times 10^6}{20 \times 10^6}\right)$$

= 420 ms

The above description is valid always and not only at Start-Up. This means that the Stuck rotor counter is active all the time, also when the motor is running at steady speed. If for some reason, which it is, of coarse unlikely to happens (unless the speed gets extremely low such as 'Tzero\_cross > Tstuck'), the BEMF is not detected within Tstuck time, the Stuck rotor circuit will react as explained before. The Stuck Rotor information can be read as a '0' in the Reg#7.2.

#### 4.2 BRAKE

The Brake is the ability to completely stop a Spindle Motor in a reasonable time. There are two different way to stop the spindle motor, one is Commanded through the serial port and the other one is when the Power supply is turned off causing a POR condition. The device offers three different mode to brake, **Two phase brake** (only L6254), **Three phase brake** and **Reverse brake**. In a power-down condition only Two/Three phase brake are available.

#### 4.2.1 Three Phase Brake

This mode is selectable by re-setting (=0) the 2/3\_PHASE bit (Reg#5.3). The brake function is asserted by resetting (=0) the RUN bit (Reg#2.3) in power on condition and after retract in case of power loss. The low side output DMOS of phase A, B and C at this time are turned on. Since the 2/3\_PHASE bit (Reg#5.3) is not reset by POR, at power on, it is undefined, therefore it is mandatory to always write it.

In a power-down condition, after retract, when spindle brake initiate, the voltage on VCC drops very rapidly because the low side DMOS are turned on shorting the motor BEMF. In order to keep the spindle sink transistors ON in this mode, an external capacitor is used on the BRK\_CAP pin (#12) to hold the gates of the sink devices ON. This capacitor is charged up whenever VCC is high to about 5V, and it is isolated from all supplies by blocking diodes. Following is the formula to calculate Brake storage Capacitor where **Time** is the duration in seconds of the brake time required.

• 7.  $25 \times 10^{-8}$  · Time Spindle Brake Capacitor ( $\mu$ F)

Example with Brake Time=8 seconds : Brake Capcitor =  $(25 \times 10^{-8} \cdot 8) = 2 \mu F$ .

#### 4.2.2 Two Phase Brake

This mode is available only in the L6254 device. It works exactly like the Three phase brake and it is selectable by setting (=1) the 2/3\_PHASE bit (Reg#5.3). The difference, in this case is that only the phase A and B of the low side outputs DMOS are turned on, while the phase C is kept off.

## 4.2.3 Reverse Brake

It is available only when power is present (PORB=1). It is asserted by setting the REV\_BRAKE bit (Reg #10.5). At this time the current in the winding of the motor is reversed respect its previous flowing, resulting a rapid deceleration of the motor. The system will end over to the normal three/two phase brake (according to the Reg#5.3 bit value) as soon as the time between two zero cross is reaching a predefined value.

Three different values are available by toggling the REV\_BRAKE bit (Reg#10.5) according to the following table (#3).

Table 3. Zero Crossing Time after reverse brake

| Reg#10.5  | Zero Cross Time |

|-----------|-----------------|

| 1 Toggle  | 10ms            |

| 2 Toggles | 20ms            |

| 3 Toggles | 40ms            |

Since the saturation of the Powers are required to succeed the Reverse Brake operation, the above statement is valid if PWM Current Control mode is operating. In case of Linear Control Loop, a little trick needs to be used. Right before setting the REV\_BRAKE bit, the CPH bit (Reg#8.7) must be set (=1). This will disconnect the FLL loop from the Current control loop bringing quickly the low side DMOS to saturation.

#### 4.3 CURRENT CONTROL

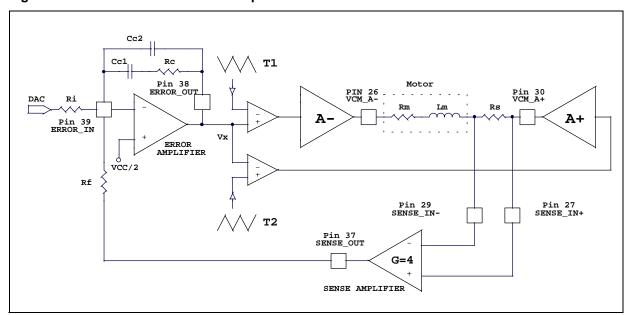

The current in the spindle motor is sensed by a small resistor (typ.  $0.3\Omega$ ) connected to the bottom of the H bridge and ground. The voltage drop across the resistor is amplified by a sense amplifier with a gain of four. The output voltage of the sense amplifier is sent to the Error Amplifier Stage where it is compared to the Current command coming from the FLL circuit. The Error Amplifier circuit will drive the power stage according to the driving mode selected. The device provides two different Current Control Loop, Linear and Pulse Width Modulation (PWM). By changing the Reg#2.6 bit, the selection of the two modes can be done any time regardless the motor is running or not.

# 4.3.1 Current Limitation

During initial Start-Up, the error signal from the output of the FLL will be at compliance in order to quickly bring the motor up to correct speed.

The maximum current flowing into the coil at the beginning (when the motor is stopped and no BEMF is present) is given by the following equation where RdsON is the ON resistance of the power DMOS.

Icoil = Vsupply / (2\*RdsON + Rmotor + Rsense )

The motor current during this condition can be safely limited to a predetermined value by setting the appropriate bits ILO and IL1 (Reg#8.4.5) according to the table #4.

**Table 4. Spindle Rsense Voltage Limit**

| "ILO" | "IL1" | V_SENSE_LIMIT (+/- 15%) |

|-------|-------|-------------------------|

| 0     | 0     | .45V                    |

| 1     | 0     | .50V                    |

| 0     | 1     | .55V                    |

| 1     | 1     | .75V                    |

The current flowing into the coil will be calculated as follow:

• 8. V\_sense\_limit | Spindle Maximum Coil Current (Amp)

Example with Rsense= $0.3\Omega$  and IL0/IL1=0 : Max Coil Current = (0.45 / 0.3) = 1.5 A.

# 4.3.2 Linear Current Control

The Linear mode of operation for the Spindle driver is activated by a "0" on bit 6 in the Spindle Control register Reg #2.6.

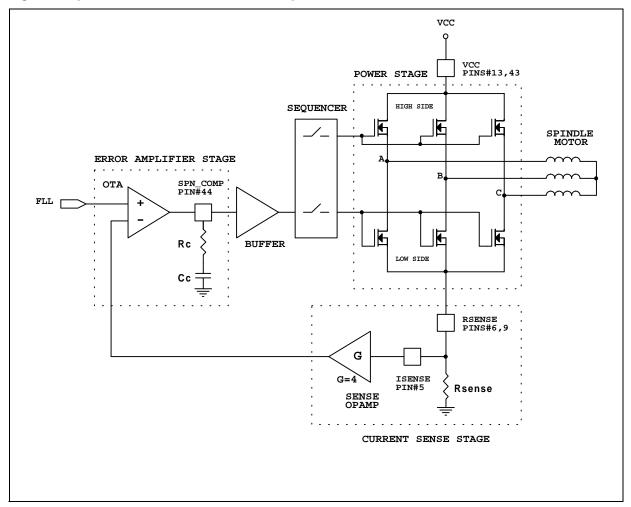

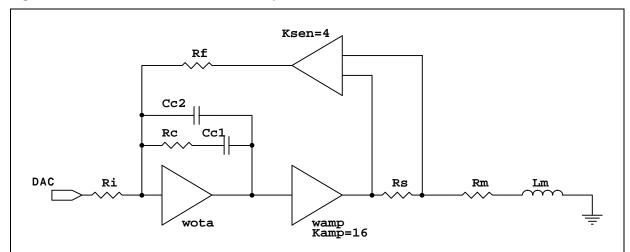

Figure 6. Spindle Linear Current Control Loop

The output current is controlled in a Linear fashion via a transconductance loop. Referring to Figure #6, the sourcing FET (High Side Dmos) of one phase is forced into full conduction, while the sinking FET (Low Side Dmos) of an appropriate phase operate as a transconductance element. During a run condition, the current in the sinking FET, is monitored by a RSENSE resistor. The resulting voltage that appears across the resistor is amplified by a factor of four by the sense amplifier opamp and is sent to the Error Amplifier Stage where it is compared to the Current command coming from the FLL circuit. The Error Amplifier circuit along with the Buffer, provides sufficient drive to the sinking FET in order to maintain the motor speed at the proper level as commanded by the Speed Controller (FLL).

#### 4.3.2.1 Transconductance Loop Stability

The RC network connected to the Compensation pin (SPIN\_COMP pin#44 - Figure #6) provides a single pole/zero compensation scheme. The pole/zero locations are adjusted such that a few dB (typ. 20dB) remains in the transconductance loop at frequencies higher than the zero. The inductive characteristic of the load provides the pole necessary for loop stability. Thus the loop bandwidth is actually limited by the motor itself.

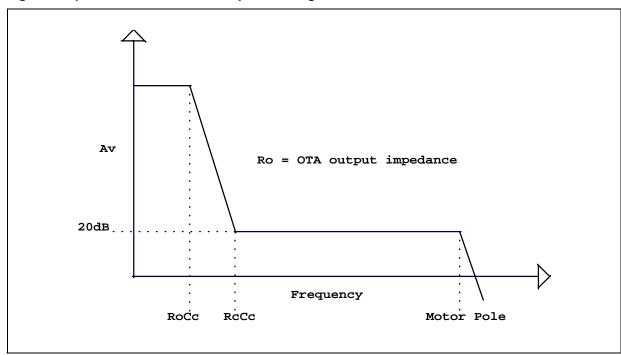

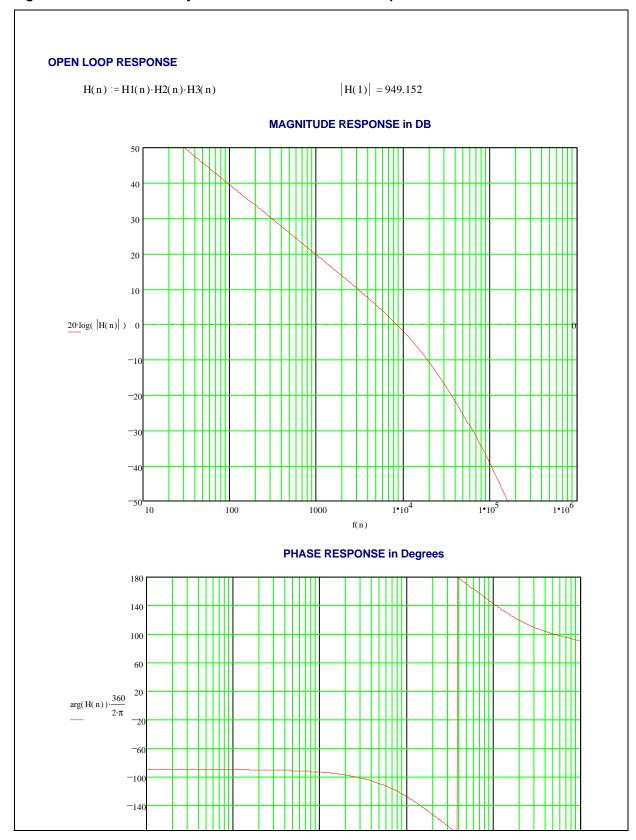

Figure 7. Spindle Linear Current Loop Bode Diagram

The Bode plot in Figure #7, depicts the normal way to achieve stability in the loop. The pole and the zero are used to set a gain of 20dB at a higher frequency and the pole of the motor cuts the gain to achieve stability.

Loop instability may be caused by two factor:

- 1) The motor pole is too close to zero. The zero is not able to decrement the shift of the phase, and when the effect of the motor pole is present, the phase shift may reach 180° and the loop will oscillate. To rectify this situation the pole/zero must be shifted at lower frequencies by increasing the compensation capacitor (Cc).

- 2) The motor capacitance itself can interfere with the loop, creating double poles. If the gain at higher frequencies is sufficiently high, the double pole slope of 40dB/decade can cause the phase shift to reach 180°, resulting in oscillation. By leaving the pole unchanged and increasing the zero, the stable response can be achieved. The Model and a Mathcad analysis for the Spindle Current Control Loop can be found in chapter 8 (Appendix), section 8.1.1 (Spindle Current Control loop).

#### 4.3.2.2 Slew Rate Control

A 3-phase motor appears as an inductive load to the power supply. The power supply sees a disturbance when one motor phase turns OFF and another turns ON because the DMOS turn-off time is much shorter than the L/R rise time. Furthermore, the turn-off of the DMOS can even cause current recirculation back into the supply. However, the need for a snubber circuit can be eliminated by controlling the turn-OFF time of the DMOS. The rate at which the upper and lower drivers turn ON and OFF is programmable via an external resistor, Rslew, connected to the PWM/SLEW pin (#3). This resistor define an internal current source that is utilized to limit the voltage slew rate at the outputs during transition, thus minimizing the load change that the power supply sees. To insure proper operation, the range of the resistor value indicated should not be exceeded.

If a relatively low value of Rslew is selected, the resultant fast Slew Rate will result in increasing commutation cross-over current, higher EMI and large amount of commutation current.

Higher values of Rslew result of course in slow Slew Rate at the outputs which is, under most conditions, the desired case since the problems associated with fast rates are reduced. The additional advantage is lower acoustical noise. Problems can occur though if the Slew Rate for a given application is too slow. The problem manifest itself as the motor begins to spin-up. At lower RPMs, the Bemf of the motor is relatively small resulting in higher amounts of commutation current. The excessively long Slew Rate may exceed the mask period and the commutation spike can be detected as a zero cross.

With a high value of Rslew, also the Power Dissipation needs to be considered. Following is the formula to calculate the intended Slew Rate Resistor in Linear mode.

• 9.

$$\frac{(3 \cdot 10 \times 10^4)}{\text{Slew Rate}}$$

Spindle Output Slew Rate Resistror - Rslew ( $\Omega$ )

Example for Slew Rate =

$$6V/\mu S$$

: Rslew =  $\frac{(3 \cdot 10 \times 10^4)}{6}$  =  $50 \text{K}\Omega$

#### 4.3.3 Pwm Current Control

The PWM mode of operation for the Spindle driver is activated by a "1" on the Spindle Control register Reg #2.6 bit.

In the switch mode current control operation, only the high side drivers are pulse width modulated to control the current in the motor. The low side drivers are fully switched ON or OFF according to their commutation sequence timing. The PWM control of the high side drivers is achieved by a constant TOFF single shot circuit. Constant TOFF control operates on the principle of monitoring the motor current and comparing it to a reference or control level (FLL). When the motor current reaches this commanded level, the output drivers turn OFF and remain OFF for a constant time. After this time the drivers turn back ON to repeat the cycle. Referring to Figure #8, the current in the motor windings is monitored via the voltage dropped in the sensing resistor, Rsense. This voltage is multiplied by a factor of four in the Current Sense Amplifier and sent to the negative input of a comparator. The control voltage (FLL), is applied to the positive input of the comparator. When the output of the Current Sense Amplifier reaches a level that is equal to the commanded level, the output of the comparator switches low resetting the Q output of the F/F.

This causes the upper driver to turn OFF and through -Q (which will go high) turn off the PMOS switch allowing the capacitor (Coff) to discharge through Roff, initiating then the Constant TOFF time.

When the voltage on Coff reaches 1.2V, the F/F will be set again causing the upper drive to turn ON and the Coff capacitor itself to be quickly recharged.

The Figure #8 shows the Current Control Loop in PWM mode.

VCC VCC PINS#13,43 POWER STAGE HIGH SIDE SECUENCER SPINDLE MOTOR COMPARATOR F/F FLL [ PMOS SWITCH s PWM/SLEW LOW SIDE Coff Roff RSENSE PINS#6,9 CONSTANT TOFF STAGE G TSENSE Rsense SENSE OPAMP CURRENT SENSE STAGE

Figure 8. Spindle Pwm Current Control Loop

#### 4.3.3.1 Constant OFF Time

The timing of the single shot circuit can be programmed by an external RC network at PWM/SLEW pin (#3). The constant OFF time can be calculated as follow:

• 10. 0.69 · Roff · Coff Spindle PWM Constant OFF Time - Toff (μS)

Example for Toff =  $10\mu S$  and Roff =  $100K\Omega$  (Typ.): Coff =  $\frac{10\times10^{-6}}{0.69}\cdot100\times10^{3}$  = 150pF.

# 4.3.3.2 Minimum ON Time

In a Spindle PWM current control system, the chopping in a commanded phase causes a swinging also in the floating phase. For this reason the BEMF zero cross signal is masked most of the time. The BEMF detection is possible by opening a small window in which the floating phase is monitored.

The window will be opened  $6.4\mu S$  (based on 20MHz SYS\_CLK) after the turn ON of the driver and it will be closed when the zero cross occurs or at the turn OFF of the driver. In the case of minimum ON time less than  $6.4\mu S$ , the window will be opened only at the point where the output is about to be turned OFF and then it will be closed right away.

Since the noise caused by the turning ON of the high side driver can be detected as a false zero cross, the

minimum ON time has to be chosen large enough to cover those spike. In the other hand has not to be too large otherwise the motor can not slow down fast when required or it may run at higher undesired speed. For this reason four different ON times value are available through the serial port, MIN1 and MIN2 bits (Reg#3.1.2), Those timing are not dependent from the external SYS\_CLK signal but are internally generated. The table #5 shows the timing available.

**Table 5. Spindle PWM Minimum ON Time**

| "MIN1" | "MIN2" | Minimum ON Time |

|--------|--------|-----------------|

| 0      | 0      | 5.9μS           |

| 0      | 1      | 1.4μS           |

| 1      | 0      | 12.0µS          |

| 1      | 1      | 5.21μS          |

#### 4.3.3.3 Slew Rate Control

In the PWM current control mode, two different slew rate control are present, the first one during commutation and the second one during chopping. Both are addressable through the serial port. The COMSLEW bit (Reg#11.3) will performs slew rate at commutation with '0' for  $30V/\mu S$  and '1' for  $2V/\mu S$ . The SSLEW bit (Reg#8.0) will perform slew rate during chopping with '0' for  $10V/\mu S$  and '1' for  $20V/\mu S$ .

#### 4.3.3.4 PWM Design Methodology

The bandwidth of the PWM loop was optimized to reject unwanted switching noise while providing sufficient response, commensurate with the switching speed of the output drivers. At higher frequencies the switching losses inherent in the drivers start to negate any of the power dissipation savings gained with PWM operation. At lower frequencies, less that 20KHz, the switching of the coil may result in the undesirable acoustic range. A good compromised PWM frequency can be assumed around:

# (1) Chopping Frequency: 30-40KHz.

The time that the current flowing into an inductor needs to reach a certain value is equal to a time that it needs to get from that value to zero. This time is depending from the Inductor (Lm) and the resistor (Rm) values. In the case of a running motor the BEMF generated by the motor itself at that speed needs to be taken in consideration. Due to the fact that BEMF is opposing to the power supply, the voltage across the motor will be less (Vmotor = Vpower-Bemf). For this reason the charging and discharging of the inductor will result with different voltage and so different duration. The ratio to have a good regulation margin will be about:

#### (2) Ton / Toff Ratio: TON = 70% - TOFF = 30%

The device architecture has been designed to work in constant OFF time mode, this means that the system is using the frequency (changing only the ON time) to adjust the speed. The ratio TON / TOFF provide the motor with the required amount of current to spin at desired speed.

Assuming that 40KHz chopping frequency is used, at steady speed, the period will be equal to  $25\mu$ S. For the previous assumption (2), the TOFF needs to be 30% of  $25\mu$ S so will be about 7.5 $\mu$ S. In this case the TON will be equal to 17.5 $\mu$ S (TON=Period -TOFF). If this Ratio can not be achieved, most probably the motor is not been designed to run at that speed (BEMF provided is too high).

#### 4.4 SPEED CONTROL (FLL)

The rotational position of the motor is inferred from the BEMF waveform generated by the floating coil. The chip uses the instant of a particular zero-crossing and the period between successive zero crossings to dictate the

477

commutation timings. The complete control loop is on chip and the speed is controlled by a reference clock at pin SYS\_CLK (pin#15).

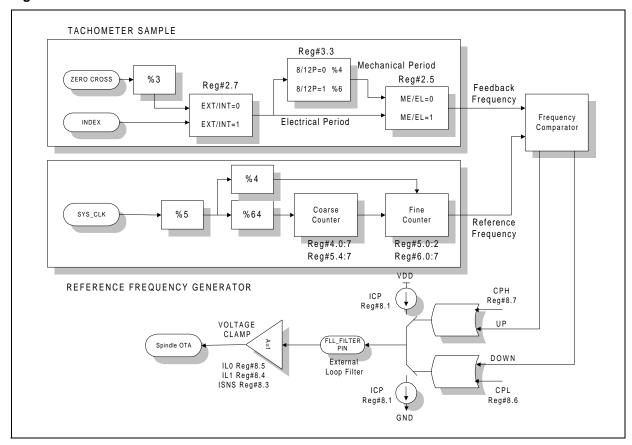

The speed control loop uses a frequency locked loop (FLL) which in conjunction with an external compensation network brings the frequency of the tachometer signal to be equal to the internally generated reference frequency. The tachometer signal can either be the BEMF signal divided down to a once per mechanical or electrical revolution signal or an externally generated tachometer signal, sector burst. The output of the speed control is a current demand signal that goes to the Spindle Driver.

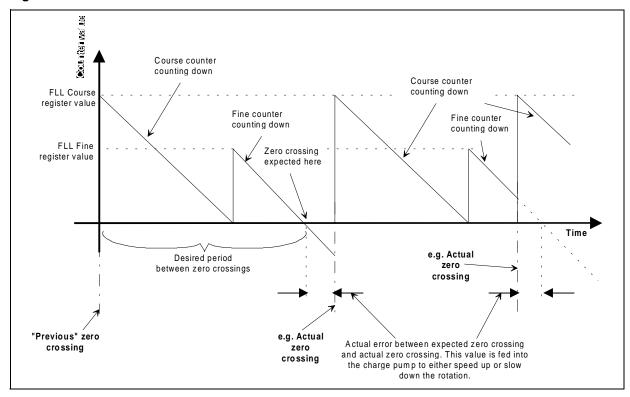

There are a "Fine" and a "Coarse" counters that define the speed of the motor. The register #4 and half of the #5 are the FLL Coarse Counter registers (12bits total, only count down to zero). The register #6 and the other half of the #5 are the FLL Fine Counter registers (11bits, count down to 2's complement of the 11 bit value). The figure #9 shows the counters.

In more detail, those three registers are used in conjunction with two down counters which form a frequency detector that in turn creates feedback through to a charge pump to maintain the motor's speed regulation. The frequency clock applied to SYS\_CLK pin is internally divided by a factor of 5.

The coarse counter is 12 bits and it is clocked at 1/64th the rate of the internal frequency clock. The fine counter is 11 bits and it is clocked at 1/4th the rate of the internal frequency clock. The on-chip Frequency Locked Loop uses the electrical or mechanical cycle pulses, according to the Reg#2.5 setting to adjust the speed of the motor. Upon the first pulse, the coarse register's contents (loaded via the serial port) is loaded into the internal coarse counter which immediately starts to count down. When this coarse counter reaches zero, the fine counter is then loaded from its corresponding register. The fine counter then also immediately starts to count down. The fine counter can count down through zero and continue counting down to the 2's complement of the original fine counter value.

The period between the start of the coarse counter and the zero crossing during the fine counter operation is

the programmed period. Any differences between the desired period and the pulse is the error in the transconductance loop and corrective action is taken by the charge pump.

The pulse measurement is initiated by an edge of the Feedback Frequency (Figure #10). If the feedback frequency is higher than the reference frequency, then a DOWN pulse will be generated whose width is the difference in pulse width of the two inputs. If the feedback frequency is lower than the reference frequency than an UP pulse will be generated whose width is the difference on pulse width of the inputs. The maximum pulse width of the frequency comparator is set by the value programmed into the fine counter. UP and DOWN pulses control the output of a current source or sink respectively which are connected to the FLL\_FILTER pin (#21). The current source and sink may also be turned on by the CPH and CPL bits in the serial port (Reg#8.6.7), however these are mainly for testing purpose. The value of the source and sink currents is set by the ICP bit (Reg#8.1) in the serial port. The result of this is a current pulse, whose width is proportional to the speed error, this is presented to the FLL\_FILTER pin which is used with an external RC network to construct the Loop Filter for the motor speed control. The FLL\_FILTER pin is also internally connected to the input of a unity gain buffer. The output of this buffer is clamped to a voltage set by ILO, IL1 and ISNS bits (Reg#8.3.4.5.) in the serial port. The value for the clamp voltage are outlined in tables #2 and #4.

The coarse and fine counter arrangement is guaranteed to work in all possible circumstances. For example if the zero crossing is within or outside the fine window or even if the zero crossing is in the coarse register range. This system will even work if the zero crossing occurs across multiple coarse/fine cycles. The FLL has a prescaler (defined by the System Control Register bits MEC/ELEC and 8\_12\_POLE (Reg#2.5 & Reg#3.3) that changes the cycle counting mechanism between electrical or mechanical (8 pole or 12 pole) i.e. dividing the electrical period clock by 1, 4 or 6.

The equation for setting the Coarse and Fine Counters are calculated as shown in formulas #11 and #12 where T0 is the period of the updating frequency that can be either electrical or mechanical and it is calculate as **T0 = 60 / Rpm \* Cycle**. **Cycle** is the cycle counting mechanism and as explained before it can be 1,4 or 6 according to desired cycle. Use 1 if Mechanical cycle is selected, use 4 or 6 if electrical cycle is chosen according to the motor pole. Conventionally, **90%** of T0 goes into the Coarse Counter, **10%** goes into the Fine Counter. **Rpm** is the desired speed.

The CoarseCounterPeriod is the time of one period of the Coarse Counter and it is equal to 1/Frequency(SYS\_CLK) \* 5 \* 64. The FineCounterPeriod is the time of one period of Fine Counter and it is equal to 1/Frequency(SYS\_CLK) \*5 \*4. The CoarseCounterError is the error from the Coarse Counter calculation and needs to be added to the FINE register calculation.

• 11. COARSE\_REG =

$$\frac{(0.9 \cdot T0)}{CoarseCounterPeriod}$$

FLL Coarse Counter

• 12. COARSE\_FREQ =

$$\frac{(0.1 \cdot T0) + CoarseCounterError}{FineCounterPeriod}$$

FLL Fine Counter]

Example whit a speed of 5400Rpm, Cycle=Mechanical and SYS\_CLK=20MHz.

1. Calculate T0 reference period.

$$T0 = 60 / (Speed*Cycle) = 60 / (5400 *1) = 11 mS$$

Calculate Coarse Counter Period.

CoarseCounterPeriod =

$$(1 / Frequency(SYS_CLK)) *5 * 64 = (1 / 20e6) * 5 * 64 = 16 \mu S$$

3. Calculate Fine Counter Period.

**FineCounterPeriod** =

$$(1 / Frequency(SYS_CLK)) *5 * 4 = (1 / 20e6) * 5 * 4 = 1 \mu S$$

4. Calculate Coarse Register value.

**COARSE\_REG** = (0.9 \* T0) / CoarseCounterPeriod = (0.9 \* 11e-3) / 16e-6 = **618.75**

The number 618 is the value that has to be programmed into the Coarse Counter Register. The decimal number 0.75 is the error that needs to be added to the computation of the Fine Register.

5. Calculate Coarse Counter Error.

CoarseCounterError =  $0.5 * CoarseCounterPeriod = 0.75 * 16e-6 = 12 \mu S$

6. Calculate Fine Register Value.

FINE\_REG = (0.1\*T0+CoarseCounterError) / CoarseCounterPeriod = (0.1\*11e-3+12e-6) / 1e-6 = 1112

The number 1112 is the value that has to be programmed into the Fine Counter Register.

Figure 10. FLL LOOP

Since the Coarse Counter is a 12 bit counter, the maximum count available is 4096. Therefore, from the above example, the full Coarse count set limit will be 65,536mS (4096\*CoarseCounterPeriod). The Fine Counter is only a 11 bit counter for a total of 2048 counts. The full Fine count set limit will be 2,048mS (2048\*FineCounter-Period). If a greater number will result from the calculation, the percentage of T0 used in the Fine Counter equation needs to be decreased and added to the Coarse Counter equations (for example, 91% of T0 goes into the Coarse Counter and 9% of T0 goes into the fine Counter). This procedure needs to be repeated until the number will fit the Fine Counter Register. Figure #10 depicts the complete FLL loop block diagram.

#### 4.4.1 Internal Frequency Feedback

The internal frequency for the Speed Loop Feedback is taken internally from the FCOM signal divided down by 3 and it is selectable by resetting (=0) the EXT/INT bit (Reg#2.7). The Figure#10 shows the configuration.

# 4.4.2 External Frequency Feedback

An INDEX pin (#11) is provided for external Speed Loop Feedback frequency. This pin will allow the user to control the motor speed with a signal taken from the data read off of the disk itself. This mode is selectable by setting (=1) the EXT/INT bit (Reg#2.7). The Figure#10 shows the configuration.

# 4.4.3 Speed Loop Compensation

The Frequency Comparator and Charge Pump generate and error current based on the frequency difference between a programmed reference frequency. This error current is converted to an error voltage by the loop filter, which programs the current delivered to the motor through the OTA loop. The Model and a Mathcad analysis for the Spindle Speed Control Loop can be found in chapter 8 (Appendix), section 8.1.2 (Spindle Speed Control loop).

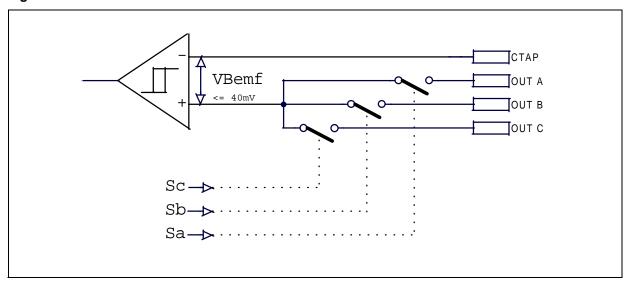

#### 4.5 BEMF DETECTION

Since no Hall Effect Sensors are required, the commutation information is derived from the BEMF voltage zero-crossing of the undriven phase with respect to the center tap. The Bemf comparator and associated signal levels are depicted in Figure #11. For reliable operation, the BEMF signal amplitude should be a minimum of +/- 40mV to be properly detected. In order to provide for noise immunity, internal hysteresis (typically 15mV) is incorporated in the detection circuitry to prevent false zero crossing detection.

Figure 11. BEMF AMPLIFIER

# 4.6 DELAY, COMMUTATION & MASK

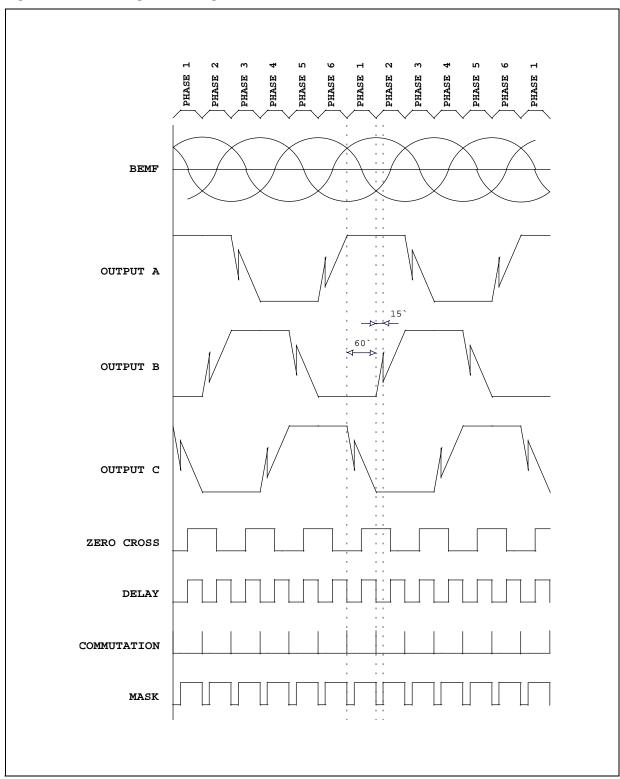

The Figure #12, represent the internal signal timing associated with the Motor Bemf and Output stage.

Figure 12. Internal Signals Timing

The BEMF waveform is shown as a reference along with a dashed line to indicate the occurrence of a zero crossing. A typical sequence starts when the outputs switch states. Referring to Figure #12, during Phase 1,

output A goes high, while output B is low. During this phase, output C is floating and the Bemf is monitored. The outputs remain in this state for 60 electrical degrees as indicated by the first set of dashed lines. After this period the output switches to phase 2 with output A high and C low with the Bemf amplifier monitoring output B.

In order to prevent commutation current noise being detected as a false zero crossing, a **Masking** circuit automatically blanks out all incoming signals as soon as a zero crossing is detected. When the next commutation occurs an internal counter starts counting down to set the time that the masking pulse remains. This time is equal to 7.5° or 15° of the electrical cycle and it can be programmed through the serial port by setting or resetting the Reg#3.0. Thus the actual masking period is the total of the time from the detected zero crossing to the commutation plus 12.5% (7.5°) or 25% (15°) of the previous period. The selection of the Mask has to be done in order to cover (as shown in Figure #12, between dashed lines) the spike produced by the commutation. This can be sperimentally achieved by looking with an oscilloscope the phase commutation Voltage during start-up (worse case condition due to high current). The time of the Mask signal has to be large enough to cover the duration of the commutation spike.

After the masking period, the Bemf voltage at output B is monitored for a zero crossing. Upon detection of the zero crossing the output is commutated after a **Delay** (in case of Figure #12, 30 electrical degrees) insuring maximum torque. The Delay can be programmed through the serial port by setting Reg#3.4:7 bits. The adjustment range is from 1.875 through 30 electrical degrees in 1.875 degree increments. The Delay has to be chosen in order to optimize the commutation point to insure maximum torque. This can be sperimentally achieved by looking with an oscilloscope the Voltage and the Current in a phase and adjusting the delay in order to have those waveforms as much symmetric as possible.

#### 4.7 FCOM SIGNAL

The FCOM signal available on pin#1 has two different functions. Normally when the motor is running it will provide feedback information of the rotor's position (Zero Crossing, Electrical or Mechanical). During Spindle Inductive sense Start-Up, it will provide informations whether the current threshold is reached or not. In this last case, if Spindle Linear current control is used the FCOM pin will start low and it will go high when the current in the sense resistor will reach the threshold set by IL0,IL1 and ISNS bits (Reg#8.3.4.5). The FCOM pin will stay high until the Spindle outputs are disabled then it will go low again. If Spindle PWM current control is used, the FCOM will behave like in Linear mode but instead to stay all the time high, it will start chopping with 50% duty cycle and the half period will be equal to the TOFF time set by the external components attached on PWM/ SLEW pin (#3). The FCOM pin will continue to chop until the Spindle outputs are disabled then it will go low. The table #6 shows the options of the FCOM output signal available by the combination of the ISNS (Reg#8.3), FLL\_OUT(Reg#10.4) and MECH/ELEC(Reg#2.5) bits.

**Table 6. FCOM Output Signal**

| ISNS | FLL_OUT | MECH/ELEC | FCOM SIGNAL                  |

|------|---------|-----------|------------------------------|

| 0    | 0       | 0         | Toggle every Zero Crossing   |

| 0    | 1       | 0         | Toggle every Mechanical turn |

| 0    | 1       | 1         | Toggle every Electrical turn |

| 1    | X       | Х         | Inductive Sense              |

#### 4.8 BEMF RECTIFICATION

In case of a power down, at the falling edge of the POR signal, the spindle outputs will be tristated and the retract sequence will initiate. The energy for the retract function in power down condition comes from the rectified BEMF of the motor acting as a generator on VCC. Because of the bottom spindle transistors are commutated in sync with the BEMF, the voltage on VCC is only one diode drop less than the BEMF voltage (the body diode of the top side spindle drivers).

#### 4.9 POWER STAGE

The Spindle Power driver consist of a 3 Phase H bridge power transistor. Both the low and the high side drivers are NMOS transistor. The drivers are built by a special low Rdson DMOS structure. The 12 volts power supply is connected to the H bridge via an external power NMOS device. The H bridge returns to ground through the sink pins and via an external resistor. An on chip Boost voltage generator is being used to switch the high side drivers and the external isolation NMOS as explained in chapter 2 (Auxiliary circuits), section 2.3 (Charge Pump).

#### 4.10 EXTERNAL ISOFET

An external NMOS device is used to connect the Power Supply to the Spindle and VCM high side Dmos. The meaning of this device is to isolate the Spindle and VCM power stage from the power supply during retract at Power Off. This will insure the Bemf voltage available from the Spindle motor to stay inside the chip and thus providing the necessary voltage to retract the Voice Coil. Without this device, the Bemf voltage will be discharged very fast through the power supply. The external Isofet is turned on upon the POR signal goes HIGH and is turned off when the POR signal goes low. The high voltage (~17V) to apply to the gate necessary to turn it on, it is provided by the charge pump circuit and it is available on SW1 pin (33). If no particular care is needed on the voltage drop of the external ISOFET, it can be substituted with a normal Schottky diode.

#### 4.11 EXTERNAL BEMF PROCESSING OPTION

The external Bemf processing is available by re-setting (=0) the Reg#2.1 bit. At this time the FCOM signal has to be monitored by the external  $\mu P$  as a zero crossing reference. Upon the transition of the FCOM signal, a sequencer commutation needs to be programmed after a delay calculated by the  $\mu P$  itself. The Delay has to be calculated as a percentage of the previous period (typical 30 electrical degree equal to half of the previous period). The Mask time like in internal Bemf processing is also calculated as a percentage of the previous period, but it is also performed by the high state of the commutation signal INCRE\_SEQ (Reg#2.0 bit). When the INCRE\_SEQ bit is set (=1) the bemf is masked. The actual mask time signal is a combination of the two. The Figure #19 in the chapter 6 (Application and Tools), section 6.1 (application configurations) depicts this feature.

# 4.12 EXTERNAL SPEED CONTROL OPTION

The external Speed Control is available through the FLL\_FILTER pin (21). By removing the components attached to this pin, the control of the input of the spindle OTA can be reached by an external analog voltage signal (see Figure #10). The feedback frequency for the external FLL/PLL can be taken from the FCOM pin or from the data read off of the disk itself. During Start-up, the OTA input is internally forced high until the Speed reach the value set by the internal FLL counters, then the control is ended over to the charge pump leaving the FLL\_FILTER pin at high impedance. For this reason if the external speed control is chosen, the FLL registers has to be set to a lower speed than the target one. Another way to perform the external speed control is through the serial port. This feature can be accomplished by turning ON and OFF the CPH and CPL bits (Reg#8.6.7, see Figure #10). In this case the external filter components are to be connected. The Figure #20 in the chapter 6 (Application & Tools), section 6.1 (application configurations) depicts this feature.

#### 5.0 VOICE COIL CIRCUITS

#### 5.1 DESCRIPTION

A complete Voice Coil control circuit plus 14 bit DAC and DMOS full bridge drivers are integrated in the chip. The class AB power stage which do not require snubber networks for load compensation, yet maintaining high accuracy on gain and offset parameter, allows a well controlled quiescent current, therefore maximum precision in the positioning of the head actuator. The reference voltage for the system is VCC/2 to allow symmetrical use of the available power supply. The DAC command input to the actuator is a voltage centered around VCC/2 that swings ±1V.

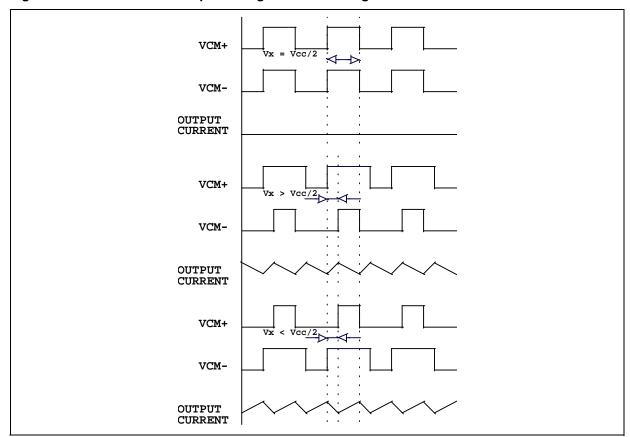

#### 5.2 CURRENT CONTROL

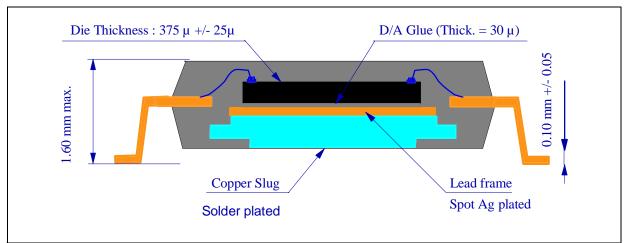

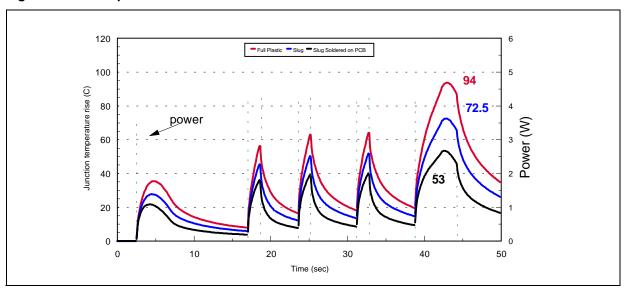

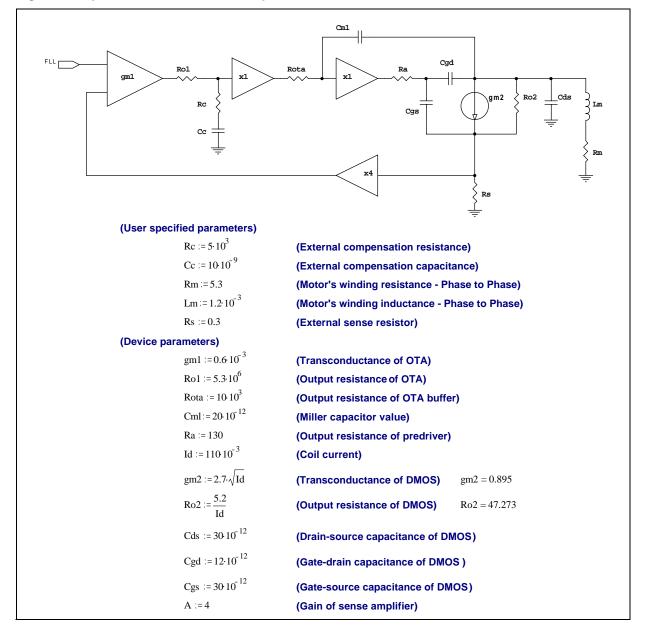

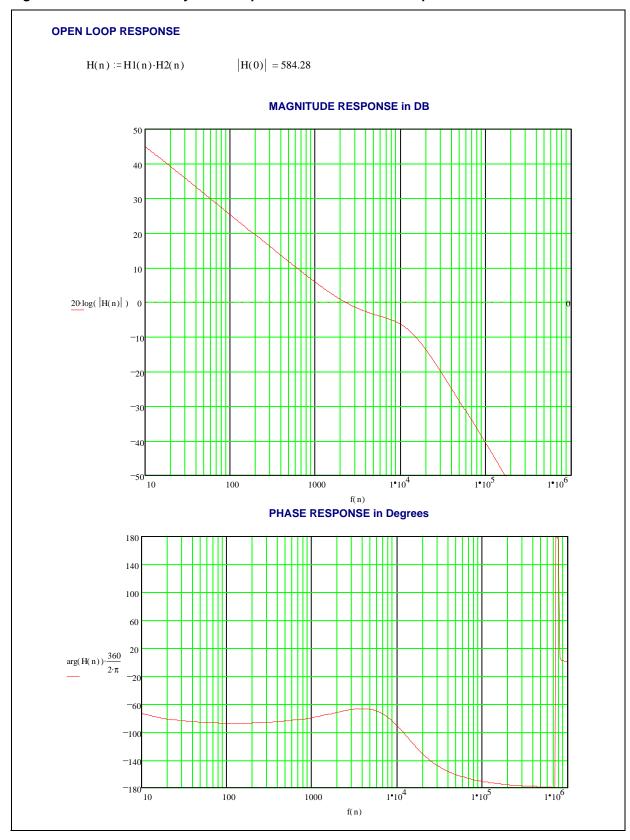

The current in the actuator is sensed by a small resistor (typ.  $250m\Omega$ ) in series to the coil. The voltage drop across the resistor is amplified by a differential amplifier with a gain of four. The output voltage of this amplifier is proportional to the current in the coil. This voltage and the DAC voltage summed at the input of the error amplifier, represent the difference between the desired current and the actual motor current. The output of the error amplifier is the signal that will drive the power stage according to the driving mode selected. Two different modes are available, Linear mode and Phase Shift Modulation