# LM3S316 Microcontroller

DATA SHEET

Copyright © 2006 Luminary Micro, Inc.

# **Legal Disclaimers and Trademark Information**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH LUMINARY MICRO PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN LUMINARY MICRO'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, LUMINARY MICRO ASSUMES NO LIABILITY WHATSOEVER, AND LUMINARY MICRO DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF LUMINARY MICRO'S PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. LUMINARY MICRO'S PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE-SUSTAINING APPLICATIONS.

Luminary Micro may make changes to specifications and product descriptions at any time, without notice. Contact your local Luminary Micro sales office or your distributor to obtain the latest specifications before placing your product order.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Luminary Micro reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Copyright © 2006 Luminary Micro, Inc. All rights reserved. Stellaris and the Luminary Micro logo are trademarks of Luminary Micro, Inc. or its subsidiaries in the United States and other countries. ARM and Thumb are registered trademarks, and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.

Luminary Micro, Inc. 2499 South Capital of Texas Hwy, Suite A-100 Austin, TX 78746 Main: +1-512-279-8800 Fax: +1-512-279-8879 http://www.luminarymicro.com

LUMINARYMICRO

# **Table of Contents**

| Legal   | Disclaimers and Trademark Information       | . 2 |

|---------|---------------------------------------------|-----|

| Revisi  | on History                                  | 18  |

| About   | This Document                               | 19  |

| Audiend | ce                                          | 19  |

| About T | his Manual                                  | 19  |

| Related | Documents                                   | 19  |

| Docume  | entation Conventions                        | 19  |

| 1.      | Architectural Overview                      | 22  |

| 1.1     | Product Features                            | 22  |

| 1.2     | Target Applications                         | 26  |

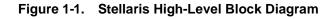

| 1.3     | High-Level Block Diagram                    | 27  |

| 1.4     | Functional Overview                         | 28  |

| 1.4.1   | ARM Cortex™-M3                              | 28  |

| 1.4.2   | Motor Control Peripherals                   | 28  |

| 1.4.3   | Analog Peripherals                          | 29  |

| 1.4.4   | Serial Communications Peripherals           |     |

| 1.4.5   | System Peripherals                          |     |

| 1.4.6   | Memory Peripherals                          |     |

| 1.4.7   | Additional Features                         |     |

| 1.4.8   | Hardware Details                            |     |

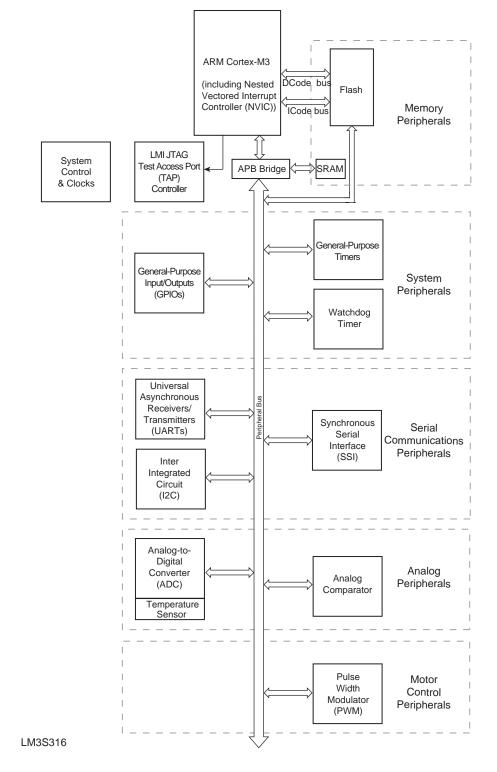

| 1.5     | System Block Diagram                        |     |

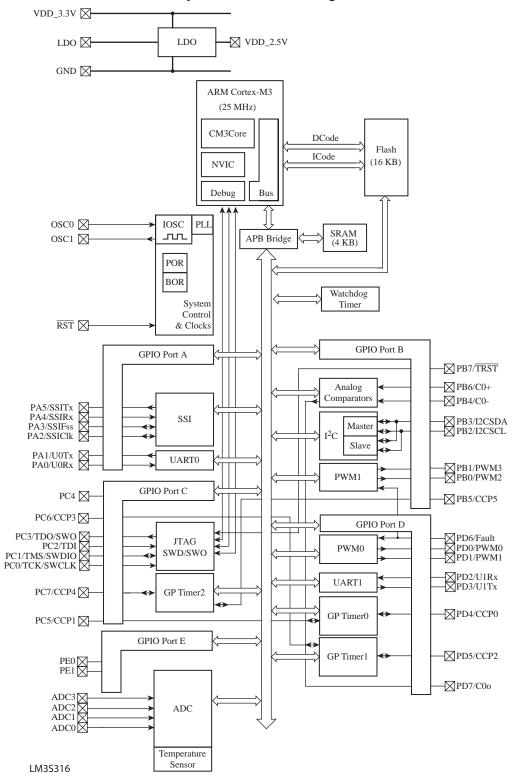

| 2.      | ARM Cortex-M3 Processor Core                |     |

| 2.1     | Block Diagram                               |     |

| 2.2     | Functional Description                      | 35  |

| 2.2.1   | Serial Wire and JTAG Debug                  |     |

| 2.2.2   | Embedded Trace Macrocell (ETM)              |     |

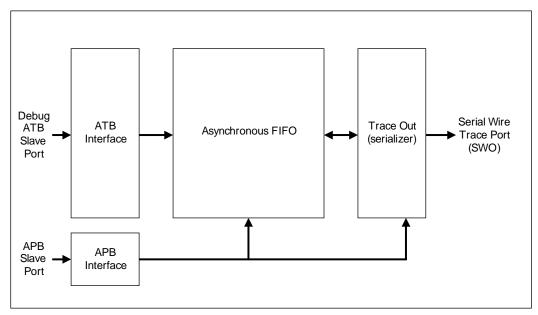

| 2.2.3   | Trace Port Interface Unit (TPIU)            |     |

| 2.2.4   | ROM Table                                   |     |

| 2.2.5   | Memory Protection Unit (MPU)                |     |

| 2.2.6   | Nested Vectored Interrupt Controller (NVIC) |     |

| 3.      | Метогу Мар                                  |     |

| 4.      | Interrupts                                  | 39  |

| 5.      | JTAG Interface                              | 42  |

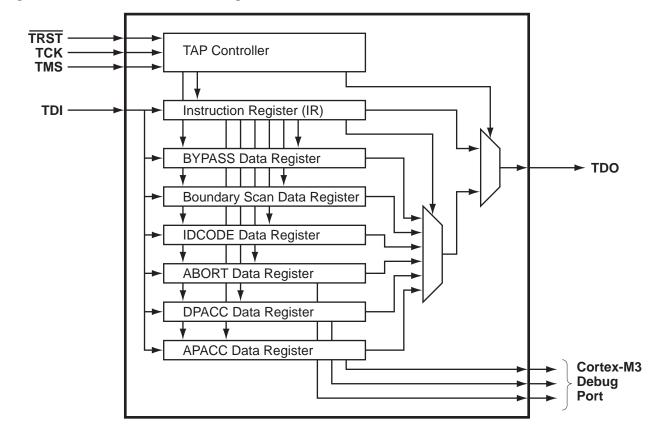

| 5.1     | Block Diagram                               | 43  |

| 5.2     | Functional Description                      |     |

| 5.2.1   | JTAG Interface Pins                         |     |

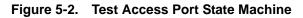

| 5.2.2   | JTAG TAP Controller                         |     |

| 5.2.3   | Shift Registers                             |     |

| 5.2.4   | Operational Considerations                  |     |

| 5.3     | Initialization and Configuration            |     |

| 5.4     | Register Descriptions                       |     |

| 5.4.1   | Instruction Register (IR)                   |     |

| 5.4.2   | Data Registers                              |     |

| 6.      | System Control                              |     |

| 6.1     | Functional Description                      |     |

| 6.1.1   | Device Identification                       | 52  |

| 6.1.2          | Reset Control                         | 52  |

|----------------|---------------------------------------|-----|

| 6.1.3          | Power Control                         |     |

|                |                                       |     |

| 6.1.4          | Clock Control                         |     |

| 6.1.5          | System Control                        |     |

| 6.2            | Initialization and Configuration      |     |

| 6.3            | Register Map                          |     |

| 6.4            | Register Descriptions                 | 59  |

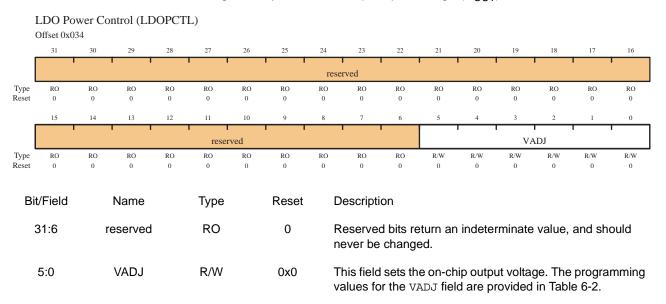

| 7.             | Internal Memory                       | 94  |

| 7.1            | Block Diagram                         |     |

| 7.2            | Functional Description                |     |

| 7.2.1          | SRAM Memory                           |     |

|                |                                       |     |

| 7.2.2          | Flash Memory                          |     |

| 7.3            | Initialization and Configuration      |     |

| 7.3.1          | Changing Flash Protection Bits        |     |

| 7.3.2          | Flash Programming                     |     |

| 7.4            | Register Map                          |     |

| 7.5            | Register Descriptions                 | 98  |

| 8.             | General-Purpose Input/Outputs (GPIOs) | 108 |

| 8.1            | Block Diagram                         |     |

| 8.2            | Functional Description                |     |

| 8.2.1          | Data Register Operation               |     |

| -              |                                       |     |

| 8.2.2          | Data Direction                        |     |

| 8.2.3          | Interrupt Operation                   |     |

| 8.2.4          | Mode Control                          |     |

| 8.2.5          | Pad Configuration                     |     |

| 8.2.6          | Identification                        |     |

| 8.3            | Initialization and Configuration      |     |

| 8.4            | Register Map                          | 114 |

| 8.5            | Register Descriptions                 | 115 |

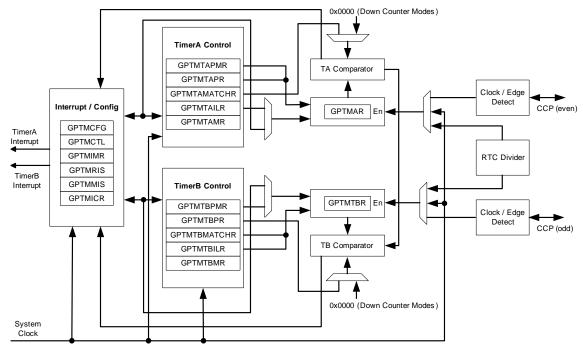

| 9.             | General-Purpose Timers                | 146 |

| 9.1            | Block Diagram                         |     |

| 9.2            | Functional Description                |     |

| 9.2.1          | GPTM Reset Conditions                 |     |

| 9.2.1          | 32-Bit Timer Operating Modes          |     |

| 9.2.2<br>9.2.3 | 16-Bit Timer Operating Modes          |     |

| 9.2.3<br>9.3   | Initialization and Configuration      |     |

|                |                                       |     |

| 9.3.1          | 32-Bit One-Shot/Periodic Timer Mode   |     |

| 9.3.2          | 32-Bit Real-Time Clock (RTC) Mode     |     |

| 9.3.3          | 16-Bit One-Shot/Periodic Timer Mode   |     |

| 9.3.4          | 16-Bit Input Edge Count Mode          |     |

| 9.3.5          | 16-Bit Input Edge Timing Mode         |     |

| 9.3.6          | 16-Bit PWM Mode                       |     |

| 9.4            | Register Map                          | 156 |

| 9.5            | Register Descriptions                 | 157 |

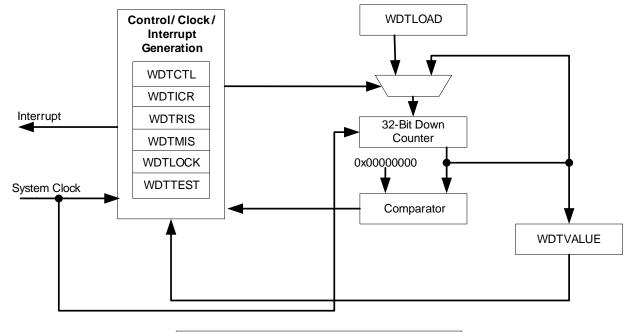

| 10.            | Watchdog Timer                        | 178 |

| 10.1           | Block Diagram                         |     |

| 10.1           | Functional Description                |     |

|                | •                                     |     |

| 10.3           | Initialization and Configuration      |     |

| 10.4           | Register Map                          | 179 |

| 10.5             | Register Descriptions                                 | . 180 |

|------------------|-------------------------------------------------------|-------|

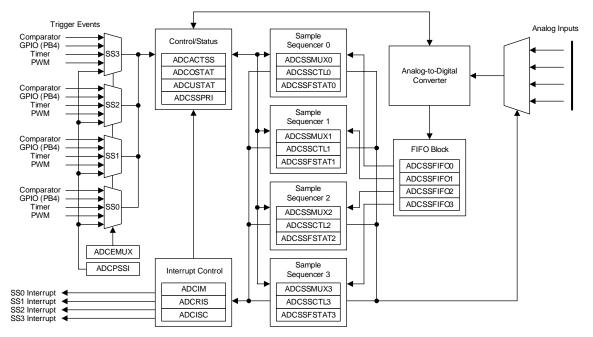

| 11.              | Analog-to-Digital Converter (ADC)                     | 201   |

| 11.1             | Block Diagram                                         |       |

| 11.2             | Functional Description                                | . 202 |

| 11.2.1           | Sample Sequencers                                     | . 202 |

| 11.2.2           | Module Control                                        | . 203 |

| 11.2.3           | Hardware Sample Averaging Circuit                     | . 204 |

| 11.2.4           | Analog-to-Digital Converter                           | . 204 |

| 11.2.5           | Test Modes                                            |       |

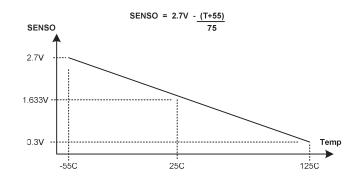

| 11.2.6           | Internal Temperature Sensor                           |       |

| 11.3             | Initialization and Configuration                      |       |

| 11.3.1           | Module Initialization                                 |       |

| 11.3.2           | Sample Sequencer Configuration                        |       |

| 11.4             | Register Map                                          |       |

| 11.5             | Register Descriptions                                 |       |

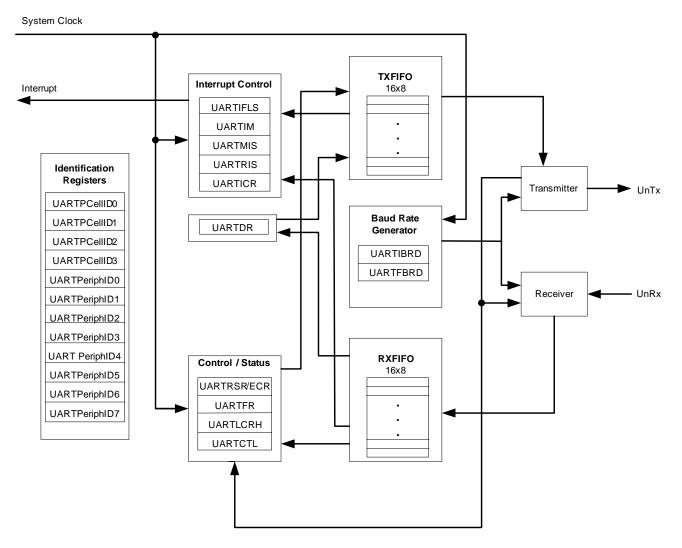

| 12.              | Universal Asynchronous Receivers/Transmitters (UARTs) |       |

| 12.1             | Block Diagram                                         |       |

| 12.2             | Functional Description                                |       |

| 12.2.1           | Transmit/Receive Logic                                |       |

| 12.2.2           | Baud-Rate Generation                                  |       |

| 12.2.3           | Data Transmission                                     |       |

| 12.2.4<br>12.2.5 | FIFO Operation<br>Interrupts                          |       |

| 12.2.5           | Loopback Operation                                    |       |

| 12.2.0           | Initialization and Configuration                      |       |

| 12.4             | Register Map                                          |       |

| 12.5             | Register Descriptions                                 |       |

| 13.              | Synchronous Serial Interface (SSI)                    |       |

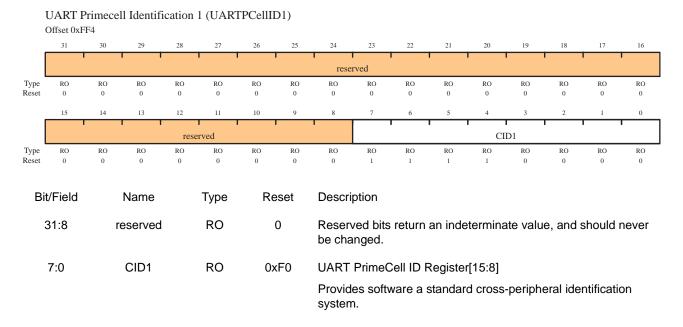

| 13.1             | Block Diagram                                         |       |

| 13.2             | Functional Description                                |       |

| 13.2.1           | Bit Rate Generation                                   |       |

| 13.2.2           | FIFO Operation                                        |       |

| 13.2.3           | Interrupts                                            |       |

| 13.2.4           | Frame Formats                                         |       |

| 13.3             | Initialization and Configuration                      | . 276 |

| 13.4             | Register Map                                          | . 277 |

| 13.5             | Register Descriptions                                 | . 278 |

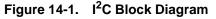

| 14.              | Inter-Integrated Circuit (I2C) Interface              | 302   |

| 14.1             | Block Diagram                                         |       |

| 14.2             | Functional Description                                |       |

| 14.2.1           | I <sup>2</sup> C Bus Functional Overview              |       |

| 14.2.2           | Available Speed Modes                                 |       |

| 14.3             | Initialization and Configuration                      | . 311 |

| 14.4             | Register Map                                          | . 311 |

| 14.5             | Register Descriptions (I2C Master)                    | . 312 |

| 14.6             | Register Descriptions (I2C Slave)                     | . 326 |

| 15.              | Analog Comparator                                     | 334   |

| 15.1             | Block Diagram                                         |       |

| 15.2             | Functional Description                                |       |

|                  | ·                                                     |       |

| 15.2.1<br>15.3                                                                                                       | Internal Reference Programming<br>Initialization and Configuration                                          | 336                                                                              |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 15.4<br>15.5                                                                                                         | Register Map<br>Register Descriptions                                                                       |                                                                                  |

| 16.                                                                                                                  | Pulse Width Modulator (PWM)                                                                                 |                                                                                  |

| 16.1                                                                                                                 | Block Diagram                                                                                               |                                                                                  |

| 16.2                                                                                                                 | Functional Description                                                                                      | 345                                                                              |

| 16.2.1                                                                                                               | PWM Timer                                                                                                   | 345                                                                              |

| 16.2.2                                                                                                               | PWM Comparators                                                                                             |                                                                                  |

| 16.2.3                                                                                                               | PWM Signal Generator                                                                                        |                                                                                  |

| 16.2.4<br>16.2.5                                                                                                     | Dead-Band Generator<br>Interrupt/ADC-Trigger Selector                                                       |                                                                                  |

| 16.2.5                                                                                                               | Synchronization Methods                                                                                     |                                                                                  |

| 16.2.7                                                                                                               | Fault Conditions                                                                                            |                                                                                  |

| 16.2.8                                                                                                               | Output Control Block                                                                                        |                                                                                  |

| 16.3                                                                                                                 | Initialization and Configuration                                                                            |                                                                                  |

| 16.4                                                                                                                 | Register Map                                                                                                |                                                                                  |

| 16.5                                                                                                                 | Register Descriptions                                                                                       |                                                                                  |

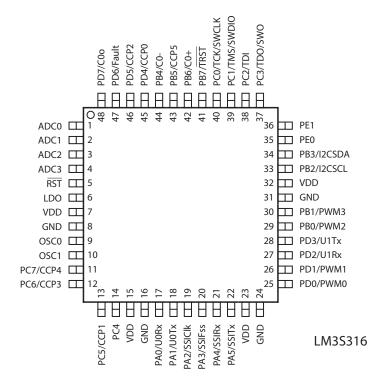

| 17.                                                                                                                  | Pin Diagram                                                                                                 |                                                                                  |

| 18.                                                                                                                  | Signal Tables                                                                                               | 378                                                                              |

| 19.                                                                                                                  | Operating Characteristics                                                                                   | 388                                                                              |

| 20.                                                                                                                  | Electrical Characteristics                                                                                  |                                                                                  |

| 20.1                                                                                                                 | DC Characteristics                                                                                          |                                                                                  |

| 20.1.1                                                                                                               | Maximum Ratings                                                                                             |                                                                                  |

| 20.1.2                                                                                                               | Recommended DC Operating Conditions                                                                         |                                                                                  |

| 20.1.3<br>20.1.4                                                                                                     | On-Chip Low Drop-Out (LDO) Regulator Characteristics                                                        |                                                                                  |

| 20.1.4                                                                                                               | Flash Memory Characteristics                                                                                |                                                                                  |

| 20.2                                                                                                                 | AC Characteristics                                                                                          |                                                                                  |

| 20.2.1                                                                                                               | Load Conditions                                                                                             |                                                                                  |

| 20.2.2                                                                                                               | Clocks                                                                                                      |                                                                                  |

|                                                                                                                      | Temperature Sensor                                                                                          |                                                                                  |

|                                                                                                                      | Analog-to-Digital Converter                                                                                 |                                                                                  |

| 20.2.5                                                                                                               | Analog Comparator                                                                                           | 394                                                                              |

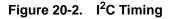

|                                                                                                                      | I <sup>2</sup> C<br>Synchronous Serial Interface (SSI)                                                      |                                                                                  |

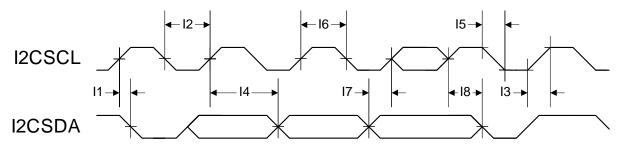

| ZU.Z.1                                                                                                               | SAUCUTODORS SERVICIEDAGE (220                                                                               | 390                                                                              |

|                                                                                                                      |                                                                                                             | 208                                                                              |

| 20.2.8                                                                                                               | JTAG and Boundary Scan                                                                                      |                                                                                  |

| 20.2.8<br>20.2.9                                                                                                     | JTAG and Boundary Scan<br>General-Purpose I/O                                                               | 400                                                                              |

| 20.2.8<br>20.2.9                                                                                                     | JTAG and Boundary Scan                                                                                      | 400<br>400                                                                       |

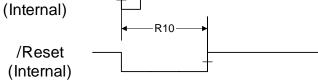

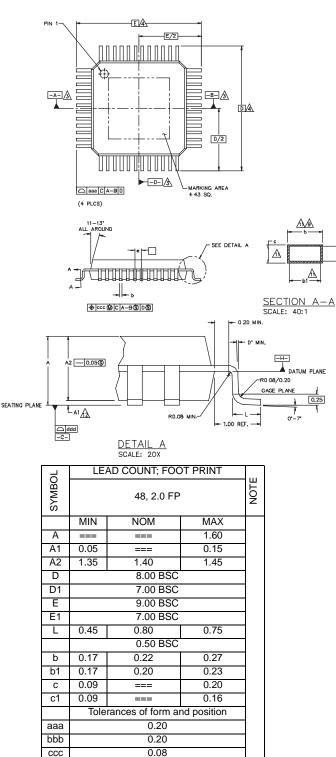

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b>                                                                            | JTAG and Boundary Scan<br>General-Purpose I/O<br>Reset                                                      | 400<br>400<br><b>403</b>                                                         |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b>                                                                            | JTAG and Boundary Scan<br>General-Purpose I/O<br>Reset<br>Package Information                               | 400<br>400<br><b>403</b><br><b>404</b>                                           |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br>Appen<br>A.1<br>A.1.1                                                   | JTAG and Boundary Scan<br>General-Purpose I/O<br>Reset<br>Package Information<br>dix A. Serial Flash Loader | 400<br>400<br><b>403</b><br><b>404</b><br>404                                    |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br>A.1<br>A.1.1<br>A.1.1<br>A.1.2                                          | JTAG and Boundary Scan                                                                                      | 400<br>400<br><b>403</b><br><b>404</b><br>404<br>404<br>404                      |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br><b>Appen</b><br>A.1<br>A.1.1<br>A.1.2<br>A.2                            | JTAG and Boundary Scan                                                                                      | 400<br>400<br><b>403</b><br><b>404</b><br>404<br>404<br>404<br>404               |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br><b>Appen</b><br>A.1<br>A.1.1<br>A.1.2<br>A.2<br>A.2.1                   | JTAG and Boundary Scan                                                                                      | 400<br>400<br><b>403</b><br><b>404</b><br>404<br>404<br>404<br>404<br>405        |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br><b>Appen</b><br>A.1<br>A.1.1<br>A.1.2<br>A.2<br>A.2.1<br>A.2.1<br>A.2.2 | JTAG and Boundary Scan                                                                                      | 400<br>400<br><b>403</b><br><b>404</b><br>404<br>404<br>404<br>404<br>405<br>405 |

| 20.2.8<br>20.2.9<br>20.2.10<br><b>21.</b><br><b>Appen</b><br>A.1<br>A.1.1<br>A.1.2<br>A.2<br>A.2.1                   | JTAG and Boundary Scan                                                                                      | 400<br>400<br><b>403</b><br><b>404</b><br>404<br>404<br>404<br>405<br>405<br>405 |

| COMMAND_PING (0x20)              | 406                                                                                                                                                               |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMMAND_GET_STATUS (0x23)        | 406                                                                                                                                                               |

| COMMAND_DOWNLOAD (0x21)          | 406                                                                                                                                                               |

| COMMAND_SEND_DATA (0x24)         | 406                                                                                                                                                               |

| COMMAND RUN (0x22)               | 407                                                                                                                                                               |

| COMMAND_RESET (0x25)             |                                                                                                                                                                   |

| Ordering and Contact Information |                                                                                                                                                                   |

| ng Information                   |                                                                                                                                                                   |

| Development Kit                  |                                                                                                                                                                   |

| Company Information              |                                                                                                                                                                   |

| rt Information                   |                                                                                                                                                                   |

|                                  | COMMAND_DOWNLOAD (0x21).<br>COMMAND_SEND_DATA (0x24)<br>COMMAND_RUN (0x22)<br>COMMAND_RESET (0x25)<br>ing and Contact Information<br>pment Kit<br>uny Information |

# **List of Figures**

| Figure 1-1.   | Stellaris High-Level Block Diagram                                    | 27  |

|---------------|-----------------------------------------------------------------------|-----|

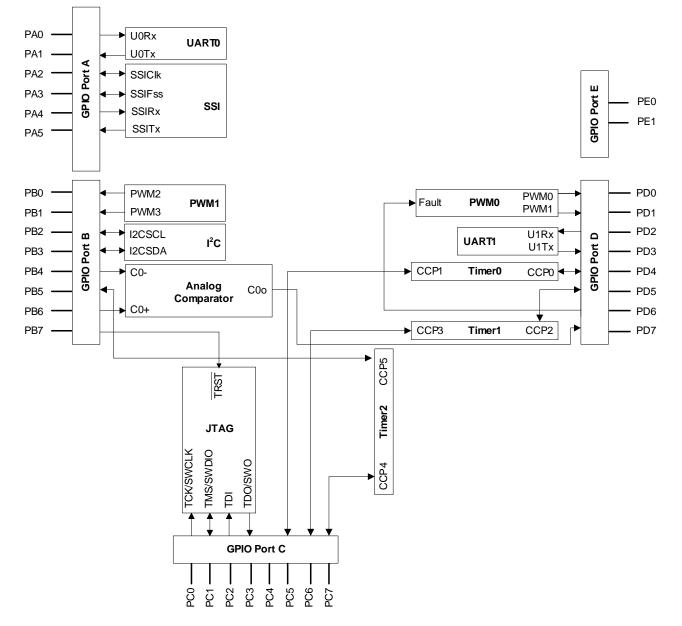

| Figure 1-2.   | LM3S316 Controller System-Level Block Diagram                         | 33  |

| Figure 2-1.   | CPU Block Diagram                                                     | 35  |

| Figure 2-2.   | TPIU Block Diagram                                                    | 36  |

| Figure 5-1.   | JTAG Module Block Diagram                                             | 43  |

| Figure 5-2.   | Test Access Port State Machine                                        |     |

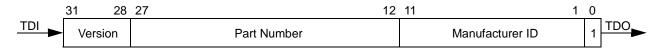

| Figure 5-3.   | IDCODE Register Format                                                | 50  |

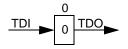

| Figure 5-4.   | BYPASS Register Format                                                |     |

| Figure 5-5.   | Boundary Scan Register Format                                         |     |

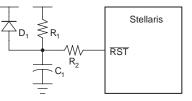

| Figure 6-1.   | External Circuitry to Extend Reset                                    |     |

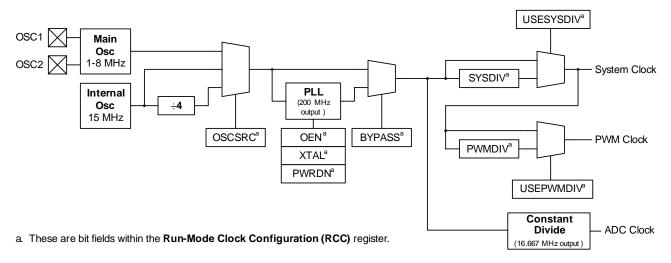

| Figure 6-2.   | Main Clock Tree                                                       |     |

| Figure 7-1.   | Flash Block Diagram                                                   | 94  |

| Figure 8-1.   | GPIO Module Block Diagram                                             |     |

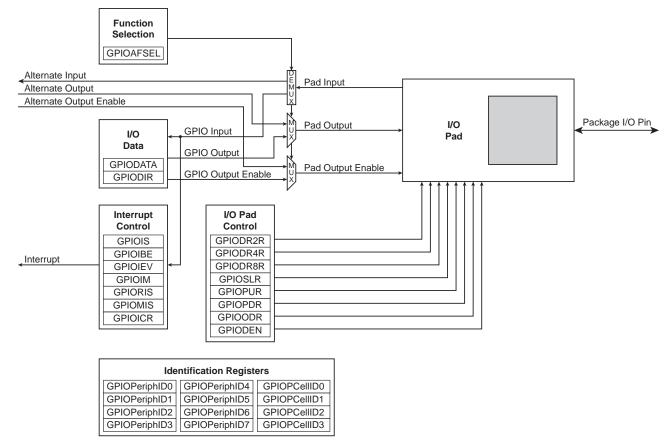

| Figure 8-2.   | GPIO Port Block Diagram                                               |     |

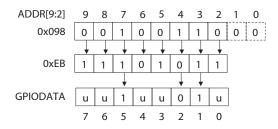

| Figure 8-3.   | GPIODATA Write Example                                                |     |

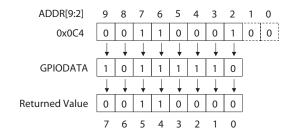

| Figure 8-4.   | GPIODATA Read Example                                                 |     |

| Figure 9-1.   | GPTM Module Block Diagram                                             |     |

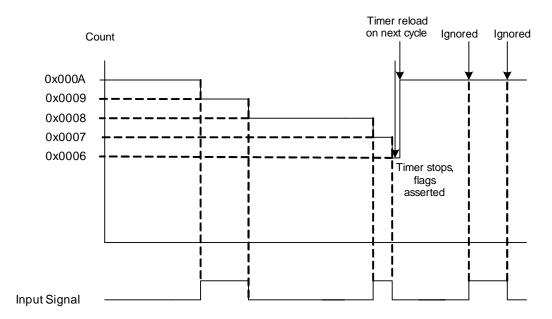

| Figure 9-2.   | 16-Bit Input Edge Count Mode Example                                  |     |

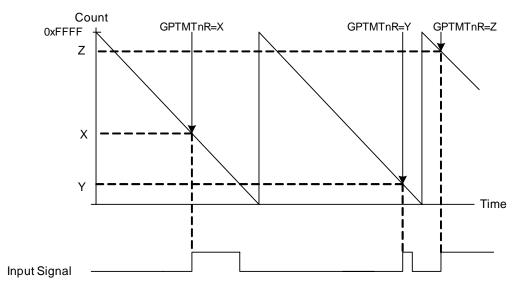

| Figure 9-3.   | 16-Bit Input Edge Time Mode Example                                   |     |

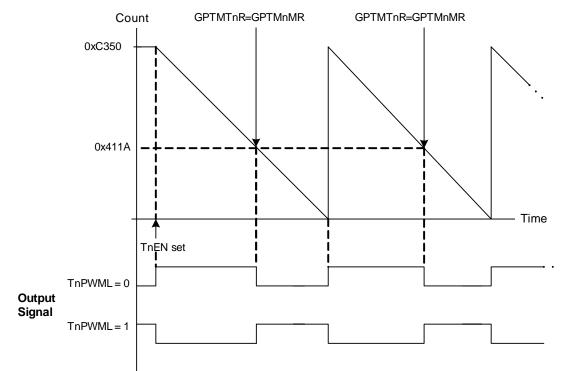

| Figure 9-4.   | 16-Bit PWM Mode Example                                               |     |

| Figure 10-1.  | WDT Module Block Diagram                                              | 178 |

| Figure 11-1.  | ADC Module Block Diagram                                              | 202 |

| Figure 11-2.  | Internal Temperature Sensor Characteristic                            | 204 |

| Figure 12-1.  | UART Module Block Diagram                                             | 232 |

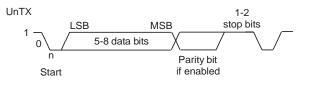

| Figure 12-2.  | UART Character Frame                                                  | 233 |

| Figure 13-1.  | SSI Module Block Diagram                                              | 267 |

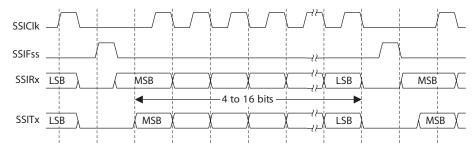

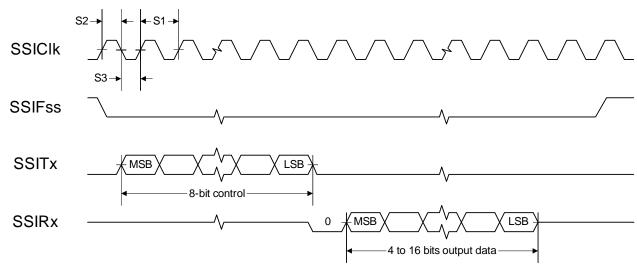

| Figure 13-2.  | TI Synchronous Serial Frame Format (Single Transfer)                  | 269 |

| Figure 13-3.  | TI Synchronous Serial Frame Format (Continuous Transfer)              | 270 |

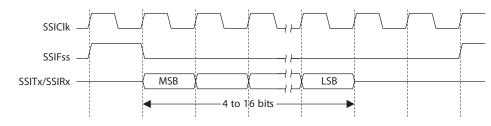

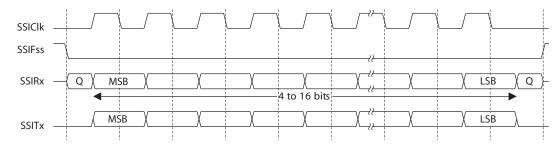

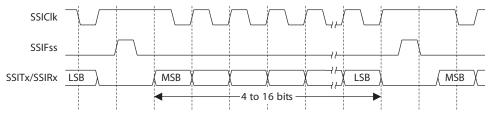

| Figure 13-4.  | Freescale SPI Format (Single Transfer) with SPO=0 and SPH=0           | 271 |

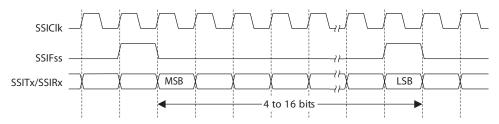

| Figure 13-5.  | Freescale SPI Format (Continuous Transfer) with SPO=0 and SPH=0       | 271 |

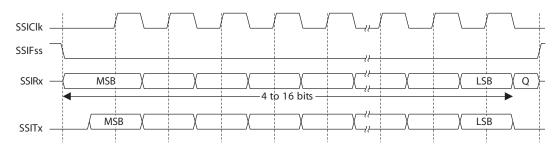

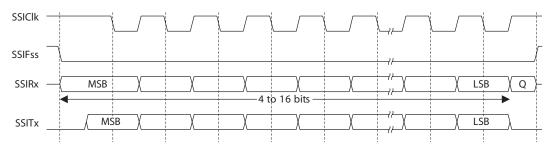

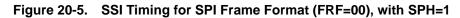

| Figure 13-6.  | Freescale SPI Frame Format with SPO=0 and SPH=1                       | 272 |

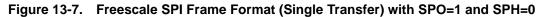

| Figure 13-7.  | Freescale SPI Frame Format (Single Transfer) with SPO=1 and SPH=0     | 272 |

| Figure 13-8.  | Freescale SPI Frame Format (Continuous Transfer) with SPO=1 and SPH=0 | 273 |

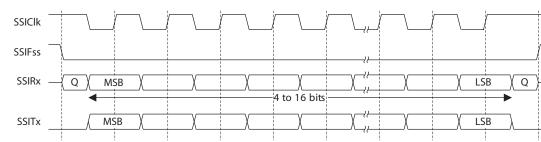

| Figure 13-9.  | Freescale SPI Frame Format with SPO=1 and SPH=1                       | 273 |

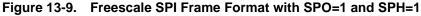

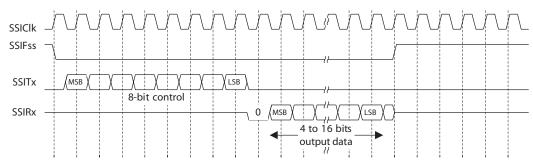

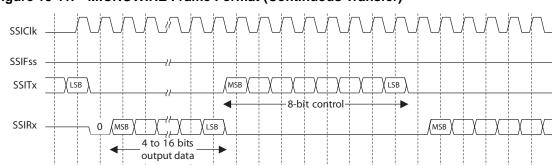

| Figure 13-10. | MICROWIRE Frame Format (Single Frame)                                 | 274 |

| Figure 13-11. | MICROWIRE Frame Format (Continuous Transfer)                          | 275 |

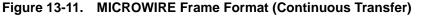

| Figure 13-12. | MICROWIRE Frame Format, SSIFss Input Setup and Hold Requirements      | 276 |

| Figure 14-1.  | I <sup>2</sup> C Block Diagram                                        | 302 |

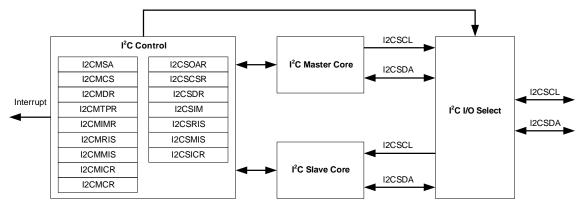

| Figure 14-2.  | I <sup>2</sup> C Bus Configuration                                    |     |

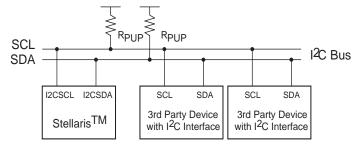

| Figure 14-3.  | Data Validity During Bit Transfer on the I <sup>2</sup> C Bus         |     |

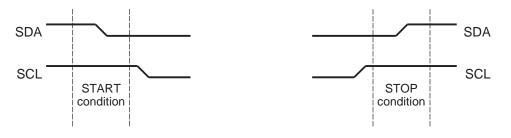

| Figure 14-4.  | START and STOP Conditions                                             | 303 |

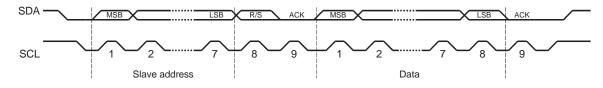

| Figure 14-5.  | Complete Data Transfer with a 7-Bit Address                           | 304 |

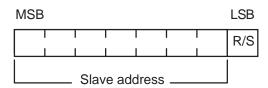

| Figure 14-6.  | R/S Bit in First Byte                                                 |     |

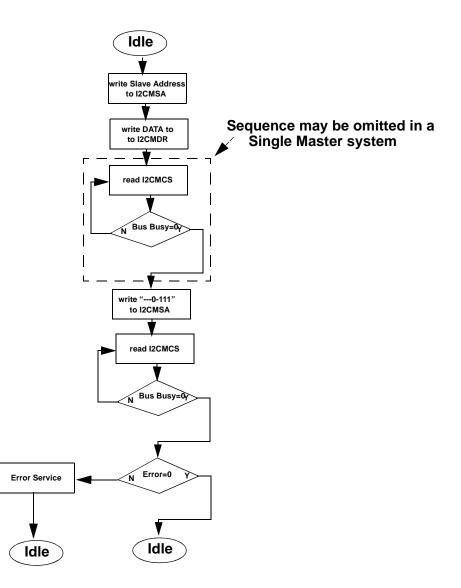

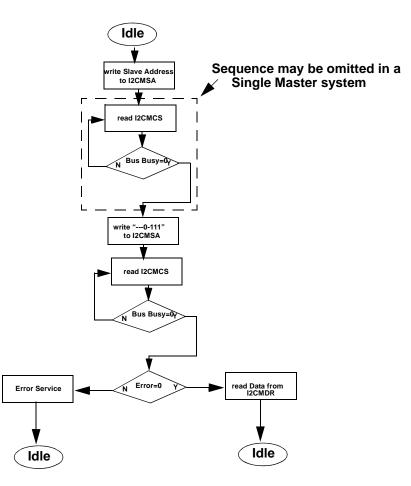

| Figure 14-7.  | Master Single SEND                                                    |     |

| Figure 14-8.  | Master Single RECEIVE                                                 |     |

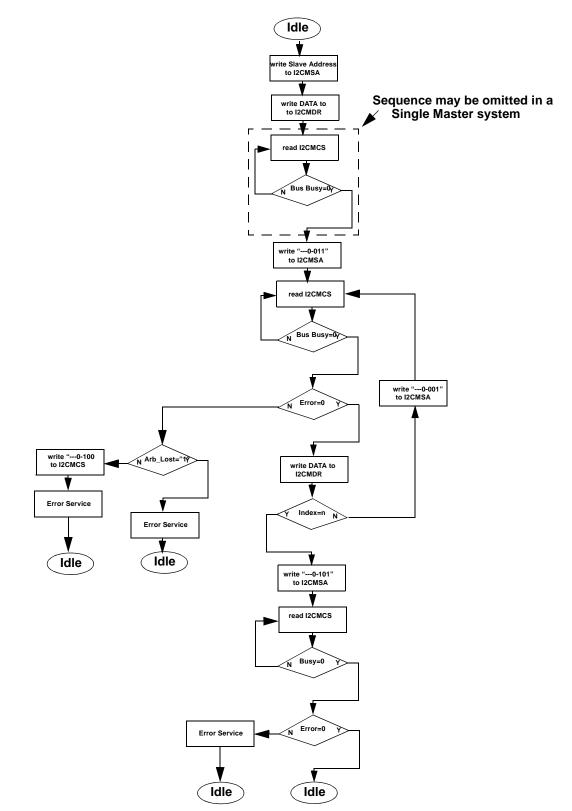

| Figure 14-9.  | Master Burst SEND                                                     | 307 |

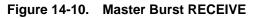

|               | Master Burst RECEIVE                                                        |       |

|---------------|-----------------------------------------------------------------------------|-------|

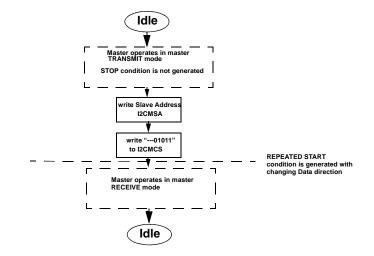

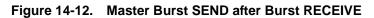

| Figure 14-11. | Master Burst RECEIVE after Burst SEND                                       | . 309 |

| Figure 14-12. | Master Burst SEND after Burst RECEIVE                                       | . 309 |

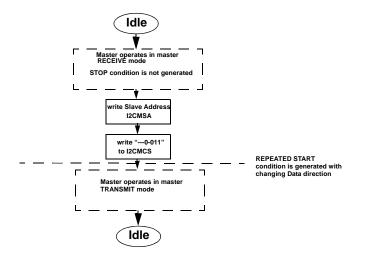

| Figure 14-13. | Slave Command Sequence                                                      | . 310 |

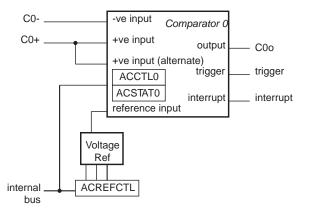

| Figure 15-1.  | Analog Comparator Module Block Diagram                                      | . 334 |

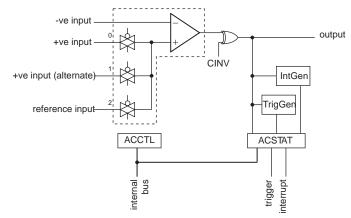

| Figure 15-2.  | Structure of Comparator Unit                                                | . 335 |

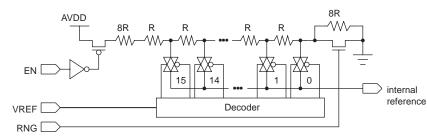

| Figure 15-3.  | Comparator Internal Reference Structure                                     | . 336 |

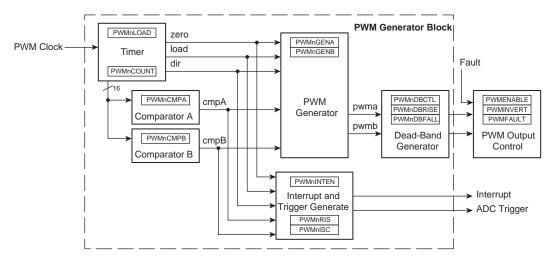

| Figure 16-1.  | PWM Module Block Diagram                                                    | . 345 |

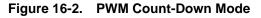

| Figure 16-2.  | PWM Count-Down Mode                                                         | . 346 |

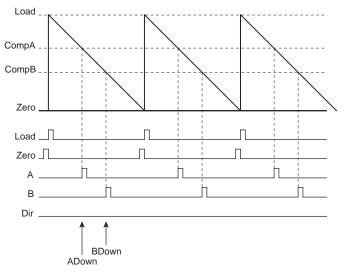

| Figure 16-3.  | PWM Count-Up/Down Mode                                                      |       |

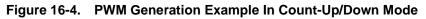

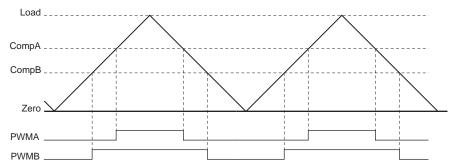

| Figure 16-4.  | PWM Generation Example In Count-Up/Down Mode                                | . 347 |

| Figure 16-5.  | PWM Dead-Band Generator                                                     |       |

| Figure 17-1.  | Pin Connection Diagram                                                      |       |

| Figure 20-1.  | Load Conditions                                                             | . 392 |

| Figure 20-2.  | I <sup>2</sup> C Timing                                                     | . 395 |

| Figure 20-3.  | SSI Timing for TI Frame Format (FRF=01), Single Transfer Timing Measurement |       |

| Figure 20-4.  | SSI Timing for MICROWIRE Frame Format (FRF=10), Single Transfer             | . 397 |

| Figure 20-5.  | SSI Timing for SPI Frame Format (FRF=00), with SPH=1                        | . 397 |

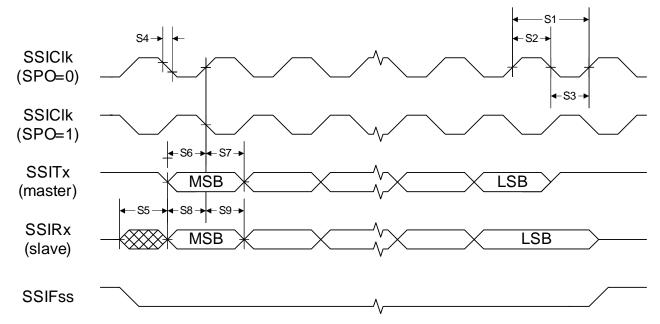

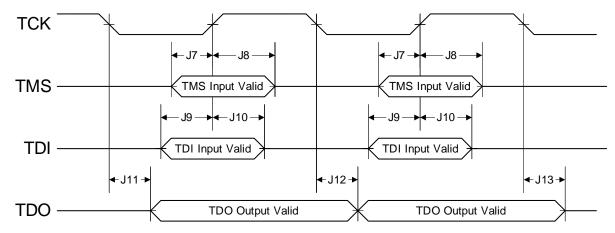

| Figure 20-6.  | JTAG Test Clock Input Timing                                                |       |

| Figure 20-7.  | JTAG Test Access Port (TAP) Timing                                          | . 399 |

| Figure 20-8.  | JTAG TRST Timing                                                            | . 399 |

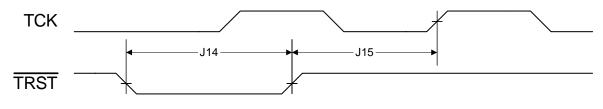

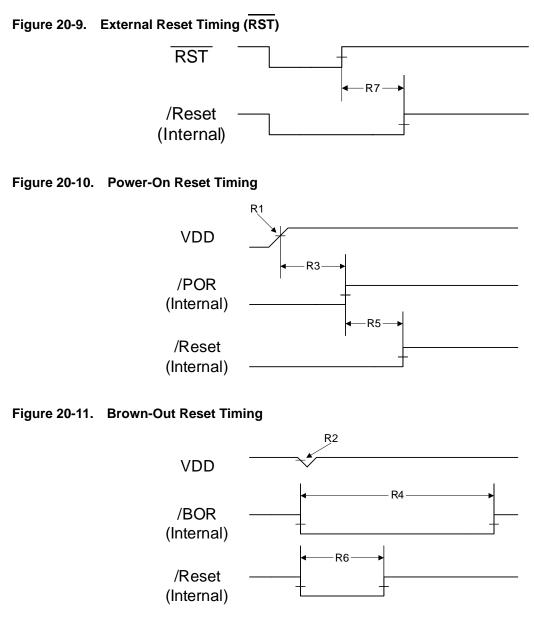

| Figure 20-9.  | External Reset Timing (RST)                                                 | . 401 |

| -             | Power-On Reset Timing                                                       |       |

| Figure 20-11. | Brown-Out Reset Timing                                                      | . 401 |

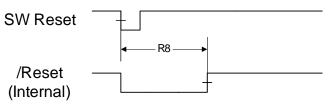

| Figure 20-12. | Software Reset Timing                                                       | . 401 |

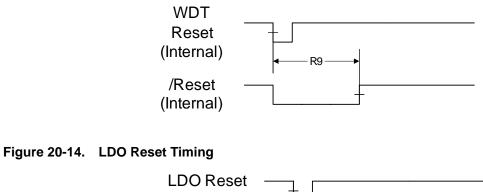

| Figure 20-13. | Watchdog Reset Timing                                                       | . 402 |

| -             | LDO Reset Timing                                                            |       |

| Figure 21-1.  | 48-Pin LQFP Package                                                         | . 403 |

|               |                                                                             |       |

# **List of Tables**

| Table 0-1.   | Documentation Conventions                                          | 19    |

|--------------|--------------------------------------------------------------------|-------|

| Table 3-1.   | Memory Map                                                         | 37    |

| Table 4-1.   | Exception Types                                                    | 39    |

| Table 4-2.   | Interrupts                                                         | 40    |

| Table 5-1.   | JTAG Port Pins Reset State                                         |       |

| Table 5-2.   | JTAG Instruction Register Commands                                 | 48    |

| Table 6-1.   | System Control Register Map                                        | 58    |

| Table 6-2.   | VADJ to VOUT                                                       | 71    |

| Table 6-3.   | PLL Mode Control                                                   |       |

| Table 6-4.   | Default Crystal Field Values and PLL Programming                   | 83    |

| Table 7-1.   | Flash Protection Policy Combinations                               | 96    |

| Table 7-2.   | Flash Register Map                                                 | 97    |

| Table 8-1.   | GPIO Pad Configuration Examples                                    | . 113 |

| Table 8-2.   | GPIO Interrupt Configuration Example                               | . 113 |

| Table 8-3.   | GPIO Register Map                                                  | . 114 |

| Table 9-1.   | 16-Bit Timer With Prescaler Configurations                         | . 150 |

| Table 9-2.   | GPTM Register Map                                                  | . 156 |

| Table 10-1.  | WDT Register Map                                                   | . 179 |

| Table 11-1.  | Samples and FIFO Depth of Sequencers                               | 202   |

| Table 11-2.  | ADC Register Map                                                   | . 205 |

| Table 12-1.  | UART Register Map                                                  | . 236 |

| Table 13-1.  | SSI Register Map                                                   |       |

| Table 14-1.  | Examples of I <sup>2</sup> C Master Timer Period versus Speed Mode |       |

| Table 14-2.  | I <sup>2</sup> C Register Map                                      |       |

| Table 14-3.  | Write Field Decoding for I2CMCS[3:0] Field                         |       |

| Table 15-1.  | Comparator 0 Operating Modes                                       |       |

| Table 15-2.  | Internal Reference Voltage and ACREFCTL Field Values               |       |

| Table 15-3.  | Analog Comparator Register Map                                     |       |

| Table 16-1.  | PWM Register Map                                                   | . 350 |

| Table 16-2.  | PWM Generator Action Encodings                                     |       |

| Table 18-1.  | Signals by Pin Number                                              |       |

| Table 18-2.  | Signals by Signal Name                                             |       |

| Table 18-3.  | Signals by Function, Except for GPIO                               |       |

| Table 18-4.  | GPIO Pins and Alternate Functions                                  |       |

| Table 19-1.  | Temperature Characteristics                                        |       |

| Table 19-2.  | Thermal Characteristics                                            | . 388 |

| Table 20-1.  | Maximum Ratings                                                    |       |

| Table 20-2.  | Recommended DC Operating Conditions                                |       |

| Table 20-3.  | LDO Regulator Characteristics                                      |       |

| Table 20-4.  | Power Specifications                                               |       |

| Table 20-5.  | Flash Memory Characteristics                                       |       |

| Table 20-6.  | Phase Locked Loop (PLL) Characteristics                            |       |

| Table 20-7.  | Clock Characteristics                                              |       |

| Table 20-8.  | Temperature Sensor Characteristics                                 |       |

| Table 20-9.  | ADC Characteristics                                                |       |

| Table 20-10. | Analog Comparator Characteristics                                  | . 394 |

| Table 20-11. | Analog Comparator Voltage Reference Characteristics                |       |

| Table 20-12. | I <sup>2</sup> C Characteristics                                   |       |

|              |                                                                    |       |

| Table 20-13. | SSI Characteristics   | . 396 |

|--------------|-----------------------|-------|

| Table 20-14. | JTAG Characteristics  | . 398 |

| Table 20-15. | GPIO Characteristics  | . 400 |

| Table 20-16. | Reset Characteristics | . 400 |

# **List of Registers**

| System C    | ontrol                                                                    |    |

|-------------|---------------------------------------------------------------------------|----|

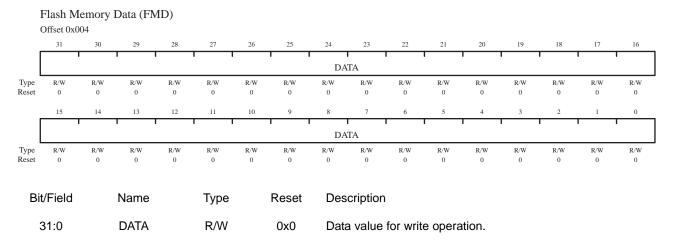

| Register 1: | Device Identification 0 (DID0), offset 0x000                              | 60 |

| Register 2: | Device Identification 1 (DID1), offset 0x004                              | 61 |

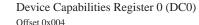

| Register 3: | Device Capabilities 0 (DC0), offset 0x008                                 | 63 |

| Register 4: | Device Capabilities 1 (DC1), offset 0x010                                 | 64 |

| Register 5: | Device Capabilities 2 (DC2), offset 0x014                                 | 66 |

| Register 6: | Device Capabilities 3 (DC3), offset 0x018                                 | 67 |

| Register 7: | Device Capabilities 4 (DC4), offset 0x01C                                 |    |

| Register 8: | Power-On and Brown-Out Reset Control (PBORCTL), offset 0x030              | 70 |

| Register 9: | LDO Power Control (LDOPCTL), offset 0x034                                 |    |

| Register 10 | : Software Reset Control 0 (SRCR0), offset 0x040                          | 72 |

| Register 11 | : Software Reset Control 1 (SRCR1), offset 0x044                          | 73 |

| Register 12 |                                                                           |    |

| Register 13 |                                                                           |    |

| Register 14 |                                                                           |    |

| Register 15 | : Masked Interrupt Status and Clear (MISC), offset 0x058                  |    |

| Register 16 | : Reset Cause (RESC), offset 0x05C                                        | 79 |

| Register 17 |                                                                           |    |

| Register 18 |                                                                           |    |

| Register 19 | : Run-Mode Clock Gating Control 0 (RCGC0), offset 0x100                   |    |

| Register 20 |                                                                           |    |

| Register 21 |                                                                           |    |

| Register 22 |                                                                           |    |

| Register 23 |                                                                           |    |

| Register 24 |                                                                           |    |

| Register 25 |                                                                           |    |

| Register 26 |                                                                           |    |

| Register 27 |                                                                           |    |

| Register 28 |                                                                           |    |

| Register 29 |                                                                           |    |

| Register 30 |                                                                           |    |

|             | lemory                                                                    |    |

| Register 1: | Flash Memory Protection Read Enable (FMPRE), offset 0x130                 |    |

| Register 2: | Flash Memory Protection Program Enable (FMPPE), offset 0x134              |    |

| Register 3: | USec Reload (USECRL), offset 0x140                                        |    |

| Register 4: | Flash Memory Address (FMA), offset 0x000                                  |    |

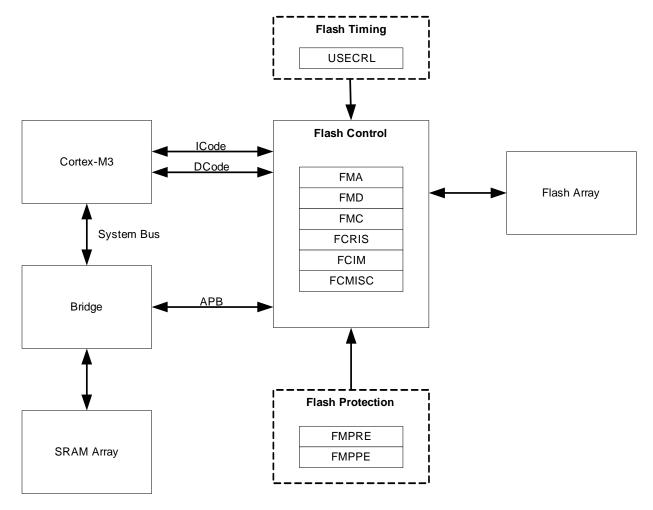

| Register 5: | Flash Memory Data (FMD), offset 0x004                                     |    |

| Register 6: | Flash Memory Control (FMC), offset 0x008                                  |    |

| Register 7: | Flash Controller Raw Interrupt Status (FCRIS), offset 0x00C               |    |

| Register 8: | Flash Controller Interrupt Mask (FCIM), offset 0x010                      |    |

| Register 9: | Flash Controller Masked Interrupt Status and Clear (FCMISC), offset 0x014 |    |

|             | Purpose Input/Outputs (GPIOs)                                             |    |

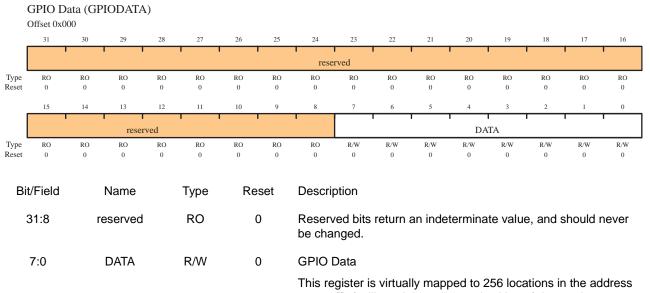

| Register 1: | GPIO Data (GPIODATA), offset 0x000                                        |    |

| Register 2: | GPIO Direction (GPIODIR), offset 0x400                                    |    |

| Register 3: | GPIO Interrupt Sense (GPIOIS), offset 0x404                               |    |

| Register 4: | GPIO Interrupt Both Edges (GPIOIBE), offset 0x408                         |    |

| Register 5:  | GPIO Interrupt Event (GPIOIEV), offset 0x40C                   | 120 |

|--------------|----------------------------------------------------------------|-----|

| Register 6:  | GPIO Interrupt Mask (GPIOIM), offset 0x410                     | 121 |

| Register 7:  | GPIO Raw Interrupt Status (GPIORIS), offset 0x414              | 122 |

| Register 8:  | GPIO Masked Interrupt Status (GPIOMIS), offset 0x418           | 123 |

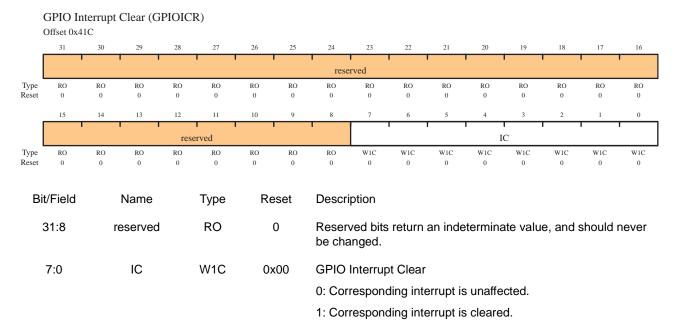

| Register 9:  | GPIO Interrupt Clear (GPIOICR), offset 0x41C                   |     |

| Register 10: | GPIO Alternate Function Select (GPIOAFSEL), offset 0x420       | 125 |

| Register 11: | GPIO 2-mA Drive Select (GPIODR2R), offset 0x500                | 126 |

| Register 12: | GPIO 4-mA Drive Select (GPIODR4R), offset 0x504                | 127 |

| Register 13: | GPIO 8-mA Drive Select (GPIODR8R), offset 0x508                | 128 |

| Register 14: | GPIO Open Drain Select (GPIOODR), offset 0x50C                 | 129 |

| Register 15: | GPIO Pull-Up Select (GPIOPUR), offset 0x510                    |     |

| Register 16: | GPIO Pull-Down Select (GPIOPDR), offset 0x514                  |     |

| Register 17: | GPIO Slew Rate Control Select (GPIOSLR), offset 0x518          |     |

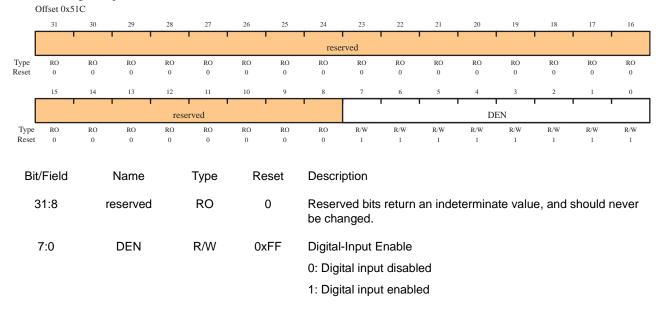

| Register 18: | GPIO Digital Input Enable (GPIODEN), offset 0x51C              |     |

| Register 19: | GPIO Peripheral Identification 4 (GPIOPeriphID4), offset 0xFD0 |     |

| Register 20: | GPIO Peripheral Identification 5 (GPIOPeriphID5), offset 0xFD4 |     |

| Register 21: | GPIO Peripheral Identification 6 (GPIOPeriphID6), offset 0xFD8 |     |

| Register 22: | GPIO Peripheral Identification 7 (GPIOPeriphID7), offset 0xFDC | 137 |

| Register 23: | GPIO Peripheral Identification 0 (GPIOPeriphID0), offset 0xFE0 |     |

| Register 24: | GPIO Peripheral Identification 1(GPIOPeriphID1), offset 0xFE4  | 139 |

| Register 25: | GPIO Peripheral Identification 2 (GPIOPeriphID2), offset 0xFE8 | 140 |

| Register 26: | GPIO Peripheral Identification 3 (GPIOPeriphID3), offset 0xFEC | 141 |

| Register 27: | GPIO PrimeCell Identification 0 (GPIOPCellID0), offset 0xFF0   |     |

| Register 28: | GPIO PrimeCell Identification 1 (GPIOPCellID1), offset 0xFF4   | 143 |

| Register 29: | GPIO PrimeCell Identification 2 (GPIOPCellID2), offset 0xFF8   | 144 |

| Register 30: | GPIO PrimeCell Identification 3 (GPIOPCellID3), offset 0xFFC   | 145 |

| General-Pur  | pose Timers                                                    | 146 |

| Register 1:  | GPTM Configuration (GPTMCFG), offset 0x000                     | 158 |

| Register 2:  | GPTM TimerA Mode (GPTMTAMR), offset 0x004                      | 159 |

| Register 3:  | GPTM TimerB Mode (GPTMTBMR), offset 0x008                      |     |

| Register 4:  | GPTM Control (GPTMCTL), offset 0x00C                           | 161 |

| Register 5:  | GPTM Interrupt Mask (GPTMIMR), offset 0x018                    |     |

| Register 6:  | GPTM Raw Interrupt Status (GPTMRIS), offset 0x01C              | 165 |

| Register 7:  | GPTM Masked Interrupt Status (GPTMMIS), offset 0x020           |     |

| Register 8:  | GPTM Interrupt Clear (GPTMICR), offset 0x024                   |     |

| Register 9:  | GPTM TimerA Interval Load (GPTMTAILR), offset 0x028            | 168 |

| Register 10: | GPTM TimerB Interval Load (GPTMTBILR), offset 0x02C            | 169 |

| Register 11: | GPTM TimerA Match (GPTMTAMATCHR), offset 0x030                 | 170 |

| Register 12: | GPTM TimerB Match (GPTMTBMATCHR), offset 0x034                 | 171 |

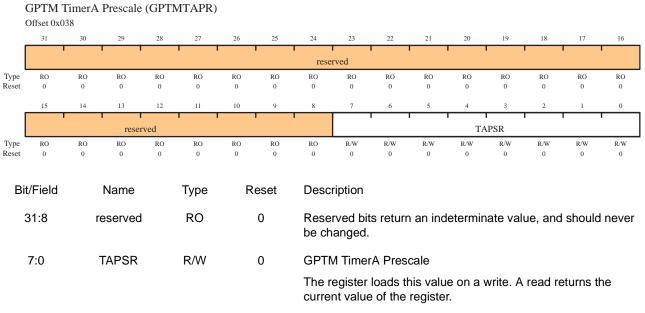

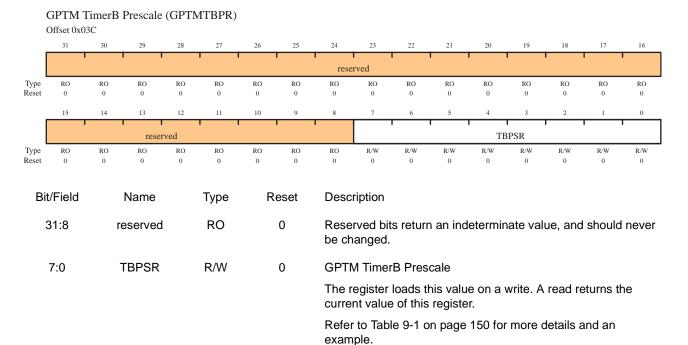

| Register 13: | GPTM TimerA Prescale (GPTMTAPR), offset 0x038                  | 172 |

| Register 14: | GPTM TimerB Prescale (GPTMTBPR), offset 0x03C                  | 173 |

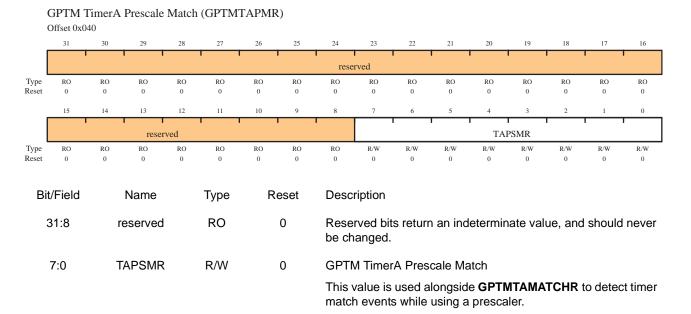

| Register 15: | GPTM TimerA Prescale Match (GPTMTAPMR), offset 0x040           |     |

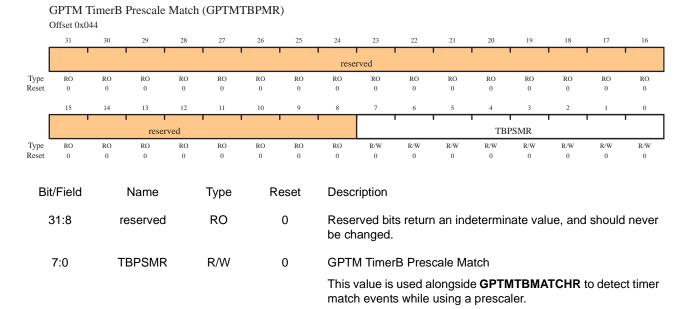

| Register 16: | GPTM TimerB Prescale Match (GPTMTBPMR), offset 0x044           |     |

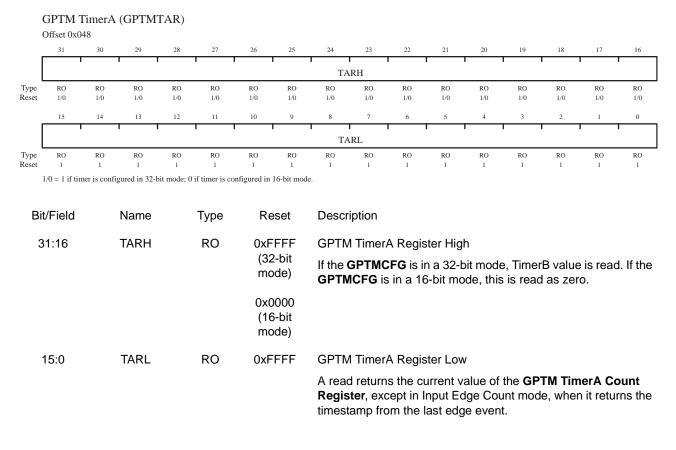

| Register 17: | GPTM TimerA (GPTMTAR), offset 0x048                            |     |

| Register 18: | GPTM TimerB (GPTMTBR), offset 0x04C                            | 177 |

| Watchdog T   | imer                                                           | 178 |

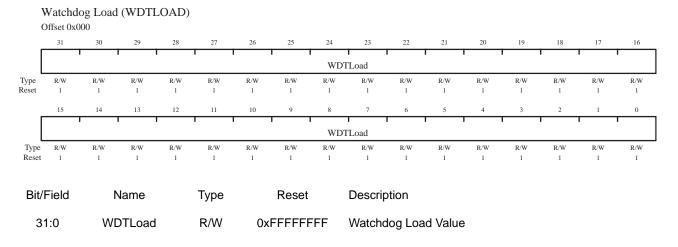

| Register 1:  | Watchdog Load (WDTLOAD), offset 0x000                          |     |

|              |                                                                |     |

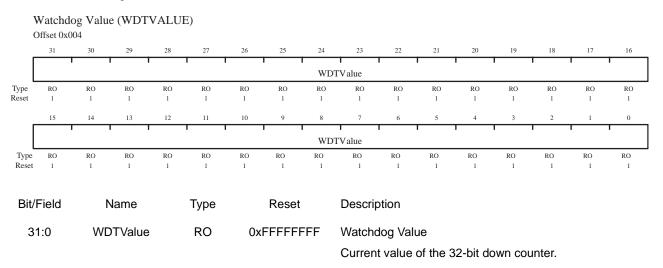

| Register 2:  | Watchdog Value (WDTVALUE), offset 0x004                        |     |

| Register 3:  | Watchdog Control (WDTCTL), offset 0x008                                  | 183 |

|--------------|--------------------------------------------------------------------------|-----|

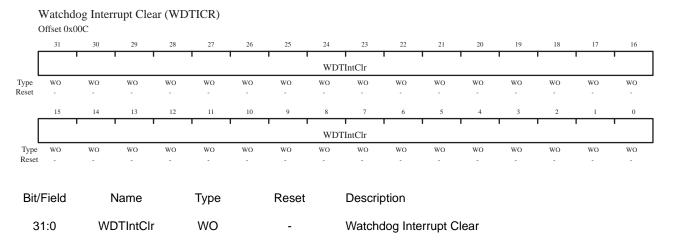

| Register 4:  | Watchdog Interrupt Clear (WDTICR), offset 0x00C                          | 184 |

| Register 5:  | Watchdog Raw Interrupt Status (WDTRIS), offset 0x010                     | 185 |

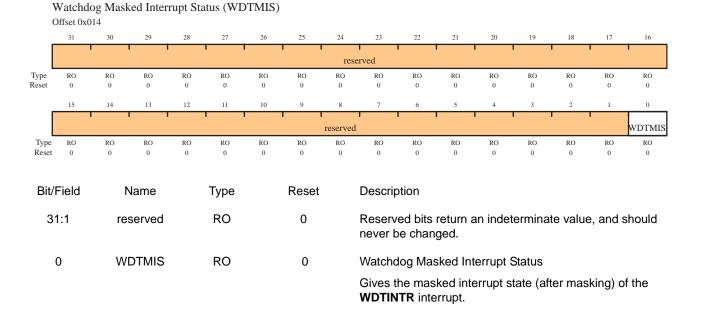

| Register 6:  | Watchdog Masked Interrupt Status (WDTMIS), offset 0x014                  | 186 |

| Register 7:  | Watchdog Lock (WDTLOCK), offset 0xC00                                    | 187 |

| Register 8:  | Watchdog Test (WDTTEST), offset 0x418                                    | 188 |

| Register 9:  | Watchdog Peripheral Identification 4 (WDTPeriphID4), offset 0xFD0        | 189 |

| Register 10: | Watchdog Peripheral Identification 5 (WDTPeriphID5), offset 0xFD4        |     |

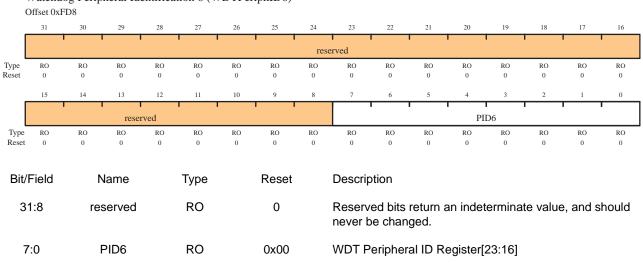

| Register 11: | Watchdog Peripheral Identification 6 (WDTPeriphID6), offset 0xFD8        |     |

| Register 12: | Watchdog Peripheral Identification 7 (WDTPeriphID7), offset 0xFDC        | 192 |

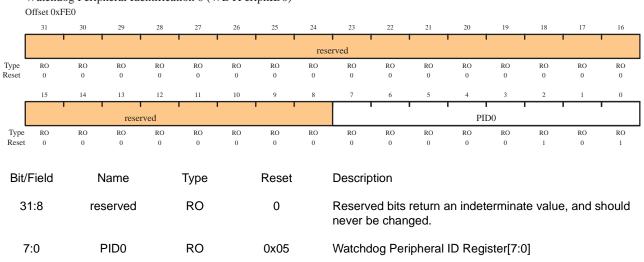

| Register 13: | Watchdog Peripheral Identification 0 (WDTPeriphID0), offset 0xFE0        | 193 |

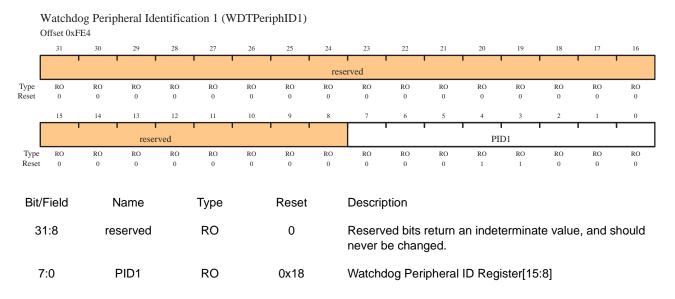

| Register 14: | Watchdog Peripheral Identification 1 (WDTPeriphID1), offset 0xFE4        | 194 |

| Register 15: | Watchdog Peripheral Identification 2 (WDTPeriphID2), offset 0xFE8        | 195 |

| Register 16: | Watchdog Peripheral Identification 3 (WDTPeriphID3), offset 0xFEC        |     |

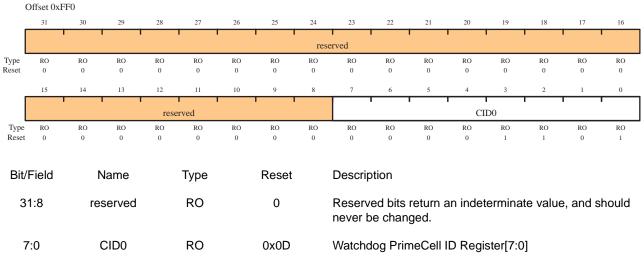

| Register 17: | Watchdog PrimeCell Identification 0 (WDTPCellID0), offset 0xFF0          |     |

| Register 18: | Watchdog PrimeCell Identification 1 (WDTPCellID1), offset 0xFF4          |     |

| Register 19: | Watchdog PrimeCell Identification 2 (WDTPCellID2), offset 0xFF8          |     |

| Register 20: | Watchdog PrimeCell Identification 3 (WDTPCellID3), offset 0xFFC          |     |

| •            | ligital Converter (ADC)                                                  |     |

| Register 1:  | ADC Active Sample Sequencer (ADCACTSS), offset 0x000                     |     |

| Register 2:  | ADC Raw Interrupt Status (ADCRIS), offset 0x004                          |     |

| Register 3:  | ADC Interrupt Mask (ADCIM), offset 0x008                                 |     |

| Register 4:  | ADC Interrupt Status and Clear (ADCISC), offset 0x00C                    |     |

| Register 5:  | ADC Overflow Status (ADCOSTAT), offset 0x010                             |     |

| Register 6:  | ADC Event Multiplexer Select (ADCEMUX), offset 0x014                     |     |

| Register 7:  | ADC Underflow Status (ADCUSTAT), offset 0x018                            |     |

| Register 8:  | ADC Sample Sequencer Priority (ADCSSPRI), offset 0x020                   |     |

| Register 9:  | ADC Processor Sample Sequence Initiate (ADCPSSI), offset 0x028           |     |

| Register 10: | ADC Sample Averaging Control (ADCSAC), offset 0x030                      |     |

| Register 11: | ADC Sample Sequence Input Multiplexer Select 0 (ADCSSMUX0), offset 0x040 |     |

| Register 12: | ADC Sample Sequence Control 0 (ADCSSCTL0), offset 0x044                  |     |

| Register 12: | ADC Sample Sequence Result FIFO 0 (ADCSSFIFO0), offset 0x048             |     |

| Register 14: | ADC Sample Sequence FIFO 0 Status (ADCSSFSTAT0), offset 0x04C            |     |

| Register 15: | ADC Sample Sequence Input Multiplexer Select 1 (ADCSSMUX1), offset 0x060 |     |

| Register 16: | ADC Sample Sequence Control 1 (ADCSSCTL1), offset 0x064                  |     |

| Register 17: | ADC Sample Sequence Result FIFO 1 (ADCSSFIFO1), offset 0x068             |     |

| Register 18: | ADC Sample Sequence FIFO 1 Status (ADCSSFSTAT1), offset 0x06C            |     |

| Register 19: | ADC Sample Sequence Input Multiplexer Select 2 (ADCSSMUX2), offset 0x080 |     |

| Register 20: | ADC Sample Sequence Control 2 (ADCSSCTL2), offset 0x084                  |     |

| Register 21: | ADC Sample Sequence Result FIFO 2 (ADCSSFIFO2), offset 0x088             |     |

| Register 22: | ADC Sample Sequence FIFO 2 Status (ADCSSFSTAT2), offset 0x08C            |     |

| Register 23: | ADC Sample Sequence Input Multiplexer Select 3 (ADCSSMUX3), offset 0x0A0 |     |

| Register 24: | ADC Sample Sequence Control 3 (ADCSSCTL3), offset 0x064                  |     |

| Register 25: | ADC Sample Sequence Result FIFO 3 (ADCSSFIFO3), offset 0x0A8             |     |

| Register 26: | ADC Sample Sequence FIFO 3 Status (ADCSSFSTAT3), offset 0x0AC            |     |

| Register 27: | ADC Test Mode Loopback (ADCTMLB), offset 0x100                           |     |

| Universal A  | synchronous Receivers/Transmitters (UARTs)                               | 231 |

| Register 1:  | UART Data (UARTDR), offset 0x000                                         |     |

| Register 2:   | UART Receive Status/Error Clear (UARTRSR/UARTECR), offset 0x004 |     |

|---------------|-----------------------------------------------------------------|-----|

| Register 3:   | UART Flag (UARTFR), offset 0x018                                |     |

| Register 4:   | UART Integer Baud-Rate Divisor (UARTIBRD), offset 0x024         |     |

| Register 5:   | UART Fractional Baud-Rate Divisor (UARTFBRD), offset 0x028      |     |

| Register 6:   | UART Line Control (UARTLCRH), offset 0x02C                      |     |

| Register 7:   | UART Control (UARTCTL), offset 0x030                            |     |

| Register 8:   | UART Interrupt FIFO Level Select (UARTIFLS), offset 0x034       |     |

| Register 9:   | UART Interrupt Mask (UARTIM), offset 0x038                      |     |

| Register 10:  | UART Raw Interrupt Status (UARTRIS), offset 0x03C               |     |

| Register 11:  | UART Masked Interrupt Status (UARTMIS), offset 0x040            |     |

| Register 12:  | UART Interrupt Clear (UARTICR), offset 0x044                    |     |

| Register 13:  | UART Peripheral Identification 4 (UARTPeriphID4), offset 0xFD0  |     |

| Register 14:  | UART Peripheral Identification 5 (UARTPeriphID5), offset 0xFD4  |     |

| Register 15:  | UART Peripheral Identification 6 (UARTPeriphID6), offset 0xFD8  |     |

| Register 16:  | UART Peripheral Identification 7 (UARTPeriphID7), offset 0xFDC  |     |

| Register 17:  | UART Peripheral Identification 0 (UARTPeriphID0), offset 0xFE0  |     |

| Register 18:  | UART Peripheral Identification 1 (UARTPeriphID1), offset 0xFE4  |     |

| Register 19:  | UART Peripheral Identification 2 (UARTPeriphID2), offset 0xFE8  |     |

| Register 20:  | UART Peripheral Identification 3 (UARTPeriphID3), offset 0xFEC  |     |

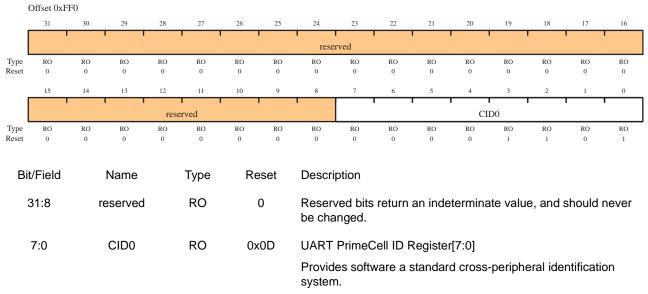

| Register 21:  | UART PrimeCell Identification 0 (UARTPCellID0), offset 0xFF0    |     |

| Register 22:  | UART PrimeCell Identification 1 (UARTPCellID1), offset 0xFF4    |     |

| Register 23:  | UART PrimeCell Identification 2 (UARTPCellID2), offset 0xFF8    |     |

| Register 24:  | UART PrimeCell Identification 3 (UARTPCellID3), offset 0xFFC    |     |

| Synchronou    | is Serial Interface (SSI)                                       |     |

| Register 1:   | SSI Control 0 (SSICR0), offset 0x000                            |     |

| Register 2:   | SSI Control 1 (SSICR1), offset 0x004                            |     |

| Register 3:   | SSI Data (SSIDR), offset 0x008                                  |     |

| Register 4:   | SSI Status (SSISR), offset 0x00C                                |     |

| Register 5:   | SSI Clock Prescale (SSICPSR), offset 0x010                      |     |

| Register 6:   | SSI Interrupt Mask (SSIIM), offset 0x014                        |     |

| Register 7:   | SSI Raw Interrupt Status (SSIRIS), offset 0x018                 |     |

| Register 8:   | SSI Masked Interrupt Status (SSIMIS), offset 0x01C              |     |

| Register 9:   | SSI Interrupt Clear (SSIICR), offset 0x020                      |     |

| Register 10:  | SSI Peripheral Identification 4 (SSIPeriphID4), offset 0xFD0    |     |

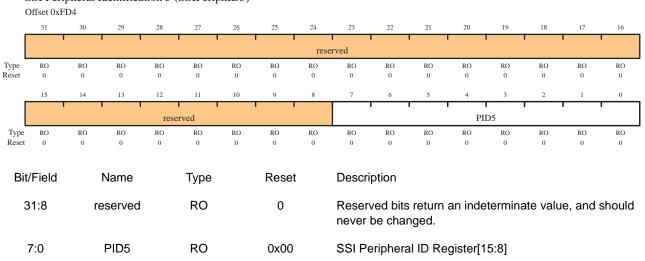

| Register 11:  | SSI Peripheral Identification 5 (SSIPeriphID5), offset 0xFD4    |     |

| Register 12:  | SSI Peripheral Identification 6 (SSIPeriphID6), offset 0xFD8    |     |

| Register 13:  | SSI Peripheral Identification 7 (SSIPeriphID7), offset 0xFDC    |     |

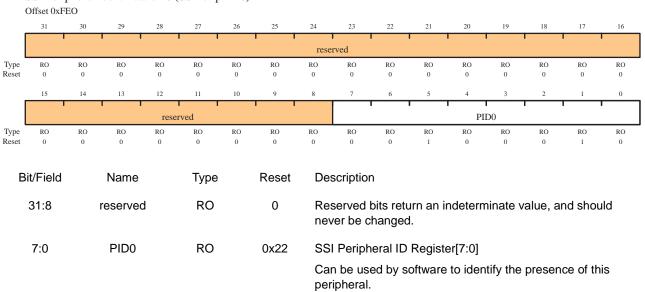

| Register 14:  | SSI Peripheral Identification 0 (SSIPeriphID0), offset 0xFE0    |     |

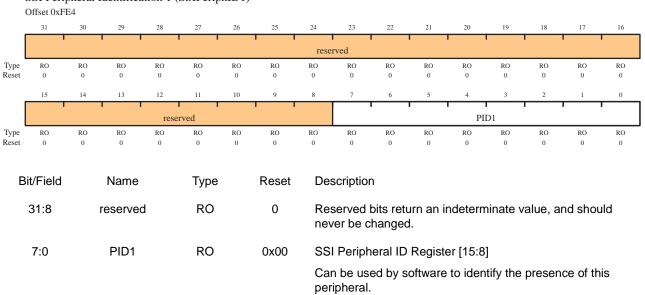

| Register 15:  | SSI Peripheral Identification 1 (SSIPeriphID1), offset 0xFE4    |     |

| Register 16:  | SSI Peripheral Identification 2 (SSIPeriphID2), offset 0xFE8    |     |

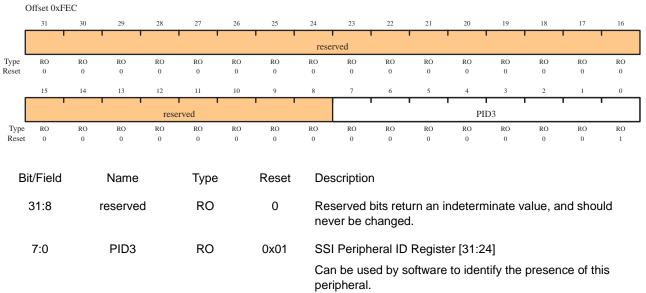

| Register 17:  | SSI Peripheral Identification 3 (SSIPeriphID3), offset 0xFEC    |     |

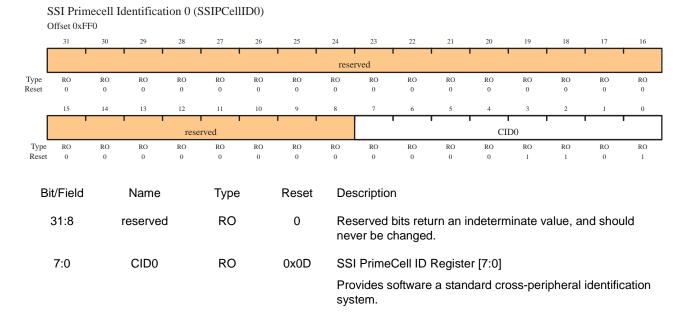

| Register 18:  | SSI PrimeCell Identification 0 (SSIPCellID0), offset 0xFF0      |     |

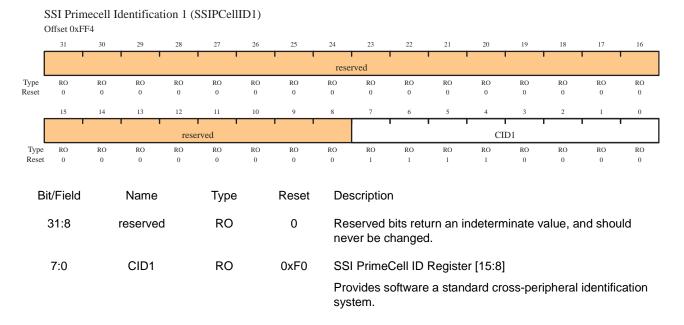

| Register 19:  | SSI PrimeCell Identification 1 (SSIPCellID1), offset 0xFF4      |     |

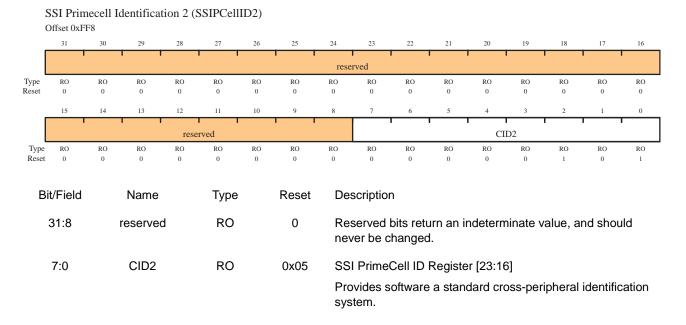

| Register 20:  | SSI PrimeCell Identification 2 (SSIPCellID2), offset 0xFF8      |     |

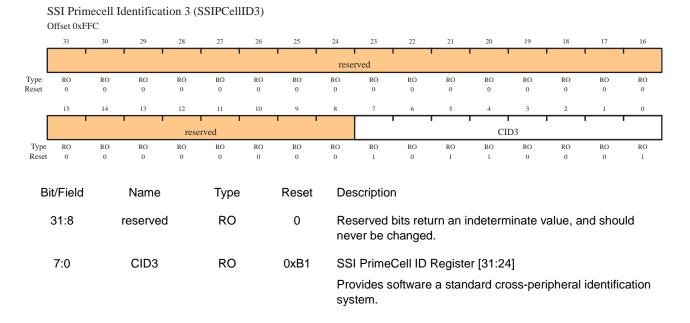

| Register 21:  | SSI PrimeCell Identification 3 (SSIPCellID3), offset 0xFFC      |     |

| Inter-Integra | ted Circuit (I2C) Interface                                     | 302 |

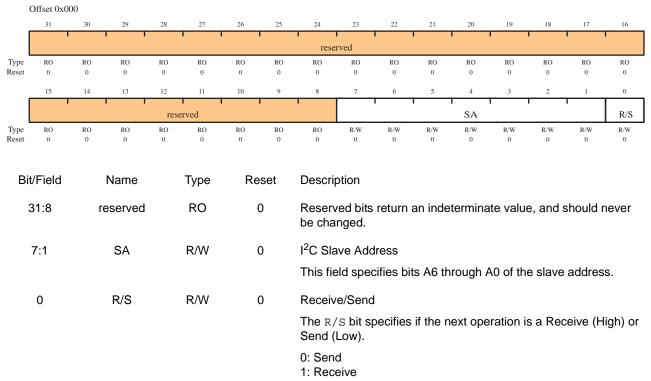

| Register 1:   | I2C Master Slave Address (I2CMSA), offset 0x000                 |     |

| Register 2:   | I2C Master Control/Status (I2CMCS), offset 0x004                |     |

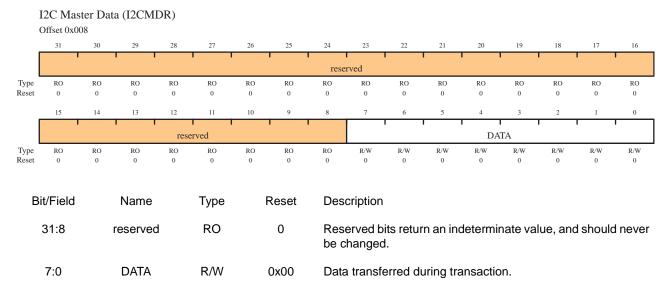

| Register 3:  | I2C Master Data (I2CMDR), offset 0x008                                  |     |

|--------------|-------------------------------------------------------------------------|-----|

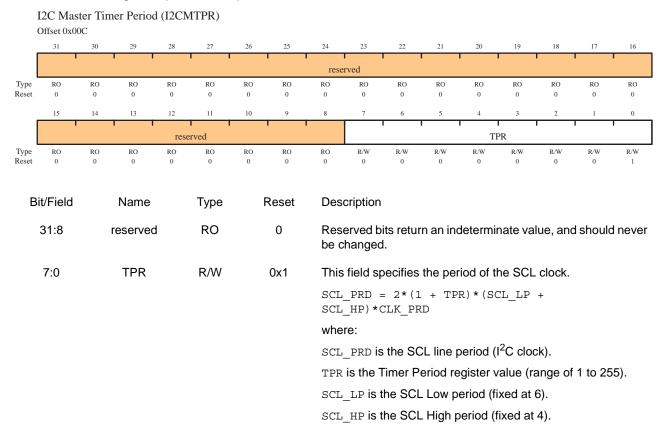

| Register 4:  | I <sup>2</sup> C Master Timer Period (I2CMTPR), offset 0x00C            |     |

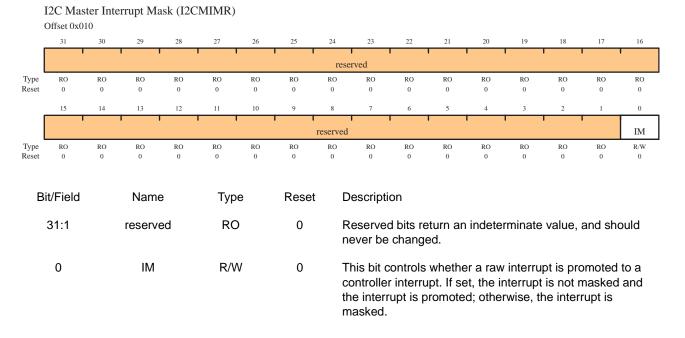

| Register 5:  | I <sup>2</sup> C Master Interrupt Mask (I2CMIMR), offset 0x010          |     |

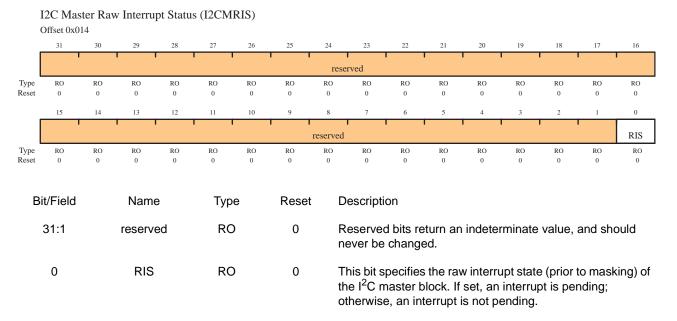

| Register 6:  | I <sup>2</sup> C Master Raw Interrupt Status (I2CMRIS), offset 0x014    |     |

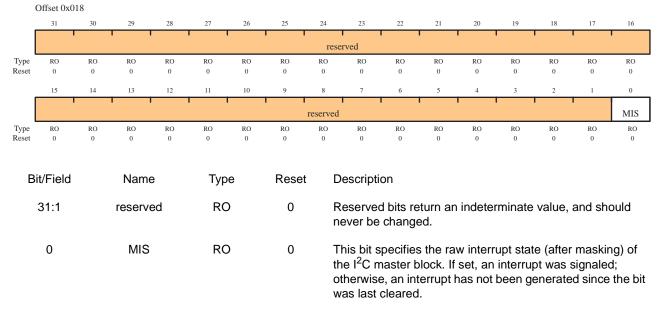

| Register 7:  | I <sup>2</sup> C Master Masked Interrupt Status (I2CMMIS), offset 0x018 |     |

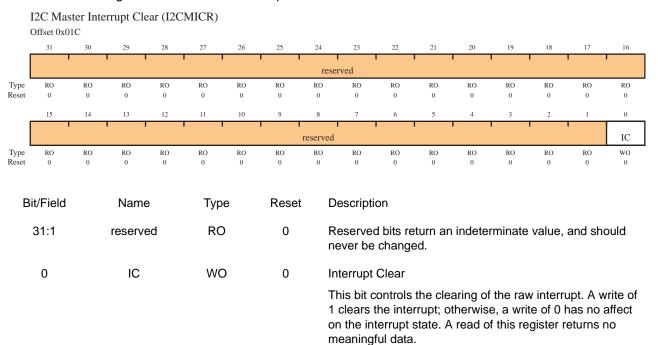

| Register 8:  | I <sup>2</sup> C Master Interrupt Clear (I2CMICR), offset 0x01C         |     |

| Register 9:  | I <sup>2</sup> C Master Configuration (I2CMCR), offset 0x020            |     |

| Register 10: | I <sup>2</sup> C Slave Own Address (I2CSOAR), offset 0x000              |     |

| Register 11: | I <sup>2</sup> C Slave Control/Status (I2CSCSR), offset 0x004           |     |

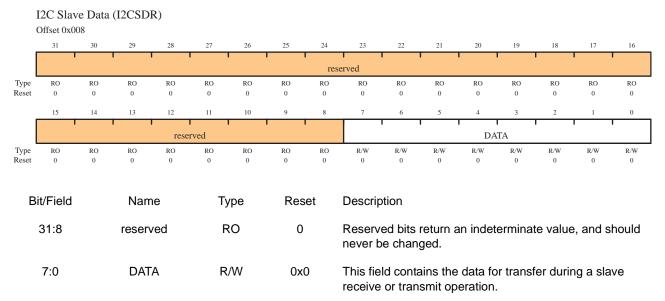

| Register 12: | I <sup>2</sup> C Slave Data (I2CSDR), offset 0x008                      |     |

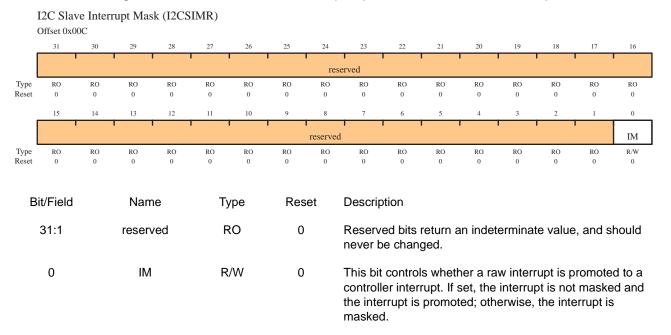

| Register 13: | I <sup>2</sup> C Slave Interrupt Mask (I2CSIMR), offset 0x00C           |     |

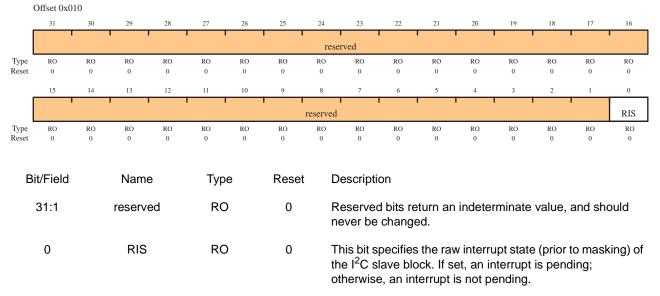

| Register 14: | I <sup>2</sup> C Slave Raw Interrupt Status (I2CSRIS), offset 0x010     | 331 |

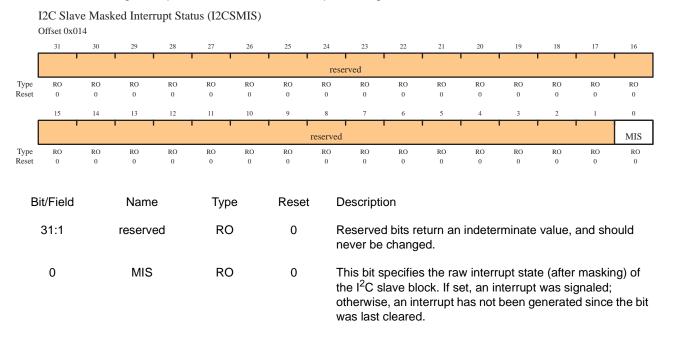

| Register 15: | I <sup>2</sup> C Slave Masked Interrupt Status (I2CSMIS), offset 0x014  |     |

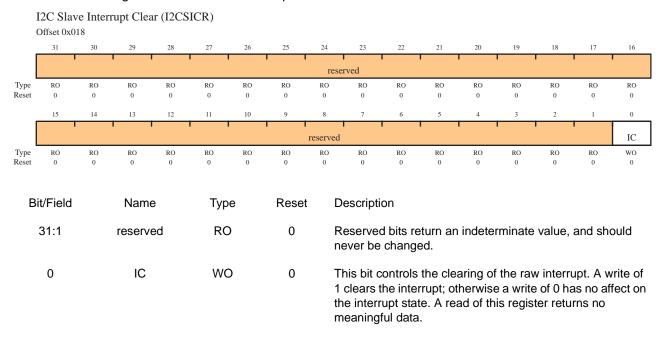

| Register 16: | I <sup>2</sup> C Slave Interrupt Clear (I2CSICR), offset 0x018          |     |

| •            | parator                                                                 |     |

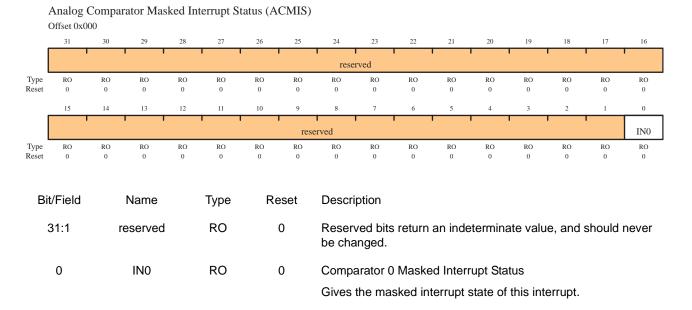

| Register 1:  | Analog Comparator Masked Interrupt Status (ACMIS), offset 0x00          |     |

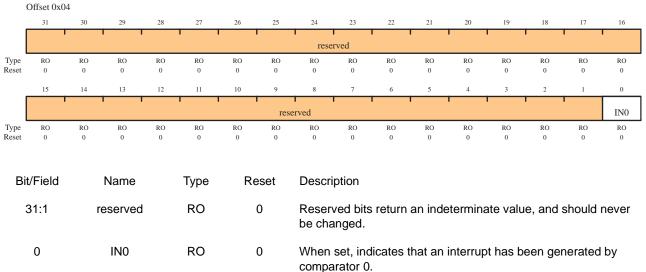

| Register 1:  | Analog Comparator Raw Interrupt Status (ACRIS), offset 0x04             |     |

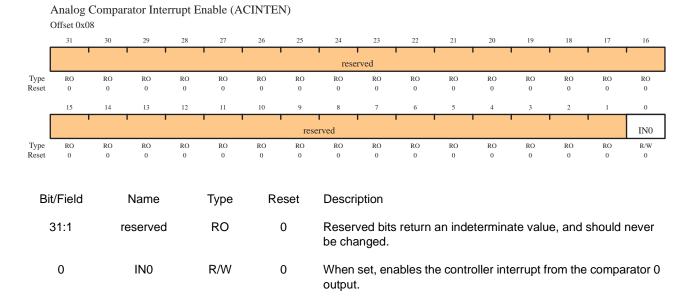

| -            | Analog Comparator Interrupt Enable (ACINTEN), offset 0x04               |     |

| Register 3:  |                                                                         |     |

| Register 4:  | Analog Comparator Reference Voltage Control (ACREFCTL), offset 0x10     |     |

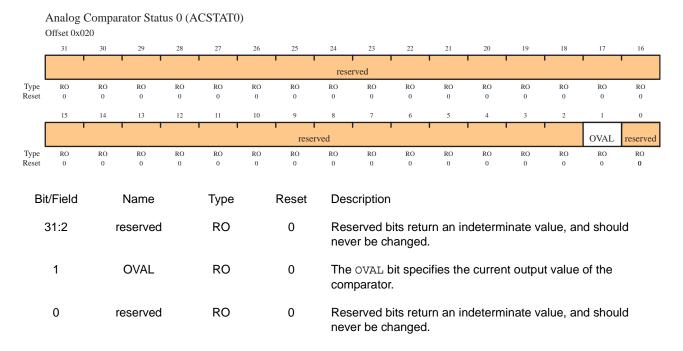

| Register 5:  | Analog Comparator Status 0 (ACSTAT0), offset 0x20                       |     |

| Register 6:  | Analog Comparator Control 0 (ACCTL0), offset 0x24                       |     |

|              | Modulator (PWM)                                                         |     |

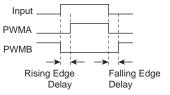

| Register 1:  | PWM Master Control (PWMCTL), offset 0x000                               |     |

| Register 2:  | PWM Time Base Sync (PWMSYNC), offset 0x004                              |     |

| Register 3:  | PWM Output Enable (PWMENABLE), offset 0x008                             |     |

| Register 4:  | PWM Output Inversion (PWMINVERT), offset 0x00C                          |     |

| Register 5:  | PWM Output Fault (PWMFAULT), offset 0x010                               |     |

| Register 6:  | PWM Interrupt Enable (PWMINTEN), offset 0x014                           |     |

| Register 7:  | PWM Raw Interrupt Status (PWMRIS), offset 0x018                         |     |

| Register 8:  | PWM Interrupt Status and Clear (PWMISC), offset 0x01C                   | 359 |

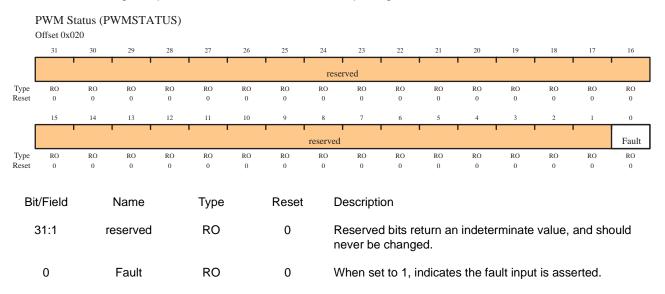

| Register 9:  | PWM Status (PWMSTATUS), offset 0x020                                    |     |

| Register 10: | PWM0 Control (PWM0CTL), offset 0x040                                    |     |

| Register 11: | PWM1 Control (PWM1CTL), offset 0x080                                    |     |

| Register 12: | PWM0 Interrupt/Trigger Enable (PWM0INTEN), offset 0x044                 |     |

| Register 13: | PWM1 Interrupt/Trigger Enable (PWM1INTEN), offset 0x084                 |     |

| Register 14: | PWM0 Raw Interrupt Status (PWM0RIS), offset 0x048                       |     |

| Register 15: | PWM1 Raw Interrupt Status (PWM1RIS), offset 0x088                       |     |

| Register 16: | PWM0 Interrupt Status and Clear (PWM0ISC), offset 0x04C                 |     |

| Register 17: | PWM1 Interrupt Status and Clear (PWM1ISC), offset 0x08C                 |     |

| Register 18: | PWM0 Load (PWM0LOAD), offset 0x050                                      |     |

| Register 19: | PWM1 Load (PWM1LOAD), offset 0x090                                      |     |

| Register 20: | PWM0 Counter (PWM0COUNT), offset 0x054                                  |     |

| Register 21: | PWM1 Counter (PWM1COUNT), offset 0x094                                  |     |

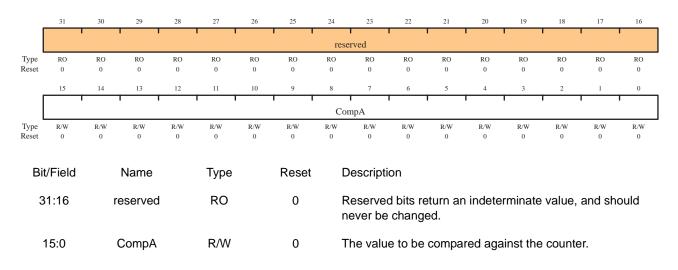

| Register 22: | PWM0 Compare A (PWM0CMPA), offset 0x058                                 |     |

| Register 23: | PWM1 Compare A (PWM1CMPA), offset 0x098                                 |     |

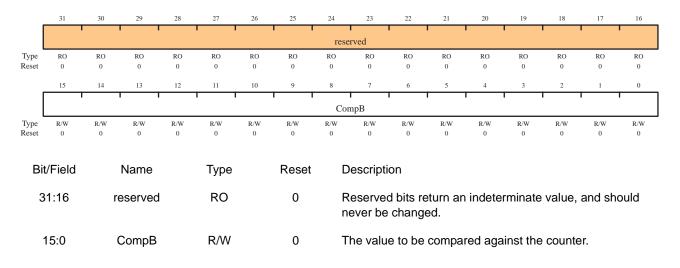

| Register 24: | PWM0 Compare B (PWM0CMPB), offset 0x05C                                 |     |

| Register 25: | PWM1 Compare B (PWM1CMPB), offset 0x09C                                 |     |

| Register 26: | PWM0 Generator A Control (PWM0GENA), offset 0x060                       |     |

| Register 27: | PWM1 Generator A Control (PWM1GENA), offset 0x0A0                       |     |

| Register 28:  | PWM0 Generator B Control (PWM0GENB), offset 0x064                 |  |

|---------------|-------------------------------------------------------------------|--|

| Register 29:  | PWM1 Generator B Control (PWM1GENB), offset 0x0A4                 |  |

| Register 30:  | PWM0 Dead-Band Control (PWM0DBCTL), offset 0x068                  |  |

| Register 31:  | PWM1 Dead-Band Control (PWM1DBCTL), offset 0x0A8                  |  |

| Register 32:  | PWM0 Dead-Band Rising-Edge Delay (PWM0DBRISE), offset 0x06C       |  |

| Register 33:  | PWM1 Dead-Band Rising-Edge Delay (PWM1DBRISE), offset 0x0AC       |  |

| Register 34:  | PWM0 Dead-Band Falling-Edge-Delay (PWM0DBFALL), offset 0x070      |  |

| Register 35:  | PWM1 Dead-Band Falling-Edge-Delay (PWM1DBFALL), offset 0x0B0      |  |

| rtogiotor oo. | T With Boad Band Failing Eage Boldy (FWith BBF AEE), enout except |  |

# **Revision History**

This table provides a summary of the document revisions.

| Date         | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2006     | 00       | Initial public release of LM3S301, LM3S310, LM3S315, and LM3S316 data sheets.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| July 2006    | 01       | Second release of LM3S301, LM3S310, LM3S315, and LM3S316 data sheets. Includes the following changes:                                                                                                                                                                                                                                                                                                                                                                                                  |

|              |          | <ul> <li>Added initialization and configuration content into PWM, I2C, Comparators, and JTAG chapters.</li> <li>Modified MAXADCSPD bit description to show how to set speed lower.</li> <li>Clarified that peripheral clock must be set before enabling peripherals in "Initialization and Configuration" sections.</li> </ul>                                                                                                                                                                         |

| October 2006 | 02       | Third release of LM3S301, LM3S310, LM3S315, and LM3S316 data sheets. Includes the following changes:                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |          | <ul> <li>Added information on hardware averaging to the ADC chapter.</li> <li>Updated the clocking examples in the I2C chapter.</li> <li>Added Serial Flash Loader usage information.</li> <li>Added "5-V-tolerant" description for GPIOs to feature list, GPIO chapter, and Electrical chapter.</li> <li>Added maximum values for 20 MHz and 25 MHz parts to Table 9-1, "16-Bit</li> </ul>                                                                                                            |

|              |          | <ul> <li>Timer With Prescaler Configurations" in the Timers chapter.</li> <li>Made the following changes in the System Control chapter: <ul> <li>Updated field descriptions in the Run-Mode Clock Configuration (RCC) register and the Device Identification 1 (DID1) register.</li> <li>Updated the internal oscillator clock speed.</li> <li>Added the Deep-Sleep Clock Configuration (DSLPCFG) register.</li> <li>Added bus fault information to the clock gating registers.</li> </ul> </li> </ul> |

# **About This Document**

This data sheet provides reference information for the LM3S316 microcontroller, describing the functional blocks of the system-on-chip (SoC) device designed around the ARM® Cortex<sup>™</sup>-M3 core.

## Audience

This manual is intended for system software developers, hardware designers, and application developers.

# **About This Manual**

This document is organized into sections that correspond to each major feature.

# **Related Documents**

The following documents are referenced by the data sheet, and available on the documentation CD or from the Luminary Micro web site at www.luminarymicro.com:

- ARM® Cortex™-M3 Technical Reference Manual

- CoreSight™ Design Kit Technical Reference Manual

- ARM® v7-M Architecture Application Level Reference Manual

The following related documents are also referenced:

IEEE Standard 1149.1-Test Access Port and Boundary-Scan Architecture

This documentation list was current as of publication date. Please check the Luminary Micro web site for additional documentation, including application notes and white papers.

# **Documentation Conventions**

This document uses the conventions shown in Table 0-1.

#### Table 0-1. Documentation Conventions

| Notation                  | Meaning                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General Register Notation |                                                                                                                                                                                                                                                                                                                                                                                 |  |

| REGISTER                  | APB registers are indicated in uppercase bold. For example,<br><b>PBORCTL</b> is the Power-On and Brown-Out Reset Control register. If<br>a register name contains a lowercase n, it represents more than one<br>register. For example, <b>SRCRn</b> represents any (or all) of the three<br>Software Reset Control registers: <b>SRCR0</b> , <b>SRCR1</b> , and <b>SRCR2</b> . |  |

| bit                       | A single bit in a register.                                                                                                                                                                                                                                                                                                                                                     |  |

| bit field                 | Two or more consecutive and related bits.                                                                                                                                                                                                                                                                                                                                       |  |

| offset 0x <i>nnn</i>      | A hexadecimal increment to a register's address, relative to that module's base address as specified in Table 3-1, "Memory Map," on page 37.                                                                                                                                                                                                                                    |  |

| Table 0-1. Do | umentation Conventions |

|---------------|------------------------|

|---------------|------------------------|

| Notation                       | Meaning                                                                                                                                                                                                                                                                |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register N                     | Registers are numbered consecutively throughout the document to aid in referencing them. The register number has no meaning to software.                                                                                                                               |

| reserved                       | Register bits marked reserved are reserved for future use. Reserved bits return an indeterminate value, and should never be changed. Only write a reserved bit with its current value.                                                                                 |

| yy:xx                          | The range of register bits inclusive from xx to yy. For example, 31:15 means bits 15 through 31 in that register.                                                                                                                                                      |