# MOS INTEGRATED CIRCUIT $\mu$ PD161622

# 396 OUTPUT TFT-LCD SOURCE DRIVER WITH RAM

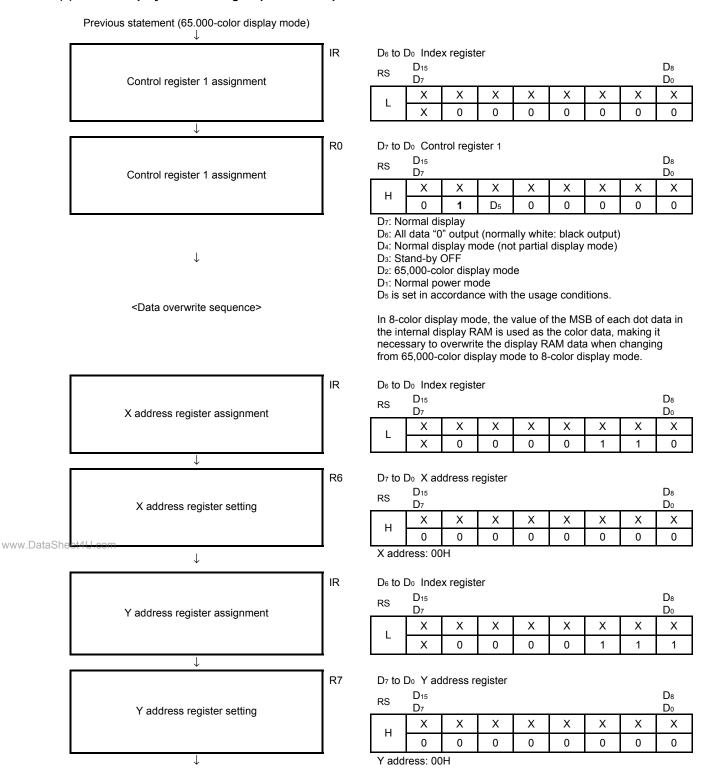

### **DESCRIPTION**

The  $\mu$  PD161622 is a TFT-LCD source driver that includes display RAM.

This driver has 396 outputs, a display RAM capacity of 371,712 bits (132 pixels x 16 bits x 176 lines) and, can provide a 65,536-color display.

### **FEATURES**

- TFT-LCD driver with on-chip display RAM

- Logic power supply voltage: 2.5 to 3.6 V

- Driver power supply voltage: 4.3 to 5.5 V

- Display RAM: 132 x 16 x 176 bits

- Driver outputs: 396 output

- CPU interface: Serial, 8-bit/16-bit parallel interface selectable

- Colors: 65,536 colors/pixel

- On-chip VCOM generator

- · On-chip timing generator

- · On-chip oscillator

## ORDERING INFORMATION

| www.DataSheet4U. Part Number | Package |

|------------------------------|---------|

| μ PD161622P                  | Chip    |

**Remark** Purchasing the above chip entails the exchange of documents such as a separate memorandum or product quality, so please contact one of our sales representatives.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

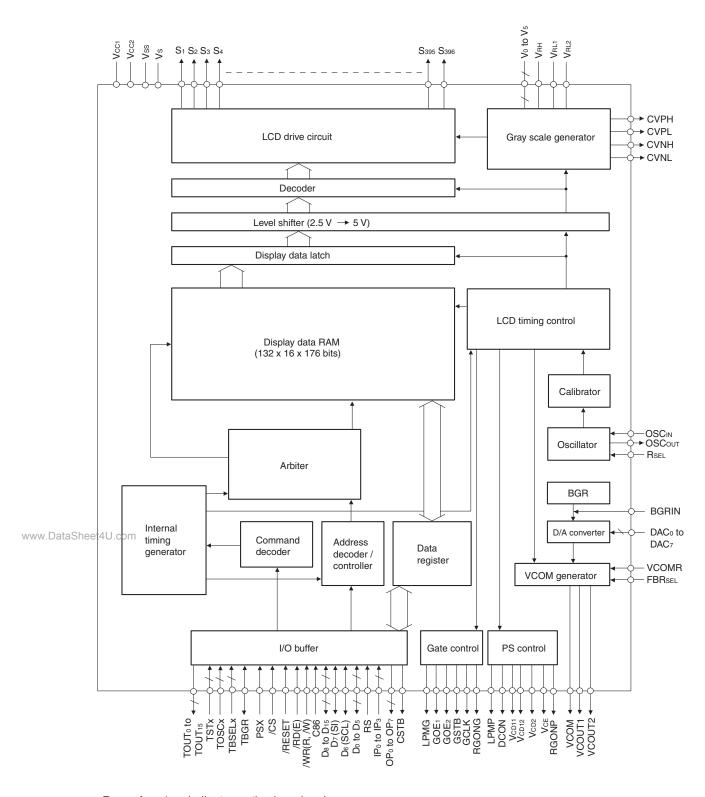

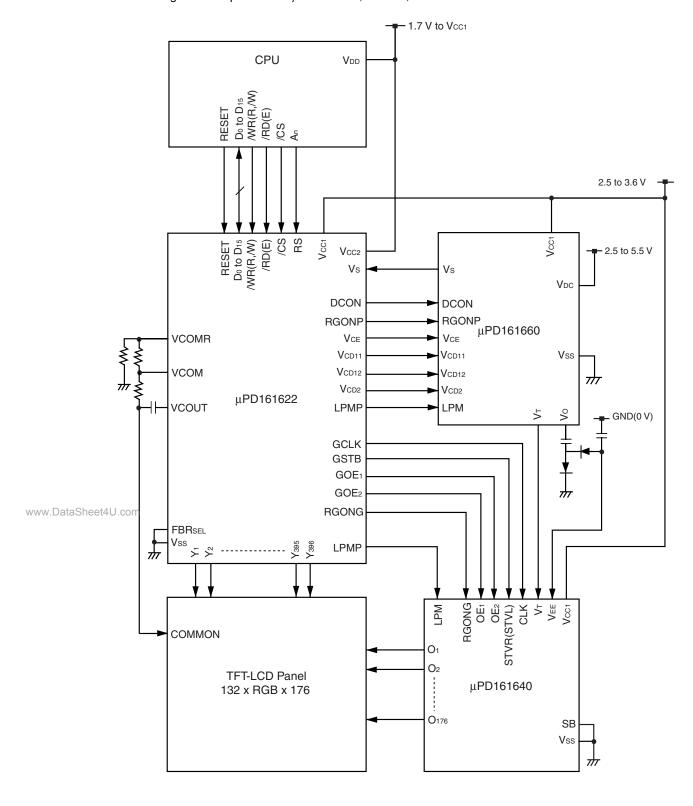

### 1. BLOCK DIAGRAM

**Remark** /xxx indicates active low signal.

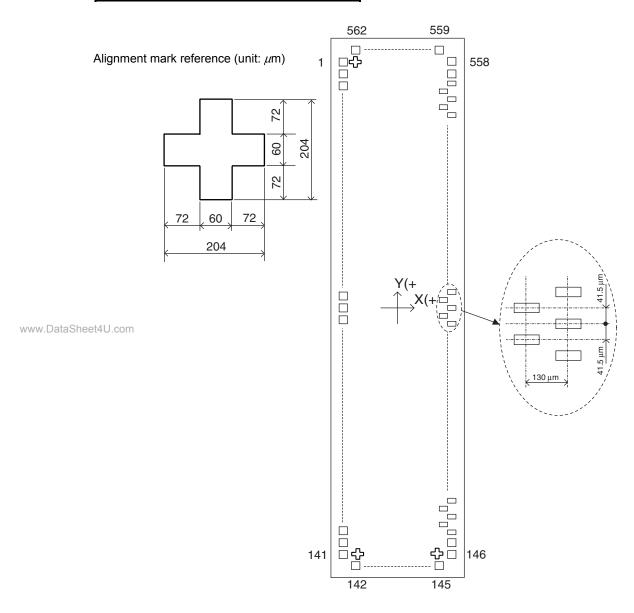

# 2. PIN CONFIGURATION (Pad Layout)

Chip size: 3.60 x 17.80 mm<sup>2</sup> TYP.

Bump size (output type A): 35 x 94  $\mu$ m<sup>2</sup> TYP. Bump size (input & dummy): 80 x 86  $\mu$ m<sup>2</sup> TYP.

Alignment mark (mark center, unit: μm)

|    | Х     | Υ     |

|----|-------|-------|

| M1 | -1615 | 8715  |

| M2 | -1615 | -8715 |

| M3 | 1435  | -8715 |

Table 2-1. Pad Layout (1/4)

| Rhl            | No. PinNa | ne PadTypa | e X[µm]              | Y[μm]              | FinNa      | PinName              | PadType | Χ[μη]                | Υ[μη]                | FinNo      | RinNane      | Pad Type | X[µn]              | Y[μm]                 |

|----------------|-----------|------------|----------------------|--------------------|------------|----------------------|---------|----------------------|----------------------|------------|--------------|----------|--------------------|-----------------------|

| 1              |           | В          | -1674.00             |                    | ଖ          | VŒ.                  | В       | -1674.00             | 119000               | 121        | OF5          | В        | -1674.00           | -6010.00              |

| 2              |           | В          | -1674.00             |                    | 62         | V022                 | В       | -1674.00             | 1070.00              | 122        | OP6          | В        | -1674.00           | -6130.00              |

| 3              |           | В          | -1674.00             |                    | 63         | VOD12                | В       | -1674.00             | 95000                | 123        | 097          | В        | -1674.00           | -6250.00              |

| 4              |           | В          | -1674.00             | 8030.00            | 64         | VOD11                | В       | -1674.00             | 830.00               | 124        | VCCI(MOD     | В        | -1674.00           | -6370.00              |

| 5              |           | В          | -1674.00             | 7910.00            | 65         | LFMP                 | В       | -1674.00             | 71000                | 125        | F0           | В        | -1674.00           | -6490.00              |

| 6              |           | В          | -1674.00             | 7790.00            | 66         | R30AP                | В       | -1674.00             | 59000                | 126        | VSS(MODE     | В        | -1674.00           | -6610.00              |

| 7              |           | В          | -1674.00             | 7670.00            | 67         | DCON                 | В       | -1674.00             | 47000                | 127        | Pl           | В        | -1674.00           | -6730.00              |

| 8              |           | В          | -1674.00             | 7550.00            | 68         | VCOUT2               | В       | -1674.00             | 350,00               | 128        | VCCI(MOD     | В        | -1674.00           | -6850.00              |

| 9              |           | В          | -1674.00             |                    | 69         | VSS                  | В       | -1674.00             | 23000                | 129        | F2           | В        | -1674.00           | -6970.00              |

| 10             |           | В          | -1674.00             | 7310.00            | 70         | VCC2                 | В       | -1674.00             | 11000                | 130        | VSS(MODE     | 1        | -1674.00           | -7090.00              |

| 11             |           | В          | -1674.00             | 7190.00            | 71         | VCCI                 | В       | -1674.00             | -1000                | 131        | P3           | В        | -1674.00           | -721000               |

| 12             |           | В          | -1674.00             | 7070.00            | 72         | VSS                  | В       | -1674.00             | -13000               | 132        | VCCI(MOD     | В        | -1674.00           | -7330.00              |

| 13             |           | В          | -1674.00             | 6950.00            | 73         | VSS                  | В       | -1674.00             | -25000               | 133        | GSTB         | В        | -1674.00           | -7450.00              |

| 1/             |           | В          | -1674.00             |                    | 74         | CML                  | В       | -1674.00             | -370.00              | 134        | GO!K         | В        | -1674.00           | -7570.00              |

| 15             |           | В          | -1674.00             |                    | 75         | CVVH                 | В       | -1674.00             | -490.00              | 135        | GOE1         | В        | -1674.00           | -7690.00              |

| 16             |           | В          | -1674.00             | 659000             | <b>7</b> 6 | CVPL                 | В       | -1674.00             | -610.00              | 136        | GOE2         | В        | -1674.00           | -7810.00              |

| 17             |           | В          | -1674.00             | 6470.00            | 77         | CVPH                 | B       | -1674.00             | -73000               | 137        | R30NG        | B        | -1674.00           | -7930.00              |

| 18             |           | В          | -1674.00             | 6350.00            | <b>7</b> 8 | VS                   | В       | -1674.00             | -850.00              | 138        | LFMG         | B        | -1674.00           | -8050.00              |

| 19             |           | В          | -1674.00             |                    | 79         | VS                   | В       | -1674.00             | -970.00              | 139        | DUMNY        | B<br>_   | -1674.00           | -8170.00              |

| 2              |           | 4          | -1674.00             |                    | 80         | VSS                  | B       | -1674.00             | -1090.00             | 140        | DUMNY        | B        | -1674.00           | -8290.00              |

| 2              |           |            | -1674.00             | 599000             | 81         | V00J1                | В       | -1674.00             | -121000              | 141        | DUMNY        | В        | -1674.00           | -8410.00              |

| 2              |           |            | -1674.00             | 5870.00            | 82         | VCOUT1               | В       | -1674.00             | -1330.00             | 142        | DUMNY        | В        | -1350.00           | -8774.00              |

| 2              |           |            | -1674.00             | 5750.00            | 83         | VCCI                 | В       | -1674.00             | -1450.00             | 143        | DUMY         | В        | -510.00            | -8774.00              |

| 24             |           |            | -1674.00             | 5630.00            | 84         | VCCI                 | В       | -1674.00             | -1570.00             | 144        | DUMNY        | В        | 330.00             | -8774.00              |

| 2              |           | В          | -1674.00             | 5510.00            | 85         | VCOM                 | В       | -1674.00             | -1690.00             | 145        | DUMNY        | В        | 1170.00            | -8774.00              |

| 2              |           | В          | -1674.00             | 5390.00            | 86         | DJMNY                | В       | -1674.00             | -1810.00             | 146        | DUMNY        | В        | 1670.00            | -8600.00              |

| 27             |           |            | -1674.00             | 5270.00            | 87         | DJMY                 | В       | -1674.00             | -1930.00             | 147        | DMY          | A        | 1670.00            | -8520.00              |

| 28             |           | В          | -1674.00             | 5150.00            | 88         | VSS(MODE             |         | -1674.00             | -2050.00             | 148        | DJMY         | A        | 1540.00            | -8478.50              |

| 2              |           |            | -1674.00             | 5030.00            | 89         | VCOMR                | В       | -1674.00             | -2170.00             | 149        | S396         | A        | 1670.00            | -8437.00              |

| 3              |           |            | -1674.00             | 4910.00            | 90         | BORN<br>N COVIA      | В       | -1674.00             | -229000              | 150        | S395         | A        | 1540.00            | -8395.50              |

| 3              |           |            | -1674.00             | 4790.00            | 91         | VCCI(MOD             |         | -1674.00             | -2410.00             | 151        | S394         | A        | 1670.00            | -8354.00              |

| 32             |           | В          | -1674.00             | 4670.00            | 92         | HB-88IL              | В       | -1674.00             | -253000              | 152        | S393         | A        | 1540.00            | -831250               |

| 3              |           |            | -1674.00             |                    | 93         | VSS(MODE             |         | -1674.00             | -2650.00             | 153        | S392         | A        | 1670.00            | -8271.00              |

| 34             |           | В          | -1674.00             | 443000             | 94         | VRH                  | В       | -1674.00             | -2770.00             | 154        | S391         | A        | 1540.00            | -8229.50              |

| 3.             |           | В          | -1674.00             | 431000             | 95         | V0                   | В       | -1674.00             | -2890.00             | 155        | S390         | A        | 1670.00            | -8188.00              |

| 33             |           | В          | -1674.00             | 4190.00            | 96         | V1                   | В       | -1674.00             | -301000              | 156        | S389         | A        | 1540.00            | -8146.50              |

| 37             |           | В          | -1674.00             | 4070.00            | 97         | V2                   | В       | -1674.00             | -313000              | 157        | S388         | A        | 1670.00            | -810500               |

| 3              |           | В          | -1674.00             | 3950.00            | 98         | V3<br>V4             | В       | -1674.00             | -325000              | 158        | S387         | A        | 1540.00            | -806350<br>           |

| 3              |           | В          | -1674.00             |                    | 99         | V <del>4</del><br>V5 | В       | -1674.00             | -337000              | 159        | S386         | A        | 1670.00            | -802200               |

| 40             |           | В          | -1674.00             |                    | 100        |                      | В       | -1674.00<br>-1674.00 | -3490.00<br>2010.00  | 160        | S385         | A        | 1540.00            | -7980.50              |

| 41             |           | В          | -1674.00<br>1674.00  | 3590.00<br>3470.00 | 101<br>102 | VR1<br>VR2           | B<br>B  |                      | -361000              | 161<br>162 | S384<br>S383 | A        | 1670.00<br>1540.00 | -7939.00<br>-7897.50  |

| 4              |           | B<br>B     | -1674.00<br>-1674.00 |                    | 103        | VH2<br>VSSMODE       |         | -1674.00<br>-1674.00 | -3730.00<br>-3850.00 | 163        | 2385         | A<br>A   | 1540.00<br>1670.00 | -785600               |

| 4              |           |            | -1674.00             | 3230.00            | 104        | VSS(WULE)            | В       | -1674.00             | -3970.00             | 164        | S381         | A        | 1540.00            | -7814.50              |

| 45             |           | В          | -1674.00             |                    | 105        | TBSH2                | В       | -1674.00             | -39/000<br>-4090.00  | 165        | S380         | A        | 1670.00            | -7674300<br>-777300   |

| 46             |           | В          | -1674.00             |                    | 106        | TBOR                 | В       | -1674.00             | -421000              | 166        | S379         | A        | 1540.00            |                       |

| 47             |           | В          | -1674.00             |                    | 107        | DAC7                 | В       | -1674.00             | -4330.00             | 167        | S378         | A        | 1670.00            | -7731.30<br>-7690.00  |

| 46             |           | В          | -1674.00             |                    | 108        | DAG6                 | В       | -1674.00             | -4450.00             | 168        | S377         | A        | 1540.00            | -764850               |

| 4              |           | В          | -1674.00             | 3                  | 109        | DAC5                 | В       | -1674.00             | -4570.00             | 169        | S376         | A        | 1670.00            | -7607.00              |

| 5              |           | В          | -1674.00             |                    | 110        | DAC4                 | В       | -1674.00             | -4690.00             | 170        | S375         | A        | 1540.00            | -7607.00<br>-7565.50  |

| 5<br>5         |           |            | -1674.00             |                    | 111        | DAC3                 | В       | -1674.00             | -4810.00             | 171        | S374         | A        | 1670.00            | -7524.00              |

| 5              |           | В          | -1674.00             |                    | 112        | DAC2                 | В       | -1674.00             | -4930.00             | 172        | S373         | A        | 1540.00            | -7324.00<br>-7482.50  |

| 5              |           | В          | -1674.00             |                    | 113        | DACI                 | В       | -1674.00             | -5050.00             | 173        | S372         | A        | 1670.00            | -7441.00              |

| 5/             |           | В          | -1674.00             |                    | 114        | DACO                 | В       | -1674.00             | -5170.00             | 174        | S371         | A        | 1540.00            | -7 <del>44</del> 1.00 |

| 5 <del>.</del> |           |            | -1674.00             |                    | 115        | VSS(MODE             |         | -1674.00             | -51/UW<br>-5290.00   | 175        | S370         | A        | 1670.00            |                       |

| 56             |           | y B        | -1674.00             |                    | 116        | 070<br>070           | В       | -1674.00             | -529000<br>-5410.00  | 176        | S369         | A        | 1540.00            | -73316.50             |

| 5              |           | В          | -1674.00             |                    | 117        | OP1                  | В       | -1674.00             | -553000              | 177        | S368         | A        | 1670.00            | -731033<br>-727500    |

| 55<br>55       |           | В          | -1674.00             |                    | 118        | OP2                  | В       | -1674.00             | -555000              | 178        | S367         | A        | 1540.00            | -723350<br>-723350    |

| α              | √صا ر     |            |                      |                    | 119        | 0P3                  | В       | -1674.00             | -5000<br>-577000     | 179        | S366         | A        | 1670.00            | -743330<br>-719200    |

| п              | ) (PE     |            | _16////              |                    |            |                      |         |                      |                      |            |              |          |                    |                       |

| 55<br>60       |           | DE B       | -1674.00<br>-1674.00 |                    | 120        | O24                  | В       | -1674.00             | -589000              | 180        | S365         | A        | 1540.00            | -7150.50              |

www.DataSheet4U.co

Table 2-1. Pad Layout (2/4)

| PinNa.              | PinName      | PadType     | X[µm]              | Y[µm]                | ₽nNb                       | PinName           | PadType  | X[µm]              | Y[µm]                | PinNb.     | PinName       | PadType     | X[µm]              | Y[µm]                        |

|---------------------|--------------|-------------|--------------------|----------------------|----------------------------|-------------------|----------|--------------------|----------------------|------------|---------------|-------------|--------------------|------------------------------|

| 181                 | S364         | Α           | 1670.00            | -710900              | 241                        | S304              | A        | 1670.00            | -4619.00             | 301        | S244          | Α           | 1670.00            | -212900                      |

| 182                 | S363<br>S362 | Α           | 1540.00            | -7067.50             | 242                        | S303<br>S302      | A        | 1540.00            | -4577.50             | 302<br>303 | S243<br>S242  |             | 1540.00            | -2087.50<br>-2046.00         |

| 183                 | S362         | A<br>A      | 1670.00            | -/(126(I)            | 243                        | S302              | A        | 1670.00            | -4536.00             | 303        | S242          | A<br>A<br>A | 1670.00            | -2046.00                     |

| 184                 | S361         | Α           | 1540.00            | -698450              | 244                        | S301              | A        | 1540.00            | -4494.50             | 304        | S241          | Α           | 1540.00            | -2004.50                     |

| 185                 | S360         | Α           | 1670.00            | -694300              | 245                        | S300              | A        | 1670.00            | -445300              | 305        | S240          | A           | 1670.00            | -1963.00                     |

| 186                 | S359         | Α           | 1540.00            | -6901.50             | 246                        | S299              | A        | 1540.00            | -4411.50             | 306        | S239          | А           | 1540.00            | -1921.50                     |

| 187                 | S358         | Α           | 1670.00            | -6860.00             | 247                        | S298              | A        | 1670.00            | -4370.00             | 307        | S238          | A<br>A      | 1670.00            | -1880.00                     |

| 188                 | S367         | A           | 1540.00            | -681850              | 248                        | S297              | A        | 1540.00            | -4328.50             | 308        | S237          |             | 1540.00            | -1838.50                     |

| 189                 | S366         | A           | 1670.00            | -6777.00             | 249                        | S296              | A        | 1670.00            | -4287.00             | 309        | S236          | A           | 1670.00            | -1797.00                     |

| 190<br>191          | S365         | А           | 1540.00<br>1670.00 | -673550              | 250<br>251                 | S295<br>S294      | A        | 1540.00<br>1670.00 | -4245.50<br>-4204.00 | 310<br>311 | S235<br>S234  | А           | 1540.00<br>1670.00 | -1755.50                     |

| 191<br>192          | S364<br>S363 | A<br>A      | 1670.00<br>1540.00 | -669400<br>-665250   | 251<br>252                 | S294<br>S293      | A        | 16/00              | -4204.00<br>-4162.50 | 311<br>312 | S234<br>S233  | A<br>A      | 1670.00<br>1540.00 | -1714.00<br>-1672.50         |

| 192<br>193          |              |             | 1540.00<br>1670.00 |                      |                            | S292              | A        | 1540.00            | -416250<br>-4121.00  |            |               | Α           | 1540.00<br>1670.00 | -167250<br>-1631.00          |

| 194                 | S362<br>S361 | A           | 1540.00            | -6611.00             | 253<br>254                 | S291              | Α        | 1670.00<br>1540.00 | 4079.50              | 313<br>314 | S231          | A           | 1540.00            | -1689.50                     |

| 195                 | S360         | A<br>A<br>A | 1670.00            | -6539.50<br>-6528.00 | 255                        | 2530<br>2530      | Α        | 1670.00            | 403800               | 314        | S230          | A<br>A<br>A | 1670.00            | -1548.00                     |

| 196                 | S349         | A           | 1540.00            | -648650              | 256                        | 2589<br>S280      | A        | 1540.00            | -3996.50             | 316        | S229          | Α           | 1540.00            | -1546.W<br>-1506.50          |

| 197                 | S348         |             | 1670.00            | -644500              | 257                        | 2288<br>S288      | A        | 1670.00            | -395500              | 317        | S228          |             | 1670.00            | -1465.00                     |

| 102                 | S347         | Α Δ         | 1540.00            | -640350              |                            | S287              | A        | 1540.00            | -3913.50             | L          | S227          | Α Δ         | 1540.00            | -1423.50                     |

| 198<br>199          | S346         | Α Α         | 1670.00            | -636200              | 258<br>259                 | S286              | Α Α      | 1670.00            | -387200              | 318<br>319 | S226          | A           | 1670.00            | -138200                      |

| 200                 | S345         | A<br>A      | 1540.00            | -632050              | 260                        | S285              | <u>^</u> | 1540.00            | -3830.50             | 320        | S225          | A<br>A      | 1540.00            | -1340.50                     |

| 201                 | S344         | A           | 1670.00            | -627900              | 261                        | S284              | A        | 1670.00            | -3789.00             | 321        | S224          | A           | 1670.00            | -1299.00                     |

| 202                 | S343         |             | 1540.00            | -6237.50             | 262                        | S283              | <u></u>  | 1540.00            | -374750              | 322        | S223          | A           | 1540.00            | -1257.50                     |

| 203                 | S342         | A<br>A<br>A | 1670.00            | -619600              | 263                        | S782              | A        | 1670.00            | -3706.00             | 323        | S222          |             | 1670.00            | -1216.00                     |

| 204                 | S341         | Α           | 1540.00            | -615450              | 264                        | S281              | A        | 1540.00            | -3664.50             | 324        | S221          | A<br>A      | 1540.00            | -1174.50                     |

| 205                 | S340         | Ą           | 1670.00            | -611300              | 265                        | S280              | Α        | 1670.00            | -3623.00             | 325        | S220          | Ą           | 1670.00            | -1133.00                     |

| 276                 | 5339         | A           | 154000             | -6071.50             | 266                        | S279              | A        | 1540.00            | -3581.50             | 326        | S219          | A           | 154000             | -1091.50                     |

| 207                 | S338         | Α           | 1670.00            | -603000              | 267                        | S278              | Α        | 1670.00            | -3540.00             | 327        | S218          | Α           | 1670.00            | -1050.00                     |

| 208                 | S337         | A<br>A      | 1540.00            | -598850              | 268                        | S277              | Α        | 1540.00            | -3498.50             | 328        | S217          | A<br>A      | 1540.00            | -1008.50                     |

| 209                 | S336         | Α           | 1670.00            | -5947.00             | 269                        | S276              | Α        | 1670.00            | -3457.00             | 329        | S216          | Α           | 1670.00            | -967.00                      |

| 210                 | S335         | A           | 1540.00            | -590550              | 270                        | S275              | Α        | 1540.00            | -3415.50             | 330        | S215          | A           | 1540.00            | -925.50                      |

| 211                 | S334         | Α .         | 1670.00            | -586400              | <i>2</i> 71                | S274              | A        | 1670.00            | -337400              | 331        | S214          | I A         | 1670.00            | -884.00                      |

| 212                 | S333         | Ā           | 1540.00            | -582250              | 272                        | S273              | A        | 1540.00            | -333250              | 332        | S213          | Α           | 1540.00            | -84250                       |

| 213<br>214          | S332<br>S331 | A           | 1670.00            | -5781.00<br>-5739.50 | <i>2</i> 73<br><i>2</i> 74 | S272<br>S271      | A        | 1670.00            | -3291.00             | 333<br>334 | S212          | A           | 1670.00            | -801.00                      |

| 214<br>215          | 2330         | A<br>A      | 1540.00<br>1670.00 | -5/3950<br>-569800   | 2/4<br>2/5                 | S270              | Α        | 1540.00<br>1670.00 | -3249.50<br>-3208.00 | 334<br>335 | S211<br>S210  | A<br>A      | 1540.00<br>1670.00 | -759.50<br>-718.00           |

| 216                 | S329         | A           | 1540.00            | -565650              | 276                        | S269              | A        | 1540.00            | -3166.50             | 336        | S209          | A           | 1540.00            | -7 16W<br>-67650             |

| 217                 | S328         | A           | 1670.00            | -561500              | 277                        | S268              | A        | 1670.00            | -312500              | 337        | S208          | A           | 1670.00            | -635.00                      |

| 218                 | S327         | Δ           | 1540.00            | -557350              | 278                        | S267              | <u>^</u> | 1540.00            | -308350              | 338        | S207          | Α Α         | 1540.00            | -593.50                      |

| 219                 | S326         | A           | 1670.00            | -553200              | 279                        | S266              | Α Α      | 1670.00            | -304200              | 339        | S206          | A           | 1670.00            | -55200                       |

| 220                 | S325         | Α           | 1540.00            | -5490.50             | 280                        | S265              | A        | 1540.00            | -3000.50             | 340        | S205          | А           | 1540.00            | -510.50                      |

| 221                 | S324         | Α           | 1670.00            | -5449.00             | 281                        | S264              | A        | 1670.00            | -2959.00             | 341        | S204          | Α           | 1670.00            | -469.00                      |

| 222                 | S323         | Δ           | 1540.00            | -5407.50             | 282                        | S263              | A        | 1540.00            | -2917.50             | 342        | S203          | Α           | 1540.00            | -427.50                      |

| 223                 | S322         | Ä           | 1670.00            | -536600              | 283                        | S262              | Α        | 1670.00            | -287600              | 343        | S202          | Α           | 1670.00            | -38600                       |

| 224                 | S321         | Ä           | 1540.00            | -532450              | 284                        | S261              | Α        | 1540.00            | -2834.50             | 344        | S201          | А           | 1540.00            | -344.50                      |

| 225                 | S320         | Α           | 1670.00            | -528300              | 285                        | S260              | A        | 1670.00            | -2793.00             | 345        | S200          | A           | 1670.00            | -33300                       |

| Shee <b>226</b> U.d | S319         | A           | 1540.00            | -5241.50             | 286                        | S259              | A        | 1540.00            | -2751.50             | 346        | S199          | Ą           | 1540.00            | -261.50                      |

| 227                 | S318<br>S317 | A<br>A      | 1670.00<br>1540.00 | -520000<br>-5158:50  | 287                        | \$258<br>\$257    | Α        | 1670.00<br>1540.00 | -2710.00<br>-2668.50 | 347        | S198<br>S197  | A           | 1670.00<br>1540.00 | -220.00<br>-178.50           |

| 228<br>229          | S317<br>S316 |             |                    |                      | 288                        | S257<br>  S256    | A        |                    | -2668.50<br>-2627.00 | 348<br>349 | S197<br> S196 | A           | 1540.00<br>1670.00 | -178.50<br>-137.00           |

| 230                 | S315         | Α           | 1670.00<br>1540.00 | -5117.00<br>-5075.50 | 289<br>290                 | S255<br>S255      | A        | 1670.00<br>1540.00 | -2627.00<br>-2585.50 | 349<br>350 | S195          | Α           | 1540.00            | -137.W<br>-95.50             |

| 231                 | CM           | Α Δ         | 167000             | -503400              | 201                        | 220               | <b></b>  | ഷനന                | 2541 M               | 351        | SHON          | Α Δ         | 167000             | - <del>9</del> 030<br>-54:00 |

| 232                 | S313         | A           | 154000             | 499250               | 292                        | S253              | Ä        | 1540.00            | -2JH:W               | 352        | S193          | A           | 1540.00            | -34.00<br>-12.50             |

| 233                 | S312         | <u>^</u>    | 1670.00            | -4951M               | 293                        | S252              | Â        | 1670.00            |                      | 353        | DUMMY         | A           | 1670.00            | -1230<br>29.00               |

| 234                 | S311         | А           | 154000             | 490950               | 294                        | S251              | Α        | 154000             | -241950              | 354        | DJMMY         | А           | 154000             | 7050                         |

| 235                 | S310         | А           | 1670.00            | -486800              | 295                        | S2 <del>3</del> 0 | Α        | 1670.00            | -237800              | 355        | DUMMY         | А           | 1670.00            | 11200                        |

| 236                 | S309         | Α           | 1540.00            | -482650              | 296                        | S249              | Α        | 1540.00            | -233650              | 356        | DUMMY         | Α           | 154000             | 15350                        |

| 237                 | S308         | А           | 1670.00            | -478500              | 297                        | S248              | A        | 1670.00            | -2295.00             | 357        | DUMMY         | Δ           | 1670.00            | 19500<br>23650               |

| 238                 | S307         | Α           | 1540.00            | -474350              | 240                        | S247              | Α        | 1540.00            | -225350              | 358        | DUMMY         | A<br>A      | 1540.00            | 236.50                       |

| 239                 | S306         | Α           | 1670.00            | -470200              | 299                        | S246              | Α        | 1670.00            | -221200              | 359        | DUMMY         | Α           | 1670.00            | 278.00                       |

| 240                 | S305         | Α           | 1540.00            | -4660.50             | 300                        | S245              | Α        | 1540.00            | -217050              | 360        | DUMMY         | А           | 1540.00            | 319.50                       |

|                     | _            |             | _                  |                      |                            | _                 | _        |                    |                      |            | _             | _           |                    | _                            |

Table 2-1. Pad Layout (3/4)

| ₽nNa              | FinName       | PadType       | X[µm]              | Y[µm]              | PinNα                       | PinName      | PadType  | X[µm]              | Y[µm]              | PlnNα       | PinName     | PadType     | X[µm]              | Y[µm]              |

|-------------------|---------------|---------------|--------------------|--------------------|-----------------------------|--------------|----------|--------------------|--------------------|-------------|-------------|-------------|--------------------|--------------------|

| 361               | DUMMY         | Α             | 1670.00            | 361.00             | 421                         | S136         | А        | 1670.00            | 2851.00            | 481         | S76         | Α           | 1670.00            | 5341.00            |

| 362               | DJMMY         | A             | 154000             | 40250              | 422                         | S135<br>S134 | A        | 1540.00            | 289250             | 482         | S75<br>S74  |             | 1540.00            | 538250<br>5424.00  |

| 1 3103            | DUMMY         | A             | 1670.00<br>1540.00 | 444.00<br>485.50   | 423<br>424                  | S134<br>S133 | A        | 1670.00<br>1540.00 | 2934.00<br>2975.50 | 483<br>484  | S74<br>S73  | A<br>A<br>A | 1670.00<br>1540.00 | 5424.00<br>5465.50 |

| 364<br>365        | DUMMY<br>S192 | A             | 1540W<br>167000    | 48550<br>527.00    | 4 <u>24</u><br>4 <u>2</u> 5 | S132         | A        | 1540.00<br>1670.00 | 3017.00            | 484<br>485  | S73<br>S72  | A           | 1540.00<br>1670.00 | 5455.50<br>5507.00 |

| 366               | S191          | A<br>A        | 1540.00            | 527.00<br>568.50   | 425<br>426                  | S131         | A        | 1540.00            | 306850             | 486         | S71         | A           | 1540.00            | 5548.50            |

| 367               | S190          |               | 1670.00            | 61000              | 427                         | S130         | <u>^</u> | 1670.00            | 3100.00            | 487         | S70         |             | 1670.00            | 5590.00            |

| 368               | S189          | A<br>A        | 1540.00            | 651.50             | 428                         | S129         | Α Α      | 1540.00            | 3141.50            | 488         | S69         | A<br>A      | 1540.00            | 5631.50            |

| 369               | S188          | A             | 1670.00            | 630                | 429                         | S128         | A        | 1670.00            | 3183.00            | 489         | S68         | A           | 1670.00            | 5673.00            |

| 370               | S187          | A             | 1540.00            | 73450              | 430                         | S127         | Α        | 1540.00            | 3224.50            | 490         | S67         | A           | 1540.00            | 5714.50            |

| 371               | S186          | A<br>A        | 1670.00            | 77600              | 431                         | S126         | Α        | 1670.00            | 326600             | 491         | S66         | Α           | 1670.00            | 5756.00            |

| 372               | S185          |               | 1540.00            | 817.50             | 432                         | S125         | Α        | 1540.00            | 3307.50            | 492         | S65         | A<br>A      | 1540.00            | 5797.50            |

| 373<br>374        | S184<br>S183  | A             | 1670.00<br>1540.00 | 859.00<br>900.50   | 433                         | S124<br>S123 | Α        | 1670.00<br>1540.00 | 3349.00<br>3390.50 | 493<br>494  | S64<br>S63  | А           | 1670.00<br>1540.00 | 5839.00<br>5880.50 |

| 3/4<br>3/5        | S182          | A<br>A<br>A   | 1540.00<br>1670.00 | 94200              | 434                         | S123<br>S122 | A        | 1540.00<br>1670.00 | 343200             | 494<br>495  | S62         | A<br>A      | 1540.00<br>1670.00 | 592200             |

| 376               | S181          | A             | 1540.00            | 942W<br>98350      | 435<br>436                  | S121         | A        | 1540.00            | 3473.50            | 496         | S61         | A           | 1540.00            | 5963.50            |

| 377               | S180          |               | 1670.00            | 102500             | 437                         | S120         | <u>^</u> | 1670.00            | 3515.00            | 497         | S60         | A           | 1670.00            | 600500             |

| 378               | S179          | A<br>A        | 154000             | 109650             | 438                         | S119         | Α Α      | 1540.00            | 377650             | <b>⊿</b> 08 | 939         | A           | 1540.00            | 604650             |

| 378<br>379        | S178          | A             | 1670.00            | 110800             | 439                         | S118         | Α Α      | 1670.00            | 359800             | 499         | SF8         | A           | 1670.00            | 6088CD             |

| 380               | S177          | A             | 1540.00            | 114950             | 440                         | S117         | Α        | 1540.00            | 3639.50            | 500         | <b>357</b>  | A           | 1540.00            | 6129.50            |

| 381               | S176          | Α             | 1670.00            | 1191.00            | 441                         | S116         | Α        | 1670.00            | 3681.00            | 501         | <b>95</b> 6 | Α           | 1670.00            | 6171.00            |

| 382               | S175          |               | 1540.00            | 123250             | 442                         | S115         | Α        | 1540.00            | 372250             | 502         | S65         | A           | 1540.00            | 621250             |

| 383<br>384        | S174<br>S173  | A<br>A        | 1670.00<br>1540.00 | 127400<br>131550   | 443<br>444                  | S114         | Α        | 1670.00            | 376400<br>3805.50  | 503         | S54<br>S53  | A<br>A      | 1670.00            | 6254.00<br>6295.50 |

| 384<br>385        | S173<br>S172  |               | 1540.00<br>1670.00 |                    |                             | S113<br>S112 | Α        | 1540.00<br>4670.00 | 3847.00            | 504         | S62         |             | 1540.00<br>1670.00 | 62950<br>6337.00   |

| 300               | S171          | A             | 1540.00            | 1357.00<br>1398.50 | 445<br>446                  | SI12<br>C111 | A        | 1670.00<br>1540.00 | 3888.50            | 505<br>506  | S51         | A           | 1540.00            | 6378.50            |

| 386<br>387        | S170          | Α Δ           | 1670.00            | 144000             | 447                         | S111<br>S110 | A        | 1670.00            | 33300              | 507         | S60         | Α Δ         | 1670.00            | 6420.00            |

| 388               | S169          | A<br>A        | 1540.00            | 1481.50            | 448                         | S109         | Α Α      | 1540.00            | 3971.50            | 508         | S49         | A<br>A      | 1540.00            | 6461.50            |

| 389               | S168          | A             | 1670.00            | 152300             | 449                         | S108         | A        | 1670.00            | 4013.00            | 509         | S48         | A           | 1670.00            | 6503.00            |

| 390               | S167          | A             | 1540.00            | 156450             | 450                         | S107         | Α        | 1540.00            | 405450             | 510         | S47         | А           | 1540.00            | 6544.50            |

| 391               | S166          | Α .           | 1670.00            | 160600             | 451                         | S106         | Α        | 1670.00            | 409600             | 511         | S46         | А           | 1670.00            | 653600             |

| 392               | S165          | A             | 1540.00            | 1647.50            | 452                         | S105         | Α        | 1540.00            | 4137.50            | 512         | S45         | А           | 1540.00            | 6627.50            |

| 393               | S164          | Α             | 1670.00            | 168900             | 453                         | S104         | Α        | 1670.00            | 4179.00            | 513         | S44         | A           | 1670.00            | 6669.00            |

| 394<br>395        | S163<br>S162  | Ä             | 1540.00<br>1670.00 | 173050<br>177200   | 454<br>455                  | S103<br>S102 | Α        | 1540.00<br>1670.00 | 4220.50<br>4262.00 | 514<br>515  | S43<br>S42  | A<br>A      | 1540.00<br>1670.00 | 6710.50<br>675200  |

| 396               | S161          | А<br>А        | 1540.00            | 181350             | 456                         | S101         | A        | 1540.00            | 4303.50            | 516         | S41         | A           | 1540.00            | 6793.50            |

| 397               | S160          | A             | 1670.00            | 185500             | 457                         | S100         | A        | 1670.00            | 434500             | 517         | S40         | A           | 1670.00            | 683500             |

| 398               | S159          | Δ             | 1540.00            | 189650             | 458                         | S99          |          | 1540.00            | 4336.50            | 518         | S39         | A           | 1540.00            | 6876.50            |

| 399               | S158          | Α             | 1670.00            | 193800             | 459                         | S98          | A        | 1670.00            | 4428.00            | 519         | S38         | Α           | 1670.00            | 691800             |

| 400               | S157          | Α             | 1540.00            | 197950             | 460                         | S97          | Α        | 1540.00            | 4469.50            | 520         | S37         | Α           | 1540.00            | 6959.50            |

| 401               | S156          | Α             | 1670.00            | 2021.00            | 461                         | S96          | Α        | 1670.00            | 4511.00            | 521         | S36         | Α           | 1670.00            | 7001.00            |

| 402               | S155          | Ą             | 1540.00            | 206250             | 462                         | <b>S</b> 95  | A        | 1540.00            | 455250             | 522         | S35         | A           | 1540.00            | 704250             |

| 403<br>404        | S154<br>S153  | A<br>A        | 1670.00<br>1540.00 | 210400<br>214550   | 463<br>464                  | 994<br>998   | A        | 1670.00<br>1540.00 | 4594.00<br>4635.50 | 523<br>524  | S34<br>S33  | A<br>A      | 1670.00<br>4540.00 | 7084.00<br>7125.50 |

| 404               | S153<br>S152  |               | 1540.00<br>1670.00 | 214550<br>2187.00  | 464<br>465                  | S92          | Α        | 1540.00<br>1670.00 | 4635.50<br>4677.00 | 524<br>525  | S32         |             | 1540.00<br>1670.00 | 712550<br>7167.00  |

| 406<br>Shee406U d | S151          | A<br>A        | 1540.00            | 2187.W<br>2228.50  | 466                         | S91          | A        | 1540.00            | 4677.W<br>4718.50  | 526         | S31         | A<br>A      | 1540.00            | 7167.W<br>7208.50  |

| 5nee-woo.c        | S150          | Α             | 1670.00            | 227000             | 467                         | S90          | <u>^</u> | 1670.00            | 4760.00            | 527         | S30         | Α Α         | 1670.00            | 7250.00            |

| 408               | S149          | Α             | 1540.00            | 2311.50            | 468                         | S89          | Ä        | 1540.00            | 4801.50            | 528         | S29         | Α           | 1540.00            | 7291.50            |

| 409               | S148          | А             | 1670.00            | 235300             | 469                         | S88          | A        | 1670.00            | 4843.00            | 529         | S28         | Α           | 1670.00            | 733300             |

| 410               | S147          | Α             | 1540.00            | 239450             | 470                         | S87          | A        | 1540.00            | 4884.50            | 530         | S27         | Α           | 1540.00            | 7374.50            |

| 411               | S146          | Α             | 1670.00            | 243600             | 471                         | S86          | A        | 1670.00            | 4926.00            | 531         | S26         | Α           | 1670.00            | 741600             |

| 412               | S145          | A             | 1540.00            | 2477.50            | 472                         | S85          | A        | 1540.00            | 4967.50            | 532         | S25         | A           | 1540.00<br>1670.00 | 7457.50            |

| 413<br>414        | S144<br>S143  | A<br>A        | 1670.00<br>1540.00 | 251900<br>2560.50  | 473<br>474                  | S84<br>S83   | A        | 1670.00<br>1540.00 | 500900             | 533         | S24         | A<br>A      | 1670.00<br>1540.00 | 7499.00<br>7540.50 |

| 414<br>415        | S143<br>S142  | <u>А</u><br>А | 1540.00<br>1670.00 | 26050<br>260200    | 4/4<br>4/5                  | S82          | A<br>A   | 1540.00<br>1670.00 | 5050.50<br>509200  | 534<br>535  | S22<br>S22  | A           | 1540.00<br>1670.00 | 7540.50<br>758200  |

| 416               | S141          | A<br>A        | 1540.00            | 264350             | 4/5<br>4/6                  | S81          | A        | 1540.00            | 5133.50            | 536         | S21         | A           | 1540.00            | 7623.50            |

| 417               | S140          | ^             | 1670.00            | 266500             | 477                         | 380<br> 380  | <u>?</u> | 1670.00            | 5175.00            | 537         | S20         | Δ           | 1670.00            | 766500             |

| 418               | S139          | A             | 154000             | 272650             | 478                         | S79          |          | 154000             | 521650             | 538         | S19         | A<br>A      | 154000             | 770650             |

| 419               | S138          | A             | 1670.00            | 276800             | 479                         | S78          | Α        | 1670.00            | 525800             | 539         | S18         | А           | 1670.00            | 7748.00            |

| 420               | S137          | А             | 1540.00            | 280950             | 480                         | S77          | Α        | 1540.00            | 529950             | 540         | S17         | А           | 1540.00            | 7789.50            |

|                   | •             |               |                    |                    |                             | •            | _        | •                  |                    |             | •           |             |                    |                    |

www.DataS

6

Table 2-1. Pad Layout (4/4)

| ₽nNo | PinName    | PadType | X[µm]    | Y[µm]   |

|------|------------|---------|----------|---------|

| 541  | S16        | Α       | 1670.00  | 7831.00 |

| 542  | S15        | Α       | 1540.00  | 787250  |

| 543  | S14        | Α       | 1670.00  | 7914.00 |

| 544  | S13        | Α       | 1540.00  | 7955.50 |

| 545  | S12        | Α       | 1670.00  | 7997.00 |

| 546  | S11        | Α       | 1540.00  | 8038.50 |

| 547  | S10        | Α       | 1670.00  | 8080.00 |

| 548  | <b>S</b> 9 | Α       | 1540.00  | 8121.50 |

| 549  | S8         | Α       | 1670.00  | 8163.00 |

| 550  | S7         | Α       | 1540.00  | 8204.50 |

| 551  | <b>S</b> 6 | Α       | 1670.00  | 8246.00 |

| 552  | <b>S</b> 5 | Α       | 1540.00  | 8287.50 |

| 553  | S4         | Α       | 1670.00  | 8329.00 |

| 554  | S3         | Α       | 1540.00  | 8370.50 |

| 555  | \$2        | Α       | 1670.00  | 841200  |

| 556  | SI         | Α       | 1540.00  | 8453.50 |

| 557  | DJMMY      | Α       | 1670.00  | 8495.00 |

| 558  | DUMY       | В       | 1670.00  | 85/5.00 |

| 559  | DUMY       | В       | 1220.00  | 8774.00 |

| 560  | DUMY       | В       | 380.00   | 8774.00 |

| 561  | DUMY       | В       | -460.00  | 8774.00 |

| 562  | DUMY       | В       | -1300,00 | 8774.00 |

www.DataSheet4U.com

# 3. PIN FUNCTIONS

# 3.1 Power Supply System Pins

| Symbol                                                                                     | Pin Name                            | Pad No.                                                  | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC1</sub>                                                                           | Logic power supply                  | 71, 83, 84                                               | -   | Power supply pin for logic circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CC2</sub>                                                                           | I/O power supply                    | 57, 70                                                   | _   | Power supply pin for I/O buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vs                                                                                         | Driver power supply                 | 78, 79                                                   | -   | Power supply pin for driver circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vss                                                                                        | Ground                              | 69, 72, 72, 80                                           | -   | Ground pin for logic and driver circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

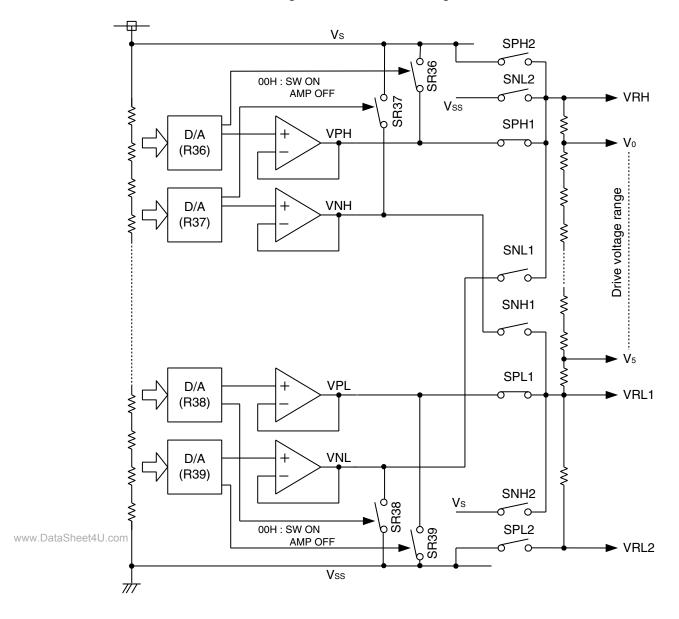

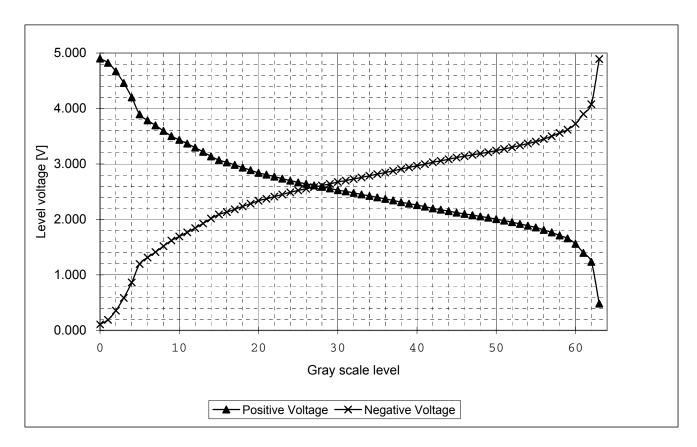

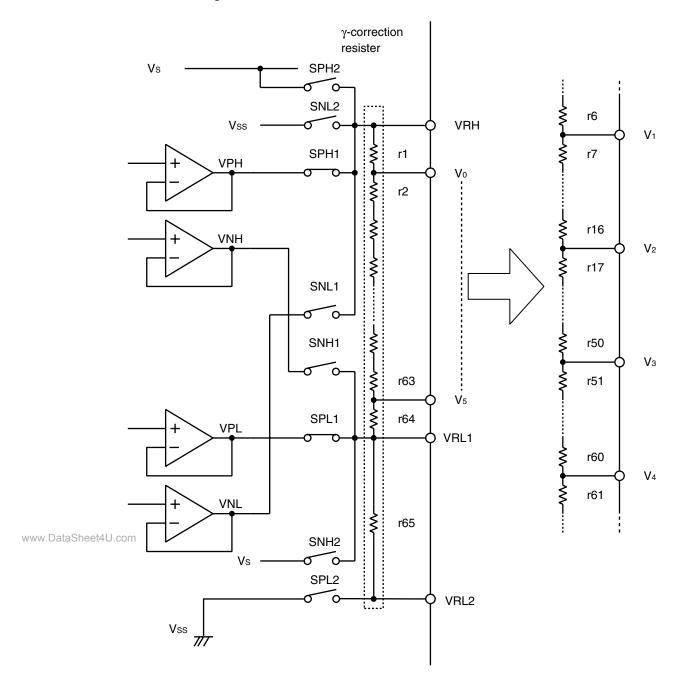

| V <sub>0</sub> to V <sub>5</sub><br>V <sub>RH</sub><br>V <sub>RL1</sub> , V <sub>RL2</sub> | Power supply for                    | 95 to 100,<br>94,<br>101, 102                            | -   | The $\mu$ PD161622 includes power supplies and resistors for the $\gamma$ -curve, so if the characteristics of the $\gamma$ -curve and LCD panel in the $\mu$ PD161622 match, leave V <sub>0</sub> to V <sub>5</sub> , V <sub>RH</sub> , V <sub>RL1</sub> , V <sub>RL2</sub> open. If some kind of correction is required, adjust the $\gamma$ -curve by connecting resistors between the V <sub>0</sub> to V <sub>5</sub> , V <sub>RH</sub> , V <sub>RL1</sub> , V <sub>RL2</sub> pins (see <b>5.9</b> $\gamma$ - <b>Curve</b> Correction Power Supply Circuit for Cases of Unbalanced Driving). |

| VCC1(MODE)                                                                                 | Mode setting pull-up power-supply   | 27, 91, 124,<br>128, 132                                 |     | Pull-up power-supply pin for mode setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vss(mode)                                                                                  | Mode setting pull-down power-supply | 20, 29, 31, 33, 51,<br>60, 88, 93, 103,<br>115, 126, 130 | _   | Pull-down power-supply pin for mode setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 3.2 Logic System Pins

(1/2)

| Symbol     | Pin Name                | Pad No. | I/O   | Function                                                                      |

|------------|-------------------------|---------|-------|-------------------------------------------------------------------------------|

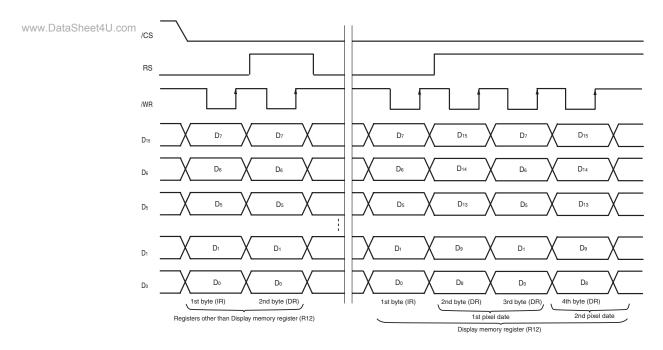

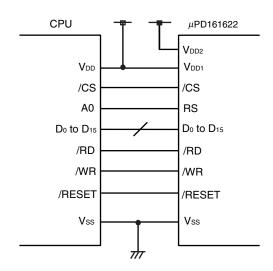

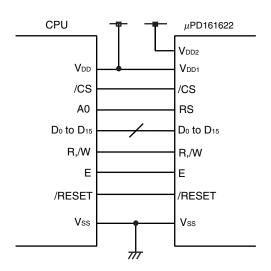

| PSX        | CPU interface selection | 58      | Input | These pins are used to select the CPU interface mode.                         |

|            |                         |         |       | PSX = H: Parallel interface                                                   |

|            |                         |         |       | PSX = L: Serial interface                                                     |

|            |                         |         |       | When the parallel interface is selected, this data but width can be changed   |

|            |                         |         |       | between 8 bits and 16 bits by using BMD of index register 5 (R5).             |

| /CS        | Chip select             | 52      | Input | This pin is used for chip select signals. When /CS = L, the chip is active    |

|            |                         |         |       | and can perform data input/output operations including command and data       |

|            |                         |         |       | I/O.                                                                          |

| /RESET     | Reset                   | 53      | Input | When /RESET is low, an internal reset is performed. The reset operation       |

| heet4U.con | n                       |         |       | is executed at the /RESET signal level. Be sure to perform reset via this     |

|            |                         |         |       | pin at power application.                                                     |

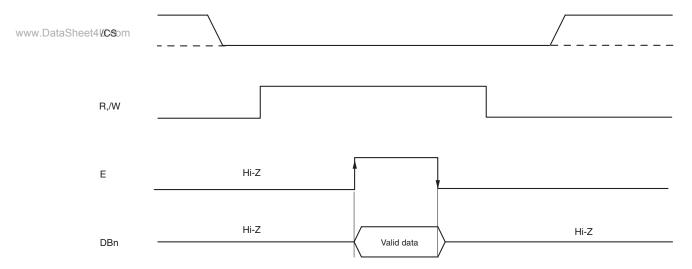

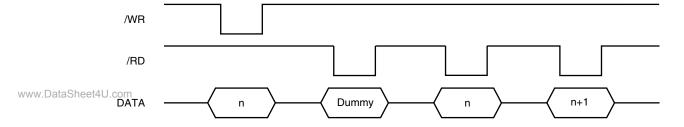

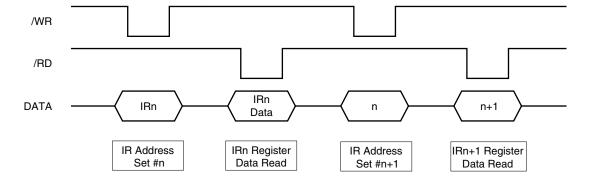

| /RD        | Read                    | 56      | Input | When i80 series parallel data transfer (/RD) has been selected, the signal    |

| (E)        | (enable)                |         |       | at this pin is used to enable read operations. Data is output to the data bus |

|            |                         |         |       | only when this pin is low.                                                    |

|            |                         |         |       | When M68 series parallel data transfer (E) has been selected, the signal at   |

|            |                         |         |       | this pin is used to enable read/write operations.                             |

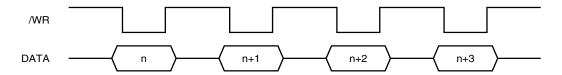

| /WR        | Write                   | 55      | Input | When i80 series parallel data transfer (/WR) has been selected, the signal    |

| (R, /W)    | (read/write)            |         |       | at this pin is used to enable write operations. Data is written at the rising |

|            |                         |         |       | edge of this signal.                                                          |

|            |                         |         |       | When M68 series parallel data transfer (R, /W) and serial data has been       |

|            |                         |         |       | selected, this pin is used to determine the direction of data transfer.       |

|            |                         |         |       | L: Write                                                                      |

|            |                         |         |       | H: Read                                                                       |

| C86        | Select interface        | 59      | Input | This pin is used to switch between interface modes (i80 series CPU or M68     |

|            |                         |         |       | series CPU).                                                                  |

|            |                         |         |       | L: Selects i80 series CPU mode                                                |

|            |                         |         |       | H: Selects M68 series CPU mode                                                |

(2/2)

| Symbol                | Pin Name                  | Pad No.    | I/O    | Function                                                                                                  |

|-----------------------|---------------------------|------------|--------|-----------------------------------------------------------------------------------------------------------|

| D₀ to D₅,             | Data bus                  | 50 to 35   | I/O    | These pins comprise 16-bit bi-directional data.                                                           |

| D8 to D15,            |                           |            |        | When the serial interface has been selected (PSX = L), D <sub>7</sub> functions as                        |

| D <sub>6</sub> (SCL), | (serial clock)            |            |        | a serial data input pin (SI), D <sub>6</sub> functions as a serial clock input pin (SCL).                 |

| D <sub>7</sub> (SI)   | (serial data input)       |            |        | In either case, pins $D_0$ to $D_7$ and $D_8$ to $D_{15}$ are in high impedance mode.                     |

|                       |                           |            |        | When the chip is not selected, Do to D15 are in high impedance mode.                                      |

| RS                    | Index register/,          | 54         | Input  | When parallel data transfer has been selected, this pin is usually                                        |

|                       | data/command selection    |            |        | connected to the least significant bit of the standard CPU address bus                                    |

|                       |                           |            |        | and is used to distinguish between data from index registers and                                          |

|                       |                           |            |        | data/commands.                                                                                            |

|                       |                           |            |        | RS = H: Indicates that data from D <sub>0</sub> to D <sub>15</sub> is data/command                        |

|                       |                           |            |        | RS = L: Indicates that data from $D_0$ to $D_7$ is index register contents                                |

|                       |                           |            |        | Also, when serial data transfer is selected, the level of the RS pin is                                   |

|                       |                           |            |        | fetched at the rising edge of the eighth clock of the serial clock and                                    |

|                       |                           |            |        | whether the data is index register contents or data/command is                                            |

|                       |                           |            |        | distinguished.                                                                                            |

|                       |                           |            |        | RS = H: Indicates that the data input to SI is data/command.                                              |

|                       |                           |            |        | RS = L: Indicates that the data input to SI is index register contents.                                   |

| IP₀ to IP₃            | Input port                | 125, 127,  | Input  | This is a general-purpose input port. The status of these pins (H or L)                                   |

|                       |                           | 129, 131   |        | can be read via a command.                                                                                |

|                       |                           |            |        | Because this is a CMOS input, do not leave open.                                                          |

| OP₀ to                | Output port               | 116 to 123 | Output | This is a general-purpose output port. The status of these pins (H or L)                                  |

| OP <sub>7</sub>       |                           |            |        | can be write via a command.                                                                               |

|                       |                           |            |        | Leave open when in unused.                                                                                |

| RSEL                  | Oscillation signal select | 28         | Input  | This pin is for oscillation signal selection. When in used external                                       |

|                       |                           |            |        | resistance connection oscillator circuit, this pin set H. When in used                                    |

|                       |                           |            |        | internal oscillator circuit, this pin set L.                                                              |

|                       |                           |            |        | R <sub>SEL</sub> = H: External resistance connection oscillator circuit select                            |

|                       |                           |            |        | Rsel = L: CR internal oscillator circuit select                                                           |

| OSCIN                 | Oscillation signal        | 32         | Input  | This pin is for oscillation signal input.                                                                 |

|                       |                           |            |        | R <sub>SEL</sub> = H: Connect 51 k $\Omega$ resistance between OSC <sub>IN</sub> and OSC <sub>OUT</sub> . |

| heet4U.con            |                           |            |        | R <sub>SEL</sub> = L: Leave open                                                                          |

| OSCout                | Oscillation signal        | 30         | Output | This pin is for oscillation signal input.                                                                 |

|                       | 3                         | 30         |        | R <sub>SEL</sub> = H: Connect 51 k $\Omega$ resistance between OSC <sub>IN</sub> and OSC <sub>OUT</sub> . |

|                       |                           |            |        | Rsel = L: Leave open                                                                                      |

| CSTB                  | GSTB logic signal         | 34         | Output | This pin outputs STB signal for gate driver leveled by interface power                                    |

|                       |                           |            |        | supply voltage (Vcc2). This output signal is reverse signal of GSTB.                                      |

# 3.3 Gate Driver IC Control Pins

| Symbol           | Pin Name                        | Pad No. | I/O    | Function                                                                     |

|------------------|---------------------------------|---------|--------|------------------------------------------------------------------------------|

| LPMG             | Low power mode signal           | 138     | Output | This is an output pin for low power mode (for the gate driver).              |

|                  |                                 |         |        | Connect to the LPM pin of the gate driver.                                   |

| GOE <sub>1</sub> | OE <sub>1</sub> output for gate | 135     | Output | This pin is an output pin for the low power mode (for the OE <sub>1</sub> ). |

|                  | driver                          |         |        | Connect to the OE <sub>1</sub> pin of the gate driver.                       |

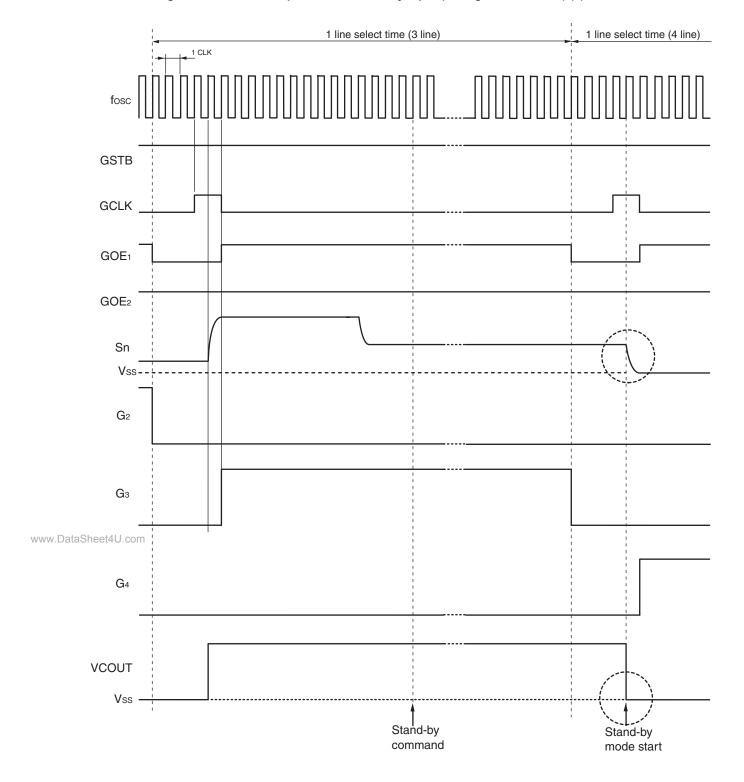

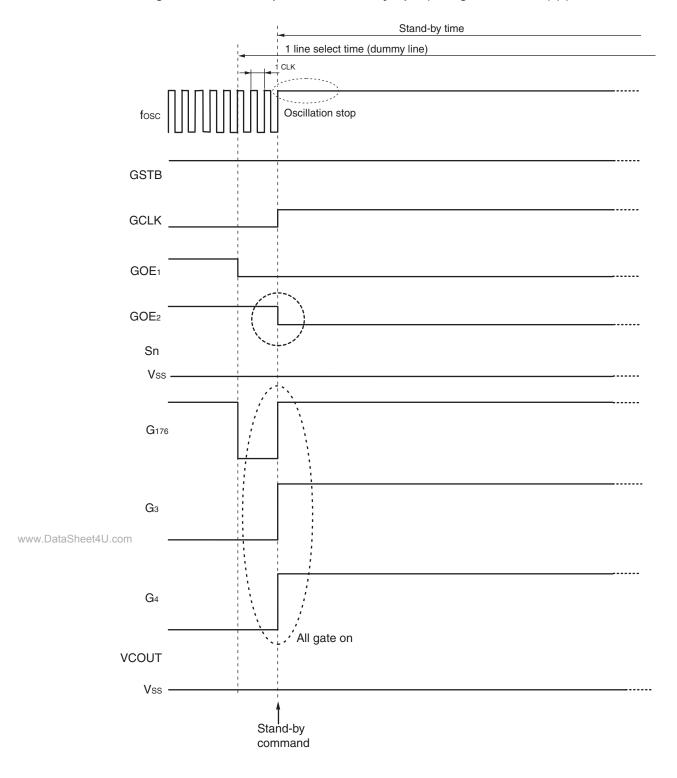

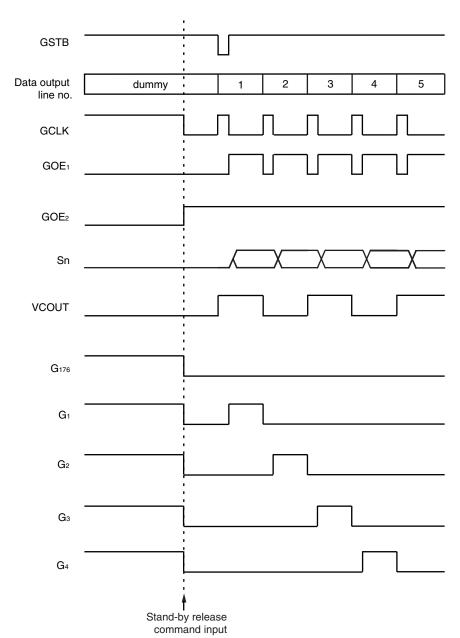

|                  |                                 |         |        | Timing signal for output, refer to 5.4 Display timing generator.             |

| GOE <sub>2</sub> | OE <sub>2</sub> output for gate | 136     | Output | This pin is the OE <sub>2</sub> output for the gate driver.                  |

|                  | driver                          |         |        | Connect to the OE <sub>2</sub> pin of the gate driver.                       |

|                  |                                 |         |        | Timing signal for output, refer to 5.4 Display timing generator.             |

| GSTB             | STB output for gate             | 133     | Output | This pin is the STB output for the gate driver.                              |

|                  | driver                          |         |        | Connect to the STVR or STVL pin of the gate driver.                          |

|                  |                                 |         |        | Timing signal for output, refer to <b>5.4 Display timing generator</b> .     |

| GCLK             | CLK output for gate             | 134     | Output | This pin is the CLK output for the gate driver.                              |

|                  | driver                          |         |        | Connect to the CLK pin of the gate driver.                                   |

| RGONG            | Regulator control               | 137     | Output | Regulator ON/OFF control of gate driver IC                                   |

|                  |                                 |         |        | Connect to the RGONG pin of the gate driver.                                 |

# 3.4 Power Supply Control Pins

| Symbol                                      | Pin Name                           | Pad No. | I/O    | Function                                                                  |

|---------------------------------------------|------------------------------------|---------|--------|---------------------------------------------------------------------------|

| LPMP                                        | Low power mode signal              | 65      | Output | Low power mode control signal output pin (for power-supply IC).           |

|                                             |                                    |         |        | This pin connects to LPM pin of power-supply IC.                          |

| DCON                                        | DC/DC converter control            | 67      | Output | DC/DC converter ON/OFF signal pin for power-supply IC.                    |

|                                             |                                    |         |        | This pin connects DCON pin of power-supply IC.                            |

| RGONP                                       | Regulator control                  | 66      | Output | Regulator ON/OFF control signal pin for power-supply IC.                  |

|                                             |                                    |         |        | This pin connects to RGONP pin of power-supply IC.                        |

| VCD11, VCD12                                | V <sub>DD1</sub> booster selection | 64, 63  | Output | Control signal to select x4/x5/x6/x7 booster of power-supply IC for Vcc1. |

|                                             |                                    |         |        | Connect to the VcD11 and VcD12 pins of the power-supply IC.               |

| Vcp <sub>2</sub><br>neet <sub>4</sub> U.com | V <sub>DD2</sub> booster selection | 62      | Output | Control signal to select x2/x3 booster of power-supply IC for Vcc2.       |

|                                             |                                    |         |        | Connect to the VcD2 pin of the power-supply IC.                           |

| VCE                                         | Vo level selection                 | 61      | Output | Signal for selecting the level of the power-supply IC booster voltage, to |

|                                             |                                    |         |        | be used for the maximum voltage of Vo. Selects that the booster           |

|                                             |                                    |         |        | voltage level is either the same level as VDD1 or a multiple of minus 1.  |

|                                             |                                    |         |        | Connect to the Vc∈ pin of the power-supply IC.                            |

# 3.5 Driver-Related Pins

| Symbol                             | Pin Name                | Pad No.     | I/O    | Function                                                                      |

|------------------------------------|-------------------------|-------------|--------|-------------------------------------------------------------------------------|

| S <sub>1</sub> to S <sub>396</sub> | Source output           | 556 to 365, | Output | Source output pins                                                            |

|                                    |                         | 352 to 149  |        |                                                                               |

| VCOM                               | COM adjustment          | 85          | Output | This pin is the common adjustment output.                                     |

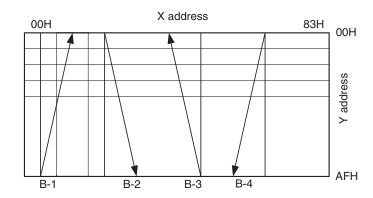

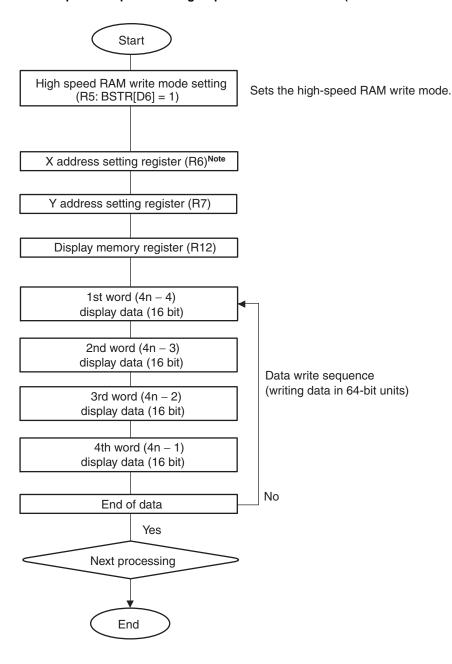

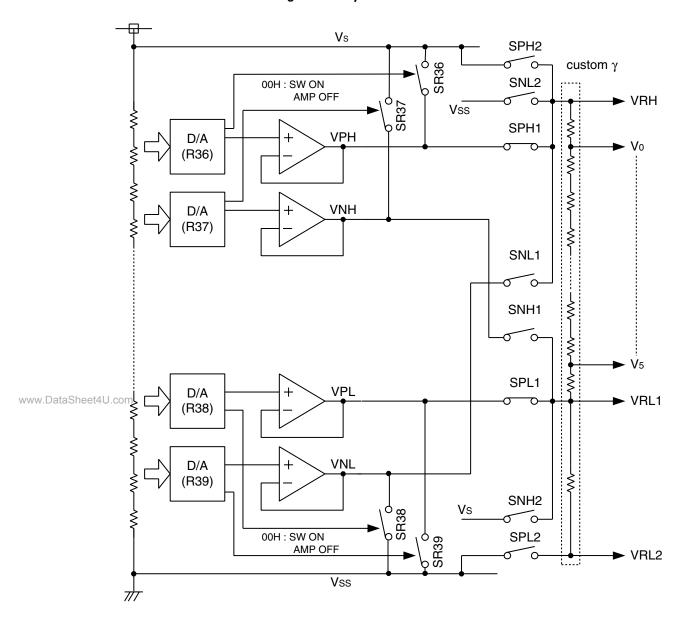

| VCOUT1                             | Center rectangle        | 81, 82      | Output | This pin is the center rectangle signal output (V <sub>P-P</sub> ) for common |