# LM4851 Boomer® Audio Power Amplifier Series

# **Integrated Audio Amplifier System**

## **General Description**

The LM4851 is an audio power amplifier system capable of delivering 1.1W (typ) of continuous average power into a mono  $8\Omega$  bridged-tied load (BTL) with 1% THD+N and 115mW (typ) per channel of continuous average power into stereo  $32\Omega$  BTL loads with 0.5% THD+N, using a 5V power supply.

The LM4851 features a 32 step digital volume control and eight distinct output modes. The digital volume control and output modes are programmed through a three-wire SPI serial control interface, that allows flexibility in routing and mixing audio channels. The LM4851 has 3 inputs: one pair for a two-channel stereo signal and the third for a single-channel mono input.

The LM4851 is designed for cellular phone, PDA, and other portable handheld applications. It delivers high quality output power from a surface-mount package and requires only five external components.

The industry leading micro SMD package utilizes only 2mm x 2.3mm of PCB space, making the LM4851 the most space efficient audio sub system available today.

## **Key Specifications**

■ THD+N at 1kHz, 1.5W into  $4\Omega$  BTL (LQ) 1% (typ) ■ THD+N at 1kHz, 1.1W into  $8\Omega$  BTL 1% (typ)

■ THD+N at 1kHz, 115mW into 32Ω BTL 0.5% (typ)

■ Single Supply Operation 2.6 to 5.0V

## **Features**

- Mono 1.1W (typ) and stereo 115mW (typ) output

- SPI programmable 32 step digital volume control (-40.5dB to +6dB)

- Eight distinct SPI programmable output modes

- micro-SMD and LLP surface mount packaging

- "Click and pop" suppression circuitry

- Thermal shutdown protection

- Low shutdown current (0.1µA, typ)

## **Applications**

- Mobile phones

- PDAs

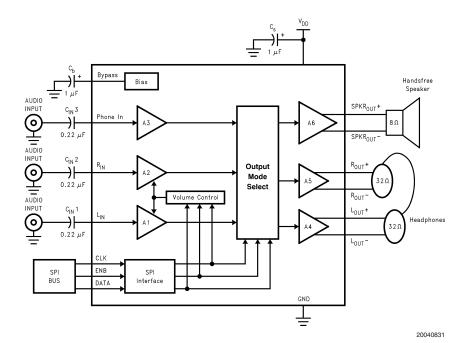

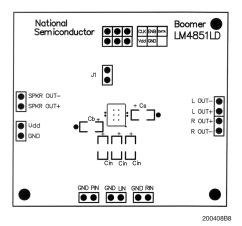

# **Typical Application**

FIGURE 1. Typical Audio Amplifier Application Circuit

Boomer® is a registered trademark of National Semiconductor Corporation.

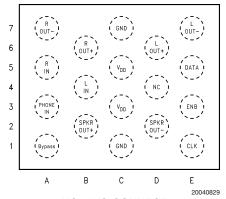

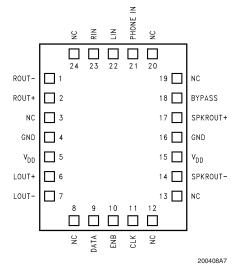

# **Connection Diagrams**

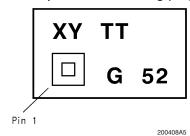

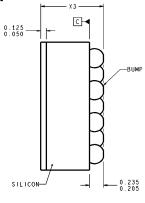

18-Bump micro SMD Marking (IBL)

Top View XY- Date Code TT - Die Traceability G - Boomer Family 52 - LM4851IBL-1

NC = NO CONNECT

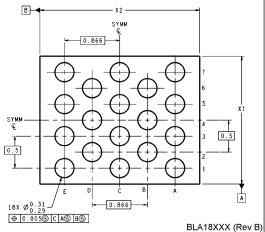

Top View

(Bump-side down)

Order Number LM4851ITL, LM4851IBL

See NS Package Number TLA18AAA, BLA18AAB

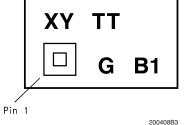

18-Bump micro SMD Marking (ITL)

Top View

XY- Date Code

TT - Die Traceability

G - Boomer Family

B1 - LM4851ITL

Top View

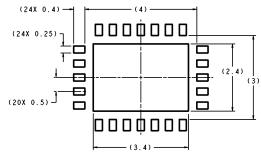

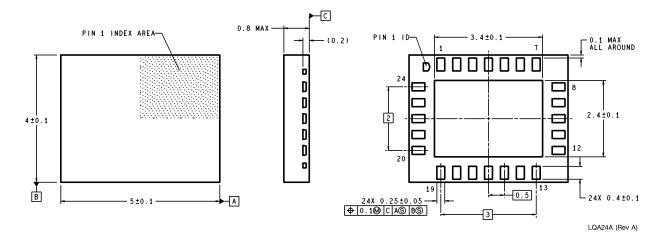

Order Number LM4851LQ

See NS Package Number LQA24A for Exposed-DAP LLP

# Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage                         | 6.0V            |

|----------------------------------------|-----------------|

| Storage Temperature                    | −65°C to +150°C |

| ESD Susceptibility (Note 4)            | 2.0kV           |

| ESD Machine model (Note 7)             | 200V            |

| Junction Temperature (T <sub>J</sub> ) | 150°C           |

| Solder Information (Note 1)            |                 |

| Vapor Phase (60 sec.)                  | 215°C           |

| Infrared (15 sec.)                     | 220°C           |

Thermal Resistance

| 42°C/W          |

|-----------------|

| 3.0°C/W         |

| 48°C/W (Note 9) |

| 23°C/W (Note 9) |

| 48°C/W (Note 9) |

| 23°C/W (Note 9) |

|                 |

# **Operating Ratings** (Note 3)

Temperature Range  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  Supply Voltage  $V_{DD}$   $2.6\text{V} \leq V_{DD} \leq 5.0\text{V}$

**Note 1:** See AN-450 "Surface Mounting and their effects on Product Reliability" for other methods of soldering surface mount devices.

# **Electrical Characteristics** (Notes 2, 8)

The following specifications apply for  $V_{DD}$ = 5.0V,  $T_A$ = 25 $^{\circ}$ C unless otherwise specified.

| Symbol           | Parameter                               | Conditions                                                                                          | LM4851              |                   | Units    |  |

|------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|-------------------|----------|--|

|                  |                                         |                                                                                                     | Typical<br>(Note 5) | Limit<br>(Note 6) | (Limits) |  |

|                  |                                         | Output mode 7 $V_{IN} = 0V; I_O = 0A$                                                               | 7.5                 | 14                | mA (max) |  |

| l <sub>DD</sub>  | Supply Current                          | Output modes 1, 2, 3, 4, 5, 6<br>$V_{IN} = 0V$ ; $I_O = 0A$                                         | 5.0                 | 9.0               | mA (max) |  |

| I <sub>DD</sub>  | Shutdown Current                        | Output mode 0                                                                                       | 0.1                 | 2                 | μA (max) |  |

| V <sub>os</sub>  | Output Offset Voltage                   | $V_{IN} = 0V$                                                                                       | 5.0                 | 50                | mV (max) |  |

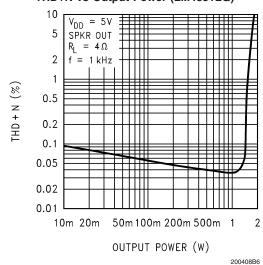

|                  |                                         | SPKR <sub>OUT</sub> ; $R_L = 4\Omega$<br>THD+N = 1%; $f = 1kHz$<br>LM4851LQ                         | 1.5                 |                   | W        |  |

| Po               | Output Power                            | SPKR <sub>OUT</sub> ; $R_L = 8\Omega$<br>THD+N = 1%; $f = 1$ kHz                                    | 1.1                 | 0.8               | W (min)  |  |

|                  |                                         | $R_{OUT}$ and $L_{OUT}$ ; $R_L = 32\Omega$<br>THD+N = 0.5%; f = 1kHz                                | 115                 | 80                | mW (min) |  |

|                  | Total Harmonic Distortion Plus<br>Noise | $R_{OUT}$ and $L_{OUT}$ ; $f = 1kHz$<br>$P_{OUT} = 80mW$ ; $R_{L} = 32\Omega$                       |                     | 0.5               | % (max)  |  |

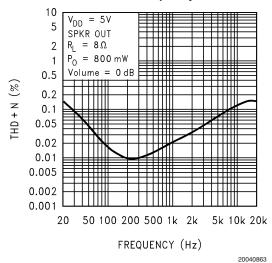

|                  |                                         | $SPKR_{OUT}; f = 1kHz$ $P_{OUT} = 800mW; R_{L} = 8\Omega$                                           |                     | 1.0               | % (max)  |  |

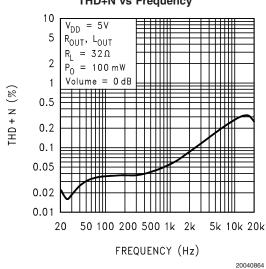

| THD+N            |                                         | $R_{OUT}$ and $L_{OUT}$ ; f = 20Hz to 20kHz<br>$P_{OUT}$ = 100mW; $R_L$ = 32 $\Omega$               | 0.3                 |                   | %        |  |

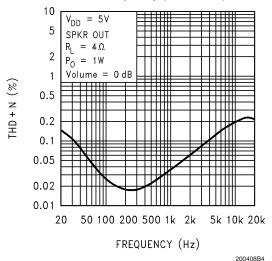

|                  |                                         | SPKR <sub>OUT</sub> ; f = 20Hz to 20kHz<br>$P_{OUT}$ = 1W; $R_L$ = $4\Omega$<br>LM4851LQ            | 0.3                 |                   | %        |  |

|                  |                                         | SPKR <sub>OUT</sub> ; f = 20Hz to 20kHz<br>P <sub>OUT</sub> = 800mW; R <sub>L</sub> = $8\Omega$     | 0.3                 |                   | %        |  |

| N <sub>OUT</sub> | Output Noise                            | A-weighted (Note 10)                                                                                | 29                  |                   | μV       |  |

| PSRR             | Power Supply Rejection Ratio            | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> ; f = 217Hz<br>Input floating; Input referred             | 70                  |                   | dB       |  |

|                  |                                         | $V_{RIPPLE} = 200 \text{mV}_{PP}$ ; f = 217Hz<br>Input terminated into $50\Omega$ ; Output referred | 62                  |                   | dB       |  |

| V <sub>IH</sub>  | Logic High Input Voltage                |                                                                                                     |                     | 1.4               | V (min)  |  |

|                  |                                         |                                                                                                     |                     | 5.0               | V (max)  |  |

| V <sub>IL</sub>  | Logic Low Input Voltage                 |                                                                                                     |                     | 0.4               | V (max)  |  |

**Electrical Characteristics** (Notes 2, 8) (Continued) The following specifications apply for  $V_{DD}$ = 5.0V,  $T_A$ = 25°C unless otherwise specified.

| Symbol | Parameter                                 | Conditions                                                    | LM <sup>2</sup>  | 1851              | Units               |

|--------|-------------------------------------------|---------------------------------------------------------------|------------------|-------------------|---------------------|

|        |                                           |                                                               | Typical (Note 5) | Limit<br>(Note 6) | (Limits)            |

|        | Digital Volume Range (R <sub>IN</sub> and | Input referred minimum gain                                   | -40.5            |                   | dB                  |

|        | L <sub>IN</sub> )                         | Input referred maximum gain                                   | +6               |                   |                     |

|        | Digital Volume Stepsize                   |                                                               | 1.5              |                   | dB                  |

|        | Stepsize Error                            |                                                               | ±0.5             |                   | dB                  |

|        | Phone In Volume                           | BTL gain from Phone In to SPKR <sub>OUT</sub>                 | 6                |                   | dB                  |

|        | Phone In Volume                           | BTL gain from Phone In to R <sub>OUT</sub> , L <sub>OUT</sub> | 0                |                   | dB                  |

|        | Phone In Input Impedance                  |                                                               | 20               | 15<br>25          | kΩ (min)<br>kΩ (max |

|        | R <sub>IN</sub> and L <sub>IN</sub>       |                                                               | 50               | 37.5<br>62.5      | kΩ (min)<br>kΩ (max |

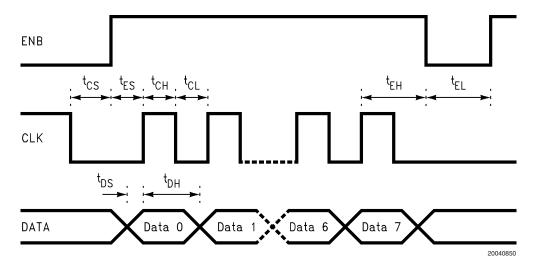

| ES .   | Enable Setup Time (ENB)                   |                                                               |                  | 20                | ns (min)            |

| ΞΗ     | Enable Hold Time (ENB)                    |                                                               |                  | 20                | ns (min)            |

| EL.    | Enable Low Time (ENB)                     |                                                               |                  | 30                | ns (min)            |

| os     | Data Setup Time (DATA)                    |                                                               |                  | 20                | ns (min)            |

| DН     | Data Hold Time (DATA)                     |                                                               |                  | 20                | ns (min)            |

| cs     | Clock Setup Time (CLK)                    |                                                               |                  | 20                | ns (min)            |

| СН     | Clock Logic High Time (CLK)               |                                                               |                  | 50                | ns (min)            |

| DL .   | Clock Logic Low Time (CLK)                |                                                               |                  | 50                | ns (min)            |

| CLK    | Clock Frequency                           |                                                               |                  | DC                | (min)               |

|        |                                           |                                                               |                  | 10                | MHz (max            |

# **Electrical Characteristics** (Notes 2, 8)

The following specifications apply for  $V_{DD}$ = 3.0V,  $T_A$ = 25 $^{\circ}$ C unless otherwise specified.

| Symbol            | Parameter             | Conditions                                                                 | LM4851              |                   | Units    |  |

|-------------------|-----------------------|----------------------------------------------------------------------------|---------------------|-------------------|----------|--|

|                   |                       |                                                                            | Typical<br>(Note 5) | Limit<br>(Note 6) | (Limits) |  |

|                   | Council Course        | Output mode 7<br>V <sub>IN</sub> = 0V; I <sub>O</sub> = 0A                 | 6.2                 | 11                | mA (max) |  |

| I <sub>DD</sub> S | Supply Current        | Output modes 1, 2, 3, 4, 5, 6<br>V <sub>IN</sub> = 0V; I <sub>O</sub> = 0A | 4.0                 | 7.0               | mA (max) |  |

| I <sub>DD</sub>   | Shutdown Current      | Output mode 0                                                              | 0.1                 | 2                 | μA (max) |  |

| Vos               | Output Offset Voltage | $V_{IN} = 0V$                                                              | 5.0                 | 50                | mV (max) |  |

| P <sub>O</sub>    | Output Power          | $SPKR_{OUT}; R_L = 4\Omega$ $THD+N = 1\%; f = 1kHz$ $LM4851LQ$             | 430                 |                   | mW       |  |

|                   |                       | SPKR <sub>OUT</sub> ; $R_L = 8\Omega$<br>THD+N = 1%; $f = 1$ kHz           | 340                 | 300               | mW (min) |  |

|                   |                       | $R_{OUT}$ and $L_{OUT}$ ; $R_{L} = 32\Omega$<br>THD+N = 0.5%; f = 1kHz     | 25                  | 20                | mW (min) |  |

# Electrical Characteristics (Notes 2, 8) (Continued)

The following specifications apply for  $V_{DD}$ = 3.0V,  $T_A$ = 25°C unless otherwise specified.

| Symbol           | Parameter                                                   | Conditions                                                                                      | LM4851              |                   | Units                              |

|------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|-------------------|------------------------------------|

|                  |                                                             |                                                                                                 | Typical<br>(Note 5) | Limit<br>(Note 6) | (Limits)                           |

|                  |                                                             | $R_{OUT}$ and $L_{OUT}$ ; $f = 1kHz$<br>$P_{OUT} = 20mW$ ; $R_L = 32\Omega$                     |                     | 0.5               | % (max)                            |

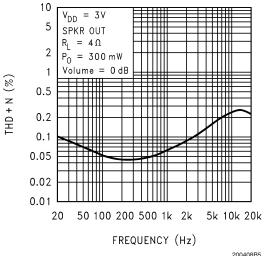

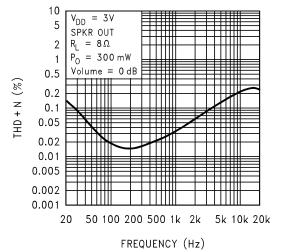

|                  |                                                             | SPKR <sub>OUT</sub> ; $f = 1kHz$<br>P <sub>OUT</sub> = 300mW; R <sub>L</sub> = 8 $\Omega$       |                     | 1.0               | % (max)                            |

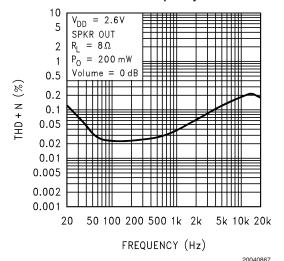

| HD+N             | Total Harmonic Distortion Plus                              | $R_{OUT}$ and $L_{OUT}$ ; $f = 20Hz$ to $20kHz$<br>$P_{OUT} = 20mW$ ; $R_L = 32\Omega$          | 0.4                 |                   | %                                  |

|                  | Noise                                                       | SPKR <sub>OUT</sub> ; f = 20Hz to 20kHz<br>$P_{OUT}$ = 300mW; $R_L$ = $4\Omega$<br>LM4851LQ     | 0.3                 |                   | %                                  |

|                  |                                                             | SPKR <sub>OUT</sub> ; f = 20Hz to 20kHz<br>P <sub>OUT</sub> = 250mW; R <sub>L</sub> = $8\Omega$ | 0.3                 |                   | %                                  |

| N <sub>OUT</sub> | Output Noise                                                | A-weighted (Note 10)                                                                            | 29                  |                   | μV                                 |

| PSRR             | Power Supply Rejection Ratio                                | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> ; f = 217Hz<br>Input floating; Input referred         | 70                  |                   | dB                                 |

|                  |                                                             | $V_{RIPPLE} = 200 m V_{PP}$ ; f = 217Hz<br>Input terminated into 50 $\Omega$ ; Output referred  | 62                  |                   | dB                                 |

| ′ін              | Logic High Input Voltage                                    |                                                                                                 |                     | 1.4<br>3.0        | V (min)<br>V (max)                 |

| / <sub>IL</sub>  | Logic Low Input Voltage                                     |                                                                                                 |                     | 0.4               | V (max)                            |

|                  | Digital Volume Range (R <sub>IN</sub> and L <sub>IN</sub> ) | Input referred minimum gain Input referred maximum gain                                         | -40.5<br>+6         |                   | dB                                 |

|                  | Digital Volume Stepsize                                     |                                                                                                 | 1.5                 |                   | dB                                 |

|                  | Stepsize Error                                              |                                                                                                 | ±0.5                |                   | dB                                 |

|                  | Phone In Volume                                             | BTL gain from<br>Phone In to SPKR <sub>OUT</sub>                                                | 6                   |                   | dB                                 |

|                  | Phone In Volume                                             | BTL gain from Phone In to R <sub>OUT</sub> ,L <sub>OUT</sub>                                    | 0                   |                   | dB                                 |

|                  | Phone In Input Impedance                                    | 0017 001                                                                                        | 20                  | 15<br>25          | $k\Omega$ (min)<br>$k\Omega$ (max) |

|                  | R <sub>IN</sub> and L <sub>IN</sub>                         |                                                                                                 | 50                  | 37.5<br>62.5      | $k\Omega$ (min)<br>$k\Omega$ (max) |

| ES               | Enable Setup Time (ENB)                                     |                                                                                                 |                     | 20                | ns (min)                           |

| <u>-5</u><br>EH  | Enable Hold Time (ENB)                                      |                                                                                                 |                     | 20                | ns (min)                           |

| =:<br>EL         | Enable Low Time (ENB)                                       |                                                                                                 |                     | 30                | ns (min)                           |

| os               | Data Setup Time (DATA)                                      |                                                                                                 |                     | 20                | ns (min)                           |

| )H               | Data Hold Time (DATA)                                       |                                                                                                 |                     | 20                | ns (min)                           |

| cs               | Clock Setup Time (CLK)                                      |                                                                                                 |                     | 20                | ns (min)                           |

| СН               | Clock Logic High Time (CLK)                                 |                                                                                                 |                     | 50                | ns (min)                           |

| CL               | Clock Logic Low Time (CLK)                                  |                                                                                                 |                     | 50                | ns (min)                           |

| CLK              | Clock Frequency                                             |                                                                                                 |                     | DC<br>10          | (min)<br>MHz (max                  |

Note 2: Absolute Maximum Rating indicate limits beyond which damage to the device may occur.

**Note 3:** Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

Note 5: Typical specifications are specified at +25°C and represent the most likely parametric norm.

Note 6: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 7: Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200pF cap is charged to the specified voltage, then discharged directly into the IC with no external series resistor (resistance of discharge path must be under  $50\Omega$ ).

Note 8: All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 9: The given  $\theta_{JA}$  and  $\theta_{JC}$  is for an LM4851 mounted on a demonstration board with a 4 in<sup>2</sup> area of 1oz printed circuit board copper ground plane.

Note 10: Please refer to the Output Noise vs Output Mode table in the Typical Performance Characteristics section for more details.

## **External Components Description**

Figure 1

| Components |                 | Functional Description                                                                                                                                                                                                                         |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.         | C <sub>in</sub> | This is the input coupling capacitor. It blocks the DC voltage at, and couples the the input signal to, the amplifier's input terminals. $C_i$ , also creates a highpass filter with the internal resistor $R_i$ at $f_c = 1/(2\pi R_i C_i)$ . |

| 2.         | $C_s$           | This is the supply bypass capacitor. It provides power supply filtering.                                                                                                                                                                       |

| 3.         | Св              | This is the BYPASS pin capacitor. It provides half-supply filtering.                                                                                                                                                                           |

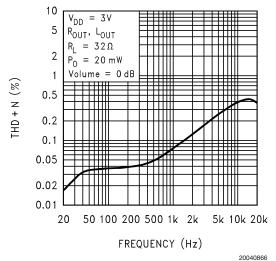

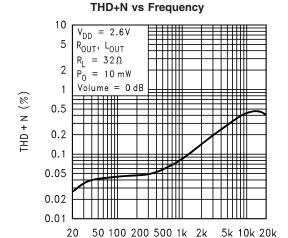

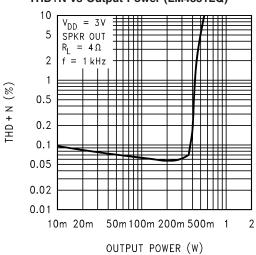

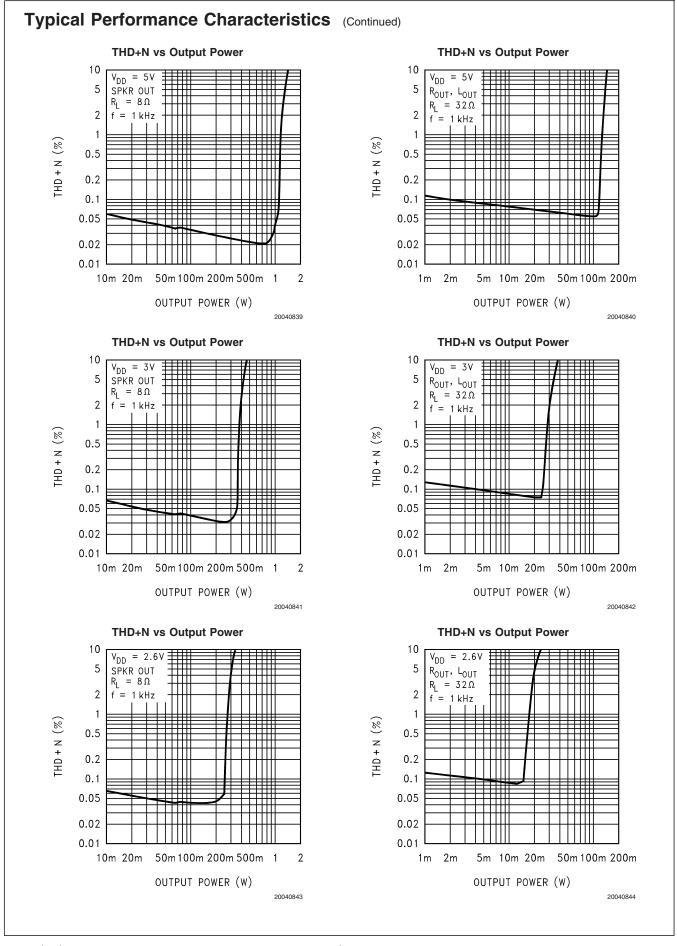

# **Typical Performance Characteristics**

## THD+N vs Frequency (LM4851LQ)

## THD+N vs Frequency (LM4851LQ)

## THD+N vs Frequency

## THD+N vs Frequency

www.national.com

## THD+N vs Frequency

## 20040865

## THD+N vs Frequency

## THD+N vs Output Power (LM4851LQ)

## THD+N vs Frequency

FREQUENCY (Hz)

## THD+N vs Output Power (LM4851LQ)

200408B7

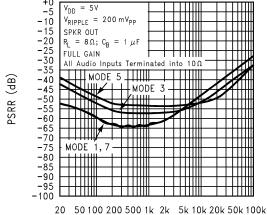

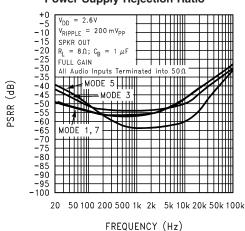

## **Power Supply Rejection Ratio**

FREQUENCY (Hz)

20040845

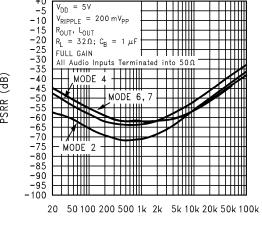

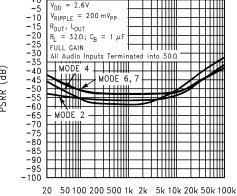

# **Power Supply Rejection Ratio**

FREQUENCY (Hz)

20040874

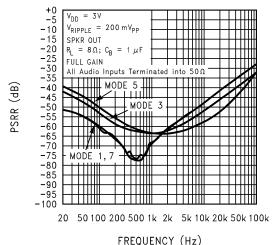

## **Power Supply Rejection Ratio**

## **Power Supply Rejection Ratio**

FREQUENCY (Hz)

20040861

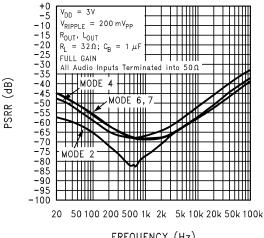

## **Power Supply Rejection Ratio**

**Power Supply Rejection Ratio**

FREQUENCY (Hz)

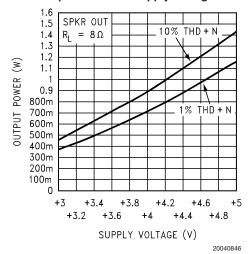

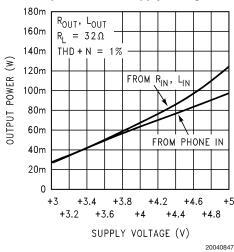

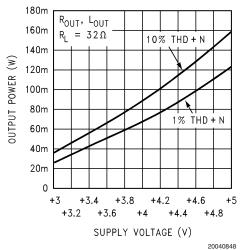

## **Output Power vs Supply Voltage**

## **Output Power vs Supply Voltage**

## **Output Power vs Supply Voltage**

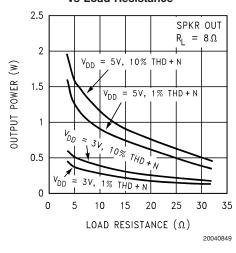

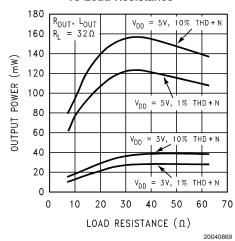

# Output Power vs Load Resistance

# Output Power vs Load Resistance

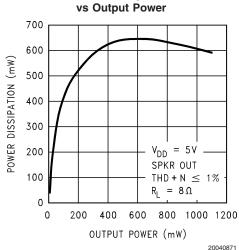

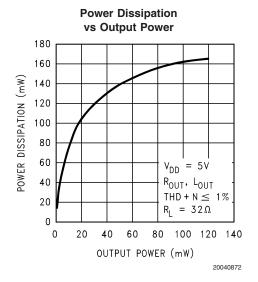

# Power Dissipation

20040871

www.national.com

10

#### vs Supply Voltage 8 No Load 7 SUPPLY CURRENT (mA) 6 MODE 7 5 4 MODE 1, 3, 5 3 2 MODE 2, 4, 6 0 3 2 2.5 3.5 4.5 5 SUPPLY VOLTAGE (V) 20040855

**Supply Current**

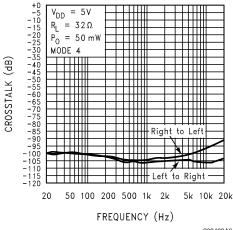

## **Channel Separation** vs Frequency

200408A6

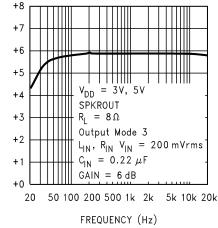

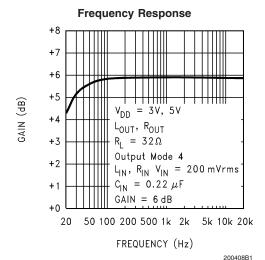

## **Frequency Response** +8 +7 +5 GAIN (dB) +4 $V_{DD} = 3V, 5V$ SPKROUT +3 $R_L = 8\Omega$ +2 Output Mode 1, 7 $PIN V_{IN} = 200 \, mVrms$ $C_{IN} = 0.22 \,\mu F$ +0

200408A8

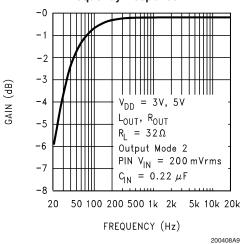

## **Frequency Response**

## **Frequency Response**

20

GAIN (dB)

50 100 200 500 1k 2k 5k 10k 20k

FREQUENCY (Hz)

200408B0

## Output Noise vs Output Mode (V<sub>DD</sub> = 3V, 5V; A-weighted)

| Output Mode | SPKROUT      | LOUT/ROUT    |

|-------------|--------------|--------------|

|             | Output Noise | Output Noise |

|             | (µV)         | (μV)         |

| 1           | 29           | X            |

| 2           | X            | 21           |

| 3           | 37 (G = 0dB) | X            |

|             | 42 (G = 6dB) |              |

| 4           | Х            | 29 (G = 0dB) |

|             |              | 32 (G = 6dB) |

| 5           | 48 (G = 0dB) | X            |

|             | 53 (G = 6dB) |              |

| 6           | Х            | 34 (G = 0dB) |

|             |              | 37 (G = 6dB) |

| 7           | 29           | 34 (G = 0dB) |

|             |              | 37 (G = 6dB) |

12

G = volume control gain

X = Not applicable

# **Application Information**

## SPI PIN DESCRIPTION

DATA: This is the serial data input pin.

CLK: This is the clock input pin.

ENB: This is the SPI enable pin and is active-high.

## SPI OPERATION DESCRIPTION

The serial data bits are organized into a field which contains 8 bits of data defined by TABLE 1. The Data 0 to Data 2 bits determine the output mode of the LM4851 as shown in TABLE 2. The Data 3 to Data 7 bits determine the volume level setting as illustrated by TABLE 3. For each SPI transfer, the data bits are written to the DATA pin with the least significant bit (LSB) first. All serial data are sampled at the rising edge of the CLK signal. Once all the data bits have been sampled, ENB transitions from logic-high to logic-low to complete the SPI sequence. All 8 bits must be received before any data latch can occur. Any excess CLK and DATA transitions will be ignored after the eighth rising clock edge

has occurred. For any data sequence longer than 8 bits, only the first 8 bits will get loaded into the shift register and the rest of the bits will be disregarded.

**TABLE 1. Bit Allocation**

| Data 0 | Mode 1   |

|--------|----------|

| Data 1 | Mode 2   |

| Data 2 | Mode 3   |

| Data 3 | Volume 1 |

| Data 4 | Volume 2 |

| Data 5 | Volume 3 |

| Data 6 | Volume 4 |

| Data 7 | Volume 5 |

**TABLE 2. Output Mode Selection**

| Output Mode # | Data 2 | Data 1 | Data 0 | SPKR <sub>OUT</sub> | R <sub>OUT</sub> | L <sub>OUT</sub> |

|---------------|--------|--------|--------|---------------------|------------------|------------------|

| 0             | 0      | 0      | 0      | SD                  | SD               | SD               |

| 1             | 0      | 0      | 1      | 6dB x P             | SD               | SD               |

| 2             | 0      | 1      | 0      | SD                  | Р                | Р                |

| 3             | 0      | 1      | 1      | G(R+L)              | SD               | SD               |

| 4             | 1      | 0      | 0      | SD                  | GxR              | GxL              |

| 5             | 1      | 0      | 1      | G(R+L) + 6dB x P    | SD               | SD               |

| 6             | 1      | 1      | 0      | SD                  | (G x R) + P      | (G x L) + P      |

| 7             | 1      | 1      | 1      | 6dB x P             | (G x R) + P      | (G x L) + P      |

P = Phone In

Default Mode upon device power-up is Output Mode 0

R = RinL = Lin

SD = Shutdown

G = Gain of volume control

**TABLE 3. Volume Control Settings**

| Gain (dB) | Data 7 | Data 6 | Data 5 | Data 4 | Data 3 |

|-----------|--------|--------|--------|--------|--------|

| -40.5     | 0      | 0      | 0      | 0      | 0      |

| -39.0     | 0      | 0      | 0      | 0      | 1      |

| -37.5     | 0      | 0      | 0      | 1      | 0      |

| -36.0     | 0      | 0      | 0      | 1      | 1      |

| -34.5     | 0      | 0      | 1      | 0      | 0      |

| -33.0     | 0      | 0      | 1      | 0      | 1      |

| -31.5     | 0      | 0      | 1      | 1      | 0      |

| -30.0     | 0      | 0      | 1      | 1      | 1      |

| -28.5     | 0      | 1      | 0      | 0      | 0      |

| -27.0     | 0      | 1      | 0      | 0      | 1      |

| -25.5     | 0      | 1      | 0      | 1      | 0      |

| -24.0     | 0      | 1      | 0      | 1      | 1      |

| -22.5     | 0      | 1      | 1      | 0      | 0      |

| -21.0     | 0      | 1      | 1      | 0      | 1      |

| -19.5     | 0      | 1      | 1      | 1      | 0      |

| -18.0     | 0      | 1      | 1      | 1      | 1      |

| -16.5     | 1      | 0      | 0      | 0      | 0      |

| -15.0     | 1      | 0      | 0      | 0      | 1      |

| -13.5     | 1      | 0      | 0      | 1      | 0      |

| -12.0     | 1      | 0      | 0      | 1      | 1      |

| -10.5     | 1      | 0      | 1      | 0      | 0      |

| -9.0      | 1      | 0      | 1      | 0      | 1      |

| -7.5      | 1      | 0      | 1      | 1      | 0      |

| -6.0      | 1      | 0      | 1      | 1      | 1      |

| -4.5      | 1      | 1      | 0      | 0      | 0      |

| -3.0      | 1      | 1      | 0      | 0      | 1      |

| -1.5      | 1      | 1      | 0      | 1      | 0      |

| 0.0       | 1      | 1      | 0      | 1      | 1      |

| 1.5       | 1      | 1      | 1      | 0      | 0      |

| 3.0       | 1      | 1      | 1      | 0      | 1      |

| 4.5       | 1      | 1      | 1      | 1      | 0      |

| 6.0       | 1      | 1      | 1      | 1      | 1      |

#### SPI OPERATIONAL REQUIREMENTS

- 1. The data bits are transmitted with the LSB first.

- 2. The maximum clock rate is 10MHz for the CLK pin.

- 3. CLK must remain logic-high for at least 50ns ( $t_{CH}$ ) after the rising edge of CLK, and CLK must remain logic-low for at least 50ns ( $t_{CL}$ ) after the falling edge of CLK.

- 4. The serial data bits are sampled at the rising edge of CLK. Any transition on DATA must occur at least 20ns ( $t_{\rm DS}$ ) before the rising edge of CLK. Also, any transition on DATA must occur at least 20ns ( $t_{\rm DH}$ ) after the rising edge of CLK and stabilize before the next rising edge of CLK.

- 5. ENB should be logic-high only during serial data transmission.

- 6. ENB must be logic-high at least 20ns ( $t_{\rm ES}$ ) before the first rising edge of CLK, and ENB has to remain logic-high at least 20ns ( $t_{\rm EH}$ ) after the eighth rising edge of CLK.

- 7. If ENB remains logic-low for more than 10ns before all 8 bits are transmitted then the data latch will be aborted.

- 8. If ENB is logic-high for more than 8 CLK pulses then only the first 8 data bits will be latched and activated when ENB transitions to logic-low.

- 9. ENB must remain logic-low for at least 30ns ( $t_{\rm EL}$ ) after all 8 bits are transmitted to latch in the data.

- 10. Coincidental rising or falling edges of CLK and ENB are not allowed. If CLK is to be held logic-high after the data transmission, the falling edge of CLK must occur at least 20ns ( $t_{\rm CS}$ ) before ENB transitions to logic-high for the next set of data

FIGURE 2. SPI Timing Diagram

## **EXPOSED-DAP MOUNTING CONSIDERATIONS**

The LM4851's exposed-DAP (die attach paddle) package (LQ) provides a low thermal resistance between the die and the PCB to which the part is mounted and soldered. This allows rapid heat transfer from the die to the surrounding PCB copper area heatsink, copper traces, ground plane, and finally, surrounding air. The result is a low voltage audio power amplifier that produces 1.1W dissipation in an  $8\Omega$  load at  $\leq$  1% THD+N. This high power is achieved through careful consideration of necessary thermal design. Failing to optimize thermal design may compromise the LM4851's high power performance and activate unwanted, though necessary, thermal shutdown protection.

The LQ package must have its DAP soldered to a copper pad on the PCB. The DAP's PCB copper pad is then, ideally, connected to a large plane of continuous unbroken copper. This plane forms a thermal mass, heat sink, and radiation area. Place the heat sink area on either outside plane in the case of a two-sided or multi-layer PCB. (The heat sink area can also be placed on an inner layer of a multi-layer board. The thermal resistance, however, will be higher.) Connect the DAP copper pad to the inner layer or backside copper heat sink area with 6 (3 X 2) (LQ) vias. The via diameter should be 0.012in - 0.013in with a 1.27mm pitch. Ensure efficient thermal conductivity by plugging and tenting the vias with plating and solder mask, respectively.

Best thermal performance is achieved with the largest practical copper heat sink area. If the heatsink and amplifier share the same PCB layer, a nominal  $2.5 \text{in}^2$  (min) area is necessary for 5V operation with a  $4\Omega$  load. Heatsink areas not placed on the same PCB layer as the LM4851 should be  $5 \text{in}^2$  (min) for the same supply voltage and load resistance. The last two area recommendations apply for  $25\,^{\circ}\text{C}$  ambient temperature. Increase the area to compensate for ambient temperatures above  $25\,^{\circ}\text{C}$ . In all circumstances and under all conditions, the junction temperature must be held below  $150\,^{\circ}\text{C}$  to prevent activating the LM4851's thermal shutdown protection. Further detailed and specific information concerning PCB layout and fabrication and mounting an LQ (LLP) is found in National Semiconductor's AN1187.

# PCB LAYOUT AND SUPPLY REGULATION CONSIDERATIONS FOR DRIVING $3\Omega$ AND $4\Omega$ LOADS

Power dissipated by a load is a function of the voltage swing across the load and the load's impedance. As load impedance decreases, load dissipation becomes increasingly dependent on the interconnect (PCB trace and wire) resistance between the amplifier output pins and the load's connections. Residual trace resistance causes a voltage drop, which results in power dissipated in the trace and not in the load as desired. For example,  $0.1\Omega$  trace resistance reduces the output power dissipated by a  $4\Omega$  load from 1.7W to 1.6W. The problem of decreased load dissipation is exacerbated

15 www.national.com

as load impedance decreases. Therefore, to maintain the highest load dissipation and widest output voltage swing, PCB traces that connect the output pins to a load must be as wide as possible.

Poor power supply regulation adversely affects maximum output power. A poorly regulated supply's output voltage decreases with increasing load current. Reduced supply voltage causes decreased headroom, output signal clipping, and reduced output power. Even with tightly regulated supplies, trace resistance creates the same effects as poor supply regulation. Therefore, making the power supply traces as wide as possible helps maintain full output voltage swing.

## **BRIDGE CONFIGURATION EXPLANATION**

As shown in Figure 1, the LM4851 consists of three pairs of output amplifier blocks (A4-A6). A4, A5, and A6 consist of bridged-tied amplifier pairs that drive LOUT, ROUT, and SPKROUT respectively. The LM4851 drives a load, such as a speaker, connected between outputs, SPKROUT+ and SPKROUT-. In the amplifier block A6, the output of the amplifier that drives SPKROUT- serves as the input to the unity gain inverting amplifier that drives SPKROUT+.

This results in both amplifiers producing signals identical in magnitude, but 180° out of phase. Taking advantage of this phase difference, a load is placed between SPKROUT- and SPKROUT+ and driven differentially (commonly referred to as 'bridge mode'). Assuming  $R_{\text{F}}=R_{\text{I}}$ , this results in a differential or BTL gain of:

$$A_{VD} = 2(R_f/R_i) = 2$$

(1)

Bridge mode amplifiers are different from single-ended amplifiers that drive loads connected between a single amplifier's output and ground. For a given supply voltage, bridge mode has a distinct advantage over the single-ended configuration: its differential output doubles the voltage swing across the load. Theoretically, this produces four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited and that the output signal is not clipped.

Another advantage of the differential bridge output is no net DC voltage across the load. This is accomplished by biasing SPKROUT- and SPKROUT+ outputs at half-supply. This eliminates the coupling capacitor that single supply, single-ended amplifiers require. Eliminating an output coupling capacitor in a typical single-ended configuration forces a single-supply amplifier's half-supply bias voltage across the load. This increases internal IC power dissipation and may permanently damage loads such as speakers.

## **POWER DISSIPATION**

Power dissipation is a major concern when designing a successful single-ended or bridged amplifier.

A direct consequence of the increased power delivered to the load by a bridge amplifier is higher internal power dissipation. The LM4851 has a pair of bridged-tied amplifiers driving a handsfree speaker, SPKROUT. The maximum internal power dissipation operating in the bridge mode is twice that of a single-ended amplifier. From Equation (2), assuming a 5V power supply and an  $8\Omega$  load, the maximum SPKROUT power dissipation is 634mW.

$$P_{DMAX-SPKROUT} = 4(V_{DD})^2/(2\pi^2 R_L)$$

: Bridge Mode (2)

The LM4851 also has 2 pairs of bridged-tied amplifiers driving stereo headphones, ROUT and LOUT. The maximum internal power dissipation for ROUT and LOUT is given by equation (3) and (4). From Equations (3) and (4), assuming a 5V power supply and a  $32\Omega$  load, the maximum power dissipation for LOUT and ROUT is 158mW, or 316mW total.

$$P_{DMAX-LOUT} = 4(V_{DD})^2/(2\pi^2 R_L)$$

: Bridge Mode (3)

$$P_{DMAX-ROUT} = 4(V_{DD})^2/(2\pi^2 R_L)$$

: Bridge Mode (4)

The maximum internal power dissipation of the LM4851 occurs when all 3 amplifiers pairs are simultaneously on; and is given by Equation (5).

$$P_{DMAX\text{-}TOTAL} = \\ P_{DMAX\text{-}SPKROUT} + P_{DMAX\text{-}LOUT} + P_{DMAX\text{-}ROUT}$$

(5)

The maximum power dissipation point given by Equation (5) must not exceed the power dissipation given by Equation (6):

$$P_{DMAX}' = (T_{JMAX} - T_A)/\theta_{JA}$$

(6)

The LM4851's TJMAX = 150°C. In the IBL and ITL packages, the LM4851's  $\theta_{JA}$  is 48°C/W. In the LQ package soldered to a DAP pad that expands to a copper area of  $2.5 \text{in}^2$  on a PCB, the LM4851's  $\theta_{JA}$  is 42°C/W. At any given ambient temperature  $T_A$ , use Equation (6) to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation (6) and substituting  $P_{DMAX-TOTAL}$  for  $P_{DMAX}$  results in Equation (7). This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM4851's maximum junction temperature.

$$T_{A} = T_{JMAX} - P_{DMAX-TOTAL} \theta_{JA}$$

(7)

For a typical application with a 5V power supply and an  $8\Omega$  load, the maximum ambient temperature that allows maximum stereo power dissipation without exceeding the maximum junction temperature is approximately  $104^{\circ}C$  for the IBL package.

$$T_{JMAX} = P_{DMAX-TOTAL} \theta_{JA} + T_{A}$$

(8)

Equation (8) gives the maximum junction temperature T<sub>J</sub>-MAX. If the result violates the LM4851's 150°C, reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is a surface mount part operating around the maximum power dissipation point. Since internal power dissipation is a function of output

power, higher ambient temperatures are allowed as output power or duty cycle decreases. If the result of Equation (5) is greater than that of Equation (6), then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. If these measures are insufficient, a heat sink can be added to reduce  $\theta_{\text{JA}}.$  The heat sink can be created using additional copper area around the package, with connections to the ground pin(s), supply pin and amplifier output pins. External, solder attached SMT heatsinks such as the Thermalloy 7106D can also improve power dissipation. When adding a heat sink, the  $\theta_{JA}$  is the sum of  $\theta_{JC}$ ,  $\theta_{CS}$ , and  $\theta_{SA}.$  ( $\theta_{JC}$  is the junction-to-case thermal impedance,  $\theta_{CS}$  is the case-to-sink thermal impedance, and  $\theta_{\text{SA}}$  is the sink-toambient thermal impedance.) Refer to the Typical Performance Characteristics curves for power dissipation information at lower output power levels.

## **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 5V regulator typically use a 10µF in parallel with a 0.1µF filter capacitors to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 1.0µF tantalum bypass capacitance connected between the LM4851's supply pins and ground. Keep the length of leads and traces that connect capacitors between the LM4851's power supply pin and ground as short as possible. Connecting a  $1\mu F$  capacitor,  $C_B$ , between the BYPASS pin and ground improves the internal bias voltage's stability and improves the amplifier's PSRR. The PSRR improvements increase as the bypass pin capacitor value increases. Too large, however, increases turn-on time and can compromise the amplifier's click and pop performance. The selection of bypass capacitor values, especially C<sub>B</sub>, depends on desired PSRR requirements, click and pop performance (as explained in the section, Proper Selection of External Components), system cost, and size constraints.

#### SELECTING EXTERNAL COMPONENTS

## **Input Capacitor Value Selection**

Amplifying the lowest audio frequencies requires high value input coupling capacitor ( $C_i$  in Figure 1). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using speakers with this limited frequency response reap little improvement by using large input capacitor.

The internal input resistor  $(R_i)$  and the input capacitor  $(C_i)$  produce a high pass filter cutoff frequency that is found using Equation (9).

$$f_c = 1 / (2\pi R_i C_i)$$

(9)

As an example when using a speaker with a low frequency limit of 150Hz,  $C_{\rm i}$ , using Equation (9) is  $0.063\mu F$ . The  $0.22\mu F$   $C_{\rm i}$  shown in Figure 1 allows the LM4851 to drive high efficiency, full range speaker whose response extends below 40Hz.

#### **Bypass Capacitor Value Selection**

Besides minimizing the input capacitor size, careful consideration should be paid to value of  $C_{\rm B}$ , the capacitor connected to the BYPASS pin. Since  $C_{\rm B}$  determines how fast the LM4851 settles to quiescent operation, its value is critical when minimizing turn-on pops. The slower the LM4851's outputs ramp to their quiescent DC voltage (nominally  $V_{\rm DD}/2$ ), the smaller the turn-on pop. Choosing  $C_{\rm B}$  equal to  $1.0\mu{\rm F}$  along with a small value of  $C_{\rm i}$  (in the range of  $0.1\mu{\rm F}$  to  $0.39\mu{\rm F}$ ), produces a click-less and pop-less shutdown function. As discussed above, choosing  $C_{\rm i}$  no larger than necessary for the desired bandwidth helps minimize clicks and pops.  $C_{\rm B}$ 's value should be in the range of 5 times to 7 times the value of  $C_{\rm i}$ . This ensures that output transients are eliminated when power is first applied or the LM4851 resumes operation after shutdown.

17 www.national.com

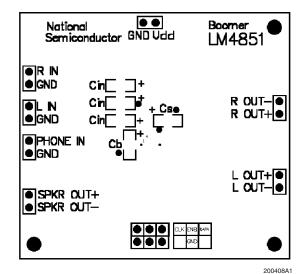

# **Demonstration Board Layout**

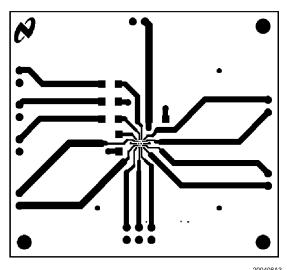

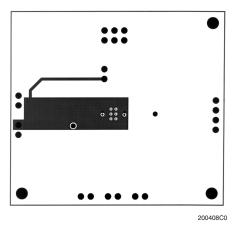

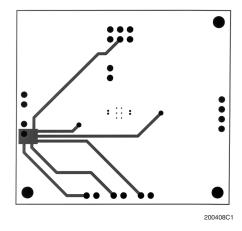

FIGURE 3. Recommended IBL, ITL PC Board Layout: Top Silkscreen

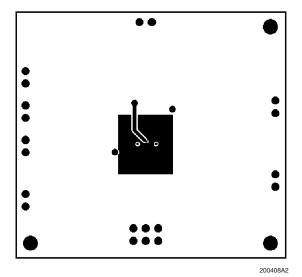

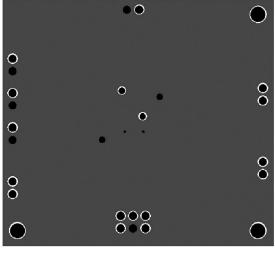

FIGURE 4. Recommended IBL, ITL PC Board Layout: Inner Layer

200400A

FIGURE 5. Recommended IBL, ITL PC Board Layout: Top Layer

200408A4

FIGURE 6. Recommended IBL, ITL PC Board Layout:

Bottom Layer

# **Demonstration Board Layout**

(Continued)

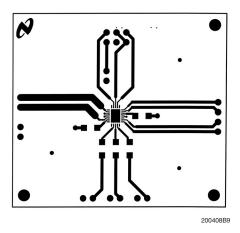

FIGURE 7. Recommended LQ PC Board Layout: Top Silkscreen Layer

FIGURE 8. Recommended LQ PC Board Layout: Top Layer

FIGURE 9. Recommended LQ PC Board Layout: Innner Layer 1

FIGURE 10. Recommended LQ PC Board Layout: Innner Layer 2

FIGURE 11. Recommended LQ PC Board Layout:

Bottom Layer

19 www.national.com

# Physical Dimensions inches (millimeters) unless otherwise noted

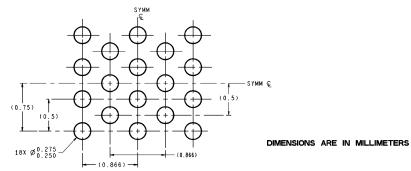

#### LAND PATTERN RECOMMENDATION

18-Bump micro SMD Order Number LM4851IBL NS Package Number BLA18AAB  $X_1 = 1.996 \ X_2 = 2.225 \ X_3 = 0.945$

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued) Output O

18-Bump micro SMD Order Number LM4851ITL NS Package Number TLA18AAA  $X_1 = 1.996 \ X_2 = 2.225 \ X_3 = 0.600$

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

DIMENSIONS ARE IN MILLIMETERS RECOMMENDED LAND PATTERN 1:1 RATION WITH PKG SOLDER PADS

24-Lead MOLDED PKG, Leadless Leadframe Package LLP Order Number LM4851LQ **NS Package Number LQA24A**

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Email: support@nsc.com

www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.