### CD54AC193/3A CD54ACT193/3A

# Presettable Synchronous 4-Bit Binary Up/Down Counter with Reset

The RCA CD54AC193/3A and CD54ACT193/3A are up/ down binary counters with separate up/down clocks. These devices utilize the new RCA ADVANCED CMOS LOGIC technology. Presetting the counter to the number on preset data inputs (P0-P3) is accomplished by a LOW asynchronous parallel load input (PL). The counter is incremented on the LOW-to-HIGH transition of the Clock-Up input (and a HIGH level on the Clock-Down input) and decremented on the LOW-to-HIGH transition of the Clock-Down input (and a HIGH level on the Clock-Up input). A HIGH level on the Reset input overrides any other input to clear the counter to its zero state. The TCU (carry) output goes LOW half a clock period before the zero count is reached and returns to a HIGH level at the zero count. The TCD (borrow) output in the count down mode likewise goes LOW half a clock period before the maximum count (15 counts) and returns to HIGH at the maximum count. Cascading is effected by connecting the TCU and TCD outputs of a less significant counter to the Clock-Up and Clock-Down inputs, respectively, of the next most significant counter.

The CD54AC193/3A and CD54ACT193/3A are supplied in 16-lead dual-in-line ceramic packages (F suffix).

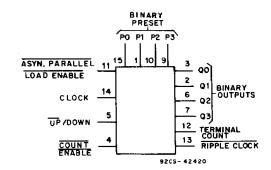

# FUNCTIONAL DIAGRAM & TERMINAL ASSIGNMENT

# Package Specifications See Section 11, Fig. 11

#### Static Electrical Characteristics (Limits with black dots (•) are tested 100%.)

|                                       | TEST CONDITIONS              |                        |                 | AMBIENT TEMPERATURE (TA) - °C |      |             |      |       |

|---------------------------------------|------------------------------|------------------------|-----------------|-------------------------------|------|-------------|------|-------|

| CHARACTERISTICS                       |                              |                        | V <sub>cc</sub> | +25                           |      | -55 to +125 |      | UNITS |

|                                       | V <sub>1</sub> (V)           | l <sub>o</sub><br>(mA) | (Ÿ)             | MIN.                          | MAX. | MIN.        | MAX. | 1     |

| Quiescent Supply<br>Current (MSI) Icc | V <sub>cc</sub><br>or<br>GND | 0                      | 5.5             | _                             | 8•   | _           | 160∙ | μΑ    |

The complete static electrical test specification consists of the above by-type static tests combined with the standard static tests in the beginning of this section.

#### **ACT INPUT LOADING TABLE**

| INPUT        | UNIT LOAD* |  |  |  |

|--------------|------------|--|--|--|

| P0 — P3, PL  | 0.75       |  |  |  |

| MR, CPU, CPD | 0.85       |  |  |  |

\*Unit load is ∆I<sub>CC</sub> limit specified in Static Characteristics Chart, e.g., 2.4 mA max. @ 25° C.

#### Burn-In Test-Circuit Connections (Use Static II for /3A burn-in and Dynamic for Life Test.)

| Static        |                   | STATIC BURN-II   | N I                      | STATIC BURN-IN II         |            |                      |  |

|---------------|-------------------|------------------|--------------------------|---------------------------|------------|----------------------|--|

|               | OPEN              | GROUND           | V <sub>∞</sub> (6V)      | OPEN                      | GROUND     | V <sub>cc</sub> (6V) |  |

| CD54AC/ACT193 | 2,3,6,7,12,<br>13 | 1,4,5,8-11,14,15 | 16                       | 2,3,6,7,12,<br>13         | 8          | 1,4,5,9-11,14-16     |  |

| Dunamia       | OPEN              | GROUND           | 1/2 V <sub>cc</sub> (3V) | (3V) V <sub>cc</sub> (6V) | OSCILLATOR |                      |  |

| Dynamic       | OPEN              |                  | 1/2 466 (04)             |                           | 50 kHz     | 25 kHz               |  |

| CD54AC/ACT193 |                   | 1,8-10,14,15     | 2,3,6,7,12,13            | 4,11,16                   | 5          |                      |  |

NOTE: Each pin except Vcc and Gnd will have a resistor of 2k-47k ohms.

## CD54AC193/3A CD54ACT193/3A

SWITCHING CHARACTERISTICS: AC Series; t,, t, = 3 ns, C, = 50 pF (Worst Case)

| CHARACTERISTICS                 | SYMBOL                               | V <sub>cc</sub><br>(V) | -55 t         |                   |       |

|---------------------------------|--------------------------------------|------------------------|---------------|-------------------|-------|

|                                 |                                      |                        | MIN.          | MAX.              | UNITS |

| Propagation Delays:<br>PL to Qn | t <sub>PLH</sub><br>t <sub>PHL</sub> | 1.5<br>3.3*<br>5†      | <u>-</u>      | 200<br>29<br>15   | ns    |

| CPU to Qn<br>CPD to Qn          | t <sub>PLH</sub><br>t <sub>PHL</sub> | 1.5<br>3.3<br>5        | _<br>_<br>_   | 188<br>27<br>14•  | ns    |

| CPU to TCU<br>CPD to TCD        | tplн<br>tpнL                         | 1.5<br>3.3<br>5        |               | 152<br>22<br>11.2 | ns    |

| MR to Qn                        | telн<br>teнl                         | 1.5<br>3.3<br>5        | _<br>_<br>_   | 215<br>30<br>16   | ns    |

| MR to TCU                       | telh<br>tehl                         | 1.5<br>3.3<br>5        | _<br>         | 200<br>29<br>15   | ns    |

| MR to TCD                       | telн<br>teнl                         | 1.5<br>3.3<br>5        |               | 245<br>35<br>18.2 | ns    |

| Pn to Qn                        | telh<br>tehl                         | 1.5<br>3.3<br>5        | <u>-</u><br>- | 222<br>31<br>16.5 | ns    |

| Power Dissipation Capacitance   | C <sub>PD</sub> §                    |                        | 9             | pF                |       |

| Input Capacitance               | Cı                                   |                        | _             | 10                | pF    |

#### SWITCHING CHARACTERISTICS: ACT Series; t,, t, = 3 ns, C<sub>L</sub> = 50 pF (Worst Case)

| CHARACTERISTICS                 | SYMBOL             | V <sub>cc</sub><br>(V) | -55 to       |      |       |

|---------------------------------|--------------------|------------------------|--------------|------|-------|

|                                 |                    |                        | MIN.         | MAX. | UNITS |

| Propagation Delays:<br>PL to Qn |                    | 5†                     | <del>-</del> | 15   |       |

| CPU to Qn                       |                    | 5                      | <u> </u>     | 14•  |       |

| CPD to Qn                       |                    | 5                      | _            | 14   |       |

| CPU to TCU                      |                    | 5                      | _            | 11.2 |       |

| CPD to TCD                      | t <sub>PLH</sub>   | 5                      | <del></del>  | 11.2 | ns    |

| MR to QN                        | t <sub>PHL</sub> - | 5                      | _            | 16   |       |

| MR to TCU                       |                    | 5                      |              | 15   |       |

| MR to TCD                       |                    | 5                      | <del>-</del> | 18.2 |       |

| Pn to Qn                        |                    | 5                      | _            | 16.5 |       |

| Power Dissipation Capacitance   | C <sub>PD</sub> §  | _                      | 126 Typ.     |      | ρF    |

| Input Capacitance               | C,                 | _                      | _            | 10   | pF    |

\*3.3 V: min. is @ 3.6 V max. is @ 3 V

$\S{C}_{PD}$  is used to determine the dynamic power consumption per package.

min. is @ 5.5 V †5 V: max. is @ 4.5 V For AC,  $P_D = C_{PD}V_{CC}^2 f_i + \sum (C_L V_{CC}^2 f_o)$ For ACT,  $P_D = C_{PD}V_{CC}^2 f_i + \sum (C_L V_{CC}^2 f_o) + V_{CC}\Delta I_{CC}$  where  $f_i = input$  frequency

$f_o = \text{output frequency}$   $C_L = \text{output load capacitance}$

V<sub>cc</sub> = supply voltage

(Limits with black dots (•) are tested 100%.)