# Product Preview

# 500 mA, Wide Input Range, LDO Linear Voltage Regulator

The NCP4629 is a CMOS 500 mA LDO linear voltage regulator which features a high input voltage range while maintaining a low quiescent current. Several protection features like current limiting and thermal shutdown are fully integrated to create a versatile and robust device. A high maximum input voltage (36 V) and wide temperature range (-40°C to 105°C) makes the NCP4629 an ideal choice for high power industrial applications.

#### **Features**

- Operating Input Voltage Range: 4 V to 24 V

- Output Voltage Range: 3.0 to 12.0 V (available in 0.1 V steps)

- ±2% Output Voltage Accuracy

- Output Current: min. 500 mA (V<sub>IN</sub> = V<sub>OUT</sub> + 1 V)

- Line Regulation: 0.05%/V

- Current Limit Circuit

- Thermal Shutdown Circuit

- Available in SOT-89-5 and DPACK5 Package

- These are Pb-Free Devices

# **Typical Applications**

- Home appliances, industrial equipment

- Cable boxes, satellite receivers, entertainment systems

- Car audio equipment, navigation systems

- Notebook adaptors, LCD TVs, cordless phones and private LAN systems

- Office equipment: copiers, printers, facsimiles, scanners, projectors, monitors

Figure 1. Typical Application Schematic

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

# ON Semiconductor<sup>™</sup>

http://onsemi.com

# MARKING DIAGRAMS

DPAK-5 CASE 369AE

SOT-89 5 CASE 528AB

XX, XXX= Specific Device Code

M, MM = Date Code

A = Assembly Location

= Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.

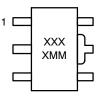

Figure 2. Simplified Schematic Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin No.<br>SOT89 | Pin No.<br>DPACK | Pin Name | Description                                                                        |  |

|------------------|------------------|----------|------------------------------------------------------------------------------------|--|

| 1                | 1                | VIN      | Input pin                                                                          |  |

| 2                | 2                | GND      | Ground pin, all ground pins must be connected together when it is mounted on board |  |

| 3                | 3                | GND      | Ground pin, all ground pins must be connected together when it is mounted on board |  |

| 4                | 4                | CE       | Chip enable pin ("H" active)                                                       |  |

| 5                | 5                | VOUT     | Output pin                                                                         |  |

# **ABSOLUTE MAXIMUM RATINGS**

| Rating                                    | Symbol           | Value            | Unit |

|-------------------------------------------|------------------|------------------|------|

| Input Voltage                             | V <sub>IN</sub>  | -0.3 to 36       | V    |

| Output Voltage                            | Vout             | -0.3 to Vin ≤ 36 | V    |

| Chip Enable Input                         | VCE              | -0.3 to Vin ≤ 36 | V    |

| Power Dissipation SOT-89                  |                  | 900              | mW   |

| Power Dissipation DPACK                   |                  | 1900             |      |

| Junction Temperature                      | T <sub>J</sub>   | -40 to 150       | °C   |

| Storage Temperature                       | T <sub>STG</sub> | -55 to 125       | °C   |

| ESD Capability, Human Body Model (Note 2) |                  | 2000             | V    |

| ESD Capability, Machine Model (Note 2)    |                  | 200              | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Duration time = 200 ms

- This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latch-up Current Maximum Rating tested per JEDEC standard: JESD78.

# THERMAL CHARACTERISTICS

| Rating                                                              | Symbol | Value | Unit |

|---------------------------------------------------------------------|--------|-------|------|

| Thermal Characteristics, SOT-89 Thermal Resistance, Junction-to-Air |        | 111   | °C/W |

| Thermal Characteristics, DPACK Thermal Resistance, Junction-to-Air  |        | 53    | °C/W |

# **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$

| Parameter                               | Test Co                                                                          | Symbol                            | Min                 | Тур  | Max   | Unit            |               |

|-----------------------------------------|----------------------------------------------------------------------------------|-----------------------------------|---------------------|------|-------|-----------------|---------------|

| Operating Input Voltage                 |                                                                                  |                                   | VIN                 | 4    |       | 24              | V             |

| Output Voltage                          | V <sub>IN</sub> = Vout + 1 V                                                     | Vout                              | x0.98               |      | x1.02 | V               |               |

| Output Voltage Temp.<br>Coefficient     | V <sub>IN</sub> = Vout + 2 V, I <sub>OUT</sub>                                   |                                   |                     | ±100 |       | ppm/°C          |               |

| Line Regulation                         | V <sub>IN</sub> = Vour + 1 V to                                                  | 24 V, I <sub>OUT</sub> = 10 mA    | Line <sub>Reg</sub> |      | 0.05  | 0.10            | %/V           |

| Load Regulation                         | V <sub>IN</sub> = Vout + 2 V, lou                                                | T = 0.1 mA to 200 mA              | Load <sub>Reg</sub> |      | 25    | 60              | mV            |

| Dropout Voltage                         | I <sub>OUT</sub> = 200 mA                                                        | 3.0 V ≤ V <sub>OUT</sub> < 5.0 V  | VDO                 |      | 0.135 | 0.225           | V             |

|                                         |                                                                                  | 5.0 V ≤ V <sub>OUT</sub> < 9.0 V  |                     |      | 0.115 | 0.180           | 1             |

|                                         |                                                                                  | 8.0 V ≤ V <sub>OUT</sub> ≤ 12.0 V |                     |      | 0.095 | 0.155           | 1             |

| Output Current                          | V <sub>IN</sub> = Vout + 1 V                                                     |                                   | Іоит                | 500  |       |                 | mA            |

| Short Current Limit                     | V <sub>OUT</sub>                                                                 | = 0 V                             | I <sub>SC</sub>     |      | 65    |                 | mA            |

| Quiescent Current                       | V <sub>IN</sub> = Vout + 1 V, V <sub>IN</sub> = Vce                              |                                   | lq                  |      | 70    | 130             | μΑ            |

| Standby Current                         | V <sub>IN</sub> = 24 V, V <sub>CE</sub> = 0 V                                    |                                   | Isтв                |      | 0.1   | 1               | μΑ            |

| CE Pin Threshold Voltage                | CE Input Voltage "H"                                                             |                                   | VCEH                | 2.0  |       | V <sub>IN</sub> | V             |

|                                         | CE Input \                                                                       | VCEL                              | 0                   |      | 0.4   | 1               |               |

| Thermal Shutdown Temperature            |                                                                                  |                                   | T <sub>SD</sub>     |      | 160   |                 | °C            |

| Thermal Shutdown Release<br>Temperature |                                                                                  |                                   | T <sub>SR</sub>     |      | 135   |                 | °C            |

| Power Supply Rejection Ratio            | $V_{IN} = V_{OUT} + 2.0 \text{ V},$<br>$\Delta V_{IN} P_{K-PK} = 0.5 \text{ V},$ | V <sub>OUT</sub> ≤ 6.0 V          | PSRR                |      | 60    |                 | dB            |

|                                         | I <sub>OUT</sub> = 100 mA, f =<br>1 kHz                                          | V <sub>OUT</sub> > 6.0 V          |                     |      | 50    |                 |               |

| Output Noise Voltage                    | V <sub>OUT</sub> = TBD V, I <sub>OUT</sub> = TBD mA, f = 10 Hz to 100 kHz        |                                   | Vn                  |      | TBD   |                 | $\mu V_{rms}$ |

# APPLICATION INFORMATION

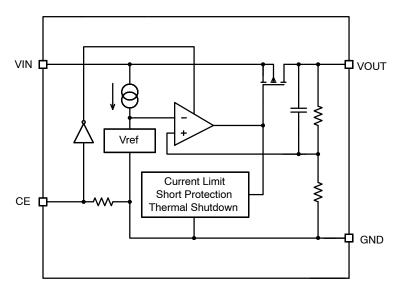

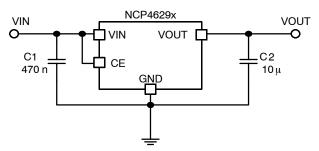

A typical application circuit for NCP4629 series is shown in Figure 3.

Figure 3. Typical Application Schematic

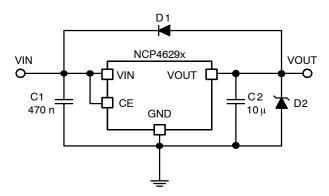

When VOUT voltage could be higher than VIN voltage it is necessary to use protective diode D1. If there is possibility that VOUT voltage could be negative then it is necessary to use schottky diode D2. See Figure 4 for details. Do not force the voltage to the VOUT pin.

Figure 4. Typical Application Schematic with Protective Diodes

#### Input Decoupling Capacitor (C1)

A 470 nF ceramic input decoupling capacitor should be connected as close as possible to the input and ground pin of the NCP4629. Higher values and lower ESR improves line transient response.

# **Output Decoupling Capacitor (C2)**

A 10  $\mu F$  ceramic output decoupling capacitor is sufficient to achieve stable operation of the IC. If tantalum capacitor is used, and its ESR is high, the loop oscillation may result. The capacitor should be connected as close as possible to the output and ground pin. Larger values and lower ESR improves dynamic parameters.

#### **Enable Operation**

The enable pin CE may be used for turning the regulator on and off. The IC is switched on when a high level voltage is applied to the CE pin. The enable pin has an internal pull down current source. If the enable function is not needed connect CE pin to VIN.

#### **Thermal**

As a power across the IC increase, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and also the ambient temperature affect the rate of temperature increase for the part. When the device has good thermal conductivity through the PCB the junction temperature will be relatively low in high power dissipation applications.

The IC includes internal thermal shutdown circuit that stops operation of regulator, if junction temperature is higher than 160°C. After that, when junction temperature decreases below 135°C, the operation of voltage regulator would restart. While high power dissipation condition is, the regulator starts and stops repeatedly and protects itself against overheating.

#### PCB layout

Pins number 2 and 3 must be wired to the GND plane while it is mounted on board. Make VIN and GND lines sufficient. If their impedance is high, noise pickup or unstable operation may result. Connect capacitors C1 and C2 as close as possible to the IC, and make wiring as short as possible.

#### **ORDERING INFORMATION**

| Device           | Nominal Output<br>Voltage | Description | Marking | Package              | Shipping <sup>†</sup> |

|------------------|---------------------------|-------------|---------|----------------------|-----------------------|

| NCP4629HDT050T5G | 5.0 V                     | Enable High | C1J050B | DPACK-5<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP4629HDT060T5G | 6.0 V                     | Enable High | C1J060B | DPACK-5<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP4629HDT120T5G | 12.0 V                    | Enable High | C1J120B | DPACK-5<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>To order other package and voltage variants, please contact your ON Semiconductor sales representative.

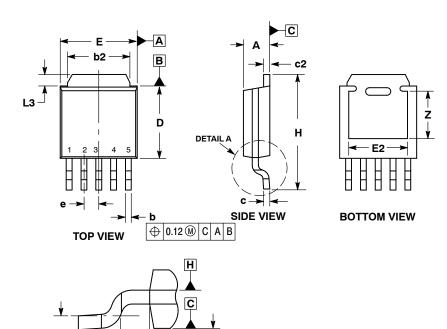

#### PACKAGE DIMENSIONS

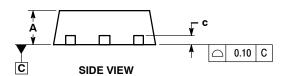

# DPAK-5 (TO-252, 5 LEAD) CASE 369AE-01 ISSUE O

Αı

**DETAIL A**

☐ 0.10 C

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. THERMAL PAD CONTOUR OPTIONAL, WITHIN DIMENSIONS b3, E2, L3 AND Z.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. THESE DIMENSIONS TO BE MEASURED AT DATUM H.

5. DIMENSIONS D AND E ARE DETERMINED AT THE

- DIMENSIONS O AND E ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY.

DATUMS A AND B ARE DETERMINED AT DATUM PLANE H.

|     | MILLIMETERS |       |  |  |  |

|-----|-------------|-------|--|--|--|

| DIM | MIN         | MAX   |  |  |  |

| Α   | 2.10        | 2.50  |  |  |  |

| A1  | 0.00        | 0.13  |  |  |  |

| b   | 0.40        | 0.60  |  |  |  |

| b2  | 5.14        | 5.54  |  |  |  |

| С   | 0.40        | 0.60  |  |  |  |

| c2  | 0.40        | 0.60  |  |  |  |

| D   | 5.90        | 6.30  |  |  |  |

| E   | 6.40        | 6.80  |  |  |  |

| E2  | 5.04 REF    |       |  |  |  |

| е   | 1.27        | BSC   |  |  |  |

| Н   | 9.60        | 10.20 |  |  |  |

| L   | 1.39        | 1.78  |  |  |  |

| L1  | 2.50        | 2.90  |  |  |  |

| L2  | 0.51 BSC    |       |  |  |  |

| L3  | 0.90        | 1.30  |  |  |  |

| Z   | 2.74 REF    |       |  |  |  |

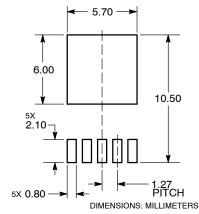

# **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

L2

GUAGE PLANE

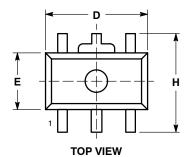

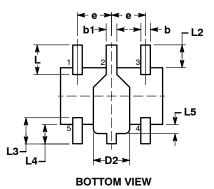

# PACKAGE DIMENSIONS

# SOT-89, 5 LEAD CASE 528AB-01 ISSUE O

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME

- Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS.

- LEAD THICKNESS INCLUDES LEAD FINISH.

DIMENSIONS D AND E DO NOT INCLUDE MOLD

- FLASH, PROTRUSIONS, OR GATE BURRS. DIMENSIONS L, L2, L3, L4, L5, AND H ARE MEAS-URED AT DATUM PLANE C.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 1.40        | 1.60 |  |  |  |

| b   | 0.32        | 0.52 |  |  |  |

| b1  | 0.37        | 0.57 |  |  |  |

| С   | 0.30        | 0.50 |  |  |  |

| D   | 4.40        | 4.60 |  |  |  |

| D2  | 1.40        | 1.80 |  |  |  |

| E   | 2.40        | 2.60 |  |  |  |

| е   | 1.40        | 1.60 |  |  |  |

| Н   | 4.25        | 4.45 |  |  |  |

| L   | 1.10        | 1.50 |  |  |  |

| L2  | 0.80        | 1.20 |  |  |  |

| L3  | 0.95        | 1.35 |  |  |  |

| L4  | 0.65        | 1.05 |  |  |  |

| L5  | 0.20        | 0.60 |  |  |  |

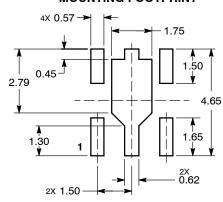

#### **RECOMMENDED** MOUNTING FOOTPRINT\*

**DIMENSIONS: MILLIMETERS**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 📖 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative