# Current Mode PWM Controller for Forward and Flyback Applications

The NCP1252 controller offers everything needed to build cost-effective and reliable ac-dc switching supplies dedicated to ATX power supplies. Thanks to the use of an internally fixed timer, NCP1252 detects an output overload without relying on the auxiliary Vcc. A Brown-Out input offers protection against low input voltages and improves the converter safety. Finally a SOIC8 package saves PCB space and represents a solution of choice in cost sensitive project.

#### **Features**

- Peak Current Mode Control

- Adjustable Switching Frequency up to 500 kHz

- Jittering Frequency ±5% of the Switching Frequency

- Latched Primary Over Current Protection with 10 ms Fixed Delay

- Delayed Operation Upon Start-up via an Internal Fixed Timer

- Adjustable Soft-start Timer

- Auto-recovery Brown-Out Detection

- UC384X-like UVLO Thresholds

- Vcc Range from 9 V to 28 V with Auto-recovery UVLO

- Internal 160 ns Leading Edge Blanking

- Adjustable Internal Ramp Compensation

- +500 mA / -800 mA Source / Sink Capability

- Maximum 50% Duty Cycle: A Version

- Maximum 80% Duty Cycle: B Version

- Ready for Updated No Load Regulation Specifications

- SOIC-8 Package

- This is a Pb-Free Device

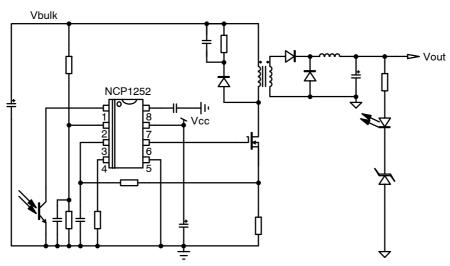

# **Typical Applications**

- Power Supplies for PC Silver Boxes, Games Adapter...

- Flyback and Forward Converter

# ON Semiconductor®

http://onsemi.com

#### **OFFLINE CONTROLLER**

SOIC-8 CASE 751 SUFFIX D

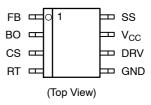

#### **PIN CONNECTIONS**

#### **MARKING DIAGRAM**

1252 = Specific Device Code

X = A or B VersionA = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

1

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

www.datasheet4u.com

**Table 1. PIN FUNCTIONS**

| Pin No. | Pin Name        | Function        | Pin Description                                                                                                    |  |  |

|---------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | FB              | Feedback        | This pin directly connects to an optocoupler collector.                                                            |  |  |

| 2       | ВО              | Brown-out input | This pin monitors the input voltage image to offer a Brown-out protection.                                         |  |  |

| 3       | CS              | Current sense   | Monitors the primary current and allows the selection of the ramp compensation amplitude.                          |  |  |

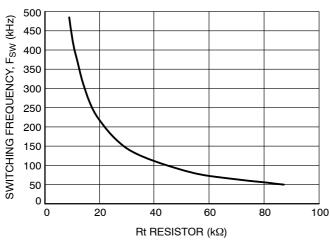

| 4       | R <sub>T</sub>  | Timing element  | A resistor connected to ground fixes the switching frequency.                                                      |  |  |

| 5       | GND             | -               | The controller ground pin.                                                                                         |  |  |

| 6       | Drv             | Driver          | This pin connects to the MOSFET gate                                                                               |  |  |

| 7       | V <sub>CC</sub> | V <sub>CC</sub> | This pin accepts voltage range from 8 V up to 28 V                                                                 |  |  |

| 8       | SSTART          | Soft-start      | A capacitor connected to ground selects the soft-start duration. The soft start is grounded during the delay timer |  |  |

Table 2. MAXIMUM RATINGS TABLE (Notes 1 and 2)

| Symbol              | Rating                                                                                | Value       | Unit |

|---------------------|---------------------------------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>     | Power Supply voltage, Vcc pin, transient voltage: 10 ms with I <sub>Vcc</sub> < 20 mA | 30          | V    |

| V <sub>CC</sub>     | Power Supply voltage, Vcc pin, continuous voltage                                     | 28          | V    |

| I <sub>Vcc</sub>    | Maximum current injected into pin 7                                                   | 20          | mA   |

|                     | Maximum voltage on low power pins (except pin 6, 7)                                   | -0.3 to 10  | V    |

| $R_{\theta J-A-SO}$ | Thermal Resistance Junction-to-Air - SO8                                              | 180         | °C/W |

| TJ <sub>MAX</sub>   | Maximum Junction Temperature                                                          | 150         | °C   |

|                     | Storage Temperature Range                                                             | -60 to +150 | °C   |

|                     | ESD Capability, HBM model                                                             | 1.8         | kV   |

|                     | ESD Capability, Machine Model                                                         | 200         | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Table 3. ORDERING INFORMATION**

| Device       | Version   | Marking | Shipping <sup>†</sup> |  |  |

|--------------|-----------|---------|-----------------------|--|--|

| NCP1252ADR2G | A version | 1252A   | 2500/Tape & Reel      |  |  |

| NCP1252BDR2G | B version | 1252B   | 2500/Tape & Reel      |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

<sup>1.</sup> This device series contains ESD protection and exceeds the following tests: Human Body Model 1800 V per JEDEC Standard JESD22-A114E. Machine Model Method 200 V per JEDEC Standard JESD22-A115A.

<sup>2.</sup> This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

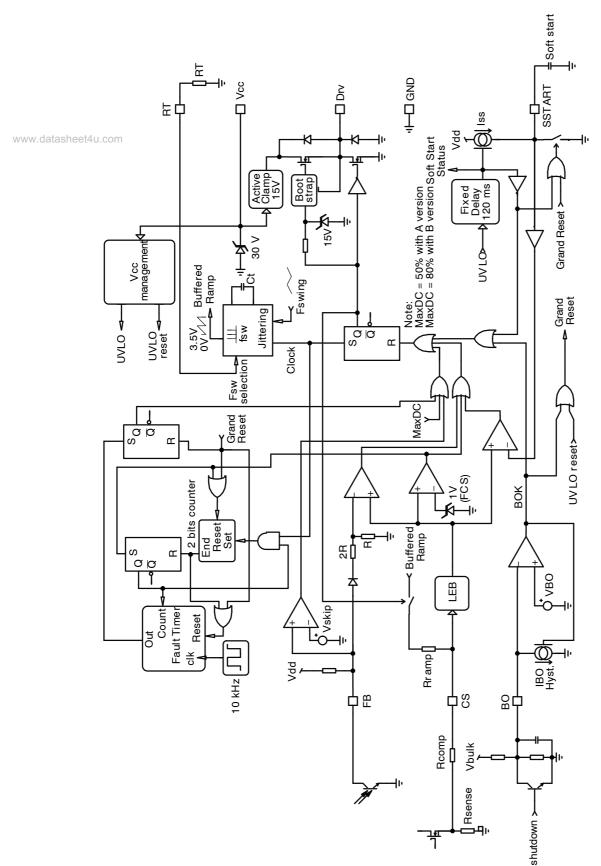

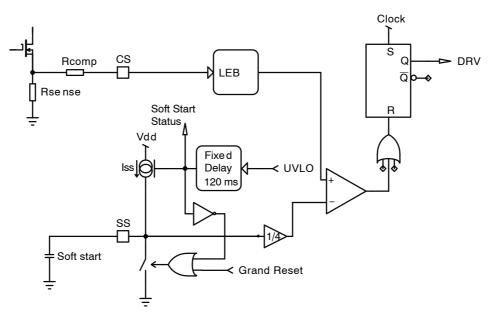

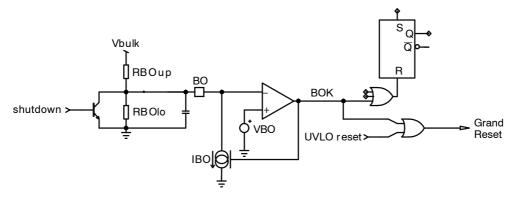

Figure 1. Internal Circuit Architecture

**Table 4. ELECTRICAL CHARATERISTICS**

$(V_{CC} = 15 \text{ V}, R_T = 43 \text{ k}\Omega, C_{DRV} = 1 \text{ nF. For typical values } T_J = 25^{\circ}C, \text{ for min/max values } T_J = -25^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted)}$

| L  | Characteristics                                                 | Test Condition                                                               | Symbol               | Min  | Тур  | Max  | ι |  |

|----|-----------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|------|------|------|---|--|

| -; | SUPPLY SECTION AND $V_{CC}$ MANAGEMEN                           | т                                                                            |                      |      |      |      |   |  |

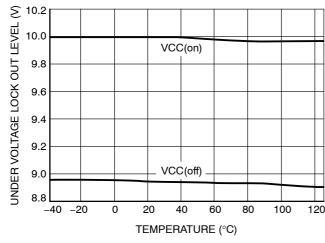

|    | Startup threshold at which driving pulses are authorized        | V <sub>CC</sub> increasing                                                   | V <sub>CC(on)</sub>  | 9.4  | 10   | 10.6 |   |  |

|    | Minimum Operating voltage at which driving pulses are stopped   | V <sub>CC</sub> decreasing                                                   | V <sub>CC(off)</sub> | 8.4  | 9    | 9.6  |   |  |

| Ī  | Hysteresis between V <sub>CC(on)</sub> and V <sub>CC(min)</sub> |                                                                              | V <sub>CC(HYS)</sub> | 0.9  | 1.0  | _    |   |  |

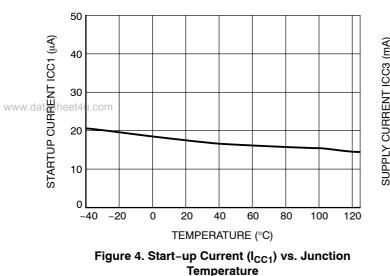

| -  | Start-up current, controller disabled                           | V <sub>CC</sub> < V <sub>CC(on)</sub> & V <sub>CC</sub> increasing from zero | I <sub>CC1</sub>     | _    | -    | 100  |   |  |

| Ī  | Internal IC consumption, controller switching                   | F <sub>sw</sub> =100 kHz, DRV = open                                         | I <sub>CC2</sub>     | 0.5  | 1.4  | 2.2  | 1 |  |

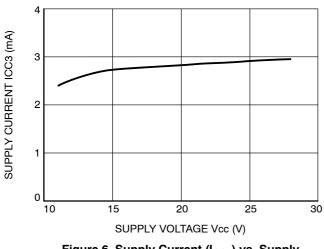

|    | Internal IC consumption, controller switching                   | F <sub>sw</sub> =100 kHz, C <sub>DRV</sub> = 1 nF                            | I <sub>CC3</sub>     | 2.0  | 2.7  | 3.5  | ı |  |

| _  | CURRENT COMPARATOR                                              |                                                                              |                      |      |      |      |   |  |

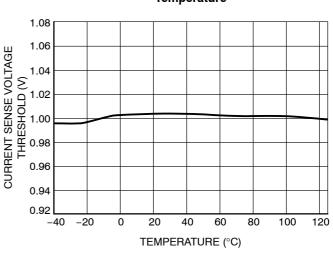

| -  | Current Sense Voltage Threshold                                 |                                                                              | $V_{ILIM}$           | 0.92 | 1    | 1.08 |   |  |

| Ī  | Leading Edge Blanking Duration                                  |                                                                              | t <sub>LEB</sub>     | -    | 160  | _    |   |  |

| Ī  | Input Bias Current                                              | (Note 3)                                                                     | I <sub>bias</sub>    | -    | 0.02 | -    |   |  |

| Ī  | Propagation delay                                               | From CS detected to gate turned off                                          | t <sub>ILIM</sub>    | _    | 70   | 150  |   |  |

| Ī  | Internal Ramp Compensation Voltage level                        | @ 25°C (Note 4)                                                              | $V_{ramp}$           | 3.15 | 3.5  | 3.85 |   |  |

|    | Internal Ramp Compensation resistance to CS pin                 | @ 25°C (Note 4)                                                              | R <sub>ramp</sub>    | =    | 26.5 | -    |   |  |

|    | INTERNAL OSCILLATOR                                             |                                                                              |                      |      |      |      |   |  |

| ſ  | Oscillator Frequency                                            | $R_T$ = 43 kΩ & DRV pin = 47 kΩ                                              | fosc                 | 92   | 100  | 108  | ŀ |  |

| (  | Oscillator Frequency                                            | $R_T$ = 8.5 kΩ & DRV pin = 47 kΩ                                             | fosc                 | 425  | 500  | 550  | ŀ |  |

| Ī  | Frequency Modulation in percentage of f <sub>OSC</sub>          | (Note 3)                                                                     | f <sub>jitter</sub>  | -    | ±5   | -    |   |  |

| Ī  | Frequency modulation Period                                     | (Note 3)                                                                     | T <sub>swing</sub>   | -    | 3.33 | _    |   |  |

| Ī  | Maximum operating frequency                                     | (Note 3)                                                                     | f <sub>MAX</sub>     | 500  | -    | -    | ı |  |

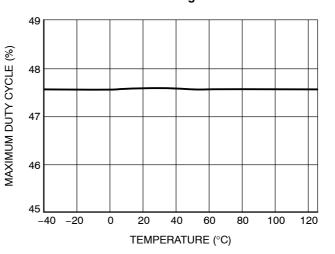

| Ī  | Maximum duty-cycle – A version                                  |                                                                              | DC <sub>maxA</sub>   | 45.6 | 48   | 49.6 |   |  |

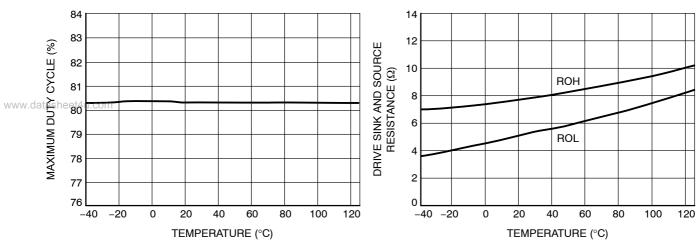

| Ī  | Maximum duty-cycle – B version                                  |                                                                              | DC <sub>maxB</sub>   | 76   | 80   | 84   |   |  |

| _  | FEEDBACK SECTION                                                |                                                                              |                      |      |      |      |   |  |

|    | Internal voltage division from FB to CS set-<br>point           |                                                                              | FB <sub>div</sub>    | -    | 3    | _    |   |  |

| Ī  | Internal pull-up resistor                                       |                                                                              | R <sub>pull-up</sub> | -    | 3.5  | -    |   |  |

| Ī  | FB pin maximum current                                          | FB pin = GND                                                                 | I <sub>FB</sub>      | 1.5  | -    | -    |   |  |

|    | Internal feedback impedance from FB to<br>GND                   |                                                                              | Z <sub>FB</sub>      | _    | 40   | _    |   |  |

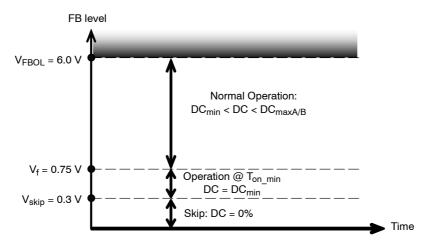

| (  | Open loop feedback voltage                                      | FB pin = open                                                                | $V_{FBOL}$           | -    | 6.0  | -    |   |  |

| Ī  | Internal Diode forward voltage                                  | (Note 3)                                                                     | V <sub>f</sub>       | _    | 0.75 | _    |   |  |

| _  | DRIVE OUTPUT                                                    |                                                                              |                      |      |      |      |   |  |

| Γ  | DRV Source resistance                                           |                                                                              | R <sub>SRC</sub>     | -    | 10   | 30   |   |  |

| ħ  | DRV Sink resistance                                             |                                                                              | R <sub>SINK</sub>    | -    | 6    | 19   |   |  |

| -  | Output voltage rise-time                                        | V <sub>CC</sub> = 15 V, C <sub>DRV</sub> = 1nF,<br>10 to 90%                 | t <sub>r</sub>       | _    | 26   | -    |   |  |

| ᆫ  |                                                                 |                                                                              |                      |      | 1    | 1    |   |  |

Guaranteed by design

V<sub>ramp</sub>, R<sub>ramp</sub> Guaranteed by design

**Table 4. ELECTRICAL CHARATERISTICS**

$(V_{CC} = 15 \text{ V}, R_T = 43 \text{ k}\Omega, C_{DRV} = 1 \text{ nF. For typical values T}_J = 25^{\circ}\text{C}, \text{ for min/max values T}_J = -25^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted})$

|      | Characteristics                                                                   | Test Condition                                                                                                               | Symbol                   | Min        | Тур                                           | Max          | Unit |  |  |  |

|------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------|-----------------------------------------------|--------------|------|--|--|--|

| _    | DRIVE OUTPUT                                                                      |                                                                                                                              |                          |            |                                               |              |      |  |  |  |

|      | Output voltage fall-time                                                          | V <sub>CC</sub> = 15 V, C <sub>DRV</sub> = 1nF,<br>90 to 10%                                                                 | t <sub>f</sub>           | -          | 22                                            | -            | ns   |  |  |  |

| date | Clamping voltage (maximum gate voltage)                                           | $V_{CC}$ = 25 V $R_{DRV}$ = 47 k $\Omega$ , $C_{DRV}$ = 1 nF                                                                 | V <sub>CL</sub>          | -          | 15                                            | 18           | V    |  |  |  |

|      | High-state voltage drop                                                           | $\begin{split} V_{CC} &= V_{CC(min)} + 100 \text{ mV}, \\ R_{DRV} &= 47 \text{ k}\Omega, C_{DRV} = 1 \text{ nF} \end{split}$ | V <sub>DRV(clamp)</sub>  | -          | 50                                            | 500          | mV   |  |  |  |

|      | CYCLE SKIP                                                                        |                                                                                                                              |                          |            |                                               |              |      |  |  |  |

| ſ    | Skip cycle level                                                                  |                                                                                                                              | $V_{skip}$               | 0.2        | 0.3                                           | 0.4          | V    |  |  |  |

|      | Skip threshold Reset                                                              |                                                                                                                              | V <sub>skip(reset)</sub> | -          | V <sub>skip</sub> +<br>V <sub>skip(HYS)</sub> | -            | V    |  |  |  |

| Ī    | Skip threshold Hysteresis                                                         |                                                                                                                              | V <sub>skip(HYS)</sub>   | _          | 25                                            | -            | mV   |  |  |  |

| _    | SOFT START                                                                        |                                                                                                                              |                          |            |                                               |              |      |  |  |  |

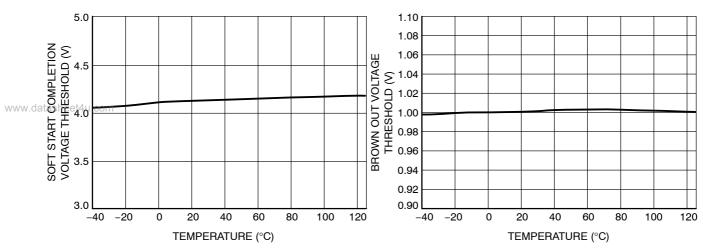

| ſ    | Soft-start charge current                                                         | SS pin = GND                                                                                                                 | I <sub>SS</sub>          | 8.8        | 10                                            | 11           | μΑ   |  |  |  |

| ſ    | Soft start completion voltage threshold                                           |                                                                                                                              | V <sub>SS</sub>          | 3.5        | 4.0                                           | 4.5          | V    |  |  |  |

| -    | Internal delay before starting the Soft start when V <sub>CC(on)</sub> is reached |                                                                                                                              | SS <sub>delay</sub>      | 100        | 120                                           | 155          | ms   |  |  |  |

| -    | PROTECTION                                                                        |                                                                                                                              |                          |            |                                               |              |      |  |  |  |

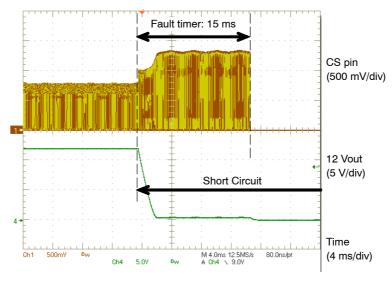

|      | Current sense fault voltage level triggering the timer                            |                                                                                                                              | F <sub>CS</sub>          | 0.9        | 1                                             | 1.1          | V    |  |  |  |

|      | Timer delay before latching a fault (overload or short circuit)                   | When CS pin > F <sub>CS</sub>                                                                                                | T <sub>fault</sub>       | 10         | 15                                            | 20           | ms   |  |  |  |

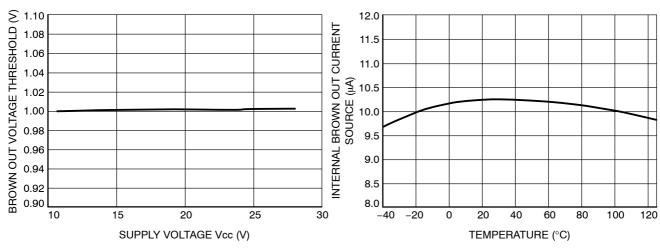

|      | Brown-out voltage                                                                 |                                                                                                                              | V <sub>BO</sub>          | 0.974      | 1                                             | 1.026        | V    |  |  |  |

|      | Internal current source generating the Brown-out hysteresis                       | –5°C ≤ T <sub>J</sub> ≤ +125°C<br>–25°C ≤ T <sub>J</sub> ≤ +125°C                                                            | I <sub>BO</sub>          | 8.8<br>8.6 | 10<br>10                                      | 11.2<br>11.2 | μΑ   |  |  |  |

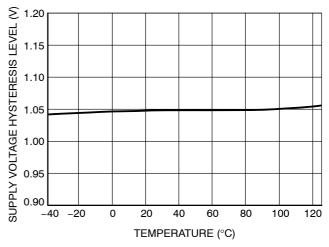

Figure 2. Supply Voltage Threshold vs. **Junction Temperature**

Figure 3. Supply Voltage Hysteresis vs. **Junction Temperature**

Guaranteed by design

V<sub>ramp</sub>, R<sub>ramp</sub> Guaranteed by design

SUPPLY CURRENT ICC3 (mA) 2 -40 -20 0 40 60 80 100 120 TEMPERATURE (°C)

Figure 5. Supply Current (I<sub>CC3</sub>) vs. Junction Temperature

Figure 6. Supply Current (I<sub>CC3</sub>) vs. Supply Voltage

Figure 7. Current Sense Voltage Threshold vs. **Junction Temperature**

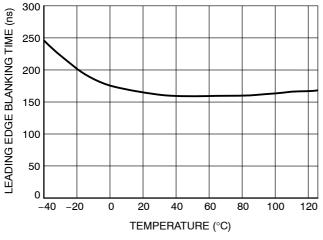

Figure 8. Leading Edge Blanking Time vs. **Junction Temperature**

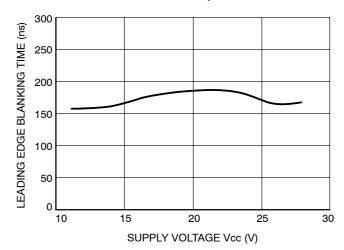

Figure 9. Leading Edge Blanking Time vs. **Supply Voltage**

160 140 PROPAGATION DELAY (ns) 120 100 80 60 40 20 0 25 10 15 20 30 SUPPLY VOLTAGE Vcc (V)

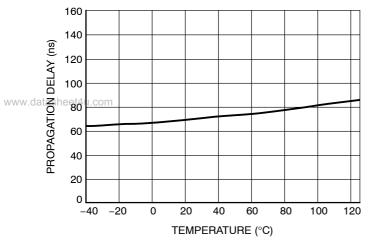

Figure 10. Propagation Delay from CS to DRV vs. Junction Temperature

Figure 11. Propagation Delay from CS to DRV vs. Supply Voltage

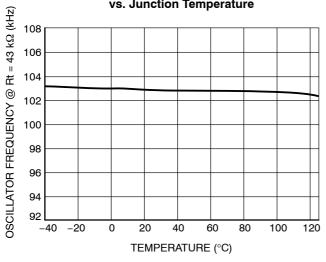

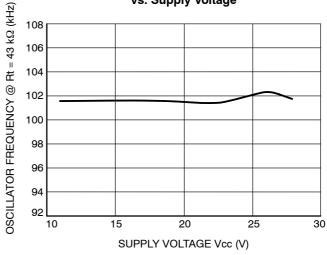

Figure 12. Oscillator Frequency vs. Junction Temperature

Figure 13. Oscillator Frequency vs. Supply Voltage

Figure 14. Oscillator Frequency vs. Oscillator

Resistor

Figure 15. Maximum Duty-cycle, A Version vs.

Junction Temperature

Figure 16. Maximum Duty-cycle, B Version vs.

Junction Temperature

Figure 17. Drive Sink and Source Resistances vs. Junction Temperature

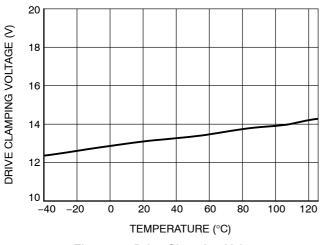

Figure 18. Drive Clamping Voltage vs. Junction Temperature

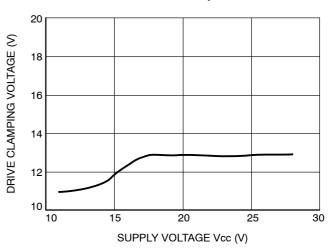

Figure 19. Drive Clamping Voltage vs. Supply Voltage

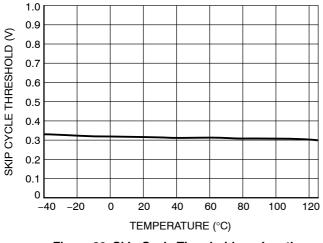

Figure 20. Skip Cycle Threshold vs. Junction Temperature

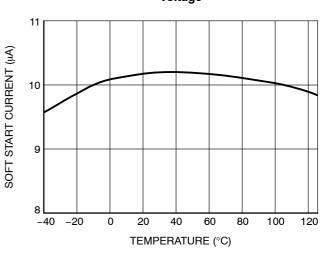

Figure 21. Soft Start Current vs. Junction Temperature

Figure 22. Soft Start Completion Voltage Threshold vs. Junction Temperature

Figure 23. Brown Out Voltage Threshold vs. Junction Temperature

Figure 24. Brown Out Voltage Threshold vs. Supply Voltage

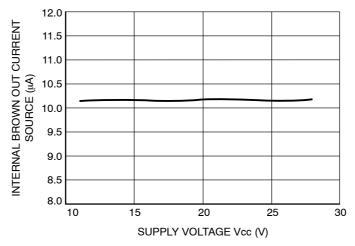

Figure 25. Internal Brown Out Current Source vs. Junction Temperature

Figure 26. Internal Brown Out Current Source vs. BO Pin Voltage

## **Application Information**

#### Introduction

The NCP1252 hosts a high-performance current-mode controller specifically developed to drive power supplies designed for the ATX and the adapter market:

- Current Mode operation: implementing peak current—mode control topology, the circuit offers UC384X—like features to build rugged power supplies.

- Adjustable switching frequency: a resistor to ground precisely sets the switching frequency between 50 kHz and a maximum of 500 kHz. There is no synchronization capability.

- Internal frequency jittering: Frequency jittering softens the EMI signature by spreading out peak energy within a band ±5% from the center frequency.

- Wide Vcc excursion: the controller allows operation up to 28 V continuously and accepts transient voltage up to 30 V during 10 ms with I<sub>VCC</sub> < 20 mA</li>

- **Gate drive clamping:** a lot of powers MOSFETs do not allow their driving voltage to exceed 20 V. The controller includes a low–loss clamping voltage which prevents the gate from going beyond 15 V typical.

- Low startup-current: reaching a low no-load standby power represents a difficult exercise when the controller requires an external, lossy, resistor connected to the bulk capacitor. The start-up current is guaranteed to be less than 100 μA maximum, helping the designer to reach a low standby power level.

- Short-circuit protection: by monitoring the CS pin voltage when it exceeds 1 V (maximum peak current), the controller detects a fault and starts an internal digital timer. On the condition that the digital timer elapses, the controller will permanently latch-off. This allows accurate overload or short-circuit detection which is not dependant on the auxiliary winding. Reset occurs when: a) a BO reset is sensed, b) V<sub>CC</sub> is cycled down to V<sub>CC(min)</sub> level. If the short circuit or the fault disappear before the fault timer ends, the fault timer is reset only if the CS pin voltage level is below 1 V at least during 3 switching frequency periods. This delay before resetting the fault timer prevents any false or missing fault or over load detection.

- Adjustable soft-start: the soft-start is activated upon a start-up sequence (V<sub>CC</sub> going-up and crossing

- $V_{\rm CC(on)}$ ) after a minimum internal time delay of 120 ms (SS<sub>delay</sub>). But also when the brown–out pin is reset without in that case timer delay. This internal time delay gives extra time to the PFC to be sure that the output PFC voltage is in regulation. The soft start pin is grounded until the internal delay is ended.

- **Shutdown:** if an external transistor brings the BO pin down, the controller is shut down, but all internal biasing circuits are alive. When the pin is released, a new soft–start sequence takes place.

- Brown-Out protection: BO pin permanently monitors a fraction of the input voltage. When this image is below the V<sub>BO</sub> threshold, the circuit stays off and does not switch. As soon the voltage image comes back within safe limits, the pulses are re-started via a start-up sequence including soft-start. The hysteresis is implemented via a current source connected to the BO pin; this current source sinks a current (I<sub>BO</sub>) from the pin to the ground. As the current source status depends on the brown-out comparator, it can easily be used for hysteresis purposes. A transistor pulling down the BO pin to ground will shut-off the controller. Upon release, a new soft-start sequence takes place.

- Internal ramp compensation: a simple resistor connected from the CS pin to the sense resistor allows the designer to inject ramp compensation inside his design.

- Skip cycle feature: When the power supply loads are decreasing to a low level, the duty cycle also decreases to the minimum value the controller can offer. If the output loads disappear, the converter runs at the minimum duty cycle fixed by the propagation delay and driving blocks. It often delivers too much energy to the secondary side and it trips the voltage supervisor. To avoid this problem, the FB is allowed to impose the min ton down to ~ V<sub>f</sub> and it further decreases down to V<sub>skip</sub>, zero duty cycle is imposed. This mode helps to ensure no-load outputs conditions as requested by recently updated ATX specifications. Please note that the converter first goes to min ton before going to zero duty cycle: normal operation is thus not disturbed. The following figure illustrates the different mode of operation versus the FB pin level.

Figure 27. Mode of Operation versus the FB Pin Level

# **Startup Sequence:**

www.datasheet4u.com

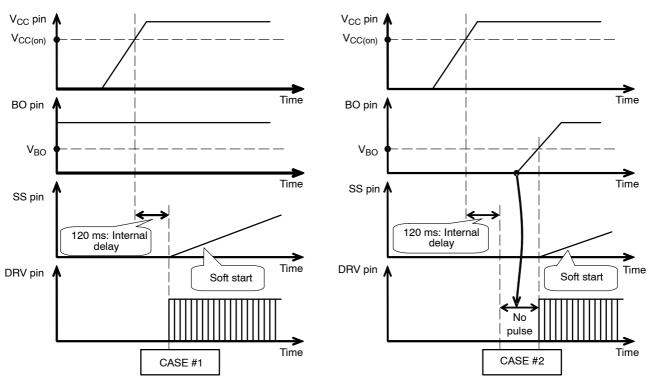

The startup sequence is activated when Vcc pin reaches  $V_{CC(on)}$  level. Once the startup sequence has been activated the internal delay timer ( $SS_{delay}$ ) runs. Only when the internal delay elapses the soft start can be allowed if the BO pin level is above  $V_{BO}$  level. If the BO pin threshold is reached or as soon as this level will be reached the soft start

is allowed. When the soft start is allowed the SS pin is released from the ground and the current source connected to this pin sources its current to the external capacitor connected on SS pin. The voltage variation of the SS pin divided by 4 gives the same peak current variation on the CS pin.

The following figures illustrate the different startup cases.

Figure 28. Different Startup Sequence Case #1 & #2

With the Case #1, when the  $V_{CC}$  pin reaches the  $V_{CC(on)}$  level, the internal timer starts. As the BO pin level is above the  $V_{BO}$  threshold at the end of the internal delay, a soft start sequence is started.

With the Case #2, at the end of the internal delay, the BO pin level is below the  $V_{BO}$  threshold thus the soft start sequence can not start. A new soft start sequence will start only when the BO pin reaches the  $V_{BO}$  threshold.

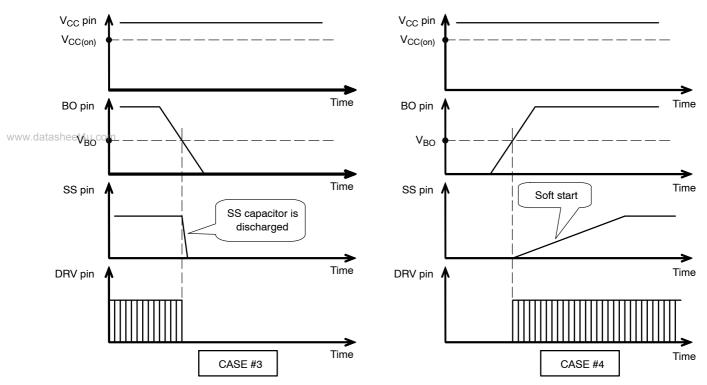

Figure 29. Controller Shuts Down with the Brown Out Pin

When the BO pin is grounded, the controller is shut down and the SS pin is internally grounded in order to discharge the soft start capacitor connected to this pin (Case #3). If the BO pin is released, when its level reaches the  $V_{BO}$  level a new soft start sequence happens.

#### **Soft Start:**

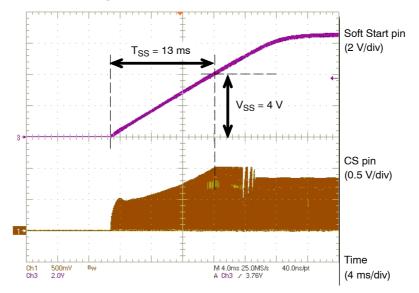

As illustrated by the following figure, the rising voltage on the SS pin voltage divided by 4 controls the peak current sensed on the CS pin. Thus as soon as the CS pin voltage becomes higher than the SS pin voltage divided by 4 the driver latch is reset.

Figure 30. Soft Start Principle

The following figure illustrates a soft start sequence.

Figure 31. Soft Start Example

#### **Brown-Out Protection**

www.datasheet4u.com

By monitoring the level on BO pin, the controller protects the forward converter against low input voltage conditions. When the BO pin level falls below the  $V_{BO}$  level, the controllers stops pulsing until the input level goes back to normal and resumes the operation via a new soft start sequence.

The brown-out comparator features a fixed voltage reference level ( $V_{BO}$ ). The hysteresis is implemented by using the internal current connected between the BO pin and the ground when the BO pin is below the internal voltage reference ( $V_{BO}$ ).

Figure 32. BO Pin Setup

The following equations show how to calculate the resistors for BO pin.

First of all, select the bulk voltage value at which the controller must start switching  $(V_{bulkon})$  and the bulk voltage for shutdown  $(V_{bulkoff})$  the controller.

## Where:

- $V_{bulkon} = 370 \text{ V}$

- $V_{bulkoff} = 350 \text{ V}$

- $V_{BO} = 1 V$

- $I_{BO} = 10 \, \mu A$

When BO pin voltage is below  $V_{BO}$  (internal voltage reference), the internal current source ( $I_{BO}$ ) is activated. The following equation can be written:

$$V_{\text{bulkON}} = R_{\text{BOup}} \left( I_{\text{BO}} + \frac{V_{\text{BO}}}{R_{\text{BOlo}}} \right) + V_{\text{BO}}$$

(eq. 1)

When BO pin voltage is higher than  $V_{BO}$ , the internal current source is now disabled. The following equation can be written:

$$V_{BO} = \frac{V_{bulkoff}R_{BOlo}}{R_{BOlo} + R_{BOup}}$$

(eq. 2)

From Equation 2 it can be extracted the R<sub>BOup</sub>:

$$R_{BOup} = \left(\frac{V_{bulkoff} - V_{BO}}{V_{BO}}\right) R_{BOlo}$$

(eq. 3)

Equation 3 is substituted in Equation 1 and solved for  $R_{\mbox{BOlo}}$ , yields:

$$R_{BOlo} = \frac{V_{BO}}{I_{BO}} \left( \frac{V_{bulkon} - V_{BO}}{V_{bulkoff} - V_{BO}} - 1 \right)$$

(eq. 4)

$R_{BOup}$  can be also written independently of  $R_{BOlo}$  by substituting Equation 4 into Equation 3 as follow:

$$R_{BOup} = \frac{V_{bulkon} - V_{bulkoff}}{I_{BO}}$$

(eq. 5)

www.datasFrom Equation 4 and Equation 5, the resistor divider value can be calculated:

$$R_{BOlo} = \frac{1}{10 \,\mu} \left( \frac{370 - 1}{350 - 1} - 1 \right) = 5731 \,\Omega$$

$$R_{BOup} = \frac{370 - 350}{10 \,\mu} = 2.0 \,M\Omega$$

#### Short Circuit or Over Load Protection:

A short circuit or an overload situation is detected when the CS pin level reaching its maximum level at 1 V. In that case the fault status is stored in the latch and allows the digital timer count. If the digital timer ends then the fault is latched and the controller permanently stops the pulses on the driver pin.

If the fault is gone before ending the digital timer, the timer is reset only after 3 switching controller periods without fault detection (or when the CS pin < 1 V during at least 3 switching periods).

If the fault is latched the controller can be reset if a BO reset is sensed or if  $V_{CC}$  is cycled down to  $V_{CC(off)}$ .

Figure 33. Short Circuit Detection Example

#### **Shut Down**

There is one possibility to shut down the controller; this possibility consists at grounding the BO pin as illustrated in Figure 32.

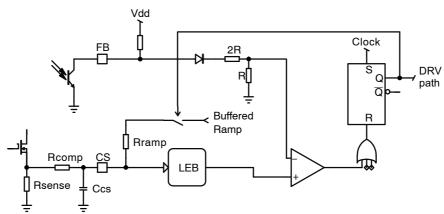

## **Ramp Compensation**

Ramp compensation is a known mean to cure subharmonic oscillations. These oscillations take place at half of the switching frequency and occur only during Continuous Conduction Mode (CCM) with a duty-cycle close to and above 50%. To lower the current loop gain, one usually injects between 50 and 100% of the inductor downslope, depicts how internally the ramp is generated:

The ramp compensation applied on CS pin is from the internal oscillator ramp buffered. A switch placed between the buffered internal oscillator ramp and R<sub>ramp</sub> disconnects the ramp compensation during the OFF time DRV signal.

www.datasheet4u.com

Figure 34. Ramp Compensation Setup

In the NCP1252, the internal ramp swings with a slope of:

$$\boldsymbol{S}_{int} = \frac{\boldsymbol{V}_{ramp}}{D\boldsymbol{C}_{max}}\boldsymbol{F}_{SW} \tag{eq. 6}$$

In a forward application the secondary-side downslope viewed on a primary side requires a projection over the sense resistor  $R_{\text{sense}}$ . Thus:

$$S_{sense} = \frac{(V_{out} + V_f)}{L_{out}} \frac{N_s}{N_p} R_{sense}$$

(eq. 7)

where:

- Vout is output voltage level

- V<sub>f</sub> the freewheel diode forward drop

- Lout, the secondary inductor value

- N<sub>s</sub>/N<sub>p</sub> the transformer turn ratio

- R<sub>sense</sub>: the sense resistor on the primary side

Assuming the selected amount of ramp compensation to be applied is  $\delta_{comp}$ , then we must calculate the division ratio to scale down  $S_{int}$  accordingly:

$$Ratio = \frac{R_{sense}\delta_{comp}}{S_{int}}$$

(eq. 8)

A few line of algebra determined Rcomp:

$$R_{comp} = R_{ramp} \frac{Ratio}{1 - Ratio}$$

(eq. 9)

The previous ramp compensation calculation does not take into account the natural primary ramp created by the transformer magnetizing inductance. In some case illustrated here after the power supply does not need additional ramp compensation due to the high level of the natural primary ramp.

The natural primary ramp is extracted from the following formula:

$$S_{natural} = \frac{V_{bulk}}{L_{mag}} R_{sense}$$

(eq. 10)

Then the natural ramp compensation will be:

$$\delta_{\text{natural\_comp}} = \frac{S_{\text{natural}}}{S_{\text{sense}}}$$

(eq. 11

If the natural ramp compensation ( $\delta_{natural\_comp}$ ) is higher than the ramp compensation needed ( $\delta_{comp}$ ), the power supply does not need additional ramp compensation. If not, only the difference ( $\delta_{comp}$ – $\delta_{natural\_comp}$ ) should be used to calculate the accurate compensation value.

Thus the new division ratio is:

$$\text{if} \quad \delta_{\text{natural\_comp}} < \delta_{\text{comp}} \Rightarrow \text{Ratio} = \frac{S_{\text{sense}}(\delta_{\text{comp}} - \delta_{\text{natural\_comp}})}{S_{\text{int}}} \tag{eq. 12}$$

Then  $R_{comp}$  can be calculated with the same equation used when the natural ramp is neglected (Equation 9).

## Ramp Compensation Design Example:

2 switch–Forward Power supply specification:

- Regulated output: 12 V

- $L_{out} = 27 \mu H$

- $V_f = 0.7 \text{ V}$  (drop voltage on the regulated output)

- Current sense resistor :  $0.75 \Omega$

- Switching frequency: 125 kHz

- V<sub>bulk</sub> = 350 V, minimum input voltage at which the power supply works.

- Duty cycle max:  $DC_{max} = 84\%$

- $V_{ramp} = 3.5 \text{ V}$ , Internal ramp level.

- $R_{ramp} = 26.5 \text{ k}\Omega$ , Internal pull-up resistance

- Targeted ramp compensation level: 100%

- Transformer specification:

- $-L_{\text{mag}} = 13 \text{ mH}$

- $-N_{\rm s}/N_{\rm p} = 0.085$

Internal ramp compensation level

$$S_{int} = \frac{V_{ramp}}{DC_{max}}F_{sw} \Rightarrow S_{int} = \frac{3.5}{0.84}$$

125 kHz = 520 mV /  $\mu s$

Secondary-side downslope projected over the sense resistor is:

www.datas Natural primary ramp:

$$S_{natural} = \frac{V_{bulk}}{L_{mag}} R_{sense} \Rightarrow S_{natural} = \frac{350}{13 \cdot 10^{-3}} \ 0.75 = 20.19 \ mV \ / \ \mu s$$

Thus the natural ramp compensation is:

$$\delta_{\text{natural\_comp}} = \frac{S_{\text{natural}}}{S_{\text{sense}}} \Rightarrow \delta_{\text{natural\_comp}} = \frac{20.19}{29.99} = 67.3\%$$

Here the natural ramp compensation is lower than the desired ramp compensation, so an external compensation should be added to prevent sub-harmonics oscillation.

$$Ratio = \frac{S_{sense}(\delta_{comp} - \delta_{natural\_comp})}{S_{int}} \Rightarrow Ratio = \frac{29.99 \cdot (1.00 - 0.67)}{520} = 0.019$$

We can know calculate external resistor  $(R_{comp})$  to reach the correct compensation level.

$$R_{comp} = R_{ramp} \frac{Ratio}{1 - Ratio} \Rightarrow R_{comp} = 26.5 \cdot 10^3 \frac{0.019}{1 - 0.019} = 509 \Omega$$

Thus with  $R_{comp} = 510 \Omega$ , 100% compensation ramp is applied on the CS pin.

The following example illustrates a power supply where the natural ramp offers enough ramp compensation to avoid external ramp compensation.

2 switch-Forward Power supply specification:

- Regulated output: 12 V

- $L_{out} = 27 \mu H$

- $V_f = 0.7 \text{ V}$  (drop voltage on the regulated output)

- Current sense resistor:  $0.75 \Omega$

- Switching frequency: 125 kHz

- V<sub>bulk</sub> = 350 V, minimum input voltage at which the power supply works.

- Duty cycle max: DC<sub>max</sub> = 84%

- $V_{ramp} = 3.5 \text{ V}$ , Internal ramp level.

- $R_{ramp} = 26.5 \text{ k}\Omega$ , Internal pull-up resistance

- Targeted ramp compensation level: 100%

- Transformer specification:

$$-L_{mag} = 7 \text{ mH}$$

$-N_s/N_p = 0.085$

Secondary-side downslope projected over the sense resistor is:

$$S_{sense} = \frac{(V_{out} + V_{f})}{L_{out}} \frac{N_{s}}{N_{p}} R_{sense} \Rightarrow S_{sense} = \frac{(12 + 0.7)}{27 \cdot 10^{-6}} 0.085 \times 0.75 = 29.99 \text{ mV} / \mu s$$

The natural primary ramp is:

$$S_{natural} = \frac{V_{bulk}}{L_{mag}} R_{sense} \Rightarrow S_{natural} = \frac{350}{7 \cdot 10^{-3}} 0.75 = 37.5 \text{ mV} / \mu s$$

And the natural ramp compensation will be:

$$\delta_{\text{natural\_comp}} = \frac{S_{\text{natural}}}{S_{\text{sense}}} \Rightarrow \delta_{\text{natural\_comp}} = \frac{37.5}{29.99} = 125\%$$

So in that case the natural ramp compensation due to the magnetizing inductance of the transformer will be enough to prevent any sub-harmonics oscillation in case of duty cycle above 50%.

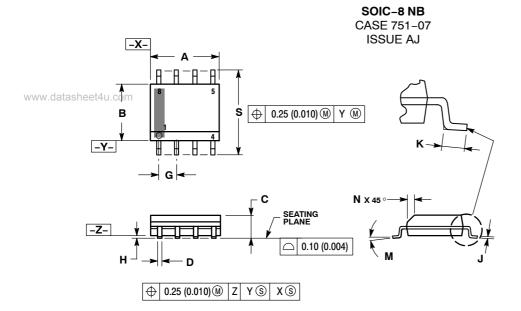

#### PACKAGE DIMENSIONS

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION

- 751-01 THRU 751-06 ARE OBSOLETE. NEW

|     | MILLIN | IETERS | INCHES    |       |  |  |

|-----|--------|--------|-----------|-------|--|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |  |

| С   | 1.35   | 1.75   | 0.053     | 0.069 |  |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |  |

| M   | 0 °    | 8 °    | 0 °       | 8 °   |  |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |  |

| S   | 5.80   | 6.20   | 0.228     | 0.244 |  |  |

# **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 👊 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and war engineer trademarks of semiconductor components industries, Ite (SciLLC) solitate services are injective to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative