# **INTEGRATED CIRCUITS**

# DATA SHEET

# TDA9874A Digital TV sound demodulator/decoder

Preliminary specification File under Integrated Circuits, IC02 1999 Dec 03

**TDA9874A**

### **CONTENTS**

| 1            | FEATURES                                                                  |

|--------------|---------------------------------------------------------------------------|

| 2            | GENERAL DESCRIPTION                                                       |

| 2.1          | Supported standards                                                       |

| 3            | ORDERING INFORMATION                                                      |

| 4            | BLOCK DIAGRAM                                                             |

| 5            | PINNING                                                                   |

| 6            | FUNCTIONAL DESCRIPTION                                                    |

| 6.1          | Description of the demodulator and decoder section                        |

| 6.2          | Description of the DSP                                                    |

| 6.3          | Description of the analog audio section                                   |

| 7            | LIMITING VALUES                                                           |

| 8            | THERMAL CHARACTERISTICS                                                   |

| 9            | CHARACTERISTICS                                                           |

| 10           | I <sup>2</sup> C-BUS CONTROL                                              |

| 10.1         | Introduction                                                              |

| 10.2         | Power-up state                                                            |

| 10.3<br>10.4 | Slave receiver mode Slave transmitter mode                                |

| 10.4         | I <sup>2</sup> S-BUS DESCRIPTION                                          |

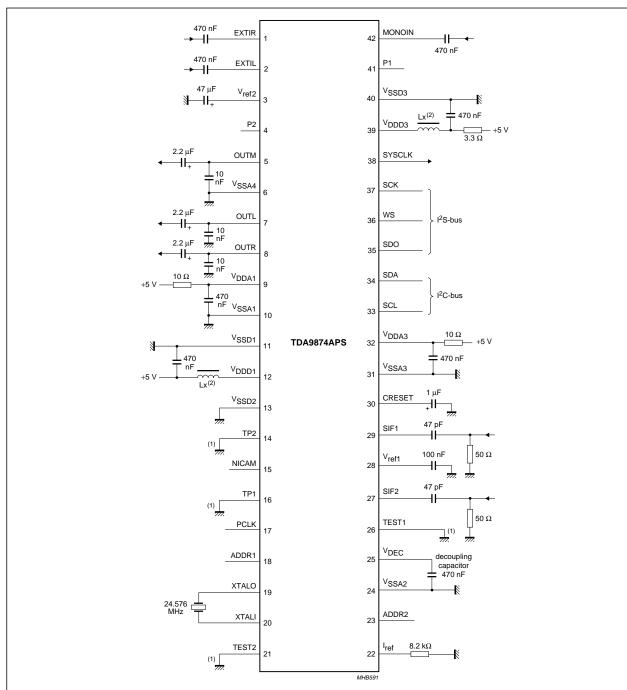

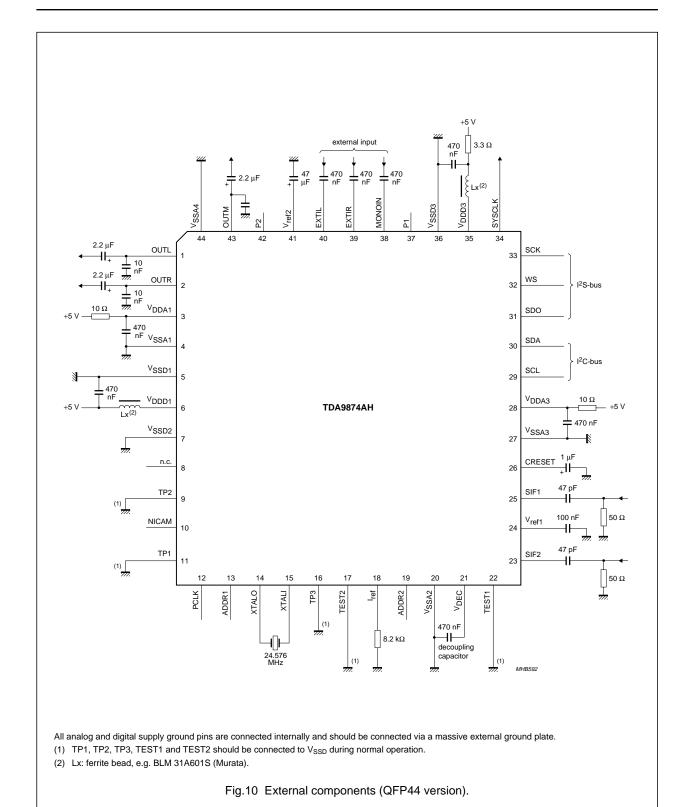

| 12           | EXTERNAL COMPONENTS                                                       |

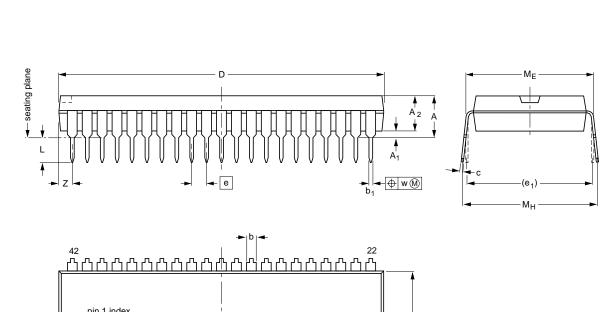

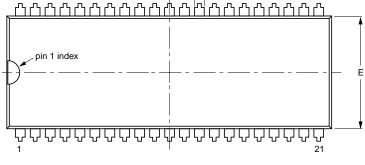

|              | PACKAGE OUTLINES                                                          |

| 13           |                                                                           |

| 14           | SOLDERING                                                                 |

| 14.1<br>14.2 | Introduction Through-hole mount packages                                  |

| 14.2         | Surface mount packages                                                    |

| 14.4         | Suitability of IC packages for wave, reflow and dipping soldering methods |

| 15           | DEFINITIONS                                                               |

| 16           | LIFE SUPPORT APPLICATIONS                                                 |

| 17           | PURCHASE OF PHILIPS I2C COMPONENTS                                        |

TDA9874A

### 1 FEATURES

- · Sound IF (SIF) input switch

- SIF AGC with 24 dB control range

- Switchable 10 dB SIF input attenuator

- SIF 8-bit Analog-to-Digital Converter (ADC)

- · Easy TV standard programming option

- Differential Quadrature Phase Shift Keying (DQPSK) demodulation for different standards, simultaneously with 1-channel FM demodulation

- NICAM decoding (B/G, D/K, I and L standard)

- 2-carrier multi-standard FM demodulation (B/G, D/K and M standard)

- Single carrier high deviation FM mono demodulation mode

- Decoding for three analog multi-channel systems (A2) and satellite sound

- · Adaptive de-emphasis for satellite

- Programmable identification (B/G, D/K and M standard) and different identification times

- · FM pilot carrier presence detector

- Optional AM demodulation for system L, simultaneously with NICAM

- Monitor selection for FM/AM demodulator outputs and FM and NICAM signals with peak option

- · Automatic FM dematrixing option

- · Digital crossbar switch

- I<sup>2</sup>S-bus serial audio output with matrix, level adjustment and mute

- Dual audio Digital-to-Analog Converter (DAC) from digital crossbar switch to analog crossbar switch, bandwidth = 15 kHz

- Automatic Volume Level (AVL) control

- · Analog crossbar switch with inputs for mono and stereo

- Output selection of mono, stereo, dual, dual A or dual B

- · Additional mono output with automatic select

- · 20 kHz bandwidth for analog path

- Standby mode

- · Automatic output selection for TV applications.

### 2 GENERAL DESCRIPTION

The TDA9874A is a single-chip Digital TV Sound Demodulator/Decoder (DTVSD) for analog and digital multi-channel sound systems in TV/VCR sets and satellite receivers.

### 2.1 Supported standards

The multi-standard/multi-stereo capability of the TDA9874A is of interest in Europe, Hong Kong/PR China and South East Asia. This includes B/G, D/K, I, M and L standard. In other application areas subsets of the standard combinations are available or, only single standards are transmitted.

All A2 (analog 2-carrier) and NICAM systems are supported. M standard (with mono or BTSC stereo sound) can be received and processed in mono sound mode.

The AM sound of L/L' standard is normally demodulated in the 1st sound IF. The resulting AF signal has to be entered into the mono audio input of the TDA9874A. A second possibility is to use the internal AM demodulator stage (with 6.5 MHz intercarrier), which gives limited performance.

Korea has a stereo sound system similar to Europe and is supported by the TDA9874A. The differences include deviation, modulation contents and identification. It is based on M standard.

For all FM standards a high deviation mode for a single carrier monaural sound demodulation is selectable.

An overview of the supported standards and sound systems and their key parameters is given in Tables 1 to 3.

The analog multi-channel systems are sometimes also called 2CS (2-carrier systems).

**TDA9874A**

### 2.1.1 ANALOG 2-CARRIER SYSTEMS

Table 1 Frequency modulation

|          | SOUND  | SOUND CARRIER      |      | FM DEVIATION (kHz) |       |                      | ATION      | BANDWIDTH/              |  |

|----------|--------|--------------------|------|--------------------|-------|----------------------|------------|-------------------------|--|

| STANDARD | SYSTEM | FREQUENCY<br>(MHz) | NOM. | MAX.               | OVER. | SC1                  | SC2        | DE-EMPHASIS<br>(kHz/μs) |  |

| M        | mono   | 4.5                | 15   | 25                 | 50    | mono                 | _          | 15/75                   |  |

| M        | A2     | 4.5/4.724          | 15   | 25                 | 50    | $\frac{1}{2}(L + R)$ | ¹⁄₂(L − R) | 15/75 (Korea)           |  |

| B/G      | A2     | 5.5/5.742          | 27   | 50                 | 80    | $\frac{1}{2}(L + R)$ | R          | 15/50                   |  |

| 1        | mono   | 6.0                | 27   | 50                 | 80    | mono                 | _          | 15/50                   |  |

| D/K (2)  | A2     | 6.5/6.742          | 27   | 50                 | 80    | $\frac{1}{2}(L + R)$ | R          | 15/50                   |  |

| D/K (1)  | A2     | 6.5/6.258          | 27   | 50                 | 80    | ½(L + R)             | R          | 15/50                   |  |

| D/K (3)  | A2     | 6.5/5.742          | 27   | 50                 | 80    | ½(L + R)             | R          | 15/50                   |  |

Table 2 Identification for A2 systems

| PARAMETER                       | A2; A2*                                                  | A2+ (KOREA)                                              |

|---------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| Pilot frequency                 | $54.6875 \text{ kHz} = 3.5 \times \text{line frequency}$ | $55.0699 \text{ kHz} = 3.5 \times \text{line frequency}$ |

| Stereo identification frequency | $117.5 \text{ Hz} = \frac{\text{line frequency}}{133}$   | $149.9 \text{ Hz} = \frac{\text{line frequency}}{105}$   |

| Dual identification frequency   | 274.1 Hz = line frequency 57                             | $276.0 \text{ Hz} = \frac{\text{line frequency}}{57}$    |

| AM modulation depth             | 50%                                                      | 50%                                                      |

### 2.1.2 2-CARRIER SYSTEMS WITH NICAM

Table 3 NICAM

|          | SC1                |            |      |       |              |              |                |          |                  |                 |

|----------|--------------------|------------|------|-------|--------------|--------------|----------------|----------|------------------|-----------------|

|          |                    | MODULATION |      |       |              | SC2          | DE-            | 2011     | NIO 4 54         |                 |

| STANDARD | FREQUENCY<br>(MHz) | TYPE       | INDE | X (%) | DEVIA<br>(kl | ATION<br>Hz) | (MHz)<br>NICAM | EMPHASIS | ROLL-<br>OFF (%) | NICAM<br>CODING |

|          |                    |            | NOM. | MAX.  | NOM.         | MAX.         |                |          |                  |                 |

| B/G      | 5.5                | FM         | _    | _     | 27           | 50           | 5.85           | J17      | 40               | note 1          |

| I        | 6.0                | FM         | _    | _     | 27           | 50           | 6.552          | J17      | 100              | note 1          |

| D/K      | 6.5                | FM         | ı    | ı     | 27           | 50           | 5.85           | J17      | 40               | note 2          |

| L        | 6.5                | AM         | 54   | 100   | _            | _            | 5.85           | J17      | 40               | note 1          |

### Notes

- 1. See "EBU NICAM 728 specification" or equivalent specification.

- 2. Not yet officially defined.

# Digital TV sound demodulator/decoder

**TDA9874A**

### 2.1.3 SATELLITE SYSTEMS

An important specification for satellite TV reception is the Astra specification. The TDA9874A is suitable for the reception of Astra and other satellite signals, with sound carrier frequencies from 4 to 9.2 MHz.

Table 4 FM satellite sound

| CARRIER TYPE | CARRIER<br>FREQUENCY<br>(MHz) | MODULATION<br>INDEX | MAXIMUM<br>FM DEVIATION<br>(kHz) | MODULATION            | BANDWIDTH/<br>DE-EMPHASIS<br>(kHz/μs) |

|--------------|-------------------------------|---------------------|----------------------------------|-----------------------|---------------------------------------|

| Main         | 6.50 <sup>(1)</sup>           | 0.26                | 85 <sup>(2)</sup>                | mono                  | 15/50 <sup>(1)</sup>                  |

| Sub          | 7.02/7.20                     | 0.15                | 50                               | m/st/d <sup>(3)</sup> | 15/adaptive <sup>(4)</sup>            |

|              | 7.38/7.56                     |                     |                                  |                       |                                       |

|              | 7.74/7.92                     |                     |                                  |                       |                                       |

|              | 8.10/8.28                     |                     |                                  |                       |                                       |

### **Notes**

- 1. For other satellite systems, frequencies of e.g. 5.80, 6.60 or 6.65 MHz can also be received. A de-emphasis of  $60 \mu s$ , or in accordance with J17, is available.

- 2. Main channels with high deviation can also be handled.

- 3. m/st/d = mono or stereo or dual language sound.

- 4. Adaptive de-emphasis is compatible to transmitter specification.

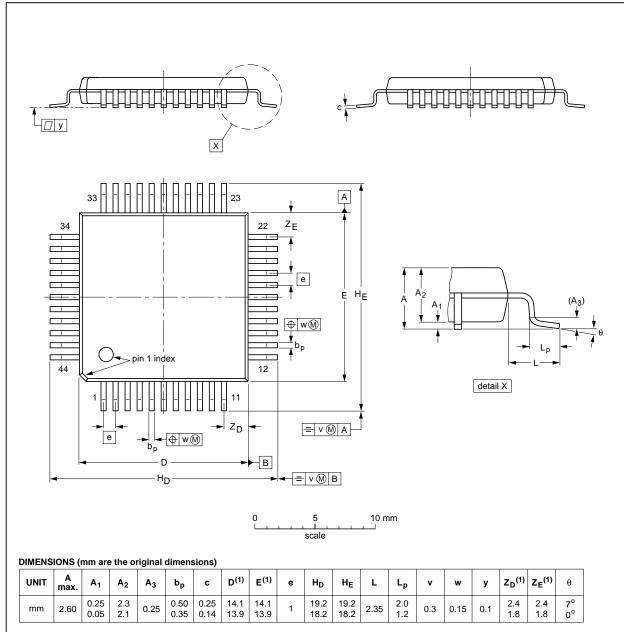

### 3 ORDERING INFORMATION

| TYPE NUMBER | PACKAGE |                                                                                              |          |  |  |

|-------------|---------|----------------------------------------------------------------------------------------------|----------|--|--|

| TIPE NOMBER | NAME    | DESCRIPTION                                                                                  | VERSION  |  |  |

| TDA9874APS  | SDIP42  | plastic shrink dual in-line package; 42 leads (600 mil)                                      | SOT270-1 |  |  |

| TDA9874AH   | QFP44   | plastic quad flat package; 44 leads (lead length 2.35 mm); body $14 \times 14 \times 2.2$ mm | SOT205-1 |  |  |

**TDA9874A**

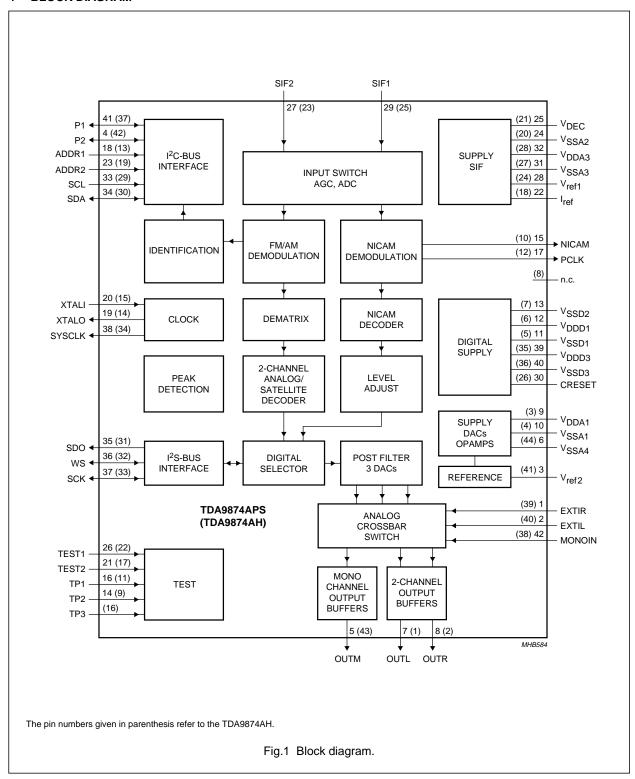

### 4 BLOCK DIAGRAM

TDA9874A

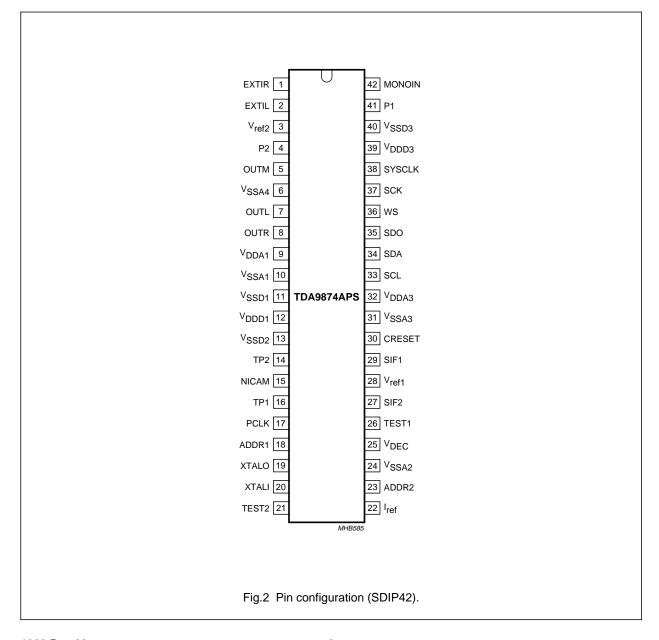

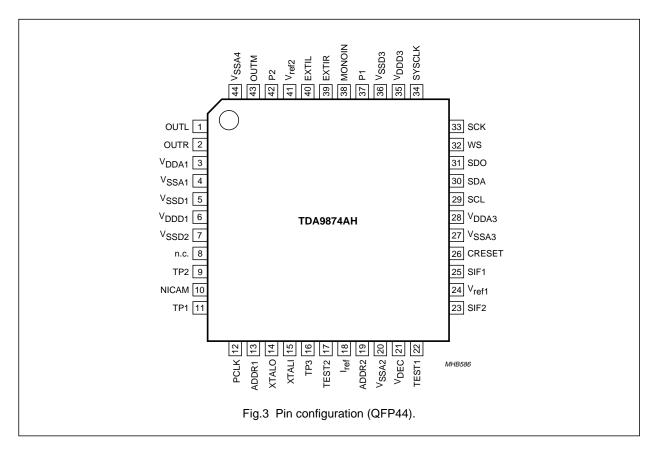

### 5 PINNING

| 0.41501           | Р      | IN    |                                                                           |

|-------------------|--------|-------|---------------------------------------------------------------------------|

| SYMBOL            | SDIP42 | QFP44 | DESCRIPTION                                                               |

| EXTIR             | 1      | 39    | external audio input right channel                                        |

| EXTIL             | 2      | 40    | external audio input left channel                                         |

| V <sub>ref2</sub> | 3      | 41    | analog reference voltage for DAC and operational amplifiers               |

| P2                | 4      | 42    | second general purpose I/O pin                                            |

| OUTM              | 5      | 43    | analog output right                                                       |

| V <sub>SSA4</sub> | 6      | 44    | analog ground supply 4 for analog back-end circuitry                      |

| OUTL              | 7      | 1     | analog output left                                                        |

| OUTR              | 8      | 2     | analog output right                                                       |

| $V_{DDA1}$        | 9      | 3     | analog supply voltage 1; back-end circuitry 5 V                           |

| V <sub>SSA1</sub> | 10     | 4     | analog ground supply 1; back-end circuitry                                |

| V <sub>SSD1</sub> | 11     | 5     | digital ground supply 1; core circuitry                                   |

| $V_{DDD1}$        | 12     | 6     | digital supply voltage 1; core voltage regulator circuitry                |

| V <sub>SSD2</sub> | 13     | 7     | digital ground supply 2; core circuitry                                   |

| n.c.              | _      | 8     | not connected                                                             |

| TP2               | 14     | 9     | additional test pin 2; connected to V <sub>SSD</sub> for normal operation |

| NICAM             | 15     | 10    | serial NICAM data output (at 728 kHz)                                     |

| TP1               | 16     | 11    | additional test pin 1; connected to V <sub>SSD</sub> for normal operation |

| PCLK              | 17     | 12    | NICAM clock output (at 728 kHz)                                           |

| ADDR1             | 18     | 13    | first I <sup>2</sup> C-bus slave address modifier input                   |

| XTALO             | 19     | 14    | crystal oscillator output                                                 |

| XTALI             | 20     | 15    | crystal oscillator input                                                  |

| TP3               | -      | 16    | additional test pin 3; connected to V <sub>SSD</sub> for normal operation |

| TEST2             | 21     | 17    | test pin 2; connected to V <sub>SSD</sub> for normal operation            |

| I <sub>ref</sub>  | 22     | 18    | resistor for reference current generation; front-end circuitry            |

| ADDR2             | 23     | 19    | second I <sup>2</sup> C-bus slave address modifier input                  |

| V <sub>SSA2</sub> | 24     | 20    | analog ground supply 2; analog front-end circuitry                        |

| $V_{DEC}$         | 25     | 21    | analog front-end circuitry supply voltage decoupling                      |

| TEST1             | 26     | 22    | test pin 1; connected to V <sub>SSD</sub> for normal operation            |

| SIF2              | 27     | 23    | sound IF input 2                                                          |

| V <sub>ref1</sub> | 28     | 24    | reference voltage; for analog front-end circuitry                         |

| SIF1              | 29     | 25    | sound IF input 1                                                          |

| CRESET            | 30     | 26    | capacitor for Power-on reset                                              |

| V <sub>SSA3</sub> | 31     | 27    | digital ground supply 3; front-end circuitry                              |

| $V_{DDA3}$        | 32     | 28    | analog front-end circuitry regulator supply voltage 3 (5 V)               |

| SCL               | 33     | 29    | I <sup>2</sup> C-bus serial clock input                                   |

| SDA               | 34     | 30    | I <sup>2</sup> C-bus serial data input/output                             |

| SDO               | 35     | 31    | I <sup>2</sup> S-bus serial data output                                   |

| WS                | 36     | 32    | I <sup>2</sup> S-bus word select input/output                             |

### **TDA9874A**

| SYMBOL            | PIN    |       | DESCRIPTION                                |

|-------------------|--------|-------|--------------------------------------------|

|                   | SDIP42 | QFP44 | - DESCRIPTION                              |

| SCK               | 37     | 33    | I <sup>2</sup> S-bus clock input/output    |

| SYSCLK            | 38     | 34    | system clock output                        |

| $V_{DDD3}$        | 39     | 35    | digital supply voltage 3; digital I/O pads |

| V <sub>SSD3</sub> | 40     | 36    | digital ground supply 3; digital I/O pads  |

| P1                | 41     | 37    | first general purpose I/O pin              |

| MONOIN            | 42     | 38    | analog mono input                          |

**TDA9874A**

### **6 FUNCTIONAL DESCRIPTION**

# 6.1 Description of the demodulator and decoder section

### 6.1.1 SIF INPUT

Two input pins are provided, SIF1 and SIF2. For higher SIF signal levels the SIF input can be attenuated with an internal switchable –10 dB resistor divider. As no specific filters are integrated, both inputs have the same specification giving flexibility in application. The selected signal is passed through an AGC circuit and then digitized by an 8-bit ADC operating at 24.576 MHz.

### 6.1.2 AGC

The gain of the AGC amplifier is controlled from the ADC output by means of a digital control loop employing hysteresis. The AGC has a fast attack behaviour to prevent ADC overloads, and a slow decay behaviour to prevent AGC oscillations. For AM demodulation the AGC must be switched off. When switched off, the control loop is reset and fixed gain settings can be chosen; see Table 16.

The AGC can be controlled via the I<sup>2</sup>C-bus; details are given in Sections 10.3.2, 10.3.3 and 10.4.6.

### 6.1.3 MIXER

The digitized input signal is fed to the mixers, which mix one or both input sound carriers down to zero IF. A 24-bit control word for each carrier sets the required frequency. Access to the mixer control word registers is via the I<sup>2</sup>C-bus (see Sections 10.3.5 and 10.3.6) or via Easy Standard Programming (ESP, see Section 10.3.23). When receiving NICAM programs, a feedback signal is added to the control word of the second carrier mixer to establish a carrier-frequency loop.

### 6.1.4 FM AND AM DEMODULATION

An FM or AM input signal is fed through a switchable band-limiting filter into a demodulator that can be used for either FM or AM demodulation. Apart from the standard (fixed) de-emphasis characteristic, an adaptive de-emphasis is available for Wegener-Panda 1 encoded satellite programs.

TDA9874A

### 6.1.5 FM DECODING

A 2-carrier stereo decoder recovers the left and right signal channels from the demodulated sound carriers. Both the European and Korean stereo systems are supported.

Automatic FM dematrixing is also supported, which means that the FM sound mode identification (mono, stereo or dual) switches the FM dematrix directly. No loop via the microcontroller is needed.

For highly overmodulated signals, a high deviation mode for monaural audio sound single carrier demodulation can be selected.

NICAM decoding is still possible in high deviation mode.

### 6.1.6 FM IDENTIFICATION

The identification of the FM sound mode is performed by AM synchronous demodulation of the pilot and narrow-band detection of the identification frequencies. The result is available via the I<sup>2</sup>C-bus interface. A selection can be made via the I<sup>2</sup>C-bus for B/G, D/K and M standards, and for three different time constants that represent different trade-offs between speed and reliability of identification. A pilot detector allows the control software to identify an analog 2-carrier (A2) transmission within approximately 0.1 s.

Automatic FM dematrixing, depending on the identification, is possible.

### 6.1.7 NICAM DEMODULATION

The NICAM signal is transmitted in a DQPSK code at a bit rate of 728 kbits/s. The NICAM demodulator performs DQPSK demodulation and passes the resulting bitstream and clock signal to the NICAM decoder and, for evaluation purposes, to various pins.

A timing loop controls the frequency of the crystal oscillator to lock the sampling instants to the symbol timing of the NICAM data.

### 6.1.8 NICAM DECODING

The device performs all decoding functions in accordance with the "EBU NICAM 728 specification". After locking to the frame alignment word, the data is descrambled by applying the defined pseudo-random binary sequence. The device then synchronizes to the periodic frame flag bit C0.

The status of the NICAM decoder can be read out from the NICAM status register by the user (see Section 10.4.2). The OSB bit indicates that the decoder has locked to the NICAM data. The VDSP bit indicates that the decoder has locked to the NICAM data and that the data is valid sound data. The C4 bit indicates that the sound conveyed by the FM mono channel is identical to the sound conveyed by the NICAM channel.

The error byte contains the number of sound sample errors (resulting from parity checking) that occurred in the past 128 ms period. The Bit Error Rate (BER) is approximately 0.0000174 times the contents of the error byte:

BER =

$$\frac{\text{bit errors}}{\text{total bits}} \approx \text{error byte} \times 1.74 \times 10^{-5}$$

### 6.1.9 NICAM AUTO-MUTE

This function is enabled by setting bit AMUTE LOW (see Section 10.3.12). Upper and lower error limits may be defined by writing appropriate values to two registers in the I<sup>2</sup>C-bus section (see Sections 10.3.14 and 10.3.15). When the number of errors in a 128 ms period exceeds the upper error limit, the auto-mute function will switch the output sound from NICAM to whatever sound is on the first sound carrier (FM or AM) or to the analog mono input. When the error count is smaller than the lower error limit, the NICAM sound is restored.

The auto-mute function can be disabled by setting bit AMUTE HIGH. In this case clicks become audible when the error count increases. The user will hear a signal of degrading quality.

If no NICAM sound is received, the outputs are switched from the NICAM channel to the 1st sound carrier.

A decision to enable or disable the auto-mute is taken by the microprocessor based on an interpretation of the application control bits C1, C2, C3 and C4, and possibly any additional strategy implemented by the user in the microcontroller software.

When the AM sound in NICAM L systems is demodulated in the 1st sound IF and the audio signal connected to the mono input of the TDA9874A, the controlling microprocessor has to ensure switching from NICAM reception to mono input, if auto-muting is desired. This can be achieved by setting the AMSEL bit HIGH and the AMUTE bit LOW (see Section 10.3.12).

1999 Dec 03

TDA9874A

### 6.1.10 CRYSTAL OSCILLATOR

The digital controlled crystal oscillator (DCXO) is fully integrated. Only an external 24.576 MHz crystal is required.

### 6.1.11 TEST PINS

All test pins are active HIGH. In normal operation of the device they can be left open-circuit, as they have internal pull-down resistors. Test functions are for manufacturing tests only and are not available to customers.

### 6.1.12 POWER FAIL DETECTOR

The power fail detector monitors the internal power supply for the digital part of the device. If the supply has temporarily been lower than the specified lower limit, the power failure register bit PFR in subaddress 0 (see Section 10.4.1), will be set to HIGH. The CLRPFR bit, slave register subaddress 1 (see Section 10.3.3), resets the Power-on reset flip-flop to LOW. If this is detected, an initialization of the TDA9874A has to be performed to ensure reliable operation.

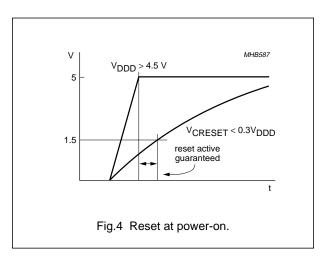

### 6.1.13 POWER-ON RESET

The reset is active LOW. In order to perform a reset at power-up, a simple RC circuit may be used which consists of an integrated passive pull-up resistor and an external capacitor connected to ground. The pull-up resistor has a nominal value of 50 k $\Omega$ , which can easily be measured between pins CRESET and V<sub>DDD3</sub>. Before the supply voltage has reached a certain minimum level, the state of the circuit is completely undefined and remains in this undefined state until a reset is applied.

The reset is guaranteed to be active when:

- The power supply is within the specified limits (4.5 to 5.5 V)

- The crystal oscillator (DCXO) is functioning

- The voltage at pin CRESET is below 0.3V<sub>DDD</sub> (1.5 V if V<sub>DDD</sub> = 5.0 V, typically below 1.8 V).

The required capacitor value depends on the gradient of the rising power supply voltage. The time constant of the RC circuit should be clearly larger than the rise time of the power supply [to make sure that the reset condition is always satisfied (see Fig.4)], even when considering tolerance spreading. To avoid problems with a too slow discharging of the capacitor at power-down, it may be helpful to add a diode from the CRESET pin to V<sub>DDD</sub>.

It should be noted that the internal ESD protection diode does not help here as it only conducts at higher voltages. Under difficult power supply conditions (e.g. very slow or non-monotonic ramp-up), it is recommended to drive the reset line from a microcontroller port or the like.

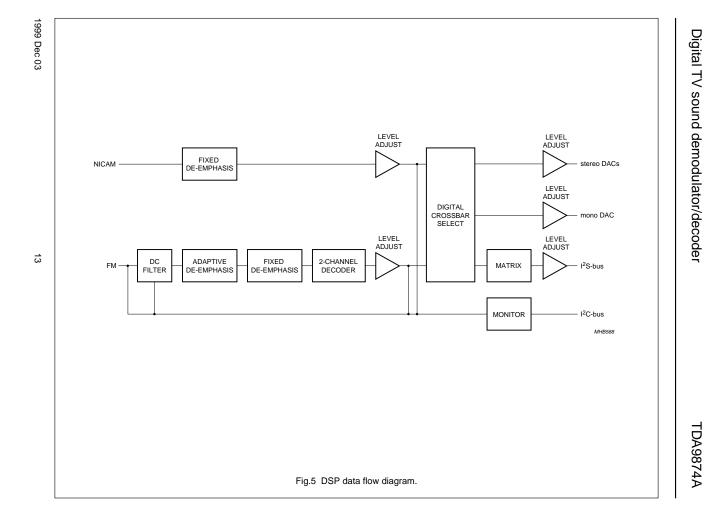

### 6.2 Description of the DSP

### 6.2.1 LEVEL SCALING

All input channels to the digital crossbar switch are equipped with a level adjustment facility to change the signal level in a range of  $\pm 15$  dB. Adjusting the signal level is intended to compensate for the different modulation parameters of the various TV standards. Under nominal conditions it is recommended to scale all input channels to be 15 dB below full-scale [–15 dB (FS)]. This will create sufficient headroom to cope with overmodulation and avoids changes of the volume impression when switching from FM to NICAM or vice versa.

### 6.2.2 NICAM PATH

The NICAM path has a switchable J17 de-emphasis.

### 6.2.3 NICAM AUTO-MUTE

If NICAM is received, the auto-mute is enabled and the signal quality becomes poor. The digital crossbar switches automatically to FM, channel 1 or the analog mono input, as selected by bit AMSEL. This automatic switching depends on the NICAM bit error rate. The auto-mute function can be disabled via the I<sup>2</sup>C-bus.

# Digital TV sound demodulator/decoder

TDA9874A

### 6.2.4 FM (AM) PATH

A high-pass filter suppresses DC offsets from the FM demodulator that may occur due to carrier frequency offsets, and supplies the FM monitor function with DC values, e.g. for the purpose of microprocessor controlled carrier search or fine tuning functions.

An adaptive de-emphasis is available for Wegener-Panda 1 encoded satellite programs.

The de-emphasis stage offers a choice of settings for the supported TV standards.

The 2-channel decoder performs the dematrixing of  $\frac{1}{2}(L+R)$ , R to L and R signals of  $\frac{1}{2}(L+R)$  and  $\frac{1}{2}(L-R)$  to L and R signals or of channel 1 and channel 2 to L and R signals, as demanded by the different TV standards or user preferences.

Automatic FM dematrixing is also supported.

Using the high deviation mode, only channel 1 (mono) can be demodulated. The scaling is –6 dB compared to 2-channel decoding.

### 6.2.5 MONITOR

This function provides data words from the FM demodulator outputs and FM and NICAM signals for external use, such as carrier search or fine tuning. The peak level of these signals can also be observed. Source selection and data read-out are performed via the I<sup>2</sup>C-bus.

### 6.2.6 DIGITAL CROSSBAR SWITCH

The input channels are derived from the FM and NICAM paths, while the output channels comprise I<sup>2</sup>S-bus and the audio DACs to the analog crossbar switch. It should be noted that there is no connection from the external analog audio inputs to the digital crossbar switch.

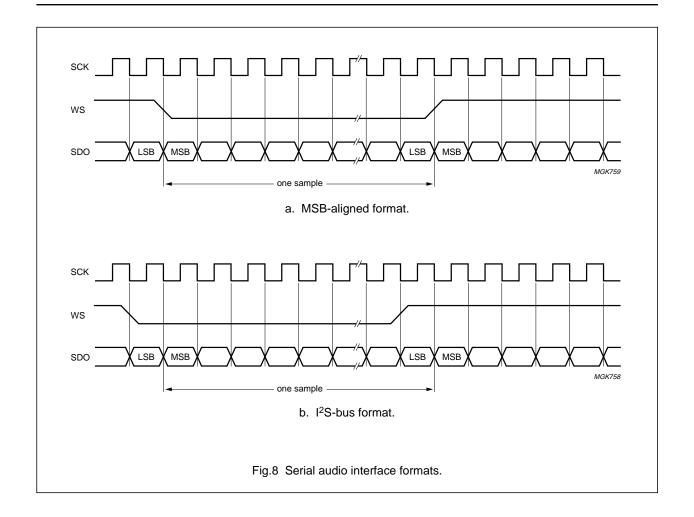

### 6.2.7 DIGITAL AUDIO OUTPUT

The digital audio output interface comprises an  $I^2S$ -bus output port and a system clock output. The  $I^2S$ -bus port is equipped with a level adjustment facility that can change the signal level in a  $\pm 15$  dB range in 1 dB steps. Muting is possible, too, and outputs can be disabled to improve EMC performance.

The I<sup>2</sup>S-bus output matrix provides the functions for forced mono, stereo, channel swap, channel 1 or channel 2.

Automatic selection for TV applications is possible. In this case the microcontroller program only has to provide a user controlled sound A or sound B selection.

### 6.2.8 STEREO CHANNEL TO THE ANALOG CROSSBAR PATH

A level adjustment function is provided with control positions of 0, 3, 6 and 9 dB in combination with the audio DACs. The Automatic Volume Level (AVL) function provides a constant output level of –20 dB (FS) for input levels between 0 and –26 dB (FS). There are some fixed decay time constants to choose from, i.e. 2, 4 or 8 s.

Automatic selection for TV applications is possible. In this case the microcontroller program only has to provide a user controlled sound A or sound B selection.

### 6.2.9 GENERAL

The level adjustment functions can provide signal gain at multiple locations. Great care has to be taken when using gain with large input signals, e.g., due to overmodulation, in order not to exceed the maximum possible signal swing, which would cause severe signal distortion. The nominal signal level of the various signal sources to the digital crossbar switch should be 15 dB below digital full-scale, i.e., –15 dB (FS).

Philips Semiconductors

Preliminary specification

TDA9874A

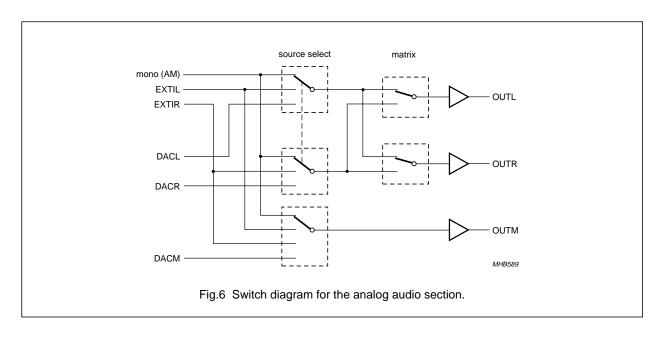

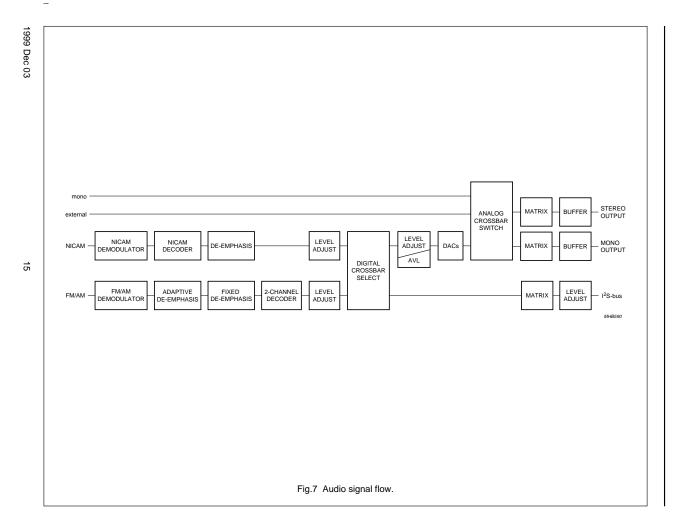

### 6.3 Description of the analog audio section

### 6.3.1 ANALOG CROSSBAR SWITCH AND ANALOG MATRIX

The TDA9874A has one external analog stereo input, one mono input, one 2-channel and one single-channel output port. Analog source selector switches are employed to provide the desired analog signal routing capability, which is done by the analog crossbar switch section.

The basic signal routing philosophy of the TDA9874A is that each switch handles two signal channels at the same time (e.g. left and right, language A and B) directly at the source. For an overview of the signal flow see Fig.7.

Each source selector switch is followed by an analog matrix to perform further selection tasks, such as putting a signal from one input channel, say language A, to both output channels or for swapping left and right channels. The analog matrix provides the functions given in Table 5. Automatic matrixing for TV applications is also supported.

All switches and matrices are controlled via the I<sup>2</sup>C-bus.

**Table 5** Analog matrix functions

| MODE | MATRIX OUTPUT |                                  |  |  |

|------|---------------|----------------------------------|--|--|

| MODE | L OUTPUT      | R OUTPUT R input L input L input |  |  |

| 1    | L input       | R input                          |  |  |

| 2    | R input       | L input                          |  |  |

| 3    | L input       | L input                          |  |  |

| 4    | R input       | R input                          |  |  |

### 6.3.2 EXTERNAL AND MONO INPUTS

The external and mono inputs accept signal levels of up to 1.4 V (RMS). By adding external series resistors to provide suitable attenuation, the external input could be used as a SCART input. Whenever the external or mono input is selected, the output of the DAC is muted to improve the crosstalk performance.

### 6.3.3 AUDIO DACS

The TDA9874A comprises a 2-channel audio DAC and an additional single-channel audio DAC for feeding signals from the DSP section to the analog crossbar switch. These DACs have a resolution of 15 bits and employ four-times oversampling and noise shaping.

### 6.3.4 AUDIO OUTPUT BUFFERS

The output buffers provide a gain of 0 dB and offer a muting possibility. The post filter capacitors of the audio DACs are connected to the buffer outputs.

### 6.3.5 STANDBY MODE

The standby mode (see Section 10.3.3) disables most functions and reduces power dissipation of the TDA9874A. It provides no other function.

Internal registers may lose their information in standby mode. Therefore, the device needs to be initialized on returning to normal operation. This can be accomplished in the same way as after a Power-on reset.

Philips Semiconductors

TDA9874A

TDA9874A

### 7 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                              | PARAMETER                                                              | CONDITIONS                                                                     | MIN. | MAX. | UNIT |

|-------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|

| V <sub>DDx</sub>                    | DC supply voltage                                                      |                                                                                | -0.5 | +6.5 | ٧    |

| $\Delta V_{DDx}$                    | voltage differences between two V <sub>DDx</sub> pins                  |                                                                                | _    | 550  | mV   |

| I <sub>IK</sub>                     | DC input clamp diode current                                           | $V_i < -0.5 \text{ V or } V_i > V_{DD} + 0.5 \text{ V}$                        | _    | ±10  | mA   |

| I <sub>OK</sub>                     | DC output clamp diode current output type 4 mA                         | $V_o < -0.5 \text{ V or} $<br>$V_o > V_{DD} + 0.5 \text{ V}$                   | _    | ±20  | mA   |

| Io                                  | DC output source or sink current output type 4 mA                      | $-0.5 \text{ V} < \text{V}_{\text{O}} < \text{V}_{\text{DDx}} + 0.5 \text{ V}$ | _    | ±20  | mA   |

| I <sub>DDD</sub> , I <sub>SSD</sub> | DC V <sub>DDD</sub> or V <sub>SSD</sub> current per digital supply pin |                                                                                | _    | ±96  | mA   |

| I <sub>DDA</sub> , I <sub>SSA</sub> | DC V <sub>DDA</sub> or V <sub>SSA</sub> current per analog supply pin  |                                                                                | -    | ±50  | mA   |

| I <sub>lu(prot)</sub>               | latch-up protection current                                            |                                                                                | 100  | _    | mA   |

| P/out                               | power dissipation per output                                           |                                                                                | -    | 100  | mW   |

| P <sub>tot</sub>                    | total power dissipation                                                |                                                                                | -    | 0.75 | W    |

| T <sub>stg</sub>                    | storage temperature                                                    |                                                                                | -55  | +125 | °C   |

| T <sub>amb</sub>                    | ambient temperature                                                    |                                                                                | -20  | +70  | °C   |

| V <sub>es</sub>                     | electrostatic handling                                                 | note 1                                                                         | 2000 | _    | V    |

|                                     |                                                                        | note 2                                                                         | 200  | _    | ٧    |

### Notes

- 1. Human body model: C = 100 pF;  $R = 1.5 \text{ k}\Omega$ .

- 2. Machine model: C = 200 pF; L = 0.75  $\mu\text{H};$  R = 0  $\Omega.$

### 8 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 70    | K/W  |

**TDA9874A**

### 9 CHARACTERISTICS

$V_{DD}=5$  V;  $T_{amb}=25$  °C; settings in accordance with B/G standard; FM deviation  $\pm 50$  kHz;  $f_{mod}=1$  kHz; FM sound parameters in accordance with system A2; NICAM in accordance with "EBU NICAM 728 specification"; 1 k $\Omega$  measurement source resistance for AF inputs;  $V_{SIF}=300$  mV (p-p); AGCOFF = 0; AGCSLOW = 1; level and gain settings according to note 1 with external components of Fig.9; unless otherwise specified.

| SYMBOL                     | PARAMETER                                                  | CONDITIONS                                            | MIN. | TYP. | MAX. | UNIT |

|----------------------------|------------------------------------------------------------|-------------------------------------------------------|------|------|------|------|

| Digital supp               | lies                                                       |                                                       | •    |      | •    |      |

| V <sub>DDD1</sub>          | digital supply voltage 1                                   |                                                       | 4.5  | 5.0  | 5.5  | V    |

| V <sub>SSD1</sub>          | digital ground supply 1                                    |                                                       | _    | 0.0  | _    | V    |

| I <sub>DDD1</sub>          | digital supply current 1                                   | V <sub>DDD1</sub> = 5.5 V                             | 40   | 59   | 74   | mA   |

|                            |                                                            | V <sub>DDD1</sub> = 5.0 V                             | 42   | 59   | 75   | mA   |

| V <sub>SSD2</sub>          | digital ground supply 2                                    |                                                       | _    | 0.0  | _    | V    |

| $V_{DDD3}$                 | digital supply voltage 3                                   |                                                       | 4.5  | 5.0  | 5.5  | V    |

| $V_{SSD3}$                 | digital ground supply 3                                    |                                                       | _    | 0.0  | _    | V    |

| I <sub>DDD3</sub>          | digital supply current 3                                   | V <sub>DDD3</sub> = 5.5 V; SYSCLK off                 | 9    | 17   | 21   | mA   |

|                            |                                                            | V <sub>DDD3</sub> = 5.0 V; SYSCLK off                 | 8    | 16   | 20   | mA   |

| Power failur               | e register                                                 |                                                       |      |      |      |      |

| V <sub>pfr</sub>           | power failure response voltage                             |                                                       | _    | 4.0  | _    | V    |

| Demodulato                 | or supplies and references                                 |                                                       | •    | •    | •    |      |

| V <sub>DDA3</sub>          | analog supply voltage 3, demodulator part                  |                                                       | 4.5  | 5.0  | 5.5  | V    |

| V <sub>SSA3</sub>          | analog ground supply 3, demodulator part                   |                                                       | _    | 0.0  | _    | V    |

| I <sub>DDA3</sub>          | analog supply current 3,                                   | V <sub>DDA3</sub> = 5.5 V                             | 24   | 32   | 40   | mA   |

|                            | demodulator part                                           | V <sub>DDA3</sub> = 5.0 V                             | 24   | 32   | 40   | mA   |

| $V_{DEC1}$                 | analog supply decoupling voltage for front-end             |                                                       | -    | 3.3  | _    | V    |

| V <sub>SSA2</sub>          | analog ground supply 2                                     |                                                       | _    | 0.0  | _    | V    |

| V <sub>ref1</sub>          | analog reference voltage, demodulator part                 |                                                       | _    | 2    | _    | V    |

| I <sub>ref1(sink)</sub>    | V <sub>ref1</sub> sink current                             |                                                       | _    | 200  | _    | μΑ   |

| Audio suppl                | lies and references                                        |                                                       |      | •    | •    | •    |

| V <sub>DDA1</sub>          | analog supply voltage 1, operational amplifiers            |                                                       | 4.5  | 5.0  | 5.5  | V    |

| V <sub>SSA1</sub>          | analog ground supply 1, operational amplifiers             |                                                       | -    | 0.0  | -    | V    |

| I <sub>DDA1</sub>          | analog supply current 1,                                   | V <sub>DDA1</sub> = 5.5 V                             | 3    | 6    | 10   | mA   |

|                            | operational amplifiers                                     | V <sub>DDA1</sub> = 5.0 V                             | 3    | 5    | 10   | mA   |

| V <sub>SSA4</sub>          | analog ground supply 4, audio DAC part                     |                                                       | -    | 0.0  | -    | V    |

| V <sub>ref2</sub>          | reference voltage 2, audio DACs and operational amplifiers | referenced to V <sub>DDA1</sub> and V <sub>SSA1</sub> | _    | 50   | _    | %    |

| Z <sub>(Vref2-VDDA3)</sub> | impedance V <sub>ref2</sub> to V <sub>DDA3</sub>           |                                                       | _    | 20   | _    | kΩ   |

TDA9874A

| SYMBOL                     | PARAMETER                                        | CONDITIONS                   | MIN.                | TYP.                 | MAX.                | UNIT |

|----------------------------|--------------------------------------------------|------------------------------|---------------------|----------------------|---------------------|------|

| Z <sub>(Vref2-VSSA3)</sub> | impedance V <sub>ref2</sub> to V <sub>SSA3</sub> |                              | -                   | 20                   | _                   | kΩ   |

| Digital input              | s and outputs                                    |                              |                     |                      |                     |      |

| INPUTS                     |                                                  |                              |                     |                      |                     |      |

| CMOS level                 | input, high drive, pull-down (pins               | TEST1, TEST2, TP1 and TF     | P2)                 |                      |                     |      |

| V <sub>IL</sub>            | LOW-level input voltage                          |                              | <u> </u>            | _                    | 0.3V <sub>DDD</sub> | V    |

| V <sub>IH</sub>            | HIGH-level input voltage                         |                              | 0.7V <sub>DDD</sub> | _                    | -                   | V    |

| C <sub>i</sub>             | input capacitance                                |                              | _                   | _                    | 10                  | pF   |

| Z <sub>i</sub>             | input impedance                                  |                              | _                   | 50                   | _                   | kΩ   |

| CMOS level                 | input, hysteresis, high drive, pull-t            | up (pin CRESET)              |                     |                      |                     |      |

| V <sub>IL</sub>            | LOW-level input voltage                          |                              |                     | _                    | 0.3V <sub>DDD</sub> | V    |

| V <sub>IH</sub>            | HIGH-level input voltage                         |                              | 0.7V <sub>DDD</sub> | _                    | _                   | V    |

| V <sub>hys</sub>           | hysteresis voltage                               |                              | _                   | 1.3                  | _                   | V    |

| C <sub>i</sub>             | input capacitance                                |                              | _                   | _                    | 10                  | pF   |

| Z <sub>i</sub>             | input impedance                                  | _                            | 50                  | _                    | kΩ                  |      |

| INPUTS/OUTPU               | JTS                                              |                              |                     | !                    | !                   |      |

| I <sup>2</sup> C-bus level | input with Schmitt trigger, open-c               | drain output stage (pins SCL | and SDA)            |                      |                     |      |

| V <sub>IL</sub>            | LOW-level input voltage                          |                              |                     | I_                   | 0.3V <sub>DDD</sub> | V    |

| V <sub>IH</sub>            | HIGH-level input voltage                         |                              | 0.7V <sub>DDD</sub> | _                    | -                   | V    |

| V <sub>hys</sub>           | hysteresis voltage                               |                              | -                   | 0.05V <sub>DDD</sub> | _                   | V    |

| I <sub>LI</sub>            | input leakage current                            |                              | _                   | -                    | ±10                 | μА   |

| C <sub>i</sub>             | input capacitance                                |                              | _                   | _                    | 10                  | pF   |

| V <sub>OL</sub>            | LOW-level output voltage                         |                              | _                   | _                    | 0.6                 | V    |

| C <sub>L</sub>             | load capacitance                                 |                              | _                   | _                    | 400                 | pF   |

| WS and SDC                 | ,                                                | out stage, pull-up (pins PCL | K, NICAM, AD        | DR1, ADDF            | R2, P1, P2          | 1    |

| V <sub>IL</sub>            | LOW-level input voltage                          |                              |                     | _                    | 0.8                 | V    |

| V <sub>IH</sub>            | HIGH-level input voltage                         |                              | 2.0                 | _                    | _                   | V    |

| C <sub>i</sub>             | input capacitance                                |                              |                     | _                    | 10                  | pF   |

| V <sub>OL</sub>            | LOW-level output voltage                         | I <sub>OL</sub> = 3 mA       |                     | _                    | 0.4                 | V    |

| V <sub>OH</sub>            | HIGH-level output voltage                        | I <sub>OH</sub> = -3 mA      | 2.4                 | _                    | _                   | V    |

| C <sub>L</sub>             | load capacitance                                 | active pull-up               |                     | -                    | 100                 | pF   |

| Z <sub>i</sub>             | input impedance                                  |                              |                     | 50                   | _                   | kΩ   |

| OUTPUTS                    |                                                  |                              |                     |                      |                     |      |

| 4 mA 3-state               | output stage (pin SYSCLK)                        |                              |                     |                      |                     |      |

| V <sub>OL</sub>            | LOW-level output voltage                         | I <sub>OL</sub> = 2 mA       | -                   | _                    | 0.3V <sub>DDD</sub> | V    |

| V <sub>OH</sub>            | HIGH-level output voltage                        | I <sub>OH</sub> = -2 mA      | 0.7V <sub>DDD</sub> | _                    | _                   | V    |

| C <sub>L</sub>             | load capacitance                                 |                              | _                   | _                    | 100                 | pF   |

| $I_{LO(Z)}$                | 3-state leakage current                          | $V_i = 0$ to $V_{DDD}$       | _                   | _                    | ±10                 | μΑ   |

TDA9874A

| SYMBOL                      | PARAMETER                                                  | CONDITIONS                                                                                                  | MIN. | TYP. | MAX. | UNIT     |

|-----------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| SIF1 and SIF                | 2 analog inputs                                            |                                                                                                             | · ·  | 1    | •    |          |

| V <sub>SIF(max)(p-p)</sub>  | maximum composite SIF input voltage before clipping        | SIF input level adjustment 0 dB                                                                             | _    | 941  | -    | mV       |

|                             | (peak-to-peak value)                                       | SIF input level adjustment –10 dB                                                                           | _    | 2976 | _    | mV       |

| V <sub>SIF(min)(p-p)</sub>  | minimum composite SIF input voltage for lower limit of AGC | SIF input level adjustment 0 dB                                                                             | _    | 59   | _    | mV       |

|                             | (peak-to-peak value)                                       | SIF input level adjustment –10 dB                                                                           | _    | 188  | _    | mV       |

| AGC                         | AGC range                                                  |                                                                                                             | _    | 24   | _    | dB       |

| $f_i$                       | input frequency                                            |                                                                                                             | 4    | _    | 9.2  | MHz      |

| R <sub>i</sub>              | input resistance                                           | AGCLEV = 0                                                                                                  | 10   | _    | _    | kΩ       |

| C <sub>i</sub>              | input capacitance                                          |                                                                                                             | _    | 7.5  | 11   | pF       |

| $\Delta f_{FM}$             | FM deviation                                               | B/G standard; THD < 1%                                                                                      | ±100 | _    | _    | kHz      |

| $\Delta f_{\text{FM(FS)}}$  | FM deviation full-scale level                              | terrestrial FM; level<br>adjustment 0 dB;<br>demodulator filter bandwidth<br>set to narrow                  | ±150 | _    | _    | kHz      |

| $\Delta f_{\text{FM(max)}}$ | maximum FM deviation in high deviation mode                | B/G standard; THD < 1%;<br>demodulator filter bandwidth<br>set to extra wide                                | ±335 | -    | -    | kHz      |

| C/N <sub>FM</sub>           | FM carrier-to-noise ratio                                  | N <sub>FM</sub> bandwidth = 6 MHz;<br>white noise for S/N = 40 dB;<br>"CCIR468-2", quasi peak               | _    | 77   | -    | dB<br>Hz |

| C/N <sub>N</sub>            | NICAM carrier-to-noise ratio                               | N <sub>N</sub> bandwidth = 6 MHz; bit error rate = 10 <sup>-3</sup> ; white noise                           | -    | 66   | -    | dB<br>Hz |

| $\alpha_{ct}$               | crosstalk attenuation<br>SIF1 to SIF2                      | f <sub>i</sub> = 4 to 9.2 MHz                                                                               | 50   | -    | _    | dB       |

| Demodulato                  | r performance                                              |                                                                                                             |      |      |      |          |

| V <sub>o(nom)(rms)</sub>    | nominal level output voltage (RMS value)                   | note 1                                                                                                      | 400  | 500  | 600  | mV       |

| THD + N                     | total harmonic distortion plus noise                       | from FM source to any output; f <sub>i</sub> = 1 kHz; bandwidth 20 Hz to 20 kHz; V <sub>o</sub> = 1 V (RMS) | _    | 0.3  | 0.5  | %        |

|                             |                                                            | from NICAM source to any output; $f_i = 1$ kHz; bandwidth 20 Hz to 20 kHz; $V_o = 1$ V (RMS)                | _    | 0.1  | 0.3  | %        |

TDA9874A

| SYMBOL                      | PARAMETER                                   | CONDITIONS                                                                     | MIN.   | TYP.                        | MAX.   | UNIT     |

|-----------------------------|---------------------------------------------|--------------------------------------------------------------------------------|--------|-----------------------------|--------|----------|

| S/N                         | signal-to-noise ratio                       | V <sub>o</sub> = 1 V (RMS);<br>"CCIR468-2"; quasi peak                         |        |                             |        |          |

|                             |                                             | SC1 from FM source to any output                                               | 64     | 70                          | _      | dB       |

|                             |                                             | SC2 from FM source to any output                                               | 60     | 66                          | _      | dB       |

|                             |                                             | SC1 during use of high deviation mode from FM source to any output             | 62     | 68                          | _      | dB       |

|                             |                                             | NICAM source                                                                   | _      | n accordan<br>ecification"; |        |          |

| B <sub>(-3dB)</sub>         | -3 dB bandwidth                             | from FM source to any output                                                   | 14.5   | 15                          | _      | kHz      |

|                             |                                             | from NICAM source to any output                                                | 14.5   | 15                          | _      | kHz      |

| f <sub>resp</sub>           | frequency response<br>20 Hz to 14 kHz       | from FM/NICAM to any output; reference 1 kHz                                   | -2     | -                           | +1     | dB       |

| α <sub>cd(dual)</sub>       | dual signal channel separation              | note 3                                                                         | 65     | 70                          | _      | dB       |

| α <sub>cs(stereo)</sub>     | stereo channel separation                   | note 4                                                                         | 40     | 45                          | _      | dB       |

| $\alpha_{AM}$               | AM suppression for FM                       | AM: 1 kHz, 30% modulation; reference: f <sub>i</sub> = 1 kHz; 50 kHz deviation | 50     | -                           | -      | dB       |

| dm <sub>AM</sub>            | AM demodulation                             | SIF level 100 mV (RMS);<br>54% AM; 1 kHz AF;<br>"CCIR468-2"; quasi peak        | 36     | 45                          | -      | dB       |

| IDENTIFICATIO               | N FOR FM SYSTEMS                            |                                                                                | !      | 1                           |        | 1        |

| m <sub>pilot(ident)</sub>   | pilot modulation for identification         |                                                                                | 25     | 50                          | 75     | %        |

| C/N <sub>pilot(ident)</sub> | pilot sideband C/N for identification start |                                                                                | -      | 27                          | -      | dB<br>Hz |

| hys <sub>(tun)</sub>        | hysteresis                                  |                                                                                | _      | -                           | 2      | dB       |

| f <sub>ident</sub>          | identification window                       | B/G stereo                                                                     |        |                             |        |          |

|                             |                                             | slow mode                                                                      | 116.85 | _                           | 118.12 | Hz       |

|                             |                                             | medium mode                                                                    | 116.11 | _                           | 118.89 | Hz       |

|                             |                                             | fast mode                                                                      | 114.65 | _                           | 120.46 | Hz       |

|                             |                                             | B/G dual                                                                       |        |                             |        |          |

|                             |                                             | slow mode                                                                      | 273.44 | _                           | 274.81 | Hz       |

|                             |                                             | medium mode                                                                    | 272.07 | _                           | 276.20 | Hz       |

|                             |                                             | fast mode                                                                      | 270.73 | _                           | 277.60 | Hz       |

| t <sub>on(ident)</sub>      | total identification time on                | slow mode                                                                      | _      | _                           | 2      | s        |

|                             |                                             | medium mode                                                                    | _      | _                           | 1      | s        |

|                             |                                             | fast mode                                                                      | _      | _                           | 0.5    | s        |

TDA9874A

| SYMBOL                    | PARAMETER                                                                                                                                                         | CONDITIONS                                                                                                                                   | MIN. | TYP. | MAX. | UNIT |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>off(ident)</sub>   | total identification time off                                                                                                                                     | slow mode                                                                                                                                    | _    | _    | 2    | s    |

|                           |                                                                                                                                                                   | medium mode                                                                                                                                  | _    | _    | 1    | s    |

|                           |                                                                                                                                                                   | fast mode                                                                                                                                    | _    | _    | 0.5  | s    |

| Mono and e                | xternal inputs                                                                                                                                                    |                                                                                                                                              |      |      |      |      |

| $V_{i(nom)(rms)}$         | nominal level input voltage (RMS value)                                                                                                                           | note 1                                                                                                                                       | _    | 500  | -    | mV   |

| $V_{i(cl)(rms)}$          | clipping level input voltage (RMS value)                                                                                                                          | THD < 3%; note 5                                                                                                                             | 1250 | 1400 | -    | mV   |

| R <sub>i</sub>            | input resistance                                                                                                                                                  | note 5                                                                                                                                       | 28   | 35   | 42   | kΩ   |

| Analog audi               | io outputs                                                                                                                                                        | •                                                                                                                                            | •    |      | •    | •    |

| V <sub>o(clip)(rms)</sub> | clipping level output voltage (RMS value)                                                                                                                         | THD < 3%                                                                                                                                     | 1400 | _    | _    | mV   |

| R <sub>o</sub>            | output resistance                                                                                                                                                 |                                                                                                                                              | 150  | 250  | 375  | Ω    |

| R <sub>L(AC)</sub>        | AC load resistor                                                                                                                                                  |                                                                                                                                              | 10   | _    | _    | kΩ   |

| R <sub>L(DC)</sub>        | DC load resistor                                                                                                                                                  |                                                                                                                                              | 10   | _    | _    | kΩ   |

| C <sub>o(L)</sub>         | output load capacitor                                                                                                                                             |                                                                                                                                              | _    | 10   | 12   | nF   |

| V <sub>offset(DC)</sub>   | static DC offset voltage                                                                                                                                          |                                                                                                                                              | _    | 30   | 70   | mV   |

| $\alpha_{mute}$           | mute suppression                                                                                                                                                  | nominal input signal from any source; f <sub>i</sub> = 1 kHz; note 1                                                                         | 80   | _    | -    | dB   |

| B <sub>line</sub>         | bandwidth                                                                                                                                                         | from external and mono source; –3 dB bandwidth                                                                                               | 20   | _    | _    | kHz  |

| G <sub>ro</sub>           | roll-off gain at 14.5 kHz                                                                                                                                         | from any source                                                                                                                              | -3   | -2   | _    | dB   |

| PSRR                      | power supply ripple rejection $f_{ripple} = 70 \text{ Hz;} \\ V_{ripple} = 100 \text{ mV (peak);} \\ C_{Vref} = 47  \mu\text{F; signal from } \\ I^2S\text{-bus}$ |                                                                                                                                              | 40   | 45   | -    | dB   |

| Audio perfo               | rmance                                                                                                                                                            |                                                                                                                                              |      |      | •    | •    |

| THD + N                   | total harmonic distortion plus noise                                                                                                                              | V <sub>in/out</sub> = 1 V (RMS);<br>f <sub>i</sub> = 1 kHz; bandwidth<br>20 Hz to 20 kHz; from<br>external/mono input to<br>output copy      | _    | 0.1  | 0.3  | %    |

| S/N                       | signal-to-noise ratio                                                                                                                                             | reference voltage  V <sub>0</sub> = 1.4 V (RMS); f <sub>i</sub> = 1 kHz; "CCIR468-2"; quasi peak; from external or mono input to output copy | 78   | 90   | -    | dB   |

| $\alpha_{ct}$             | crosstalk attenuation                                                                                                                                             | between any analog input pairs; f <sub>i</sub> = 1 kHz                                                                                       | 70   | _    | -    | dB   |

| $\alpha_{	t cs}$          | channel separation                                                                                                                                                | between left and right of external input pair                                                                                                | 65   | _    | -    | dB   |

|                           |                                                                                                                                                                   | between left and right of output pair                                                                                                        | 60   | -    | _    | dB   |

**TDA9874A**

| SYMBOL                                   | PARAMETER                                     | PARAMETER CONDITIONS MIN.                  |                 | TYP.   | MAX. | UNIT                     |  |  |  |

|------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------|--------|------|--------------------------|--|--|--|

| Crystal specification (fundamental mode) |                                               |                                            |                 |        |      |                          |  |  |  |

| f <sub>xtal</sub>                        | crystal frequency                             | note 6                                     | _               | 24.576 | _    | MHz                      |  |  |  |

| C <sub>L</sub>                           | load capacitance                              |                                            | _               | 20     | Ī-   | pF                       |  |  |  |

| C <sub>1</sub>                           | series capacitance                            |                                            | _               | 20     | Ī-   | fF                       |  |  |  |

| C <sub>0</sub>                           | parallel capacitance                          |                                            | _               | _      | 7    | pF                       |  |  |  |

| $\Phi_{pull}$                            | pulling sensitivity                           | C <sub>L</sub> changed from<br>18 to 16 pF | _               | 25     | -    | 10 <sup>-6</sup> pF      |  |  |  |

| R <sub>R</sub>                           | equivalent series resistance                  | at nominal frequency                       | _               | _      | 30   | Ω                        |  |  |  |

| R <sub>N</sub>                           | equivalent series resistance of unwanted mode |                                            | 2R <sub>R</sub> | _      | _    | Ω                        |  |  |  |

| ΔΤ                                       | temperature range                             |                                            | -20             | +25    | +70  | °C                       |  |  |  |

| X <sub>J</sub>                           | adjustment tolerance                          |                                            | _               | _      | ±30  | 10 <sup>-6</sup>         |  |  |  |

| X <sub>D</sub>                           | drift                                         | across temperature range                   | _               | _      | ±30  | 10 <sup>-6</sup>         |  |  |  |

| X <sub>A</sub>                           | ageing                                        |                                            | -               | -      | ±5   | 10 <sup>-6</sup><br>year |  |  |  |

### **Notes**

- 1. Definition of levels and level setting:

- a) The full-scale level for analog audio signals is  $V_{FS} = 1.4 \text{ V (RMS)}$ . The nominal level at the digital crossbar switch is defined at -15 dB (FS).

- b) Nominal audio input levels: external, mono: 500 mV; -9 dB (FS).

- 2. Audio performance is limited by the dynamic range of the NICAM 728 system. Due to companding, the quantization noise is never lower than –62 dB with respect to the input level.

- 3. FM source; in dual mode only A (respectively B) signal modulated; measured at B (respectively A) channel output;  $V_0 = 1 \text{ V (RMS)}$  of modulated channel.

- 4. FM source; in stereo mode only L (respectively R) signal modulated; measured at R (respectively L) channel output;  $V_0 = 1 \text{ V (RMS)}$  of modulated channel.

- 5. If the supply voltage for the TDA9874A is switched off, because of the ESD protection circuitry, all audio input pins are short-circuited.

- 6. The Philips crystal (order number 9922 520 20106) is suitable for this application.

TDA9874A

Preliminary specification

Table 6 Level setting FM, AM and NICAM 0 dB (FS) = 1.4 V (RMS); FS = full-scale.

1999 Dec 03

| SOURCE                           | TRANSMITTER NOMINAL MODULATION DEPTH | NOMINAL LEVEL AT DEMODULATOR OUTPUT | LEVEL<br>ADJUSTMENT<br>SETTING | NOMINAL LEVEL<br>AT CROSSBAR                   | DAC GAIN<br>SETTING | NOMINAL OUTPUT<br>VOLTAGE V <sub>O</sub> |

|----------------------------------|--------------------------------------|-------------------------------------|--------------------------------|------------------------------------------------|---------------------|------------------------------------------|

| FM<br>M standard                 | 15 kHz deviation                     | -24 dB (FS)                         | +9 dB                          | -15 dB (FS)<br>(spread of ±0.5 dB              | +6 dB               | 500 mV (RMS)                             |

| FM<br>B/G, D/K, I<br>standard    | 27 kHz deviation                     | -19 dB (FS)                         | +4 dB                          | due to different<br>transmitter<br>references) |                     |                                          |

| AM<br>L/L accent<br>standard     | 54%                                  | -19 dB (FS)                         | +4 dB                          |                                                |                     |                                          |