### DEVELOPMENT DATA

This data sheet contains advance information and specifications are subject to change without notice,

TDA8451A

T-47-2/

PHILIPS INTERNATIONAL

56E D 7110826 0036967 T25 PHIN

# P<sup>2</sup>CCD DELAY LINE AND MATRIX

#### **GENERAL DESCRIPTION**

The TDA8451A is an integrated P<sup>2</sup> CCD (Profiled Peristaltic Charge Coupled Device) delay line and matrix which has been designed to be used in conjunction with various colour decoder ICs (e.g. TDA8466, TDA8391). The device incorporates two delay lines with a delay length of 1 line time for colour difference signals, adding circuits for the delayed and direct signals and clock drivers for the delay lines which are driven from an internal voltage controlled oscillator (VCO) locked to the sandcastle pulse.

The TDA8451A differs from the TDA8451 by the following:

- The VCO is line locked instead of sub-carrier locked

- Adding direct and delayed signals occurs for PAL, SECAM and NTSC

#### **QUICK REFERENCE DATA**

| parameter                                            | conditions                           | symbol                                     | min.         | typ.         | max.         | unit     |

|------------------------------------------------------|--------------------------------------|--------------------------------------------|--------------|--------------|--------------|----------|

| Supply voltage<br>anàlog (pin 3)<br>digital (pin 16) |                                      | V <sub>P(a)</sub><br>V <sub>P(d)</sub>     | 10.8<br>10.8 | 12.0<br>12.0 | 13.2<br>13.2 | V<br>V   |

| Supply current<br>analog (pin 3)<br>digital (pin 16) |                                      | IP(a)<br>IP(d)                             | 5<br>10      | 10<br>22     | 15<br>35     | mA<br>mA |

| Colour difference input signals (peak-to-peak value) | PAL/NTSC mode<br>SECAM mode          | V <sub>I(p-p)</sub><br>V <sub>I(p-p)</sub> | _<br>_       | <br>_        | 1.1<br>2.1   | V<br>V   |

| Output signals                                       | PAL/NTSC mode<br>0.8 V(p-p)<br>input | Vo                                         |              | 0.8          | _            | V        |

|                                                      | SECAM mode<br>1.6 V(p-p)             |                                            |              |              |              |          |

|                                                      | input                                | ۷o                                         | -            | 0.8          |              | V        |

| Output resistance                                    |                                      | RO                                         | -            | 500          | -            | Ω        |

| Frequency response                                   |                                      | Δf                                         | -            | 1.3          | –            | MHz      |

| Additional delay                                     |                                      | t <sub>d</sub>                             | _            | 760          | _            | ns       |

#### **PACKAGE OUTLINE**

16-lead DIL; plastic with internal heat spreader (SOT38GG2).

1. If the TDA8451A is followed by a TDA4566 (CTI), it is recommended to replace the LC trap (and the usual RC low-pass filter in front of the TDA4566) by an LC low-pass circuit where L = 47  $\mu$ H and C = 270 pF.

2. For multistandard concepts, including NTSC, the following values are recommended; R1 = 47 kΩ, C1 = 100 nF and C2 = 2.2 nF.

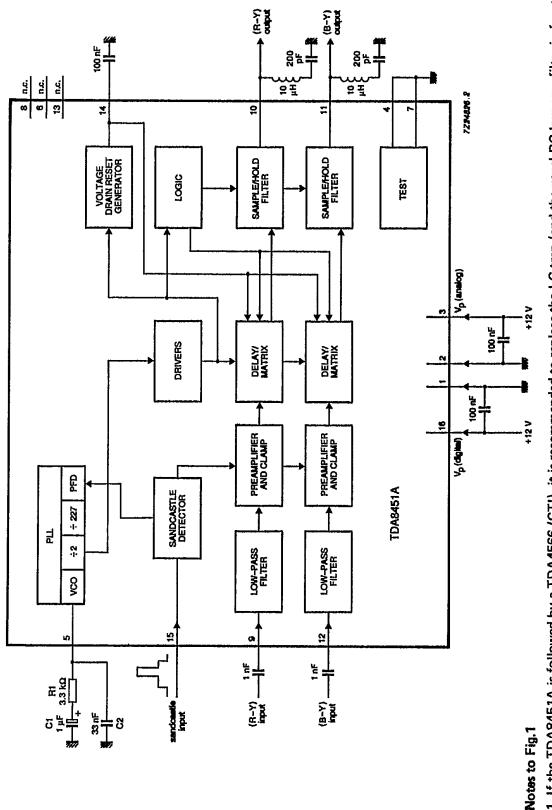

Fig. 1 Block diagram.

56E D

7110826 0036969 8T8 PHIN

#### **PINNING**

- 1 Ground (digital)

- 2 Ground (analog)

- Supply voltage input (analog)

- Test pin (grounded for normal operation)

- PLL filter 5

- 6 Not connected

- 7 Test pin (grounded for normal operation)

- Not connected

- (R-Y) input

- (R-Y) output 10

- (B-Y) output 11

- 12 (B-Y) input

- 13 Not connected

- 14 Voltage drain reset generator decoupling

- 15 Sandcastle input

- Supply voltage input (digital) 16

### TDA8451A

PHILIPS INTERNATIONAL

56E D 7110826 0036970 51T MPHIN

T-47-21

#### **FUNCTIONAL DESCRIPTION**

When the (R-Y) and (B-Y) signals have been demodulated in the decoder, the resultant signals are applied to pins 9 and 12. The colour difference signals are then applied via a low-pass filter, preamplifier and clamp circuit to the delay lines. The delayed and direct signals are added in the matrix circuit.

This action occurs for PAL, SECAM and NTSC signals. Consequently, the NTSC colour difference signals are combed.

The frequency generated by the PLL circuit is 454 times the sandcastle frequency. The delay lines are driven by the internal clock drivers at half on the PLL frequency. The outputs from the delay lines are applied to the sample-and-hold low-pass filter output stages which are used to reduce the clock signals.

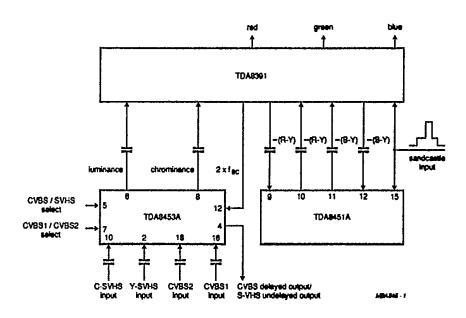

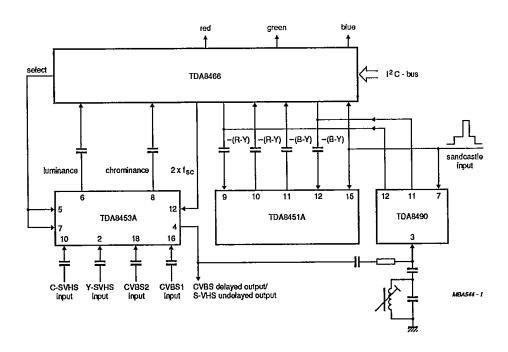

The P<sup>2</sup>CCD delay line and matrix requires a supply voltage of 12 V. The output stages require a higher voltage (approximately 14 V). This voltage is generated internally with a decoupling capacitor connected to pin 14. A circuit for the TDA8451A together with PAL decoder (TDA8391) is illustrated in Fig.2. A circuit for the TDA8451A together with the PAL/NTSC decoder (TDA8466) and the SECAM decoder (TDA8490) is illustrated in Fig.3. The TDA8490 can also be used in combination with the TDA8391.

56E D

■ 7110826 0036971 456 ■PHIN

#### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

T-47-21

| parameter                           | conditions | symbol            | min. | max.  | unit |

|-------------------------------------|------------|-------------------|------|-------|------|

| Supply voltage (analog)             |            | V <sub>P(a)</sub> |      | 13.2  | V    |

| Supply voltage (digital)            |            | V <sub>P(d)</sub> |      | 13.2  | V    |

| Total power dissipation             |            | P <sub>tot</sub>  | _    | 1.45  | W    |

| Operating ambient temperature range |            | Tamb              | -25  | +70   | oC   |

| Storage temperature range           |            | T <sub>stg</sub>  | 55   | + 150 | oC   |

#### THERMAL RESISTANCE

From junction to ambient (in free air)

R<sub>th j-a</sub>

55 K/W

# 56E D 7110826 0036972 392 MMPHIN -

#### **CHARACTERISTICS**

Vp = 12 V; Tamb = 25 °C unless otherwise specified

| P = 12 v; Tamb = 25 °C unless offie                                         | Marse sherriner      | 4                   |                            |              | 1-4/- | <b>4</b> 1   |

|-----------------------------------------------------------------------------|----------------------|---------------------|----------------------------|--------------|-------|--------------|

| parameter                                                                   | conditions           | symbol              | min.                       | typ.         | max.  | unit         |

| Supplies                                                                    |                      |                     |                            |              |       |              |

| Supply voltage (pin 3) analog                                               |                      | V <sub>P(a)</sub>   | 10.8                       | 12.0         | 13.2  | v            |

| Supply current (pin 3) analog                                               |                      | I <sub>P(a)</sub>   | 5                          | 10           | 15    | mA           |

| Supply voltage (pin 3) ripple rejection at 100 mVeff                        | f = 100 Hz<br>note 1 | SVRR                | _                          | 10           | _     | dB           |

| Supply voltage (pin 16)<br>digital                                          |                      | V <sub>P(d)</sub>   | 10.8                       | 12.0         | 13.2  | ,<br>, v     |

| Supply current (pin 16) digital                                             |                      | IP(d)               | 10                         | 22           | 35    | i<br>mA      |

| Supply voltage (pin 16) ripple rejection at 100 mVeff                       | f = 100 Hz<br>note 1 | SVRR                | _                          | 25           | _     | dB           |

| Total power dissipation                                                     |                      | P <sub>tot</sub>    | -                          | 0.38         | 0.66  | w            |

| Inputs for demodulated colour difference signals (pins 9 and 12)            |                      |                     | markanity : Arthur (Arthur | -            |       |              |

| AC coupled and clamped by sandcastle pulse                                  |                      |                     | rate : Mindage &           | :            |       |              |

| Input signal PAL/NTSC mode (peak-to-peak value)                             |                      | V <sub>I(p-p)</sub> | _                          | _            | 1.1   | V            |

| Input signal SECAM mode (peak-to-peak value)                                | i<br>i               | V <sub>I(p-p)</sub> |                            |              | 2.1   | !<br>V       |

| Input current                                                               | <u>.</u>             | '\P'                | •<br>•                     |              |       |              |

| (outside clamping time)                                                     | :<br>!               | ļl                  | · —                        | i –          | 0.1   | μΑ           |

| Input capacitance                                                           |                      | Cı                  | _                          | 10           | _     | рF           |

| Sandcastle input (pin 15)                                                   |                      | ļ                   |                            | -            |       | <del>-</del> |

| Input resistance                                                            | <u> </u>             | R <sub>15</sub>     | 1000                       |              | l –   | kΩ           |

| Detection level                                                             | #<br>:<br>:          | V <sub>15</sub>     | 6.0                        | 6.8          | 7.5   | V            |

| CD signal output (pins 10 and 11)                                           |                      |                     |                            |              |       | 1            |

| Output signals where input signal is PAL/NTSC at 0.8 V (peak-to-peak value) |                      | V10-11/>            | 0.63                       | 0.8          | 1.01  | · V          |

| Output signals where input signal is SECAM at 1.6 V                         |                      | V10; 11(p-p)        | 0.00                       | 0.0<br> <br> | 1.01  |              |

| (peak-to-peak value)                                                        | note 2               | V10; 11(p-p)        | 0.63                       | 0.8          | 1.01  | v            |

56E D

7110826 0036973 229

■ PHIN

| parameter                                                                       | conditions              | symbol                   | min.     | typ.     | max.     | unit   |

|---------------------------------------------------------------------------------|-------------------------|--------------------------|----------|----------|----------|--------|

| Output resistance                                                               |                         | RO                       | 300      | 500      | 800      | Ω      |

| Internal current load of CD outputs                                             |                         | l <sub>10; 11</sub>      | 0.4      | -        | 1.5      | mA     |

| DC output level                                                                 |                         | V <sub>10</sub> ; 11     | 4        | <u> </u> | 8        | V      |

| Rest clock signals (RMS value) at 3.55 MHz                                      | note 3                  | V <sub>10-11</sub> (rms) | ļ<br>_   |          | 5        | mV     |

| at 7.09 MHz                                                                     |                         | V10-11(rms)              | _        | -        | 6        | mV     |

| at 14.19 MHz                                                                    |                         | V10-11(rms)              | <u>-</u> | _        | 6        | mV     |

| Signal-to-noise ratio                                                           | note 4                  | S/N                      | 60       | 65       | <b> </b> | dB     |

| Linearity of output signals (peak-to-peak value)                                | note 5                  |                          |          | f        |          | !<br>! |

| (R-Y); pin 9 to 10 PAL/NTSC                                                     | $V_1 = 0.85 V$          | α                        | 0.95     | <u> </u> | -        |        |

| (R-Y); pin 9 to 10 SECAM                                                        | V <sub>I</sub> = 1.60 V | α                        | 0.92     | · –      | <u> </u> |        |

| (B-Y); pin 12 to 11 PAL/NTSC                                                    | V <sub>I</sub> = 1.10 V | α                        | 0.95     | <u> </u> | -        |        |

| (B-Y); pin 12 to 11 SECAM                                                       | V <sub>I</sub> = 2.10 V | α                        | 0.92     | -        | <u> </u> | i      |

| Frequency response                                                              | at -3 dB                | Δf                       | 1.0      | 1.3      | _        | MHz    |

| Difference in amplitude<br>between delayed and<br>undelayed signal              |                         |                          |          | _        | 1.5      | %      |

| Difference in amplitude of the<br>two output signals for equal<br>input signals |                         |                          |          | -        | 5        | %      |

| Delay time with a 15625 kHz sandcastle pulse                                    |                         | <sup>t</sup> d           | _        | 760      | _        | ns     |

#### Notes to the characteristics

- 1. The SVRR is measured with a 100  $\Omega$  resistor in series with a 1 nF capacitor connected between pin 9 and pin 2 and between pin 12 and pin 2.

- 2. During SECAM the input signal is available during one of two sequential lines. The output signal is thereby halved in comparison with the PAL signal condition. To compensate for this the input signal to the TDA8451A during SECAM is twice that during PAL.

- 3. The rest clock signals are measured with an FET probe (3.5 pF capacitor in parallel with a 1 M $\Omega$ resistor) which is connected directly to pin 1 and pin 10 or pin 1 and pin 11.

- 4. The signal-to-noise ratio (in the PAL mode) is calculated by:

----- at an input voltage of 0.8 V(p-p), 0 dB gain Vnoise(rms) (0-1 MHz)

5. The linearity is defined as the amplification of the given input voltage swing divided by the amplification when the input voltage swing is decreased to 70%.

56E D 7110826 0036974 165 PHIN

Fig.2 PAL decoder configuration.

56E D 7110826 0036975 OT1 PHIN

Fig.3 PAL-NTSC-SECAM decoder configuration.