## **INTEGRATED CIRCUITS**

## DATA SHEET

# **TDA6118JF**Video output amplifier

Product specification Supersedes data of 2002 May 06 2004 Aug 26

#### **TDA6118JF**

#### **FEATURES**

- · Bandwidth independent of gain

- Rise and fall times of 21 ns at 100 V (p-p)

- · Very simple application

- Switchable gain of -50 and -80

- Switchable output black level of 126 V and 155 V

- Internal reference voltage

- Cathode current measurement output for black-current stabilization

- · Thermal protection.

#### **GENERAL DESCRIPTION**

The TDA6118JF is a video output amplifier in a plastic DIL-bent-SIL 9-pin medium power (DBS9MPF) package (SOT111-1) using high-voltage DMOS technology, and is intended to drive the cathode of a colour CRT directly. To obtain maximum performance, the amplifier should be used with black-current control.

#### **ORDERING INFORMATION**

| TYPE NUMBER     |         | PACKAGE                                                         |         |  |  |  |

|-----------------|---------|-----------------------------------------------------------------|---------|--|--|--|

| TIPE NOWIBER    | NAME    | DESCRIPTION                                                     | VERSION |  |  |  |

| TDA6118JF/N2/S1 | DBS9MPF | plastic DIL-bent-SIL medium power package with fin; 9 leads SOT |         |  |  |  |

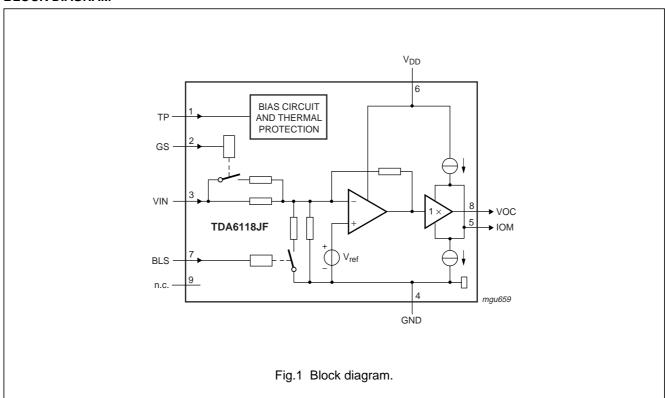

#### **BLOCK DIAGRAM**

#### **TDA6118JF**

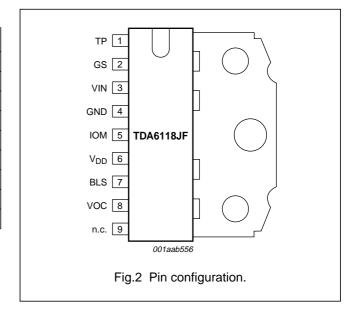

#### **PINNING**

| SYMBOL   | PIN | DESCRIPTION                      |  |  |  |  |

|----------|-----|----------------------------------|--|--|--|--|

| TP       | 1   | thermal protection input         |  |  |  |  |

| GS       | 2   | gain selection input             |  |  |  |  |

| VIN      | 3   | inverting input                  |  |  |  |  |

| GND      | 4   | ground                           |  |  |  |  |

| IOM      | 5   | black-current measurement output |  |  |  |  |

| $V_{DD}$ | 6   | supply voltage (200 V)           |  |  |  |  |

| BLS      | 7   | black level selection input      |  |  |  |  |

| VOC      | 8   | cathode output                   |  |  |  |  |

| n.c.     | 9   | not connected                    |  |  |  |  |

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134); voltages are measured with respect to pin GND.

| SYMBOL           | PARAMETER                       | CONDITIONS             | MIN.       | MAX.     | UNIT |

|------------------|---------------------------------|------------------------|------------|----------|------|

| $V_{DD}$         | supply voltage                  |                        | 0          | 250      | ٧    |

| V <sub>n</sub>   | voltage on pins                 |                        |            |          |      |

|                  | VOC                             |                        | 0          | $V_{DD}$ | V    |

|                  | VIN, IOM, BLS and GS            |                        | 0          | 12       | V    |

|                  | TP                              |                        | 0          | 24       | V    |

| T <sub>stg</sub> | storage temperature             |                        | <b>-55</b> | +150     | °C   |

| Tj               | junction temperature            |                        | -20        | +150     | °C   |

| V <sub>esd</sub> | electrostatic discharge voltage | Human Body Model (HBM) | -2000      | +2000    | V    |

|                  |                                 | Machine Model (MM)     | -300       | +300     | ٧    |

#### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see "Handling MOS Devices").

#### **QUALITY SPECIFICATION**

In accordance with the "General Quality Specification For Integrated Circuits ("SNW-FQ-611)".

#### TDA6118JF

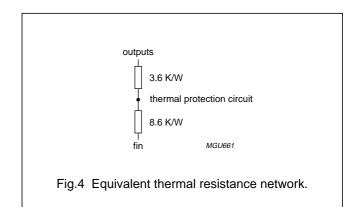

#### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS | VALUE | UNIT |

|----------------------|---------------------------------------------|------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |            | 56    | K/W  |

| $R_{th(j-fin)}$      | thermal resistance from junction to fin     | note 1     | 12.2  | K/W  |

#### Note

1. An external heatsink is necessary.

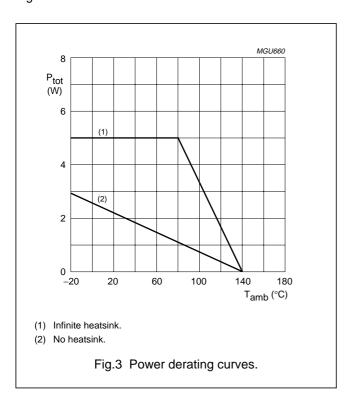

#### Thermal protection

The TDA6118JF is protected against overheating through a thermal protection circuit (see Fig.1). This circuit realizes a decrease of internal quiescent currents at high temperatures and limits the bandwidth and the static and dynamic power dissipation (see Fig.3).

Typical values for the bandwidth:

- 25 % decrease at T<sub>prot</sub> = 145 °C

- 50 % decrease at T<sub>prot</sub> = 155 °C.

Where  $T_{\text{prot}}$  is the temperature on the spot of the thermal protection circuit.

The equivalent thermal resistance network is given in Fig.4.

TDA6118JF

#### **CHARACTERISTICS**

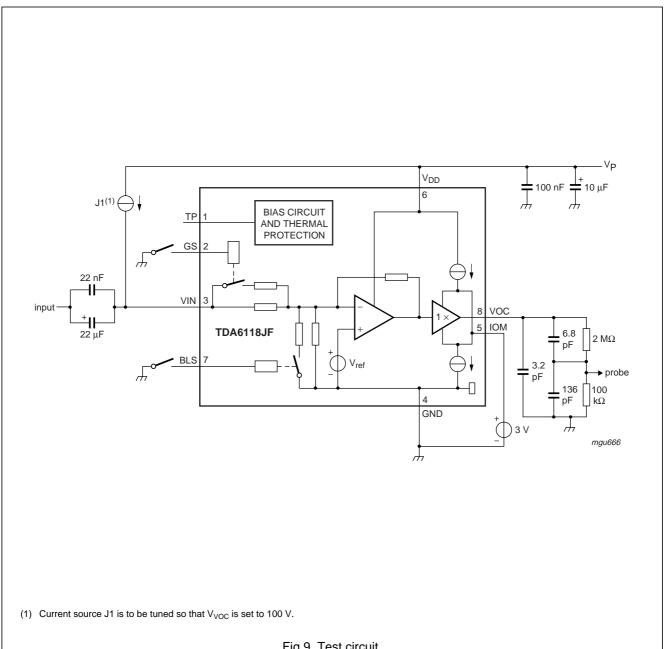

$V_{DD}$  = 200 V;  $V_{VOC}$  = 100 V;  $V_{IOM}$  = 3.0 V;  $V_{GS}$  = 0 V;  $V_{BLS}$  = 0 V;  $R_{th(fin-a)}$  = 18 K/W;  $T_{amb}$  = 25 °C; measured in test circuit of Fig.9; equivalent load of 10 pF which consists of parasitic and cathode capacitance; unless otherwise specified.

| SYMBOL                          | PARAMETER                                                     | CONDITIONS                                                                                                | MIN.                 | TYP. | MAX. | UNIT |

|---------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|------|------|------|

| Supply                          |                                                               |                                                                                                           | •                    | •    | •    | -    |

| Iq                              | quiescent supply current                                      |                                                                                                           | 10                   | 12.5 | 15   | mA   |

| PSRR                            | power supply rejection ratio                                  | f <sub>i</sub> < 50 kHz; note 1                                                                           | _                    | 54   | _    | dB   |

| Operating r                     | ange                                                          |                                                                                                           |                      | •    | •    | •    |

| $V_{DD}$                        | supply voltage                                                |                                                                                                           | 180                  | _    | 210  | V    |

| T <sub>j</sub>                  | junction temperature                                          |                                                                                                           | -20                  | _    | +140 | °C   |

| Input (pin V                    | IN)                                                           |                                                                                                           | •                    | •    |      | •    |

| R <sub>i</sub>                  | input impedance                                               | pin GS connected to ground                                                                                | 1060                 | 1780 | 2500 | Ω    |

|                                 |                                                               | pin GS left open-circuit                                                                                  | 670                  | 1110 | 1550 | Ω    |

| Amplifier                       |                                                               |                                                                                                           |                      | •    | •    | •    |

| G                               | amplifier gain                                                | pin GS connected to ground                                                                                | -45                  | -50  | -55  |      |

|                                 |                                                               | pin GS left open-circuit                                                                                  | -72                  | -80  | -88  |      |

| В                               | bandwidth                                                     | V <sub>VOC</sub> = 40 V (p-p) sine wave                                                                   | _                    | 22   | _    | MHz  |

|                                 |                                                               | V <sub>VOC</sub> = 100 V (p-p) sine wave                                                                  | _                    | 17   | _    | MHz  |

| V <sub>ref</sub>                | internal reference voltage                                    |                                                                                                           | _                    | 2.4  | _    | V    |

| Cathode ou                      | tput (pin VOC); see Figs 5 and                                | 6                                                                                                         |                      |      |      |      |

| V <sub>VOC</sub>                | DC output voltage                                             | pin BLS connected to ground                                                                               | 115                  | 126  | 137  | V    |

|                                 |                                                               | pin BLS left open-circuit                                                                                 | 142                  | 155  | 168  | V    |

| V <sub>VOC(max)</sub>           | maximum output voltage                                        | V <sub>VIN</sub> = 0 V                                                                                    | V <sub>DD</sub> – 18 | _    | _    | V    |

| $V_{VOC(min)}$                  | minimum output voltage                                        | $V_{VIN} = 7 \text{ V}; I_{VOC} = 0 \text{ mA}$                                                           | _                    | _    | 6    | V    |

|                                 |                                                               | $V_{VIN} = 7 \text{ V}; I_{VOC} = 7 \text{ mA}$                                                           | _                    | _    | 17   | V    |

| $\Delta V_{VOC(T)}$             | output voltage variation with temperature                     | pin BLS left open-circuit;<br>T <sub>j</sub> = 0 °C to 100 °C                                             | _                    | 0.5  | _    | V/°C |

| I <sub>VOC(max)</sub>           | maximum output current                                        | 50 V < V <sub>VOC</sub> < V <sub>DD</sub> - 50 V                                                          | 50                   | 70   | _    | mA   |

| Black-curre                     | nt measurement output (pin IC                                 | DM)                                                                                                       |                      |      | •    | -    |

| I <sub>IOM(offset)</sub>        | output offset current                                         | $I_{VOC} = 0$ mA; $V_{VIN} = 0$ V to 5.5 V; $V_{IOM} = 1.8$ V to 6 V                                      | -50                  | 0    | +50  | μА   |

| $\Delta I_{IOM}/\Delta I_{VOC}$ | gain of I <sub>VOC</sub> to I <sub>IOM</sub> current transfer | -100 μA < I <sub>VOC</sub> < 5 mA;<br>V <sub>VIN</sub> = 0 V to 5.5 V;<br>V <sub>IOM</sub> = 1.8 V to 6 V | 0.9                  | 1.0  | 1.1  |      |

#### TDA6118JF

| SYMBOL                                                    | PARAMETER               | CONDITIONS                       | MIN. | TYP. | MAX. | UNIT |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------|----------------------------------|------|------|------|------|--|--|--|--|--|

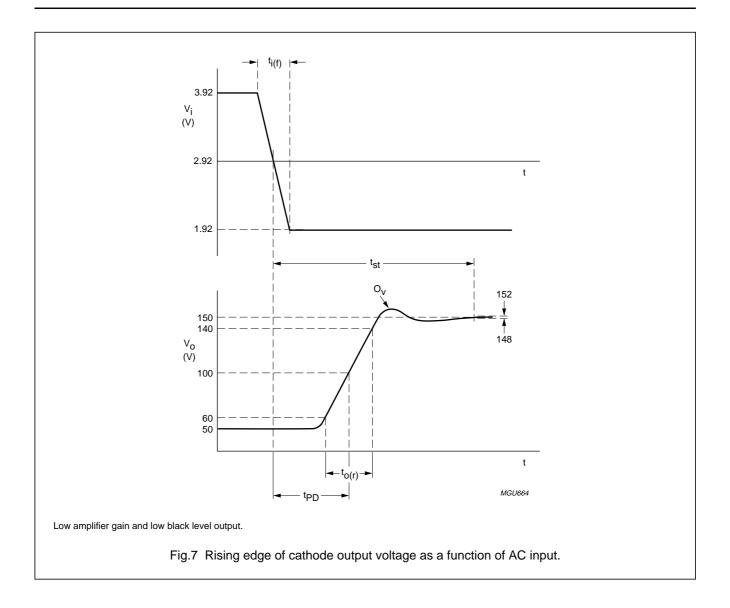

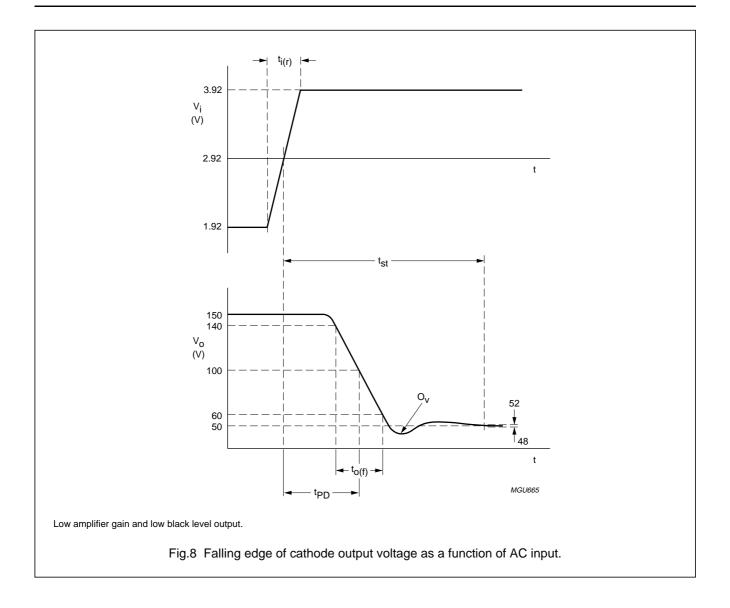

| Cathode output timing (pin VOC); see Figs 7 and 8; note 2 |                         |                                  |      |      |      |      |  |  |  |  |  |

| t <sub>o(r)</sub>                                         | output rise time        | 10 % to 90 % output              | 17   | 21   | 25   | ns   |  |  |  |  |  |

| t <sub>o(f)</sub>                                         | output fall time        | 90 % to 10 % output              | 17   | 21   | 25   | ns   |  |  |  |  |  |

| t <sub>PD</sub>                                           | propagation delay       | 50 % input to 50 % output        | 16   | 21   | 26   | ns   |  |  |  |  |  |

| t <sub>st</sub>                                           | settling time           | 50 % input to 100 % ± 2 % output | _    | _    | 200  | ns   |  |  |  |  |  |

| O <sub>v</sub>                                            | overshoot voltage ratio |                                  | _    | 6    | _    | %    |  |  |  |  |  |

#### **Notes**

- 1. PSRR definition: ratio of the change in supply voltage to the change in input voltage when there is no change in output voltage.

- 2. Timing conditions:  $f_i < 1$  MHz;  $t_{i(r)} = t_{i(f)} = 15$  ns;  $V_{VOC} = 100$  V (p-p) square wave.

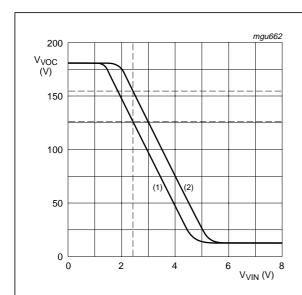

Pin GS connected to ground.

- (1) Low black level output (pin BLS connected to ground).

- (2) High black level output (pin BLS left open-circuit).

Fig.5 DC-to-DC transfer of input to output with low amplifier gain.

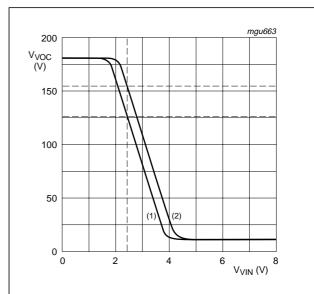

Pin GS left open-circuit.

- (1) Low black level output (pin BLS connected to ground).

- (2) High black level output (pin BLS left open-circuit).

Fig.6 DC-to-DC transfer of input to output with high amplifier gain.

## TDA6118JF

## TDA6118JF

## TDA6118JF

#### **APPLICATION AND TEST INFORMATION**

Fig.9 Test circuit.

2004 Aug 26 9 Philips Semiconductors Product specification

### Video output amplifier

#### TDA6118JF

#### **External flashover protection**

For sufficient flashover protection it is necessary to apply an external diode for each channel. See application note "AN01031 (Application note TDA6118JF)".

To limit the diode current an external 220  $\Omega$  carbon high-voltage resistor in series with the external diode and a 2 kV spark gap are needed (for this resistor value, the CRT has to be connected to the main printed-circuit board).

V<sub>DD</sub> must be decoupled to ground:

- With a capacitor ≥100 nF with good HF behaviour (e.g. foil); this capacitor must be placed as close as possible to pins V<sub>DD</sub> and GND but definitely within 5 mm.

- With a capacitor >10 μF on the picture tube base print.

#### Switch-off behaviour

The switch-off behaviour of the TDA6118JF can be controlled due to the fact that the output pins are still under control of the input pins for low power supply voltages (approximately 30 V and higher).

#### **Bandwidth**

The addition of the flash resistor produces a decreased bandwidth and increases the rise and fall times. For further information see application note "ANO1031 (Application note TDA6118JF)".

#### Dissipation

Regarding the dissipation, distinction must be made between the static dissipation (independent of the frequency) and the dynamic dissipation (proportional to the frequency).

The static dissipation of the TDA6118JF is related to the voltage supply current. The static dissipation equals:

$$P_{stat} = V_{DD} \times I_{q}$$

Where:

V<sub>DD</sub> = supply voltage

I<sub>q</sub> = quiescent supply current.

The dynamic dissipation equals:

$$P_{dvn} = V_{DD} \times (C_L + C_{int}) \times f_i \times V_{VOC} \times \delta$$

Where:

C<sub>L</sub> = load capacitance

$C_{int}$  = internal load capacitance ( $\approx 4 \text{ pF}$ )

f<sub>i</sub> = input frequency

V<sub>VOC</sub> = output voltage (peak-to-peak value)

$\delta$  = non-blanking duty cycle.

The IC must be mounted on the picture tube base print to minimize the load capacitance  $C_L$ .

## TDA6118JF

#### INTERNAL PIN CONFIGURATION

| PIN | SYMBOL   | INTERNAL CIRCUIT       |

|-----|----------|------------------------|

| 1   | TP       | 1 MGU667               |

| 3   | VIN      | 3                      |

| 2   | GS       |                        |

| 7   | BLS      | 2 MGU668               |

| 8   | VOC      |                        |

| 5   | IOM      | 8<br>8<br>MGU669       |

| 4   | GND      | connected to substrate |

| 6   | $V_{DD}$ | connected to supply    |

| 9   | n.c.     | not connected          |

## TDA6118JF

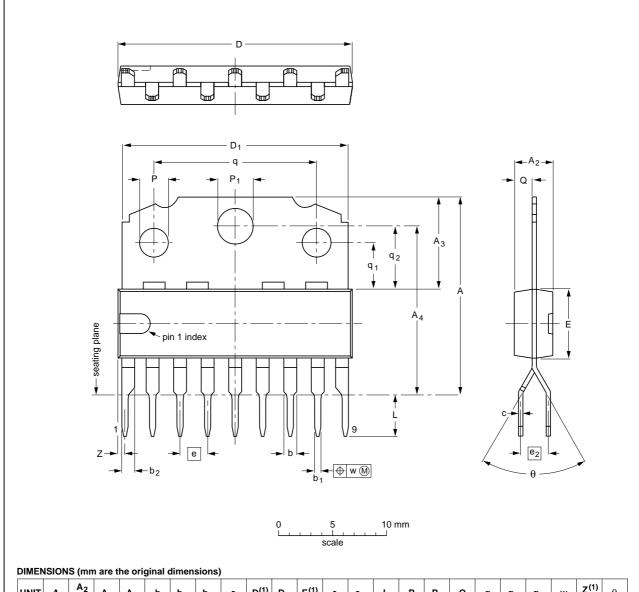

#### **PACKAGE OUTLINE**

#### DBS9MPF: plastic DIL-bent-SIL medium power package with fin; 9 leads

SOT111-1

| UNIT | Α            | A <sub>2</sub><br>max. | <b>A</b> <sub>3</sub> | A <sub>4</sub> | b            | b <sub>1</sub> | b <sub>2</sub> | С | D <sup>(1)</sup> | D <sub>1</sub> | E <sup>(1)</sup> | е    | e <sub>2</sub> | L          | Р            | P <sub>1</sub> | Q            | q            | q <sub>1</sub> | q <sub>2</sub> | w    | Z <sup>(1)</sup><br>max. | θ          |

|------|--------------|------------------------|-----------------------|----------------|--------------|----------------|----------------|---|------------------|----------------|------------------|------|----------------|------------|--------------|----------------|--------------|--------------|----------------|----------------|------|--------------------------|------------|

| mm   | 18.5<br>17.8 | 3.7                    | 8.7<br>8.0            | 15.5<br>15.1   | 1.40<br>1.14 | 0.67<br>0.50   | 1.40<br>1.14   |   |                  | 21.4<br>20.7   | 6.48<br>6.20     | 2.54 | 2.54           | 3.9<br>3.4 | 2.75<br>2.50 | 3.4<br>3.2     | 1.75<br>1.55 | 15.1<br>14.9 | 4.4<br>4.2     | 5.9<br>5.7     | 0.25 | 1                        | 65°<br>55° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | EUROPEAN | ISSUE DATE |  |            |                                 |  |

|----------|-----|----------|------------|--|------------|---------------------------------|--|

| VERSION  | IEC | JEDEC    | JEITA      |  | PROJECTION | ISSUE DATE                      |  |

| SOT111-1 |     |          |            |  |            | <del>95-03-11</del><br>03-03-12 |  |

#### TDA6118JF

#### **SOLDERING**

## Introduction to soldering through-hole mount packages

This text gives a brief insight to wave, dip and manual soldering. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

Wave soldering is the preferred method for mounting of through-hole mount IC packages on a printed-circuit board.

#### Soldering by dipping or by solder wave

Driven by legislation and environmental forces the worldwide use of lead-free solder pastes is increasing. Typical dwell time of the leads in the wave ranges from 3 to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature ( $T_{stg(max)}$ ). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

#### Suitability of through-hole mount IC packages for dipping and wave soldering methods

| PACKAGE                         | SOLDERIN | G METHOD                |

|---------------------------------|----------|-------------------------|

| PACKAGE                         | DIPPING  | WAVE                    |

| CPGA, HCPGA                     | -        | suitable                |

| DBS, DIP, HDIP, RDBS, SDIP, SIL | suitable | suitable <sup>(1)</sup> |

| PMFP <sup>(2)</sup>             | -        | not suitable            |

#### **Notes**

- 1. For SDIP packages, the longitudinal axis must be parallel to the transport direction of the printed-circuit board.

- 2. For PMFP packages hot bar soldering or manual soldering is suitable.

**TDA6118JF**

#### **DATA SHEET STATUS**

| LEVEL | DATA SHEET<br>STATUS <sup>(1)</sup> | PRODUCT<br>STATUS(2)(3) | DEFINITION                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                      | Development             | This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                    |

| II    | Preliminary data                    | Qualification           | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                        | Production              | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

#### **Notes**

- 1. Please consult the most recently issued data sheet before initiating or completing a design.

- 2. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- 3. For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **DEFINITIONS**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **DISCLAIMERS**

Life support applications — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

## Philips Semiconductors – a worldwide company

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2004

SCA76

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

R24/02/pp15

Date of release: 2004 Aug 26

Document order number: 9397 750 13715

Let's make things better.