# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

# **TDA3330**

#### TV COLOR PROCESSOR

This device will accept a PAL or NTSC composite video signal and output the three color signals, needing only a simple driver amplifier to interface to the picture tube.

Its simplified approach makes it particularly suitable for low cost CTV systems.

- No Oscillator Adjustment Required

- Four dc High Impedance User Controls

- Uses Inexpensive 4.43/3.58 MHz Crystals

- Interfaces With TDA3030B SECAM Adaptor

- Uses Horizontal Flyback or Super Sandcastle Pulse

- Single 12 V Supply

- Low Dissipation

# TV COLOR PROCESSOR

SILICON MONOLITHIC INTEGRATED CIRCUIT

# **TDA3330**

MAXIMUM RATINGS (T<sub>A</sub> = +25°C unless otherwise stated)

| Rating                      | Pin | Value       | Unit |

|-----------------------------|-----|-------------|------|

| Supply Voltage              | 20  | 14          | Vdc  |

| Operating Temperature Range |     | 0 to +70    | °C   |

| Storage Temperature Range   |     | 65 to + 150 | °C   |

ELECTRICAL CHARACTERISTICS ( $T_{\Delta} = 25^{\circ}C$ ,  $V_{CC} = 12 \text{ V}$ )

| Characteristic                                                                                                                                          | Pin           | Min              | Түр                     | Max                      | Unit                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-------------------------|--------------------------|----------------------------|

| Supply Voltage<br>Supply Current                                                                                                                        | 20            | 10.8<br>—        | 12<br>—                 | 13.2<br>50               | V<br>mA                    |

| Composite Video Input                                                                                                                                   | 17            | _                | 1.0                     |                          | Vp-p                       |

| Video Input Resistance<br>Burst Gate On<br>Off                                                                                                          |               |                  | 5.0<br>1.5              |                          | kΩ<br>MΩ                   |

| Chroma Input (Burst) Input Resistance ACC Effectiveness                                                                                                 | 22<br>22<br>1 | 10<br>—<br>— 1.5 | 100<br>5.0<br>0         | 200<br><br>+ 1.5         | mVp-p<br>kΩ<br>dB          |

| Luminance Gain between Pin 17 and Outputs (Contrast max) Luminance Bandwidth ( – 3.0 dB) Output Resistance Residual Carrier (4.43 MHz) PAL Offset (H/2) | 12, 13, 14    | I                | 8.0<br>5.0<br>170<br>—  | —<br>—<br>—<br>200<br>50 | MHz<br>Ω<br>mVp-p<br>mVp-p |

| U Input Sensitivity for 5.0 V Blue Output                                                                                                               | 5             |                  | 340                     |                          | mVp-p                      |

| Matrix Error                                                                                                                                            | 12, 13, 14    |                  |                         | 10                       | %                          |

| Oscillator Capture Range                                                                                                                                |               | 300              | 500                     | _                        | Hz                         |

| U Reference Phase Error                                                                                                                                 |               | -                | _                       | 5.0                      | Degrees                    |

| V Reference Phase Error                                                                                                                                 |               | _                | _                       | 5.0                      | Degrees                    |

| Color Kill Attenuation                                                                                                                                  | 12, 13, 14    | 50               | _                       |                          | dB                         |

| Contrast Tracking Luma/Chroma                                                                                                                           | 12, 13, 14    |                  | 0                       | 2.0                      | dB                         |

| Sandcastle Slice Level Burst Gate Line Blanking R Input V <sub>15</sub> > 7.0 V V <sub>15</sub> < 7.0 V                                                 | 15            | 0.5<br>—         | 7.2<br>1.5<br>5.0<br>10 | 8.0<br>2.5<br>—          | V<br>V<br>kΩ<br>kΩ         |

# INPUT/OUTPUT FUNCTIONS

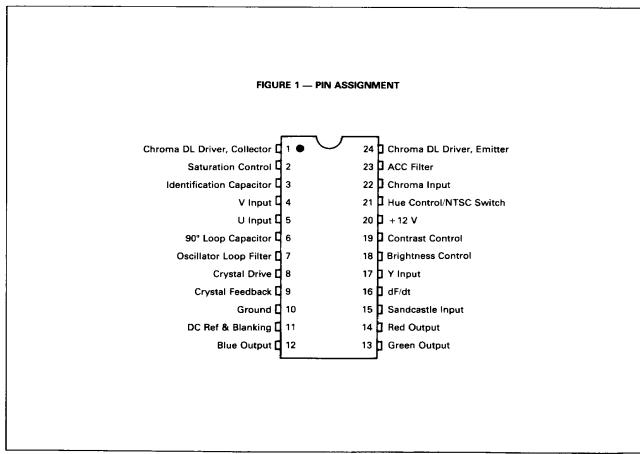

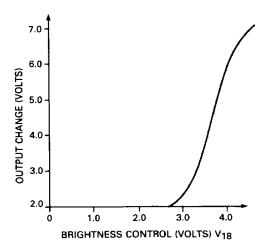

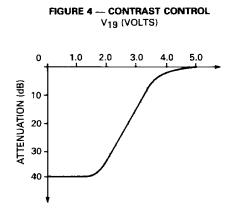

# FIGURE 2 -- BRIGHTNESS CONTROL

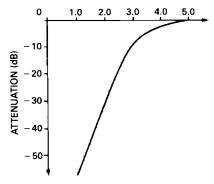

# FIGURE 3 — SATURATION CONTROL VOLTAGE $V_2$ (VOLTS)

Pin 2 is automatically pulled to ground with a misidentified PAL signal.

Note: Nominal 100% saturation point is given by choice of Rpin 23 which sets ACC operating point.

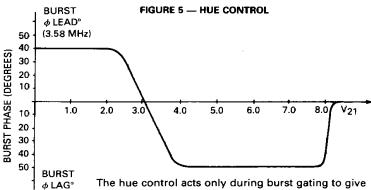

The hue control acts only during burst gating to give a  $\pm 40^{\circ}$  phase shift between the burst and chrominance signal.

Pin 21 is also used to select NTSC when  $\rm V_{21} < 8.0~V$  and thus the control will operate only in this mode. NTSC selection means the PAL phase switching is turned off. Delay-line and filter switching must be implemented externally.

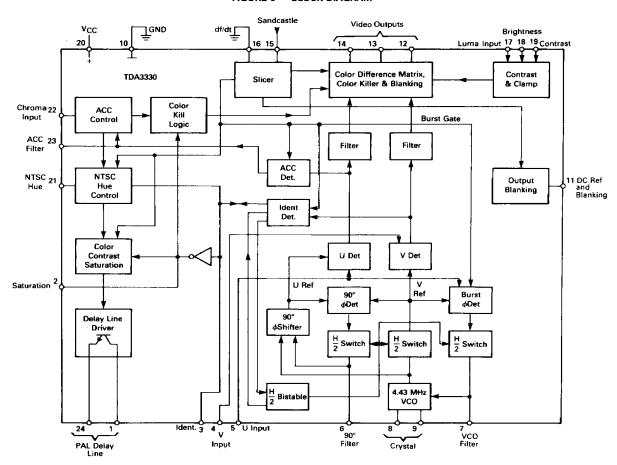

# FIGURE 6 — BLOCK DIAGRAM

# 9

#### **CIRCUIT OPERATION**

#### **CHROMINANCE DECODER SECTION**

The chrominance decoder section of the TDA3330 consists of the following blocks:

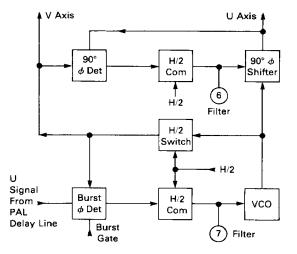

Phase-locked reference oscillator — Figures 7, 8 and 9 Phase-locked 90 degree servo loop — Figures 9 and 10 U and V axis decoders

ACC detector and identification detector — Figure 11 Identification circuits and PAL bistable — Figure 12 Color difference filters and matrixes with fast blanking circuits.

The major design considerations apart from optimum performance were:

- a minimum number of factory adjustments

- a minimum number of external components

- compatibility with the SECAM adapter TDA3030B

- low dissipation

- use of a standard 4.433618 MHz crystal rather than a 2.0 fc crystal with divider, (or standard 3.579545 MHz for NTSC).

# REFERENCE REGENERATION

The crystal VCO is of the phase shift variety in which the frequency is controlled by varying the phase of the feedback. Much care was taken to ensure that the oscillator loop gain and the crystal loading impedance were held constant in order to ensure that the circuit functions well with low grade crystals (crystals having high magnitude spurious responses can cause bad phase jitter). It is also necessary to ensure that the gain at third harmonic is low enough to ensure absence of oscillation at this frequency.

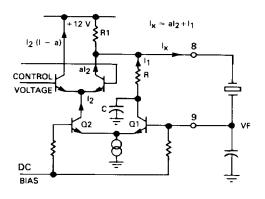

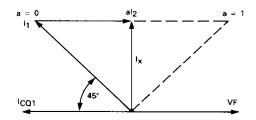

By referring to Figures 7 and 8 it can be seen that the necessary  $\pm 45^{\circ}$  phase shift is obtained by variable addition of two currents I<sub>1</sub> and I<sub>2</sub> which are then fed into the load resistance of the crystal tuned circuit R<sub>1</sub>. Feedback is taken from the crystal load capacitance which gives a voltage VF lagging the crystal current by 90°.

The RC network in Q1 collector causes I<sub>1</sub> to lag the collector current of Q1 by 45°.

For SECAM operation the currents  $I_1$  and  $I_2$  are added together in a fixed ratio giving a frequency close to nominal.

When decoding PAL there are two departures from normal chroma reference regeneration practice:

a) The loop is locked to the burst entering from the PAL delay line matrix U channel and hence there is no alternating component. A small improvement in signal noise ratio is gained but more important is that the loop filter is not compromised by the 7.8 kHz component normally required at this point for PAL identification.

#### FIGURE 7 — VOLTAGE CONTROLLED OSCILLATOR (VCO)

FIGURE 8 — VECTOR DIAGRAM FOR VCO

b) The H/2 switching of the oscillator phase is carried out before the phase detector. This implies any error signal from the phase detector is a signal at 7.8 kHz and not DC. A commutator at the phase detector output also driven from the PAL bistable converts this AC signal to a DC prior to the loop filter. The purpose of this is that constant offsets in the phase detector are converted by the commutator to a signal at 7.8 kHz which is integrated to zero and does not give a phase error.

When used for decoding NTSC the bistable is inhibited, and slightly less accurate phasing is achieved; however, as a hue control is used on NTSC this cannot be considered to be serious disadvantage.

# TDA3330

# 90° REFERENCE GENERATION

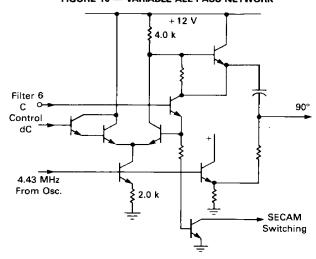

To generate the U axis reference a variable all-pass network is utilized in a servo loop. The output of the all-pass network is compared with the oscillator output with a phase detector of which the output is filtered and corrects the operating point of the variable all-pass network. (See Figure 10.)

As with the reference loop the oscillator signal is taken after the H/2 phase switch and a commutator inserted before the filter so that constant phase detector errors are cancelled.

For SECAM operation with TDA3030B the loop filter is grounded causing near zero phase shift so that the two synchronous detectors work in phase and not in quadrature.

The use of a 4.4 MHz oscillator and a servo loop to generate the required 90° reference signal allows the use of a standard, high volume, low cost crystal and gives an extremely accurate 90° which may be easily switched to 0° for decoding AM SECAM generated by the TDA3030B adapter.

FIGURE 9 — BLOCK DIAGRAM OF REFERENCE SECTION

# **ACC AND IDENTIFICATION DETECTORS**

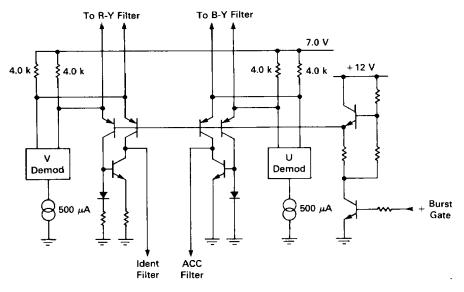

During burst gate time the output components of the U and also the V demodulators are steered into PNP emitters. One collector current of each PNP pair is mirrored and balanced against its twin giving push pull current sources for driving the ACC and the identification filter capacitors.

The identification detector is given an internal offset by making the NPN current mirror emitter resistors unequal. The resistors are offset by 5% such that the identification detector pulls up on its filter capacitor with zero signal.

# **IDENTIFICATION**

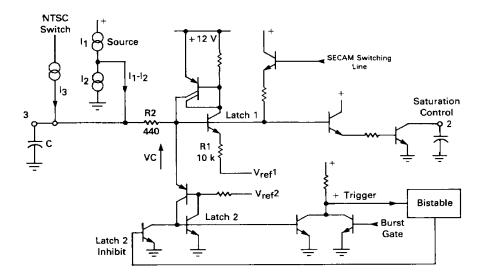

See Figure 12 for definitions.

$\begin{array}{lll} \text{Monochrome} & \text{I}_1 > \text{I}_2 \\ \text{PAL ident. OK} & \text{I}_1 < \text{I}_2 \\ \text{PAL ident. X} & \text{I}_1 > \text{I}_2 \\ \text{NTSC} & \text{I}_3 > \text{I}_2 \\ \end{array}$

Only for correctly identified PAL signal is the capacitor voltage held low since I<sub>2</sub> is then greater than I<sub>1</sub>.

FIGURE 10 — VARIABLE ALL-PASS NETWORK

For monochrome and incorrectly identified PAL signals  $I_1 > I_2$  hence voltage  $V_C$  rises with each burst gate pulse.

When  $V_{ref}1$  is exceeded by 0.7 V latch 1 is made conducting which increases rate of voltage rise on C. Maximum current is limited by  $R_1$ .

When V<sub>ref</sub>2 is exceeded by 0.7 V then latch 2 is made conducting until C is completely discharged and the current drops to a value insufficient to hold on latch 2.

As latch 2 turns on latch 1 must turn off.

Latch 2 turning on gives extra trigger pulse to bistable to correct identification.

The inhibit line on latch 2 restricts latch 2 conduction to alternate lines as controlled by the bistable. This function allows the SECAM switching line to inhibit the bistable operation by firing latch 2 in the correct phase for SECAM. For NTSC latch 2 is fired by current (I<sub>3</sub>) injected into Pin 3 by the NTSC switch. This is supplied internally when V<sub>21</sub> falls below 8.0 V.

If the voltage on C is greater than 1.4 V then the saturation is held down. Only for SECAM/NTSC with latch 2 on or correctly identified PAL can the saturation control be anywhere but minimum.

# FIGURE 11 — ACC AND IDENTIFICATION DETECTORS

**TDA3330**

FIGURE 12 — IDENTIFICATION CIRCUIT

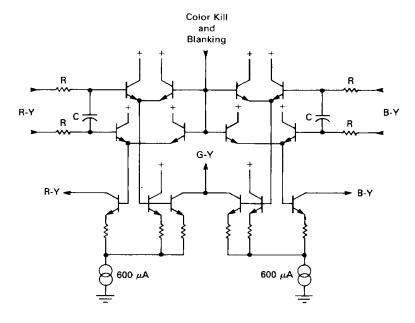

# COLOR DIFFERENCE MATRIXING, COLOR KILLING, AND CHROMA BLANKING

During picture time the two demodulators feed simple RC filters with emitter follower outputs. Color killing and blanking is performed by lifting these outputs to a voltage above the maximum value that the color difference signal could supply.

The color difference matrixing is performed by 2 differential amplifiers each with one side split to give the correct values of the -(B-Y) and -(R-Y) signals. These are added to give the (G-Y) signal.

The 3 color difference signals are then taken to the virtual earths of the video output stages together with luminance signal.

# FIGURE 13 — COLOR DIFFERENCE STAGES

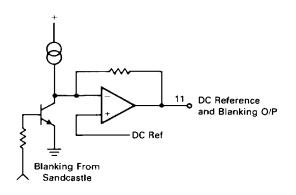

### SANDCASTLE SECTION

The input signal is sliced at 2 levels, 1.5 V and 7.2 V. Above 1.5 V is used for blanking, above 7.2 V for burst gating provided level on Pin 16 is below 0.7 V. If a normal Sandcastle is used, it is recommended to ground the

Pin 16. This input is used to inhibit the burst gate. This is used if a true Sandcastle is not available; in this case horizontal flyback may be used instead and differentiated flyback applied to the  $\frac{df}{dt}$  pin (input resistance 1.0 k $\Omega$ ).

# FIGURE 14 — DC REFERENCE AND BLANKING SECTION

The DC Reference and Blanking section is used to bias the Video output stages. The temperature coefficient is arranged to be a VBE drift less than the Red, Green and Blue outputs.

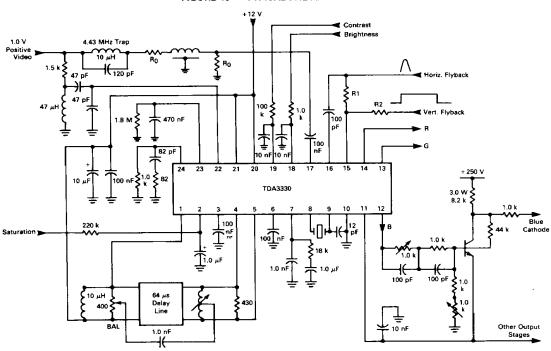

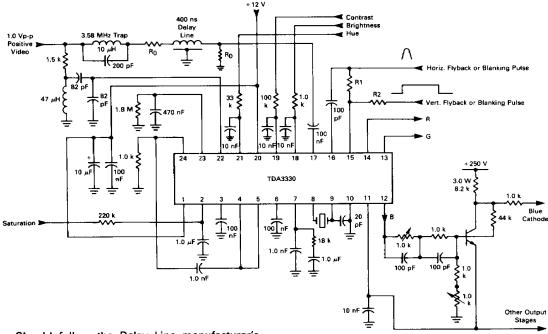

# FIGURE 15 -- TYPICAL PAL APPLICATION

FIGURE 16 -- TYPICAL NTSC APPLICATION

- ${

m R}_0$  Should follow the Delay Line manufacturer's recommendations.

- R<sub>1</sub> Should be selected to give approximately 10–12 V pulse at Pin 15 (approximately 5.0 k internal resistance).

R<sub>2</sub> — Should be selected to give approximately 4.0 to 5.0 V pulse at Pin 15 (approximately 10 k internal resistance).